Ring-Oscillator with Multiple Transconductors for Linear Analog-to-Digital Conversion

Abstract

:1. Introduction

2. Materials and Methods

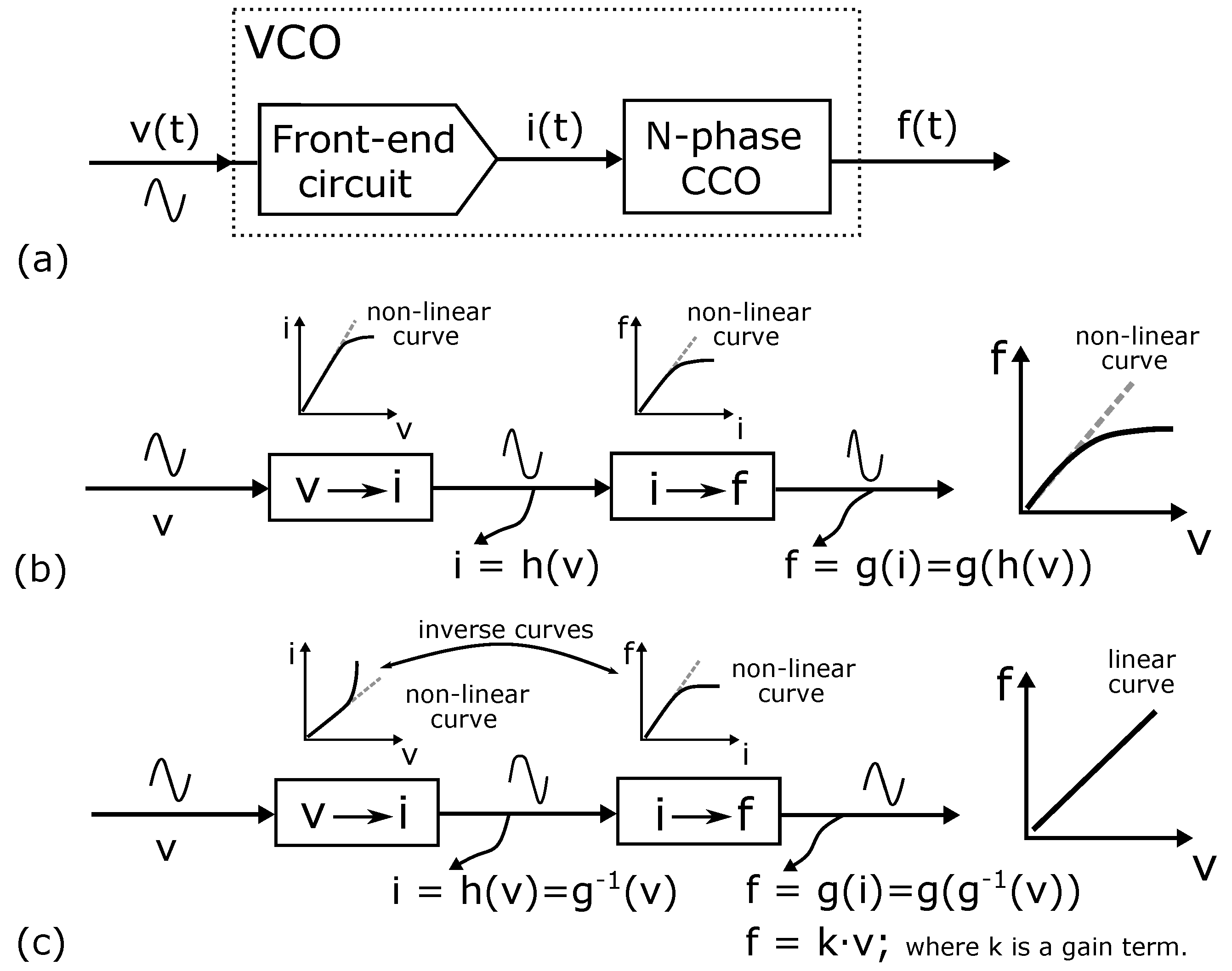

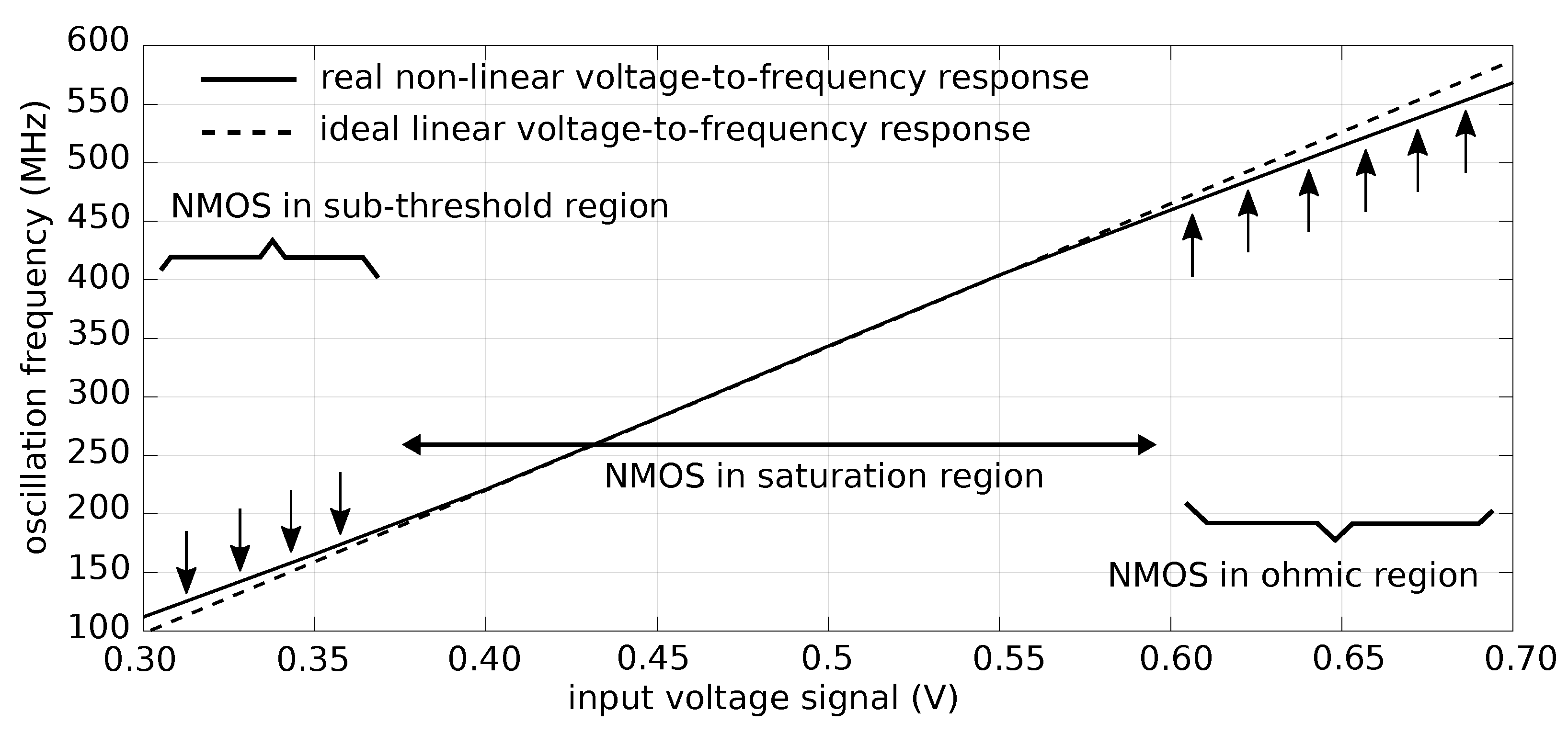

2.1. Nonlinearity in Ring-Oscillators

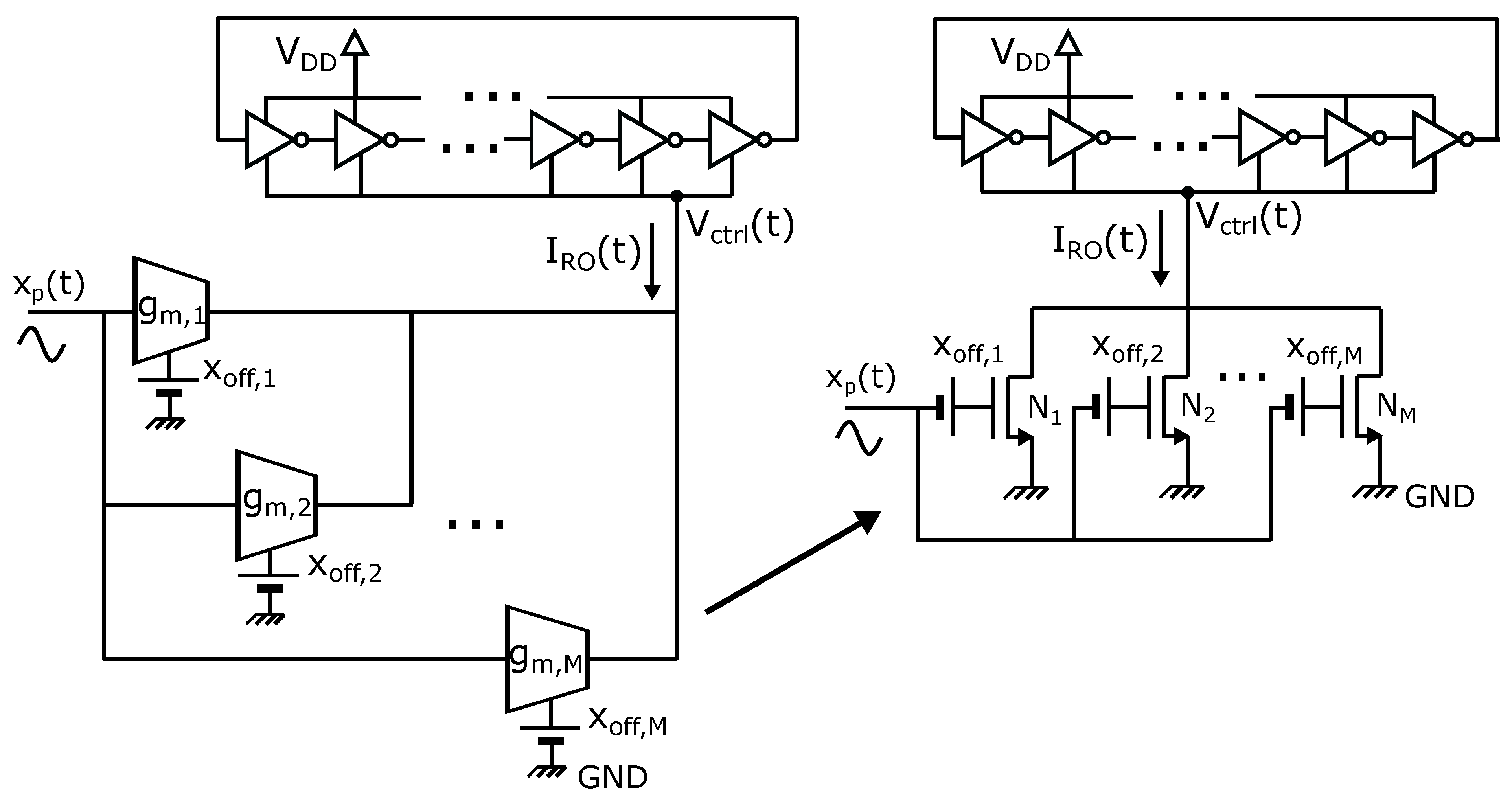

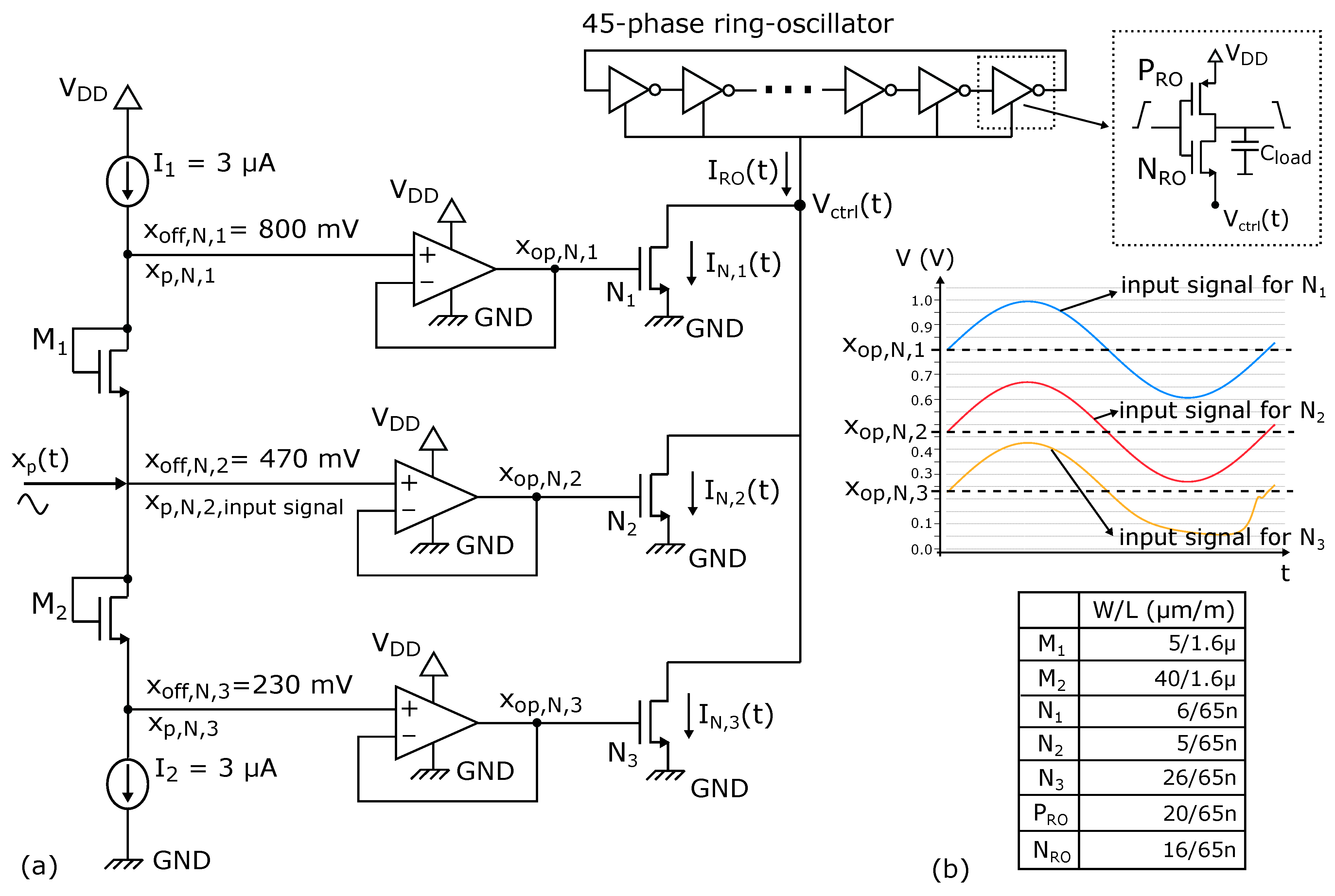

2.2. Proposed Multiple-Transconductor Ring-Oscillator

3. Results

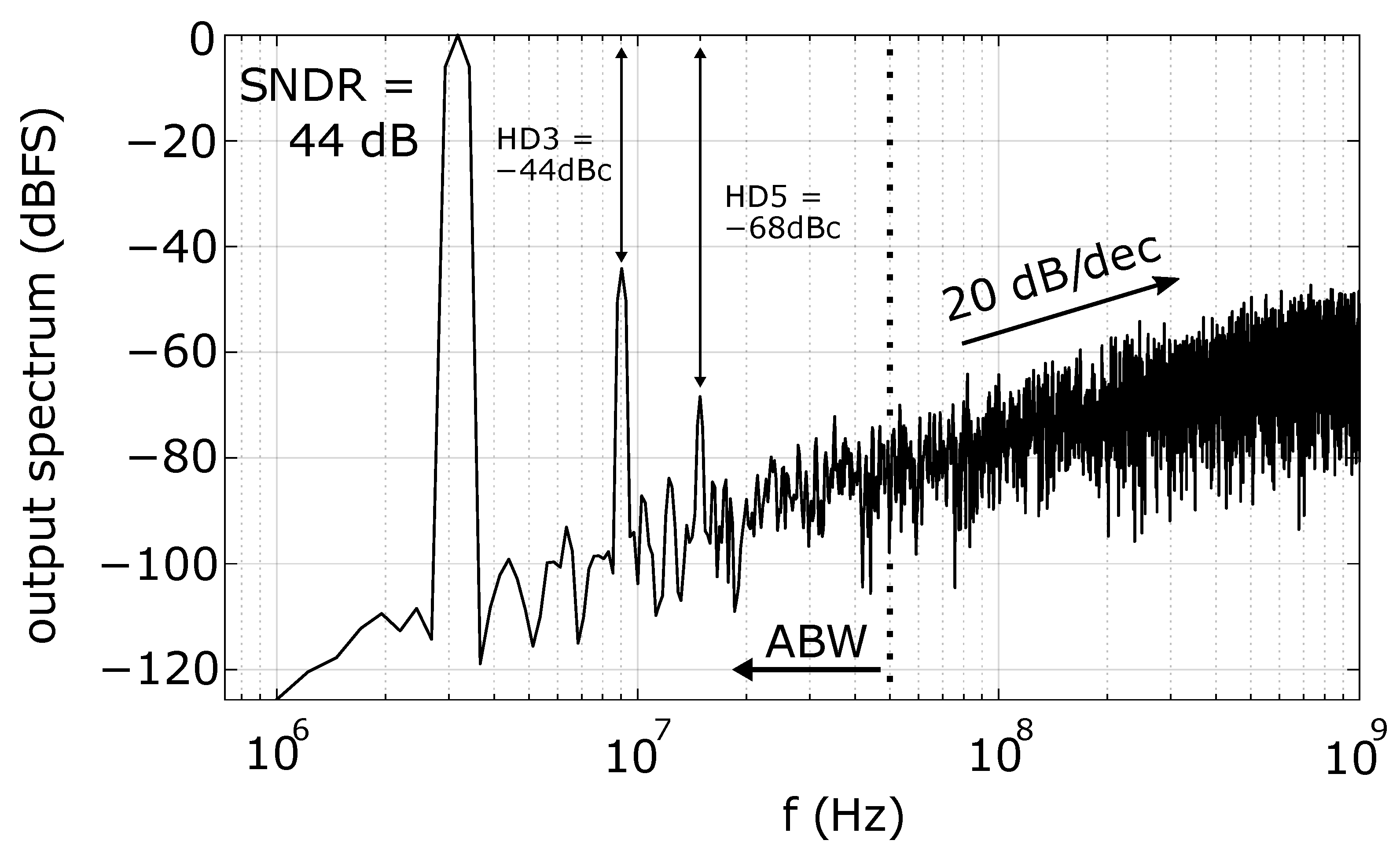

3.1. Circuit Validation

3.2. Circuit-Level Impairments

3.3. Calibration Circuit

4. Discussion

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Abbreviations

| ADC | Analog-to-digital converter |

| CCO | Current-controlled oscillator |

| ENOB | Effective number of bits |

| IoT | Internet-of-things |

| VCO | Voltage-controlled oscillator |

| SAR | Successive approximation register |

| Opamp | Operational amplifier |

| TI | Time-Interleaved |

| NS-SAR | Noise-shaping SAR |

| TINS-SAR | Time interleaving noise-shaping SAR |

| Delta-Sigma | |

| CTSDM | Continuous-time modulator |

| VCO-based ADC | Voltage-controlled oscillator-based analog-to-digital converter |

| MASH | Multi-stage noise shaping |

| THD | Total harmonic distortion |

| PVT | Process, voltage and temperature |

| ABW | Analog bandwidth |

| HD3 | Third harmonic distortion term |

| HD5 | Fifth harmonic distortion term |

| HD2 | Second harmonic distortion term |

| SNDR | Signal-to-noise-distortion ratio |

| SNR | Signal-to-noise ratio |

| INL | Integral nonlinearity |

| LSB | Least significant bit |

| NUS | Nonuniform sampling |

| DSP | Digital signal processing |

| CDF | Cumulative distribution function |

References

- Lewyn, L.L.; Ytterdal, T.; Wulff, C.; Martin, K. Analog Circuit Design in Nanoscale CMOS Technologies. Proc. IEEE 2009, 97, 1687–1714. [Google Scholar] [CrossRef]

- Zahrai, S.A.; Onabajo, M. Review of Analog-To-Digital Conversion Characteristics and Design Considerations for the Creation of Power-Efficient Hybrid Data Converters. J. Low Power Electron. Appl. 2018, 8, 12. [Google Scholar] [CrossRef] [Green Version]

- Weaver, S.; Hershberg, B.; Moon, U. Digitally Synthesized Stochastic Flash ADC Using Only Standard Digital Cells. IEEE Trans. Circuits Syst. Regul. Pap. 2014, 61, 84–91. [Google Scholar] [CrossRef]

- Fahmy, A.; Liu, J.; Kim, T.; Maghari, N. An All-Digital Scalable and Reconfigurable Wide-Input Range Stochastic ADC Using Only Standard Cells. IEEE Trans. Circuits Syst. II Express Briefs 2015, 62, 731–735. [Google Scholar] [CrossRef]

- Jeon, M.; Yoo, W.; Kim, C.; Yoo, C. A Stochastic Flash Analog-to-Digital Converter Linearized by Reference Swapping. IEEE Access 2017, 5, 23046–23051. [Google Scholar] [CrossRef]

- Aiello, O.; Crovetti, P.; Alioto, M. Fully Synthesizable Low-Area Analogue-to-Digital Converters With Minimal Design Effort Based on the Dyadic Digital Pulse Modulation. IEEE Access 2020, 8, 70890–70899. [Google Scholar] [CrossRef]

- Park, J.; Hwang, Y.; Jeong, D. A 0.5-V Fully Synthesizable SAR ADC for On-Chip Distributed Waveform Monitors. IEEE Access 2019, 7, 63686–63697. [Google Scholar] [CrossRef]

- Cao, Z.; Yan, S.; Li, Y. A 32 mW 1.25 GS/s 6b 2b/Step SAR ADC in 0.13 μm CMOS. IEEE J. Solid-State Circuits 2009, 44, 862–873. [Google Scholar] [CrossRef]

- Inerfield, M.; Kamath, A.; Su, F.; Hu, J.; Yu, X.; Fong, V.; Alnaggar, O.; Lin, F.; Kwan, T. An 11.5-ENOB 100-MS/s 8mW dual-reference SAR ADC in 28nm CMOS. In Proceedings of the 2014 Symposium on VLSI Circuits Digest of Technical Papers, Honolulu, HI, USA, 10–13 June 2014; pp. 1–2. [Google Scholar]

- Kapusta, R.; Shen, J.; Decker, S.; Li, H.; Ibaragi, E.; Zhu, H. A 14b 80 MS/s SAR ADC With 73.6 dB SNDR in 65 nm CMOS. IEEE J. Solid-State Circuits 2013, 48, 3059–3066. [Google Scholar] [CrossRef]

- Morie, T.; Miki, T.; Matsukawa, K.; Bando, Y.; Okumoto, T.; Obata, K.; Sakiyama, S.; Dosho, S. A 71dB-SNDR 50 MS/s 4.2 mW CMOS SAR ADC by SNR enhancement techniques utilizing noise. In Proceedings of the 2013 IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 17–21 February 2013; pp. 272–273. [Google Scholar]

- Chang, D.; Moon, U. A 1.4-V 10-bit 25-MS/s pipelined ADC using opamp-reset switching technique. IEEE J. Solid-State Circuits 2003, 38, 1401–1404. [Google Scholar] [CrossRef]

- Shibata, H.; Taylor, G.; Schell, B.; Kozlov, V.; Patil, S.; Paterson, D.; Ganesan, A.; Dong, Y.; Yang, W.; Yin, Y.; et al. 16.6 An 800MHz-BW VCO-Based Continuous-Time Pipelined ADC with Inherent Anti-Aliasing and On-Chip Digital Reconstruction Filter. In Proceedings of the 2020 IEEE International Solid-State Circuits Conference—(ISSCC), San Francisco, CA, USA, 16–20 February 2020; pp. 260–262. [Google Scholar]

- Dortz, N.L.; Blanc, J.; Simon, T.; Verhaeren, S.; Rouat, E.; Urard, P.; Tu, S.L.; Goguet, D.; Lelandais-Perrault, C.; Benabes, P. 22.5 A 1.62GS/s time-interleaved SAR ADC with digital background mismatch calibration achieving interleaving spurs below 70dBFS. In Proceedings of the 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 9–13 February 2014; pp. 386–388. [Google Scholar]

- Baert, M.; Dehaene, W. A 5-GS/s 7.2-ENOB Time-Interleaved VCO-Based ADC Achieving 30.5 fJ/cs. IEEE J. Solid-State Circuits 2020, 55, 1577–1587. [Google Scholar] [CrossRef]

- Paton, S.; Giandomenico, A.D.; Hernandez, L.; Wiesbauer, A.; Potscher, T.; Clara, M. A 70-mW 300-MHz CMOS continuous-time ΣΔ ADC with 15-MHz bandwidth and 11 bits of resolution. IEEE J. Solid-State Circuits 2004, 39, 1056–1063. [Google Scholar] [CrossRef]

- Jie, L.; Zheng, B.; Flynn, M.P. 20.3 A 50MHz-Bandwidth 70.4dB-SNDR Calibration-Free Time-Interleaved 4th-Order Noise-Shaping SAR ADC. In Proceedings of the 2014 2019 IEEE International Solid- State Circuits Conference—(ISSCC), San Francisco, CA, USA, 17–21 February 2019; pp. 332–334. [Google Scholar]

- Lin, C.-Y.; Lin, Y.-Z.; Tsai, C.-H.; Lu, C.-H. 27.5 An 80MHz-BW 640MS/s Time-Interleaved Passive Noise-Shaping SAR ADC in 22nm FDSOI Process. In Proceedings of the 2021 IEEE International Solid- State Circuits Conference (ISSCC), San Francisco, CA, USA, 13–22 February 2021; pp. 378–380. [Google Scholar]

- Straayer, M.Z.; Perrott, M.H. A 12-Bit, 10-MHz Bandwidth, Continuous-Time ΣΔ ADC With a 5-Bit, 950-MS/s VCO-Based Quantizer. IEEE J. Solid-State Circuits 2008, 43, 805–814. [Google Scholar] [CrossRef]

- Cardes, F.; Gutierrez, E.; Quintero, A.; Buffa, C.; Wiesbauer, A.; Hernandez, L. 0.04-mm2 103-dB-A Dynamic Range Second-Order VCO-Based Audio ΣΔ ADC in 0.13-μm CMOS. IEEE J. Solid-State Circuits 2018, 53, 1731–1742. [Google Scholar] [CrossRef]

- Huang, S.; Egan, N.; Kesharwani, D.; Opteynde, F.; Ashburn, M. 28.3 A 125MHz-BW 71.9dB-SNDR VCO-based CT ΔΣ ADC with segmented phase-domain ELD compensation in 16 nm CMOS. In Proceedings of the 2017 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 5–9 February 2017; pp. 470–471. [Google Scholar]

- Zhong, Y.; Tang, X.; Liu, J.; Zhao, W.; Li, S.; Sun, N. An 81.5dB-DR 1.25MHz-BW VCO-Based CT ΔΣ ADC with Double-PFD Quantizer. In Proceedings of the 2021 IEEE Custom Integrated Circuits Conference (CICC), Austin, TX, USA, 25–30 April 2021; pp. 1–2. [Google Scholar]

- Xing, X.; Gielen, G.G.E. A 42 fJ/Step-FoM Two-Step VCO-Based Delta-Sigma ADC in 40 nm CMOS. IEEE J. Solid-State Circuits 2015, 50, 714–723. [Google Scholar] [CrossRef]

- Dey, S.; Mayaram, K.; Fiez, T. A 12 MHz BW, 80 dB SNDR, 83 dB DR, 4th order CT-ΔΣ modulator with 2nd order noise-shaping and pipelined SAR-VCO based quantizer. In Proceedings of the 2019 IEEE Custom Integrated Circuits Conference (CICC), Austin, TX, USA, 14–17 April 2019; pp. 1–4. [Google Scholar]

- Hou, Y.; Chen, Z.; Miyahara, M.; Matsuzawa, A. An Op-amp free SAR-VCO hybrid ADC with second-order noise shaping. In Proceedings of the 2016 IEEE International Conference on Electron Devices and Solid-State Circuits (EDSSC), Hong Kong, China, 3–5 August 2016. [Google Scholar]

- Sanyal, A.; Ragab, K.; Chen, L.; Viswanathan, T.R.; Yan, S.; Sun, N. A hybrid SAR-VCO ΔΣ ADC with first-order noise shaping. In Proceedings of the IEEE 2014 Custom Integrated Circuits Conference, San Jose, CA, USA, 15–17 September 2014; pp. 1–4. [Google Scholar]

- Xie, Y.; Liang, Y.; Liu, M.; Liu, S.; Zhu, Z. A 10-Bit 5 MS/s VCO-SAR ADC in 0.18-μm CMOS. IEEE Trans. Circuits Syst. II Express Briefs 2019, 66, 26–30. [Google Scholar] [CrossRef]

- Ragab, K.; Sun, N. A 12-b ENOB 2.5-MHz BW VCO-Based 0-1 MASH ADC With Direct Digital Background Calibration. IEEE J. Solid-State Circuits 2017, 52, 433–447. [Google Scholar] [CrossRef]

- Gutierrez, E.; Hernandez, L.; Cardes, F. VCO-based sturdy MASH ADC architecture. Electron. Lett. 2017, 53, 14–16. [Google Scholar] [CrossRef]

- Sacco, E.; Vergauwen, J.; Gielen, G. A 16.1-bit Resolution 0.064-mm2 Compact Highly Digital Closed-Loop Single-VCO-Based 1-1 Sturdy-MASH Resistance-to-Digital Converter With High Robustness in 180-nm CMOS. IEEE J. Solid-State Circuits 2020, 55, 2456–2467. [Google Scholar] [CrossRef]

- Maghami, H.; Payandehnia, P.; Mirzaie, H.; Zanbaghi, R.; Zareie, H.; Goins, J.; Dey, S.; Mayaram, K.; Fiez, T.S. A Highly Linear OTA-Less 1-1 MASH VCO-Based ΔΣ ADC With an Efficient Phase Quantization Noise Extraction Technique. IEEE J. Solid-State Circuits 2020, 55, 706–718. [Google Scholar] [CrossRef]

- Wu, T.; Chen, M.S. A Noise-Shaped VCO-Based Nonuniform Sampling ADC With Phase-Domain Level Crossing. IEEE J. Solid-State Circuits 2019, 54, 623–635. [Google Scholar] [CrossRef]

- Gutierrez, E.; Perez, C.; Hernandez, L.; Cardes, F.; Petrescu, V.; Walter, S.; Gaier, U. A Pulse Frequency Modulation VCO-ADC in 40 nm. IEEE Trans. Circuits Syst. II Express Briefs 2019, 66, 51–55. [Google Scholar] [CrossRef]

- Perez, C.; Quintero, A.; Amaral, P.; Wiesbauer, A.; Hernandez, L. A 73dB-A Audio VCO-ADC based on a Maximum Length Sequence Generator in 130nm CMOS. IEEE Trans. Circuits Syst. II Express Briefs 2021. [Google Scholar] [CrossRef]

- Gutierrez, E.; Hernandez, L.; Cardes, F.; Rombouts, P. A Pulse Frequency Modulation Interpretation of VCOs Enabling VCO-ADC Architectures With Extended Noise Shaping. IEEE Trans. Circuits Syst. I Regul. Pap. 2018, 65, 444–457. [Google Scholar] [CrossRef]

- Taylor, G.; Galton, I. A Reconfigurable Mostly-Digital Delta-Sigma ADC With a Worst-Case FOM of 160 dB. IEEE J. Solid-State Circuits 2013, 48, 983–995. [Google Scholar] [CrossRef]

- Nguyen, V.; Schembari, F.; Staszewski, R.B. A 0.2-V 30-MS/s 11b-ENOB Open-Loop VCO-Based ADC in 28-nm CMOS. IEEE J. Solid-State Circuits Lett. 2018, 1, 190–193. [Google Scholar] [CrossRef]

- Ahmadi-Farsani, J.; Rosa, J.M.d. Bulk-Input VCO-Based Sigma-Delta ADCs with Enhanced Linearity in 28-nm FD-SOI CMOS. In Proceedings of the 2019 IEEE International Symposium on Circuits and Systems (ISCAS), Sapporo, Japan, 26–29 May 2019; pp. 1–5. [Google Scholar]

- Fishani, A.B.; Rombouts, P. Highly linear VCO for use in VCO-ADCs. Electron. Lett. 2016, 52, 268–270. [Google Scholar] [CrossRef] [Green Version]

- Unnikrishnan, V.; Vesterbacka, M. Time-Mode Analog-to-Digital Conversion Using Standard Cells. IEEE Trans. Circuits Syst. Regul. Pap. 2014, 61, 3348–3357. [Google Scholar] [CrossRef] [Green Version]

- Wulff, C.; Ytterdal, T. A Compiled 9-bit 20-MS/s 3.5-fJ/conv.step SAR ADC in 28-nm FDSOI for Bluetooth Low Energy Receivers. IEEE J. Solid-State Circuits 2017, 52, 1915–1926. [Google Scholar] [CrossRef]

- Weaver, S.; Hershberg, B.; Maghari, N.; Moon, U. Domino-Logic-Based ADC for Digital Synthesis. IEEE Trans. Circuits Syst. II Express Briefs 2011, 58, 744–747. [Google Scholar] [CrossRef]

- Ding, M.; Harpe, P.; Chen, G.; Busze, B.; Liu, Y.; Bachmann, C.; Philips, K.; van Roermund, A. A Hybrid Design Automation Tool for SAR ADCs in IoT. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2018, 26, 2853–2862. [Google Scholar] [CrossRef] [Green Version]

- Waters, A.; Moon, U.-K. A fully automated verilog-to-layout synthesized ADC demonstrating 56dB-SNDR with 2MHz-BW. In Proceedings of the 2015 IEEE Asian Solid-State Circuits Conference (A-SSCC), Xiamen, China, 9–11 November 2015; pp. 1–4. [Google Scholar]

- Aiello, O.; Crovetti, P.; Sharma, A.; Alioto, M. Fully-Synthesizable Current-Input ADCs for Ultra-Low Area and Minimal Design Effort. In Proceedings of the 2019 26th IEEE International Conference on Electronics, Circuits and Systems (ICECS), Genova, Italy, 27–29 November 2019; pp. 715–718. [Google Scholar]

- McConaghy, T.; Palmers, P.; Steyaert, M.; Gielen, G.G.E. Trustworthy Genetic Programming-Based Synthesis of Analog Circuit Topologies Using Hierarchical Domain-Specific Building Blocks. IEEE Trans. Evol. Comput. 2011, 15, 557–570. [Google Scholar] [CrossRef]

- Gielen, G.; Eeckelaert, T.; Martens, E.; McConaghy, T. Automated synthesis of complex analog circuits. In Proceedings of the 2007 18th European Conference on Circuit Theory and Design, Sevilla, Spain, 26–30 August 2007; pp. 20–23. [Google Scholar]

- Rutenbar, R.A.; Gielen, G.G.E.; Roychowdhury, J. Hierarchical Modeling, Optimization, and Synthesis for System-Level Analog and RF Designs. Proc. IEEE 2007, 95, 640–669. [Google Scholar] [CrossRef]

- der Plas, G.V.; Vandenbussche, J.; Gielen, G.G.E.; Sansen, W. A layout synthesis methodology for array-type analog blocks. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2002, 21, 645–661. [Google Scholar] [CrossRef]

- Rabaey, J.M. Digital Integrated Circuits: A Design Perspective; Prentice-Hall, Inc.: Upper Saddle River, NJ, USA, 1996. [Google Scholar]

- Wang, C.; Tsai, J.; Su, S.; Tsai, J.; Chen, J.; Lou, C. 20.6 An 80MHz-BW 31.9fJ/conv-step Filtering ΔΣ ADC with a Built-In DAC-Segmentation/ELD-Compensation 6b 960MS/s SAR-Quantizer in 28nm LP for 802.11ax Applications. In Proceedings of the 2019 IEEE International Solid- State Circuits Conference—(ISSCC), San Francisco, CA, USA, 17–21 February 2019; pp. 338–340. [Google Scholar]

- Borgmans, J.; Rombouts, P. Enhanced circuit for linear ring VCO-ADCs. Electron. Lett. 2019, 55, 583–585. [Google Scholar] [CrossRef] [Green Version]

- Tu, C.; Wang, Y.; Lin, T. A Low-Noise Area-Efficient Chopped VCO-Based CTDSM for Sensor Applications in 40-nm CMOS. IEEE J. Solid-State Circuits 2017, 52, 2523–2532. [Google Scholar] [CrossRef]

- Taylor, G. Mostly Digital ADCs for Highly-Scaled CMOS Processes. Ph.D. Thesis, University of California, Oakland, CA, USA, 2011. [Google Scholar]

| Parameter | [3] | [9] | [19] | [23] | [25] | [32] * | [36] | [37] * | [38] | [40] | This Work |

|---|---|---|---|---|---|---|---|---|---|---|---|

| Meas./Sim. | MR | MR | MR | MR | SR | MR | MR | MR | SR | MR | SR |

| Results | |||||||||||

| Supply [V] | 1.2 | 1 | 1.2 | 0.9 | 1 | 1 | 1.2 | 0.2 | 1 | 0.6 | 1.2 |

| Process [nm] | 90 | 28 | 130 | 40 | 65 | 65 | 65 | 28 | 28 | 65 | 65 |

| BW [MHz] | 105 | 50 | 20 | 40 | 5 | 200 | 37.5 | 0.061 | 10 | 25.6 | 50 |

| SNDR [dB] | 35.89 | 67 | 67 | 59.5 | 75.7 | 57 | 70 | 68 | 62 | 50.3 | 63 |

| THD [dBc] | – | −74.4 | −67.7 | −65.7 | −80.7 | −63.6 | −76 | −72.5 | – | −53.9 | −66.4 |

| INL [LSB] | −2/0.44 | – | – | – | – | – | – | – | – | −1.9/1.6 | −0.44/0.26 |

| ENOB | 5.67 | 10.85 | 10.84 | 9.59 | 12.3 | 9.18 | 11.34 | 11 | 10 | 8.06 | 10.17 |

| Diff. Input Range [mV] | 280 | 2000 | 180 | 715 | 1800 | 566 | 800 | 355 | 800 | 600 | 800 |

| Power [mW] | 34.8 | 8 | 40 | 2.57 | 0.51 | 35.4 | 39 | 0.0065 | 0.23 | 3.3 | 3.69 |

| Area [mm] | 0.18 | 0.1 | 0.42 | 0.017 | – | 0.1557 | 0.11 | 0.07 | – | 0.026 | – |

| FoM [dB] | 130.7 | 165 | 154 | 160.9 | 173.9 | 154.5 | 159.8 | 167.7 | 166.4 | 149.2 | 164.3 |

| FoM [fJ/c-s] | 3256 | 43.2 | 500 | 42 | 14.9 | 153 | 201.2 | 26 | 14 | 235 | 32 |

| Linearization | Inv. | Digital | Two-step | Digital | Digital | Digital | Resist. | Bulk- | Digital | Multiple | |

| technique | Gauss. | calib. | loop | VCO-ADC | f-calib. | f-calib. | b-calib. | netw. | driven | f-calib | transc. |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Alvero-Gonzalez, L.M.; Medina, V.; Kampus, V.; Paton, S.; Hernandez, L.; Gutierrez, E. Ring-Oscillator with Multiple Transconductors for Linear Analog-to-Digital Conversion. Electronics 2021, 10, 1408. https://doi.org/10.3390/electronics10121408

Alvero-Gonzalez LM, Medina V, Kampus V, Paton S, Hernandez L, Gutierrez E. Ring-Oscillator with Multiple Transconductors for Linear Analog-to-Digital Conversion. Electronics. 2021; 10(12):1408. https://doi.org/10.3390/electronics10121408

Chicago/Turabian StyleAlvero-Gonzalez, Leidy Mabel, Victor Medina, Vahur Kampus, Susana Paton, Luis Hernandez, and Eric Gutierrez. 2021. "Ring-Oscillator with Multiple Transconductors for Linear Analog-to-Digital Conversion" Electronics 10, no. 12: 1408. https://doi.org/10.3390/electronics10121408