Noise Efficient Integrated Amplifier Designs for Biomedical Applications

Abstract

:1. Introduction

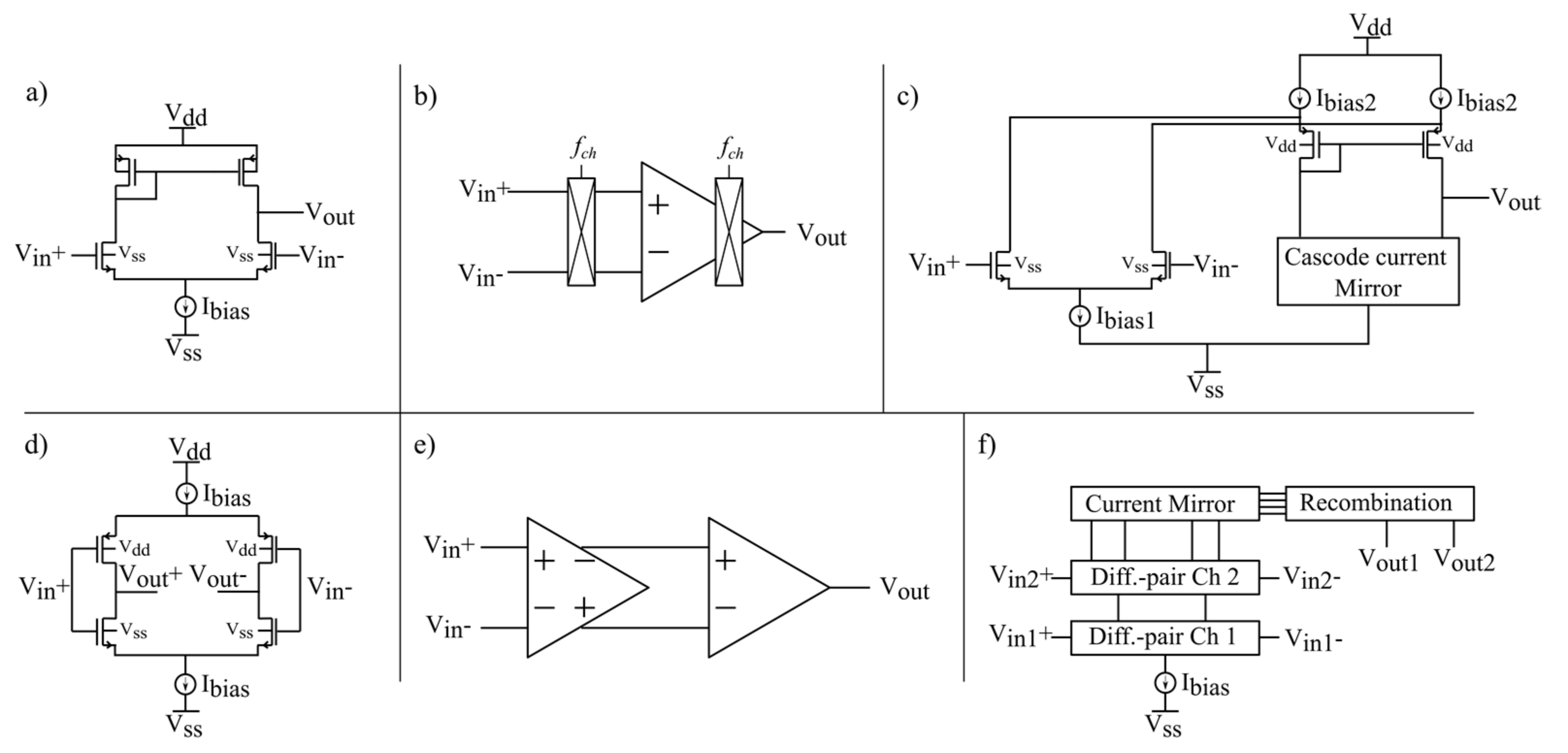

2. Amplifier Topologies

- Conventional OTA

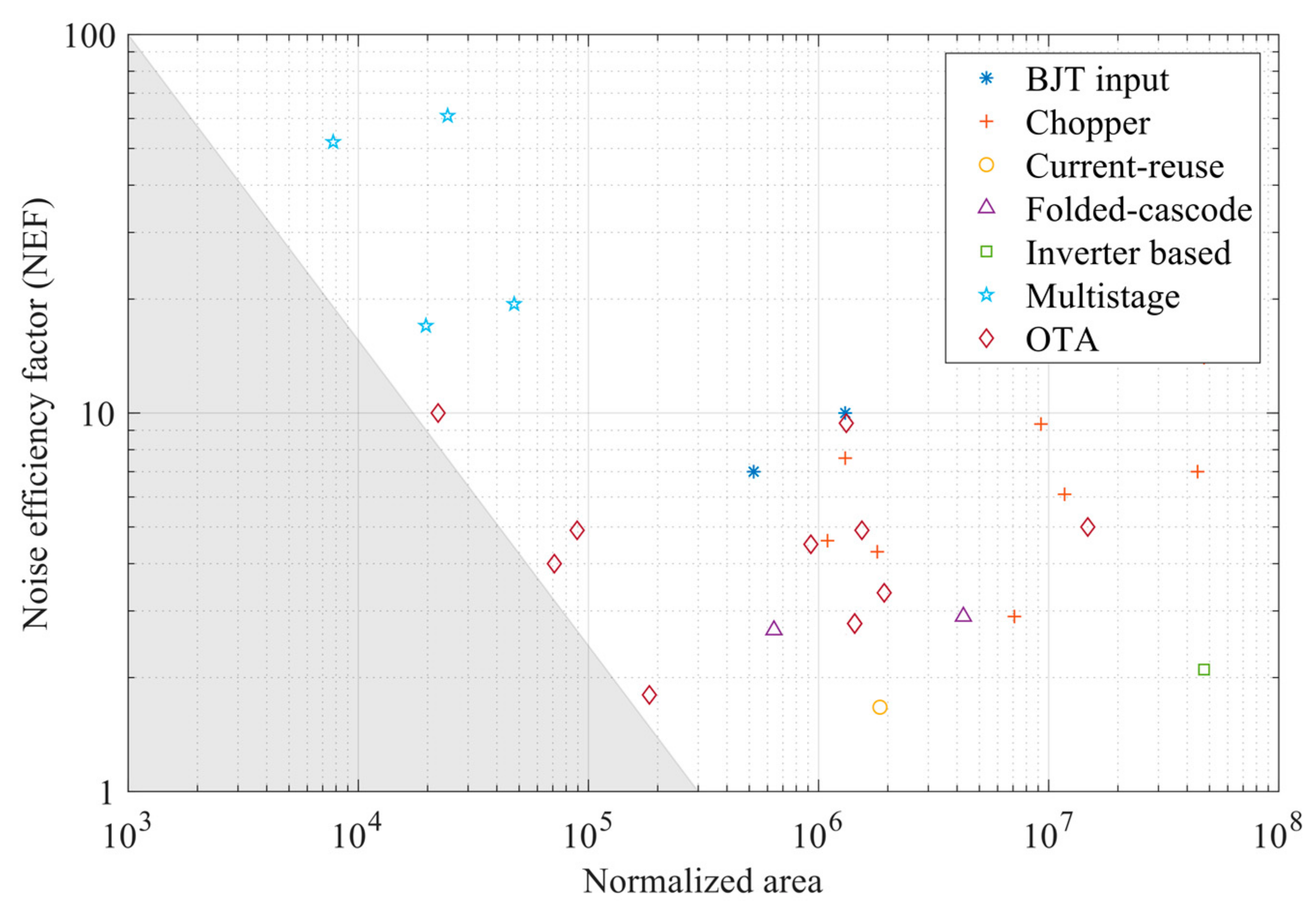

- B.

- Chopper input

- C.

- Folded-cascode

- D.

- Inverter-based input

- E.

- Multistage amplifier

- F.

- Current reuse

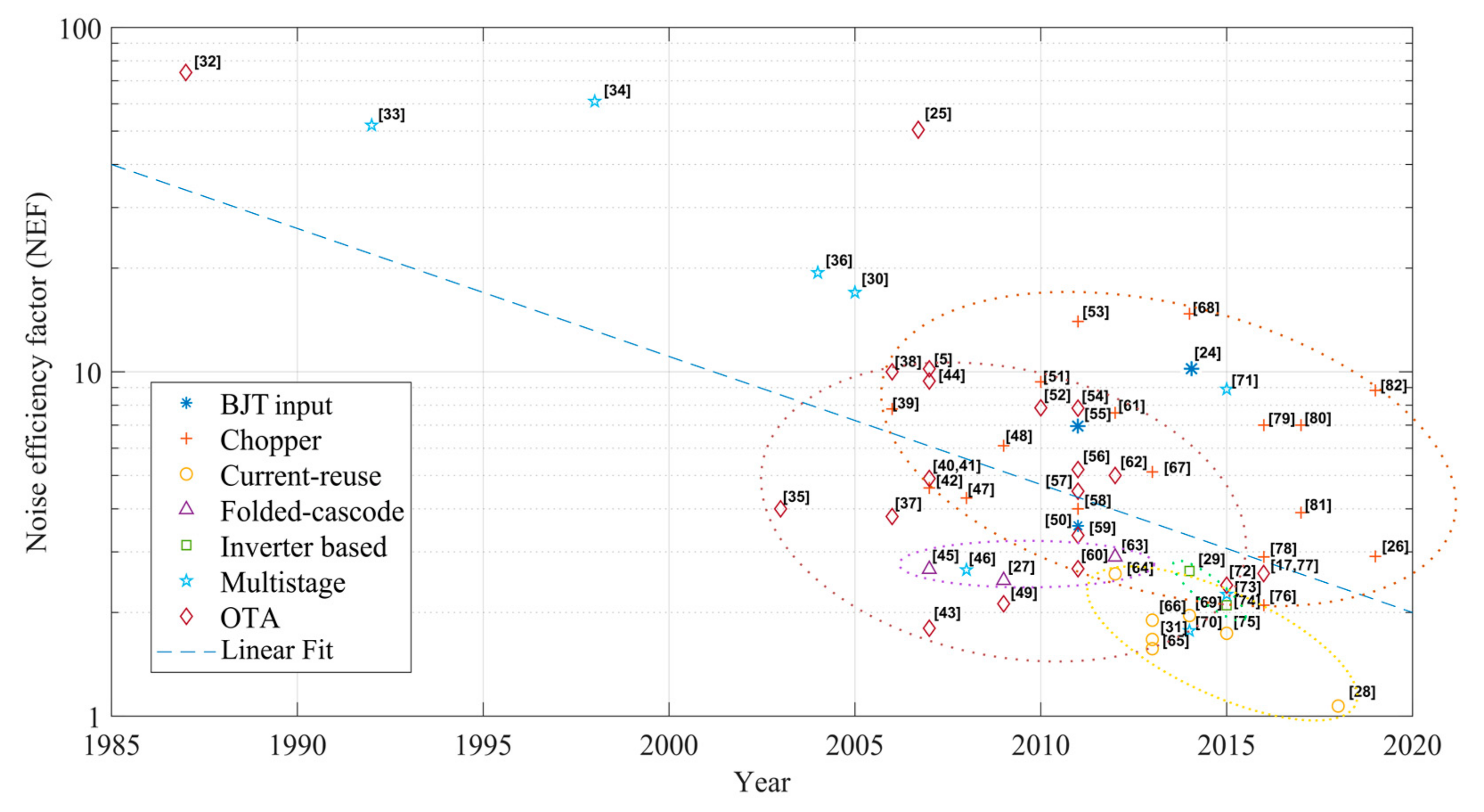

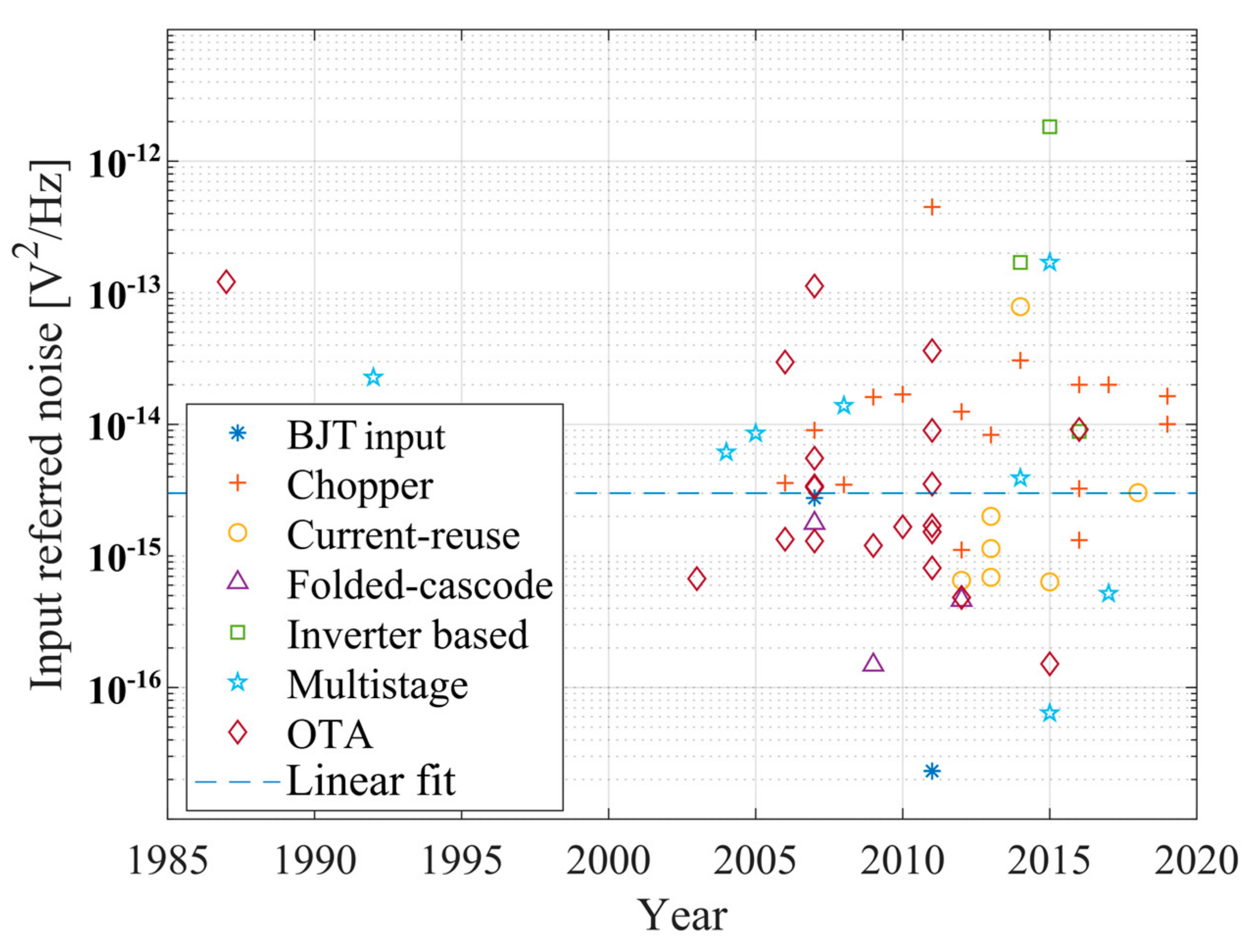

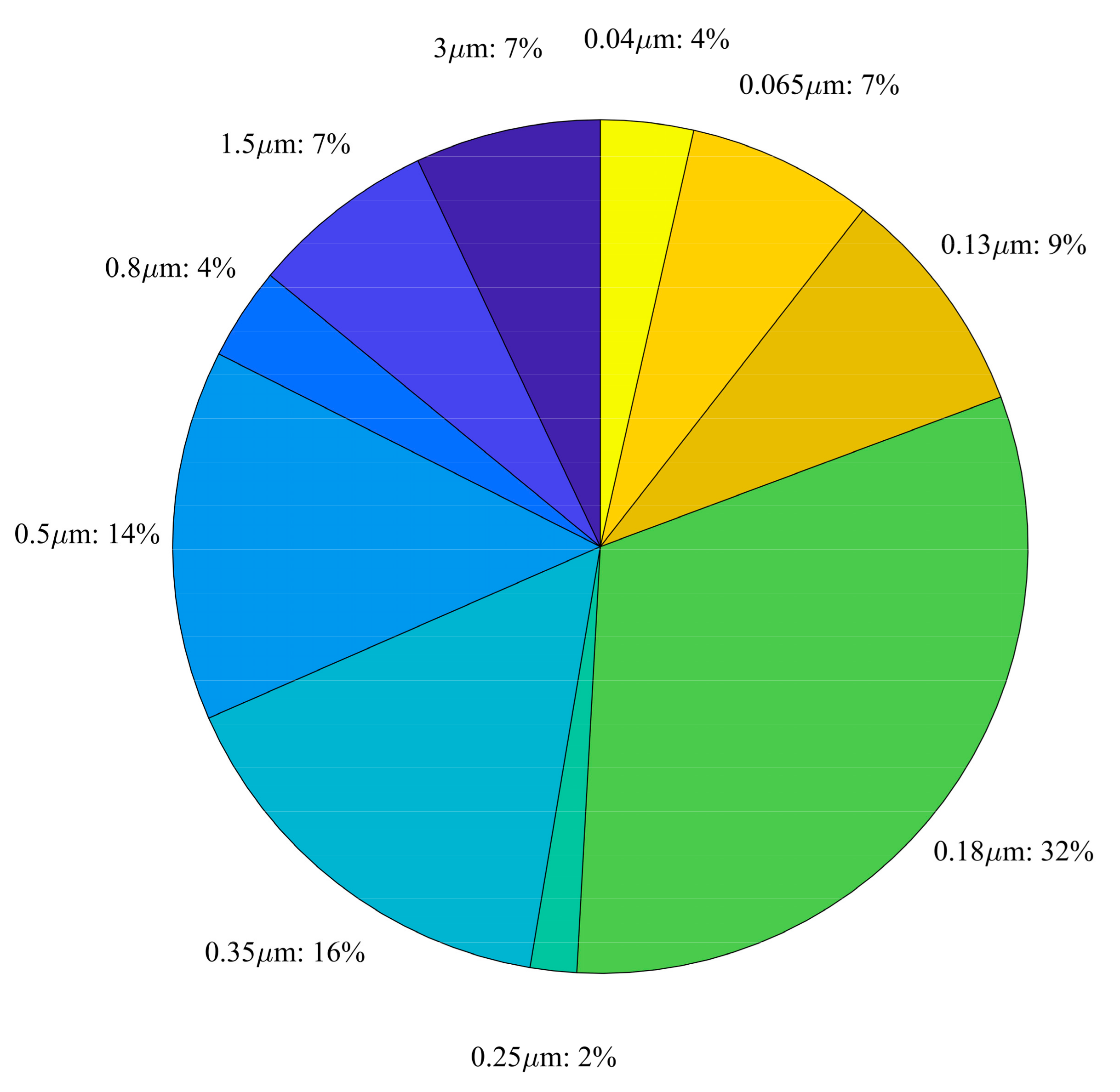

3. Noise vs. Power Trade-Off

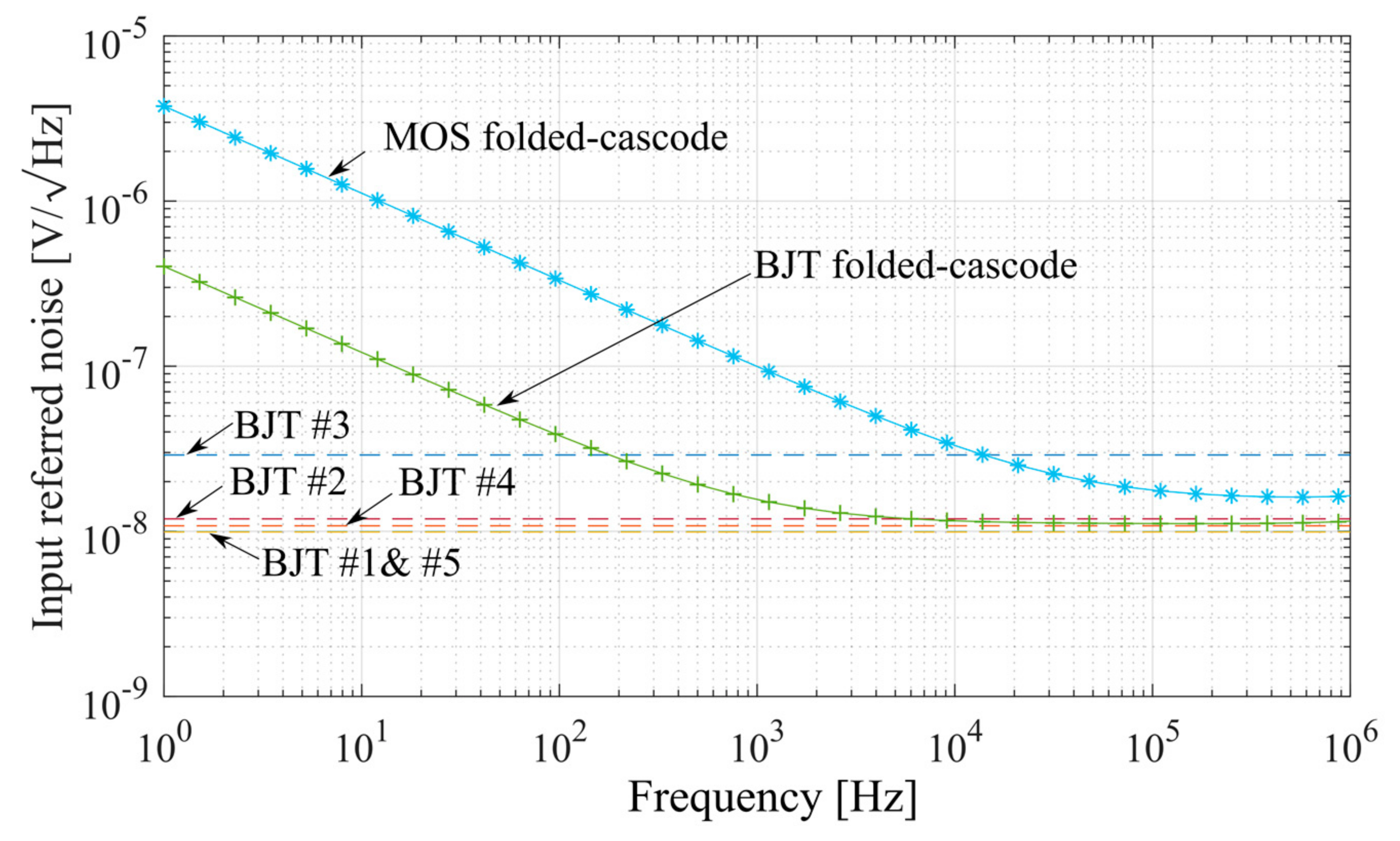

4. Lateral Bipolar Input Devices

5. Discussion

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Thomas, S.J.; Harrison, R.R.; Leonardo, A.; Reynolds, M.S. A battery-free multichannel digital neural/EMG telemetry system for flying insects. IEEE Trans. Biomed. Circuits Syst. 2012, 6, 424–436. [Google Scholar] [CrossRef] [PubMed]

- Wise, K.D.; Angell, J.B.; Starr, A. An Integrated-Circuit Approach to Extracellular Microelectrodes. IEEE Trans. Biomed. Eng. 1970, 17, 238–247. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Hoogerwerf, A.; Wise, K. A three-dimensional microelectrode array for chronic neural recording. IEEE Trans. Biomed. Eng. 1994, 41, 1136–1146. [Google Scholar] [CrossRef] [PubMed]

- Scherberger, H.; Jarvis, M.R.; Andersen, R.A. Cortical Local Field Potential Encodes Movement Intentions in the Posterior Parietal Cortex. Neuron 2005, 46, 347–354. [Google Scholar] [CrossRef] [Green Version]

- Harrison, R.R.; Watkins, P.T.; Kier, R.J.; Lovejoy, R.O.; Black, D.J.; Greger, B.; Solzbacher, F. A low-power integrated circuit for a wireless 100-electrode neural recording system. IEEE J. Solid-State Circuits 2007, 42, 123–133. [Google Scholar] [CrossRef]

- Lopez, C.M.; Mitra, S.; Putzeys, J.; Raducanu, B.; Ballini, M.; Andrei, A.; Severi, S.; Welkenhuysen, M.; Van Hoof, C.; Musa, S.; et al. 22.7 A 966-electrode neural probe with 384 configurable channels in 0.13 µm SOI CMOS. In Proceedings of the 2016 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 31 January–4 February 2016; pp. 392–393. [Google Scholar]

- Benabid, A.L.; Costecalde, T.; Eliseyev, A.; Charvet, G.; Verney, A.; Karakas, S.; Foerster, M.; Lambert, A.; Morinière, B.; Abroug, N.; et al. An exoskeleton controlled by an epidural wireless brain–machine interface in a tetraplegic patient: A proof-of-concept demonstration. Lancet Neurol. 2019, 18, 1112–1122. [Google Scholar] [CrossRef]

- Willett, F.R.; Avansino, D.T.; Hochberg, L.R.; Henderson, J.M.; Shenoy, K.V. High-performance brain-to-text communication via handwriting. Nat. Cell Biol. 2021, 593, 249–254. [Google Scholar] [CrossRef]

- Simeral, J.D.; Hosman, T.; Saab, J.; Flesher, S.N.; Vilela, M.; Franco, B.; Kelemen, J.N.; Brandman, D.M.; Ciancibello, J.G.; Rezaii, P.G.; et al. Home Use of a Percutaneous Wireless Intracortical Brain-Computer Interface by Individuals with Tetraplegia. IEEE Trans. Biomed. Eng. 2021, 68, 2313–2325. [Google Scholar] [CrossRef]

- Hugle, M.; Heller, S.; Watter, M.; Blum, M.; Manzouri, F.; Dumpelmann, M.; Schulze-Bonhage, A.; Woias, P.; Boedecker, J. Early Seizure Detection with an Energy-Efficient Convolutional Neural Network on an Implantable Microcontroller. In Proceedings of the 2018 International Joint Conference on Neural Networks (IJCNN), Rio de Janeiro, Brazil, 8–13 July 2018; pp. 1–7. [Google Scholar] [CrossRef] [Green Version]

- Manzouri, F.; Khurana, L.; Kravalis, K.; Stieglitz, T.; Schulze-Bonhage, A.; Dumpelmann, M. An Optimized EEG-Based Seizure Detection Algorithm for Implantable Devices. In Proceedings of the 2021 10th International IEEE/EMBS Conference on Neural Engineering (NER), Virtual, 4–6 May 2021; pp. 995–998. [Google Scholar]

- Bailey, J.; Haddad, W. Drug dosing control in clinical pharmacology. IEEE Control. Syst. 2005, 25, 35–51. [Google Scholar] [CrossRef]

- Hosseinzadeh, M.; Van Heusden, K.; Dumont, G.A.; Garone, E. An Explicit Reference Governor Scheme for Closed-Loop Anesthesia. In Proceedings of the 2019 18th European Control Conference (ECC), Naples, Italy, 25–28 June 2019; pp. 1294–1299. [Google Scholar] [CrossRef]

- Gernert, M.; Feja, M. Bypassing the Blood–Brain Barrier: Direct Intracranial Drug Delivery in Epilepsies. Pharmaceutics 2020, 12, 1134. [Google Scholar] [CrossRef]

- Jun, J.J.; Steinmetz, N.A.; Siegle, J.H.; Denman, D.J.; Bauza, M.; Barbarits, B.; Lee, A.K.; Anastassiou, C.A.; Andrei, A.; Aydin, C.; et al. Fully integrated silicon probes for high-density recording of neural activity. Nat. Cell Biol. 2017, 551, 232–236. [Google Scholar] [CrossRef] [Green Version]

- Shobe, J.L.; Claar, L.D.; Parhami, S.; Bakhurin, K.I.; Masmanidis, S.C. Brain activity mapping at multiple scales with silicon microprobes containing 1024 electrodes. J. Neurophysiol. 2015, 114, 2043–2052. [Google Scholar] [CrossRef] [Green Version]

- Bahr, A. Aufnahme von Hirnsignalen Mit Extrem Miniaturisierten Elektronischen Systemen zur Untersuchung von Lokalen Neuronalen Vernetzungen; Logos Verlag: Berlin, Germany, 2017. [Google Scholar]

- Marguet, S.L.; Le-Schulte, V.T.Q.; Merseburg, A.; Neu, A.; Eichler, R.; Jakovcevski, I.; Ivanov, A.; Hanganu-Opatz, I.L.; Bernard, C.; Morellini, F.; et al. Treatment during a vulnerable developmental period rescues a genetic epilepsy. Nat. Med. 2015, 21, 1436–1444. [Google Scholar] [CrossRef] [PubMed]

- Bear, M.F.; Connors, B.W.; Paradiso, M.A. Neuroscience: Exploring the Brain, 4th ed.; Wolters Kluwer: Philadelphia, PA, USA, 2016. [Google Scholar]

- Harrison, R.R. A Versatile Integrated Circuit for the Acquisition of Biopotentials. In Proceedings of the 2007 IEEE Custom Integrated Circuits Conference, San Jose, CA, USA, 16–19 September 2007. [Google Scholar] [CrossRef]

- Ng, K.A.; Greenwald, E.; Xu, Y.P.; Thakor, N.V. Implantable neurotechnologies: A review of integrated circuit neural amplifiers. Med. Biol. Eng. Comput. 2016, 54, 45–62. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Webster, J.G. Medical Instrumentation: Application and Design; Wiley: New York, NY, USA, 1998. [Google Scholar]

- Rieger, R.; Taylor, J.T. Design strategies for multi-channel low-noise recording systems. Analog. Integr. Circuits Signal Process. 2009, 58, 123–133. [Google Scholar] [CrossRef]

- Teng, S.-L.; Rieger, R.; Lin, Y.-B. Programmable ExG Biopotential Front-End IC for Wearable Applications. IEEE Trans. Biomed. Circuits Syst. 2013, 8, 543–551. [Google Scholar] [CrossRef]

- Lim, E.C.M.; Zou, X.; Zheng, Y.; Tan, J. Design of Low-Power Low-Voltage Biomedical Amplifier for Electrocardiogram Signal Recording. In Proceedings of the 2007 IEEE Biomedical Circuits and Systems Conference, Montreal, QC, Canada, 27–30 November 2007; pp. 191–194. [Google Scholar]

- Lee, C.-J.; Song, J.-I. A Chopper-Stabilized Amplifier with a Tunable Bandwidth for EEG Acquisition Applications. IEEE Access 2019, 7, 73165–73171. [Google Scholar] [CrossRef]

- Rai, S.; Holleman, J.; Pandey, J.N.; Zhang, F.; Otis, B. A 500μW neural tag with 2μVrms AFE and frequency-multiplying MICS/ISM FSK transmitter. In Proceedings of the 2009 IEEE International Solid-State Circuits Conference–Digest of Technical Papers, San Francisco, CA, USA, 8–12 February 2009; pp. 212–213. [Google Scholar]

- Shen, L.; Lu, N.; Sun, N. A 1-V 0.25- μw Inverter Stacking Amplifier with 1.07 Noise Efficiency Factor. IEEE J. Solid-State Circuits 2018, 53, 896–905. [Google Scholar] [CrossRef]

- Jeon, D.; Chen, Y.-P.; Lee, Y.; Kim, Y.; Foo, Z.; Kruger, G.; Oral, H.; Berenfeld, O.; Zhang, Z.; Blaauw, D.; et al. 24.3 An implantable 64nW ECG-monitoring mixed-signal SoC for arrhythmia diagnosis. In Proceedings of the 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 9–13 February 2014; Volume 57, pp. 416–417. [Google Scholar] [CrossRef]

- OlssonIII, R.; Buhl, D.; Sirota, A.; Buzsáki, G.; Wise, K.; Olsson, R.H. Band-Tunable and Multiplexed Integrated Circuits for Simultaneous Recording and Stimulation with Microelectrode Arrays. IEEE Trans. Biomed. Eng. 2005, 52, 1303–1311. [Google Scholar] [CrossRef]

- Johnson, B.; Molnar, A. An Orthogonal Current-Reuse Amplifier for Multi-Channel Sensing. IEEE J. Solid-State Circuits 2013, 48, 1487–1496. [Google Scholar] [CrossRef]

- Steyaert, M.S.J.; Sansen, W.M.C. A micropower low-noise monolithic instrumentation amplifier for medical purposes. IEEE J. Solid-State Circuits 1987, 22, 1163–1168. [Google Scholar] [CrossRef]

- Kensall, J.J.; Wise, D. An Implantable CMOS Circuit Interface for Multiplexed Microelectrode Recording Arrays. IEEE J. Solid-State Circuits 1992, 27, 433–443. [Google Scholar]

- Akin, T.; Najafi, K.; Bradley, R. A wireless implantable multichannel digital neural recording system for a micromachined sieve electrode. IEEE J. Solid-State Circuits 1998, 33, 109–118. [Google Scholar] [CrossRef] [Green Version]

- Harrison, R.R.; Charles, C. A low-power low-noise cmos for amplifier neural recording applications. IEEE J. Solid-State Circuits 2003, 38, 958–965. [Google Scholar] [CrossRef]

- Mohseni, P.; Najafi, K. A Fully Integrated Neural Recording Amplifier with DC Input Stabilization. IEEE Trans. Biomed. Eng. 2004, 51, 832–837. [Google Scholar] [CrossRef]

- Wu, H.; Xu, Y.P. A 1V 2.3 µW Biomedical Signal Acquisition IC. In Proceedings of the 2006 IEEE International Solid State Circuits Conference–Digest of Technical Papers, San Francisco, CA, USA, 6–9 February 2006; pp. 119–128. [Google Scholar]

- Parthasarathy, J.; Erdman, A.G.; Redish, A.D.; Ziaie, B. An integrated CMOS bio-potential amplifier with a feed-forward DC cancellation topology. In Proceedings of the 2006 International Conference of the IEEE Engineering in Medicine and Biology Society, New York, NY, USA, 30 August–3 September 2006; pp. 2974–2977. [Google Scholar]

- Yazicloglu, R.F.; Merken, P.; Puers, R.; van Hoof, C. A 60μW 60 nV/√Hz readout front-end for portable biopotential acquisition systems. In Proceedings of the 2006 IEEE International Solid State Circuits Conference–Digest of Technical Papers, San Francisco, CA, USA, 6–9 February 2006; pp. 109–118. [Google Scholar]

- Yin, M.; Ghovanloo, M. A Low-Noise Preamplifier with Adjustable Gain and Bandwidth for Biopotential Recording Applications. In Proceedings of the 2007 IEEE International Symposium on Circuits and Systems, New Orleans, LA, USA, 27–30 May 2007; pp. 321–324. [Google Scholar]

- Gosselin, B.; Sawan, M.; Chapman, C.A. A Low-Power Integrated Bioamplifier With Active Low-Frequency Suppression. IEEE Trans. Biomed. Circuits Syst. 2007, 1, 184–192. [Google Scholar] [CrossRef]

- Denison, T.; Consoer, K.; Santa, W.; Avestruz, A.T.; Cooley, J.; Kelly, A. A 2 μw 100nV/rtHz Chopper-Stabilized Instrumentation Amplifier for Chronic Measurement of Neural Field Potentials. IEEE J. Solid-State Circuits 2007, 42, 2934–2945. [Google Scholar] [CrossRef]

- Holleman, J.; Otis, B. A Sub-Microwatt Low-Noise Amplifier for Neural Recording. In Proceedings of the 2007 29th Annual International Conference of the IEEE Engineering in Medicine and Biology Society, Lyon, France, 22–26 August 2007; pp. 3930–3933. [Google Scholar] [CrossRef]

- Cheng, C.L. A 70 dB gain low-power band-pass amplifier for bio-signals sensing applications. In Proceedings of the 2007 IEEE International Symposium on Circuits and Systems, New Orleans, LA, USA, 27–30 May 2007; pp. 577–580. [Google Scholar]

- Wattanapanitch, W.; Fee, M.; Sarpeshkar, R. An Energy-Efficient Micropower Neural Recording Amplifier. IEEE Trans. Biomed. Circuits Syst. 2007, 1, 136–147. [Google Scholar] [CrossRef]

- Xu, X.; Zou, X.; Yao, L.; Lian, Y. A 1-V 450-nW fully integrated biomedical sensor interface system. In Proceedings of the 2008 IEEE Symposium on VLSI Circuits, Honolulu, HI, USA, 18–20 June 2008; pp. 78–79. [Google Scholar] [CrossRef]

- Yazicioglu, R.F.; Merken, P.; Puers, R.; van Hoof, C. A 200μW eight-channel EEG acquisition ASIC for ambulatory EEG systems. IEEE J. Solid-State Circuits 2008, 43, 3025–3038. [Google Scholar] [CrossRef]

- Kao, S.-T.; Lu, H.; Su, C. A 1.5 V 7.5 uW programmable gain amplifier for multiple biomedical signal acquisition. In Proceedings of the 2009 IEEE Biomedical Circuits and Systems Conference, Beijing, China, 26–28 November 2009; pp. 73–76. [Google Scholar] [CrossRef]

- Chae, M.S.; Yang, Z.; Yuce, M.R.; Hoang, L.; Liu, W.; Member, S. A 128 Channel 6mW Wireless Neural Recording IC with Spike Feature Extraction. IEEE Int. Solid-State Circuits 2009, 17, 312–321. [Google Scholar]

- Taylor, J.; Rieger, R. A low noise front-end for multiplexed ENG recording using CMOS technology. In Proceedings of the 2008 15th IEEE International Conference on Electronics, Circuits and Systems, Saint Julian’s, Malta, 31 August–3 September 2008; pp. 754–757. [Google Scholar]

- Verma, N.; Shoeb, A.H.; Bohorquez, J.L.; Dawson, J.L.; Guttag, J.V.; Chandrakasan, A.P. A Micro-Power EEG Acquisition SoC With Integrated Feature Extraction Processor for a Chronic Seizure Detection System. IEEE J. Solid-State Circuits 2010, 45, 804–816. [Google Scholar] [CrossRef]

- Lee, S.B.; Lee, H.-M.; Kiani, M.; Jow, U.-M.; Ghovanloo, M. An Inductively Powered Scalable 32-Channel Wireless Neural Recording System-on-a-Chip for Neuroscience Applications. IEEE Trans. Biomed. Circuits Syst. 2010, 4, 360–371. [Google Scholar] [CrossRef] [Green Version]

- Fan, Q.; Sebastiano, F.; Huijsing, J.H.; Makinwa, K.A.A. A 1.8μW 60 nV/√ Hz capacitively-coupled chopper instrumentation amplifier in 65 nm CMOS for wireless sensor nodes. IEEE J. Solid-State Circuits 2011, 46, 1534–1543. [Google Scholar] [CrossRef]

- Yin, M.; Ghovanloo, M. A low-noise clockless simultaneous 32-channel wireless neural recording system with adjustable resolution. Analog. Integr. Circuits Signal Process. 2010, 66, 417–431. [Google Scholar] [CrossRef]

- Rieger, R. Variable-Gain, Low-Noise Amplification for Sampling Front Ends. IEEE Trans. Biomed. Circuits Syst. 2011, 5, 253–261. [Google Scholar] [CrossRef]

- Chang, S.I.; Alashmouny, K.; McCormick, M.; Chen, Y.C.; Yoon, E. BioBolt: A minimally-invasive neural interface for wireless epidural recording by intra-skin communication. In Proceedings of the 2011 Symposium on VLSI Circuits–Digest of Technical Papers, Kyoto, Japan, 15–17 June 2011; pp. 146–147. [Google Scholar]

- Wattanapanitch, W.; Sarpeshkar, R. A Low-Power 32-Channel Digitally Programmable Neural Recording Integrated Circuit. IEEE Trans. Biomed. Circuits Syst. 2011, 5, 592–602. [Google Scholar] [CrossRef]

- RYazicioglu, F.; Kim, S.; Torfs, T.; Kim, H.; van Hoof, C. A 30 μw analog signal processor ASIC for portable biopotential signal monitoring. IEEE J. Solid-State Circuits 2011, 46, 209–223. [Google Scholar] [CrossRef]

- Majidzadeh, V.; Schmid, A.; Leblebici, Y. Energy Efficient Low-Noise Neural Recording Amplifier with Enhanced Noise Efficiency Factor. IEEE Trans. Biomed. Circuits Syst. 2011, 5, 262–271. [Google Scholar] [CrossRef]

- Azin, M.; Guggenmos, D.J.; Barbay, S.; Nudo, R.J.; Mohseni, P. A Battery-Powered Activity-Dependent Intracortical Microstimulation IC for Brain-Machine-Brain Interface. IEEE J. Solid-State Circuits 2011, 46, 731–745. [Google Scholar] [CrossRef]

- Guo, J.; Yuan, G.J.; Huang, J.; Law, J.K.-Y.; Yeung, C.-K.; Chan, M. 32.9 nV/rt Hz -60.6 dB THD dual-band micro-electrode array signal acquisition IC. IEEE J. Solid-State Circuits 2012, 47, 1209–1220. [Google Scholar] [CrossRef]

- Gao, H.; Walker, R.M.; Nuyujukian, P.; Makinwa, K.A.; Shenoy, K.V.; Murmann, B.; Meng, T.H. HermesE: A 96-channel full data rate direct neural interface in 0.13 μm CMOS. IEEE J. Solid-State Circuits 2012, 47, 1043–1055. [Google Scholar] [CrossRef]

- Zhang, F.; Holleman, J.; Otis, B.P. Design of Ultra-Low Power Biopotential Amplifiers for Biosignal Acquisition Applications. IEEE Trans. Biomed. Circuits Syst. 2012, 6, 344–355. [Google Scholar] [CrossRef]

- Liu, L.; Zou, X.; Goh, W.L.; Ramamoorthy, R.; Dawe, G.; Je, M. 800 nW 43 nV/√Hz neural recording amplifier with enhanced noise efficiency factor. Electron. Lett. 2012, 48, 479–480. [Google Scholar] [CrossRef]

- Han, D.; Zheng, Y.; Rajkumar, R.; Dawe, G.; Je, M. A 0.45 V 100-channel neural-recording IC with sub-μW/channel consumption in 0.18μm CMOS. In Proceedings of the 2013 IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 17–21 February 2013; Volume 56, pp. 290–291. [Google Scholar]

- Zou, X.; Liu, L.; Cheong, J.H.; Yao, L.; Li, P.; Cheng, M.-Y.; Goh, W.L.; Rajkumar, R.; Dawe, G.; Cheng, K.-W.; et al. A 100-Channel 1-mW Implantable Neural Recording IC. IEEE Trans. Circuits Syst. I Regul. Pap. 2013, 60, 2584–2596. [Google Scholar] [CrossRef]

- Yoo, J.; Yan, L.; El-Damak, D.; Altaf, M.A.B.; Shoeb, A.H.; Chandrakasan, A.P. An 8-channel scalable EEG acquisition SoC with patient-specific seizure classification and recording processor. IEEE J. Solid-State Circuits 2013, 48, 214–228. [Google Scholar] [CrossRef]

- Xu, J.; Mitra, S.; Matsumoto, A.; Patki, S.; Van Hoof, C.; Makinwa, K.A.A.; Yazicioglu, R.F. A Wearable 8-Channel Active-Electrode EEG/ETI Acquisition System for Body Area Networks. IEEE J. Solid-State Circuits 2014, 49, 2005–2016. [Google Scholar] [CrossRef] [Green Version]

- Wang, T.-Y.; Lai, M.-R.; Twigg, C.M.; Peng, S.-Y. A Fully Reconfigurable Low-Noise Biopotential Sensing Amplifier With 1.96 Noise Efficiency Factor. IEEE Trans. Biomed. Circuits Syst. 2014, 8, 411–422. [Google Scholar] [CrossRef]

- Chen, W.-M.; Chiueh, H.; Chen, T.-J.; Ho, C.-L.; Jeng, C.; Ker, M.-D.; Lin, C.-Y.; Huang, Y.-C.; Chou, C.-W.; Fan, T.-Y.; et al. A Fully Integrated 8-Channel Closed-Loop Neural-Prosthetic CMOS SoC for Real-Time Epileptic Seizure Control. IEEE J. Solid-State Circuits 2013, 49, 232–247. [Google Scholar] [CrossRef]

- Cota, O.F.; Plachta, D.; Stieglitz, T.; Manoli, Y.; Kuhl, M. In-vivo characterization of a 0.8–3 μvRMS input-noise versatile CMOS pre-amplifier. In Proceedings of the 2015 7th International IEEE/EMBS Conference on Neural Engineering (NER), Montpellier, France, 22–24 April 2015; pp. 458–461. [Google Scholar]

- Nair, V.V.; Youn, J.H.; Choi, J.R.; Vijayakumaran, N.V. An integrated chip coil sensor and instrumentation amplifier for bio-magnetic signal acquisition. In Proceedings of the 2015 Transducers–2015 18th International Conference on Solid-State Sensors, Actuators and Microsystems (TRANSDUCERS), Anchorage, AK, USA, 21–25 June 2015; pp. 1581–1584. [Google Scholar] [CrossRef]

- Chen, Y.-P.; Jeon, D.; Lee, Y.; Kim, Y.; Foo, Z.; Lee, I.; Langhals, N.B.; Kruger, G.; Oral, H.; Berenfeld, O.; et al. An Injectable 64 nW ECG Mixed-Signal SoC in 65 nm for Arrhythmia Monitoring. IEEE J. Solid-State Circuits 2015, 50, 375–390. [Google Scholar] [CrossRef]

- Harpe, P.; Gao, H.; van Dommele, R.; Cantatore, E.; van Roermund, A. A 3 nW signal-acquisition IC integrating an amplifier with 2.1 NEF and a 1.5 fJ/conv-step ADC. In Proceedings of the 2015 IEEE International Solid-State Circuits Conference–(ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 22–26 February 2015; Volume 58, pp. 382–383. [Google Scholar]

- Song, S.S.; Rooijakkers, M.M.; Harpe, P.P.; Rabotti, C.C.; Mischi, M.M.; Van Roermund, A.H.M.; Cantatore, E.E. A Low-Voltage Chopper-Stabilized Amplifier for Fetal ECG Monitoring With a 1.41 Power Efficiency Factor. IEEE Trans. Biomed. Circuits Syst. 2015, 9, 237–247. [Google Scholar] [CrossRef] [Green Version]

- Yaul, F.M.; Chandrakasan, A.P. A sub-µW 36 nV/vHz chopper amplifier for sensors using a noise-efficient inverter-based 0.2 V-supply input stage. In Proceedings of the 2016 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 31 January–4 February 2016; Volume 59, pp. 94–95. [Google Scholar]

- Bahr, A.; Abu Saleh, L.; Hinsch, R.; Schroeder, D.; Isbrandt, D.; Krautschneider, W.H. Small area, low power neural recording integrated circuit in 130 nm CMOS technology for small mammalians. In Proceedings of the 2016 28th International Conference on Microelectronics (ICM), Giza, Egypt, 17–20 December 2016; pp. 349–352. [Google Scholar] [CrossRef]

- Wu, J.; Law, M.K.; Mak, P.I.; Martins, R.P. A 2-μW 45-nV/√Hz Readout Front End with Multiple-Chopping Active-High-Pass Ripple Reduction Loop and Pseudofeedback DC Servo Loop. IEEE Trans. Circuits Syst. II Express Briefs 2016, 63, 351–355. [Google Scholar] [CrossRef]

- Chandrakumar, H.; Markovic, D. A 2 µW 40 mVpp linear-input-range chopper- stabilized bio-signal amplifier with boosted input impedance of 300 MO and electrode-offset filtering. In Proceedings of the 2016 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 31 January–4 February 2016; Volume 59, pp. 96–97. [Google Scholar]

- Chandrakumar, H.; Markovic, D. A High Dynamic-Range Neural Recording Chopper Amplifier for Simultaneous Neural Recording and Stimulation. IEEE J. Solid-State Circuits 2017, 52, 645–656. [Google Scholar] [CrossRef]

- Zheng, J.; Ki, W.-H.; Hu, L.; Tsui, C.-Y. Chopper Capacitively Coupled Instrumentation Amplifier Capable of Handling Large Electrode Offset for Biopotential Recordings. IEEE Trans. Circuits Syst. II Express Briefs 2017, 64, 1392–1396. [Google Scholar] [CrossRef]

- Yang, Z.; Wang, J. A wearable wireless bio-medical front-end circuit for monitoring electrophysiological signals. In Proceedings of the BIBE 2019, the Third International Conference on Biological Information and Biomedical Engineering, Hangzhou, China, 20–22 June 2019; pp. 1–5. [Google Scholar]

- Kaplon, J.; Dabrowski, W. Fast CMOS binary front-end for silicon strip detectors at LHC experiments. In Proceedings of the IEEE Symposium Conference Record Nuclear Science 2004, Rome, Italy, 16–22 October 2004; Volume 1, pp. 34–38. [Google Scholar]

- Ratti, L.; Gaioni, L.; Manghisoni, M.; Re, V.; Riceputi, E.; Traversi, G. 65-nm CMOS Front-End Channel for Pixel Readout in the HL-LHC Radiation Environment. IEEE Trans. Nucl. Sci. 2017, 64, 2922–2932. [Google Scholar] [CrossRef]

- Intan Technologies. RHD2000 Series Digital Electrophysiology Interface Chips. RHD2216 Datasheet, Sept. 2013 [Revised Dec. 2020]. Available online: https://intantech.com/files/Intan_RHD2000_series_datasheet.pdf (accessed on 21 June 2021).

- Musk, E.N. An Integrated Brain-Machine Interface Platform with Thousands of Channels. J. Med. Internet Res. 2019, 21, e16194. [Google Scholar] [CrossRef]

- Xu, J.; Fan, Q.; Huijsing, J.H.; van Hoof, C.; Yazicioglu, R.F.; Makinwa, K.A.A. Measurement and analysis of current noise in chopper amplifiers. IEEE J. Solid-State Circuits 2013, 48, 1575–1584. [Google Scholar]

- Chan, P.K.; Ng, L.S.; Siek, L.; Lau, K.T. Designing CMOS folded-cascode operational amplifier with flicker noise minimization. Microelectron. J. 2001, 32, 69–73. [Google Scholar] [CrossRef]

- Alves, L.N.; Aguiar, R.L. Noise performance of classical current mirrors. In Proceedings of the 9th International Conference on Electronics, Circuits and Systems, Dubrovnik, Coratia, 15–18 September 2002; Volume 1, pp. 277–280. [Google Scholar]

- Rieger, R.; Taylor, J.; Demosthenous, A.; Donaldson, N.; Langlois, P. Design of a low-noise preamplifier for nerve cuff electrode recording. IEEE J. Solid-State Circuits 2003, 38, 1373–1379. [Google Scholar] [CrossRef]

- Castagnola, E.; Maiolo, L.; Maggiolini, E.; Minotti, A.; Marrani, M.; Maita, F.; Ricci, D. PEDOT-CNT-Coated Low-Impedance, Ultra-Flexible, and Brain-Conformable Micro-ECoG Arrays. IEEE Trans. Neural Syst. Rehabil. Eng. 2015, 23, 342–350. [Google Scholar] [CrossRef]

- Homayoni, F.; Hosseini, S.E.; Baedi, J. A high gain lateral BJT on thin film silicon substrate. In Proceedings of the 2009 IEEE International Conference of Electron Devices and Solid-State Circuits (EDSSC), Xi’an, China, 25–27 December 2009; pp. 278–281. [Google Scholar]

- Gray, P.R.; Hurst, P.; Meyer, R.G.; Lewis, S. Analysis and Design of Analog Integrated Circuits, 5th ed.; Wiley: Hoboken, NJ, USA, 2009; p. 126. [Google Scholar]

| Parameter | Value |

|---|---|

| Power | <100 µW |

| Gain | >60 dB |

| Bandwidth for | |

| • ECG | 100 Hz |

| • Local Field Potentials (LFP) | 500 Hz |

| • Single-fiber Action Potentials (AP) | 10 kHz |

| Integrated IRN | <10 µV |

| Size | <0.23 mm2 |

| CMOS technology node | <0.5 µm |

| BJT #1 | BJT #2 | BJT #3 (Darlington Pair) | BJT #4 | BJT #5 | |

|---|---|---|---|---|---|

| Current gain β | 50 | 29 | 188 | 77 | 45 |

| Current efficiency α | 0.7 | 0.4 | 0.7 | 0.8 | 0.4 |

| Early voltage | 14 V | 6 V | 12 V | 6 V | 33 V |

| Input resistance rπ | 199 kΩ | 153 kΩ | 1543 kΩ | 272 kΩ | 202 kΩ |

| Transconductance gm | 256 µA/V | 190 µA/V | 122 µA/V | 285 µA/V | 224 µA/V |

| IRN [nV/√Hz] | 9.96 | 11.9 | 29 | 10.8 | 9.91 |

| NEF | 1.21 | 1.45 | 3.5 | 1.3 | 1.20 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Simmich, S.; Bahr, A.; Rieger, R. Noise Efficient Integrated Amplifier Designs for Biomedical Applications. Electronics 2021, 10, 1522. https://doi.org/10.3390/electronics10131522

Simmich S, Bahr A, Rieger R. Noise Efficient Integrated Amplifier Designs for Biomedical Applications. Electronics. 2021; 10(13):1522. https://doi.org/10.3390/electronics10131522

Chicago/Turabian StyleSimmich, Sebastian, Andreas Bahr, and Robert Rieger. 2021. "Noise Efficient Integrated Amplifier Designs for Biomedical Applications" Electronics 10, no. 13: 1522. https://doi.org/10.3390/electronics10131522

APA StyleSimmich, S., Bahr, A., & Rieger, R. (2021). Noise Efficient Integrated Amplifier Designs for Biomedical Applications. Electronics, 10(13), 1522. https://doi.org/10.3390/electronics10131522