Space-Compliant Design of a Millimeter-Wave GaN-on-Si Stacked Power Amplifier Cell through Electro-Magnetic and Thermal Simulations

Abstract

:1. Introduction

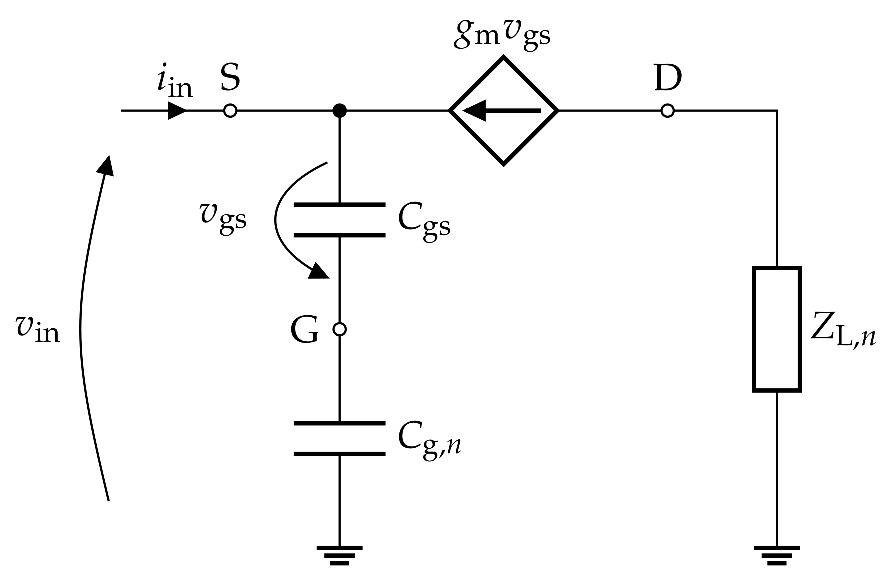

2. Stacked PA Architecture

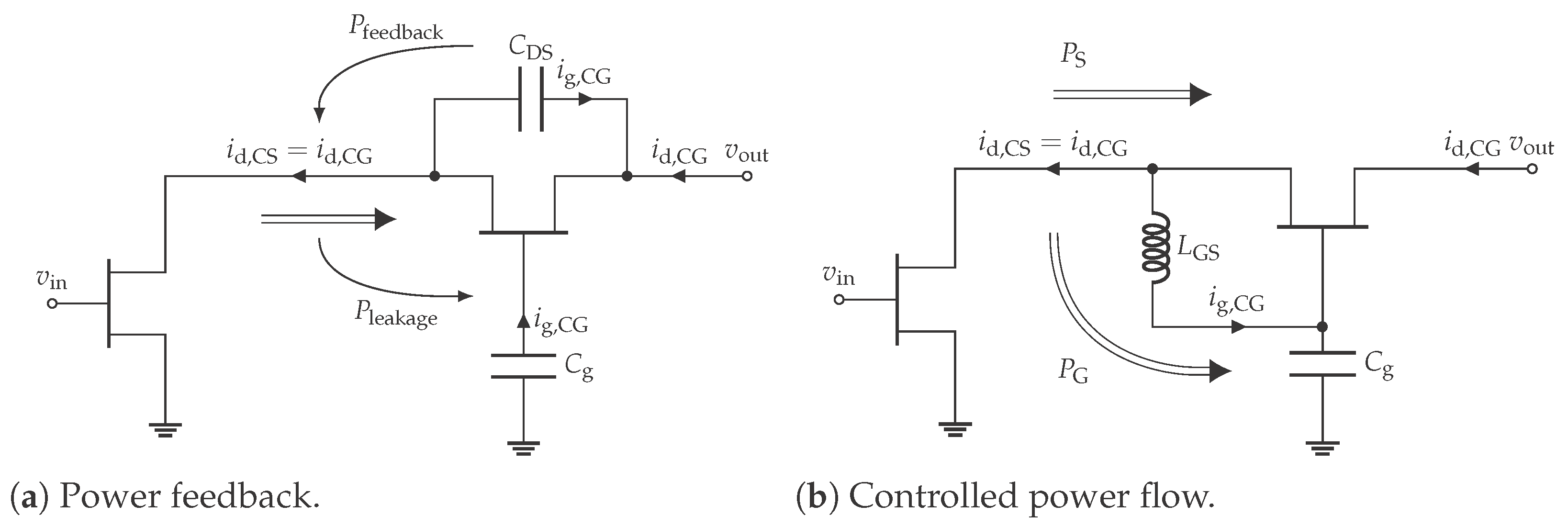

Gate Power Leakage and Maximum N

3. Technology

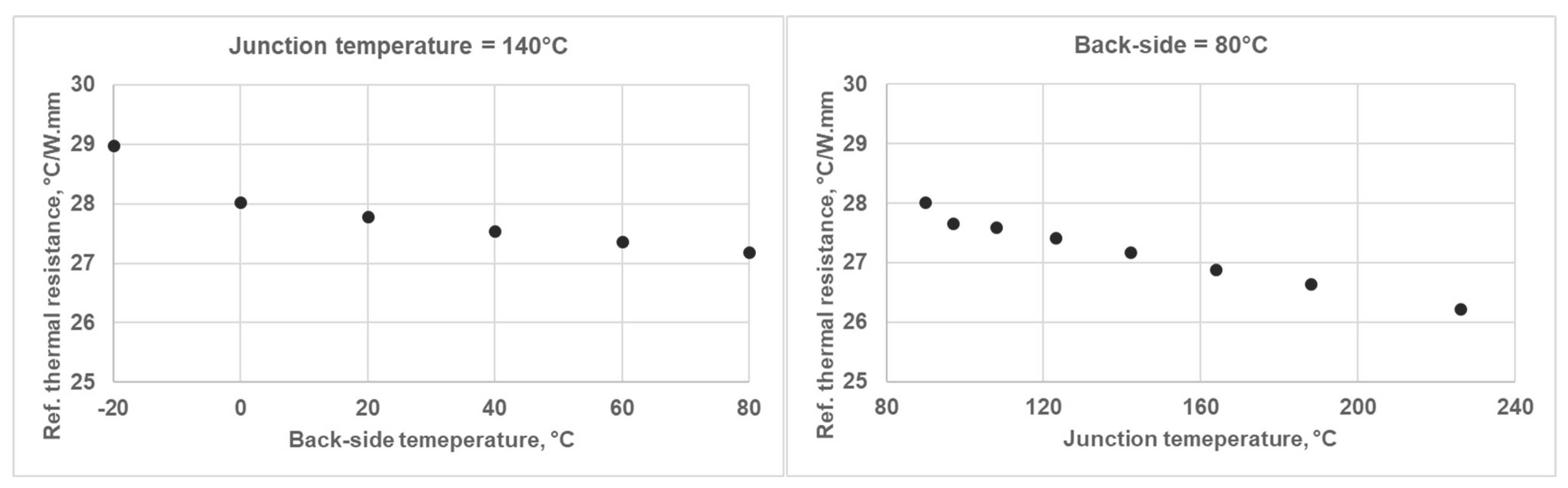

3.1. Device Thermal Model

4. Preliminary Design

4.1. Device Analysis

4.1.1. DC Bias Point Selection

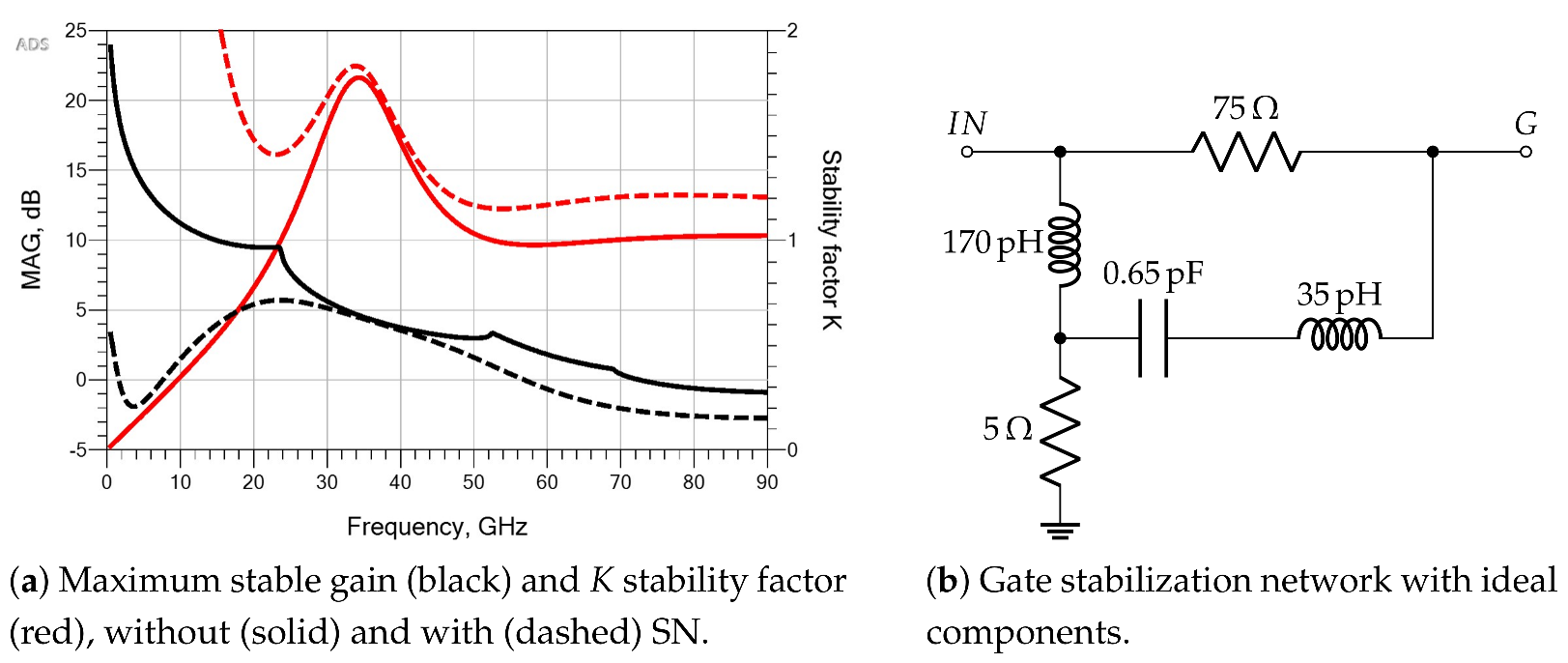

4.1.2. Small-Signal Analysis

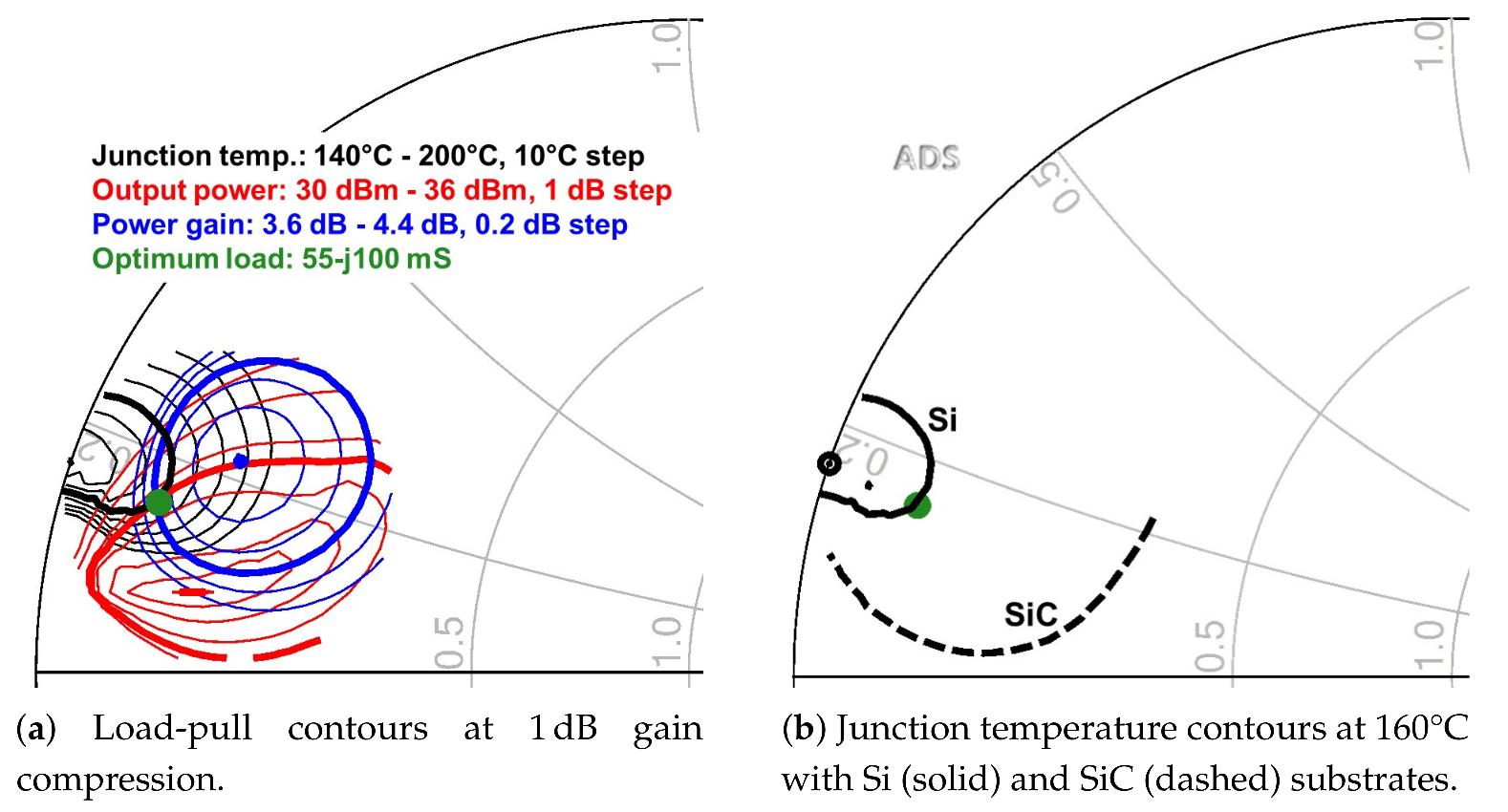

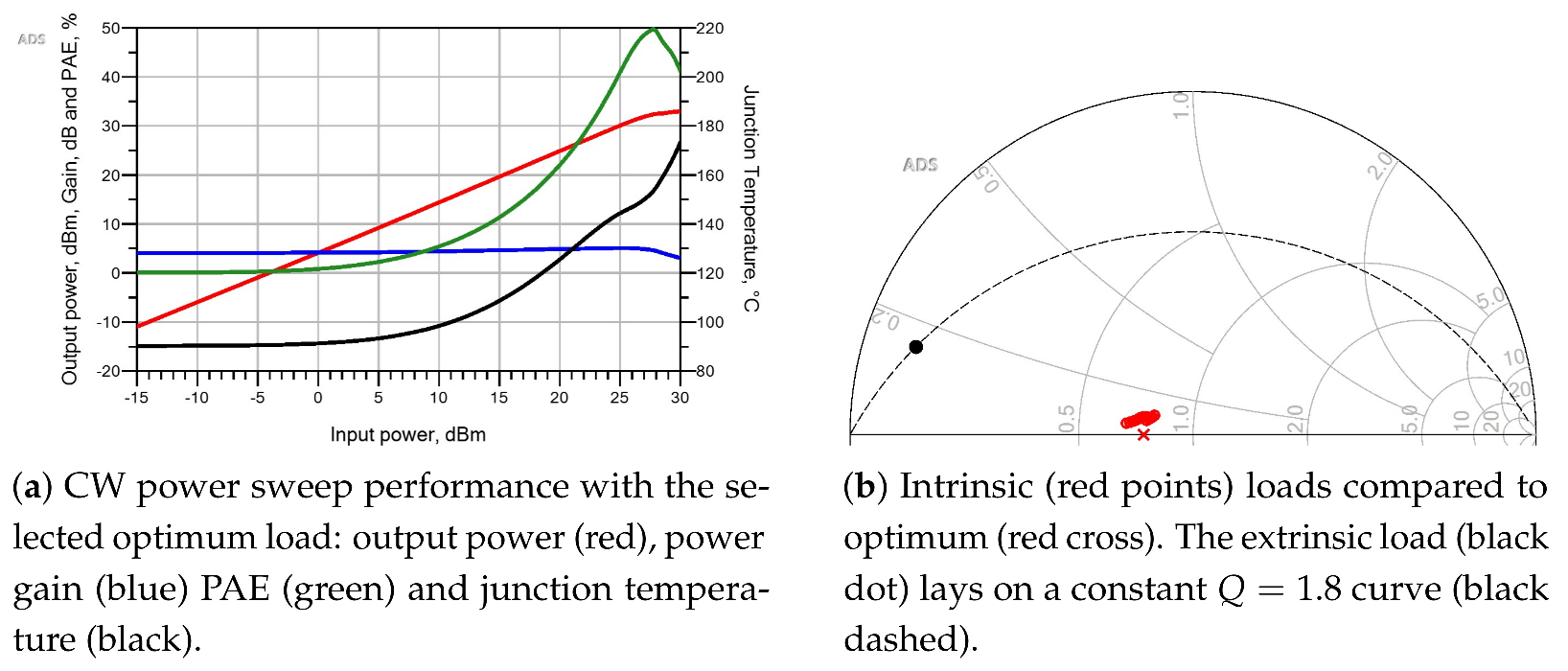

4.1.3. Load-Pull Analysis

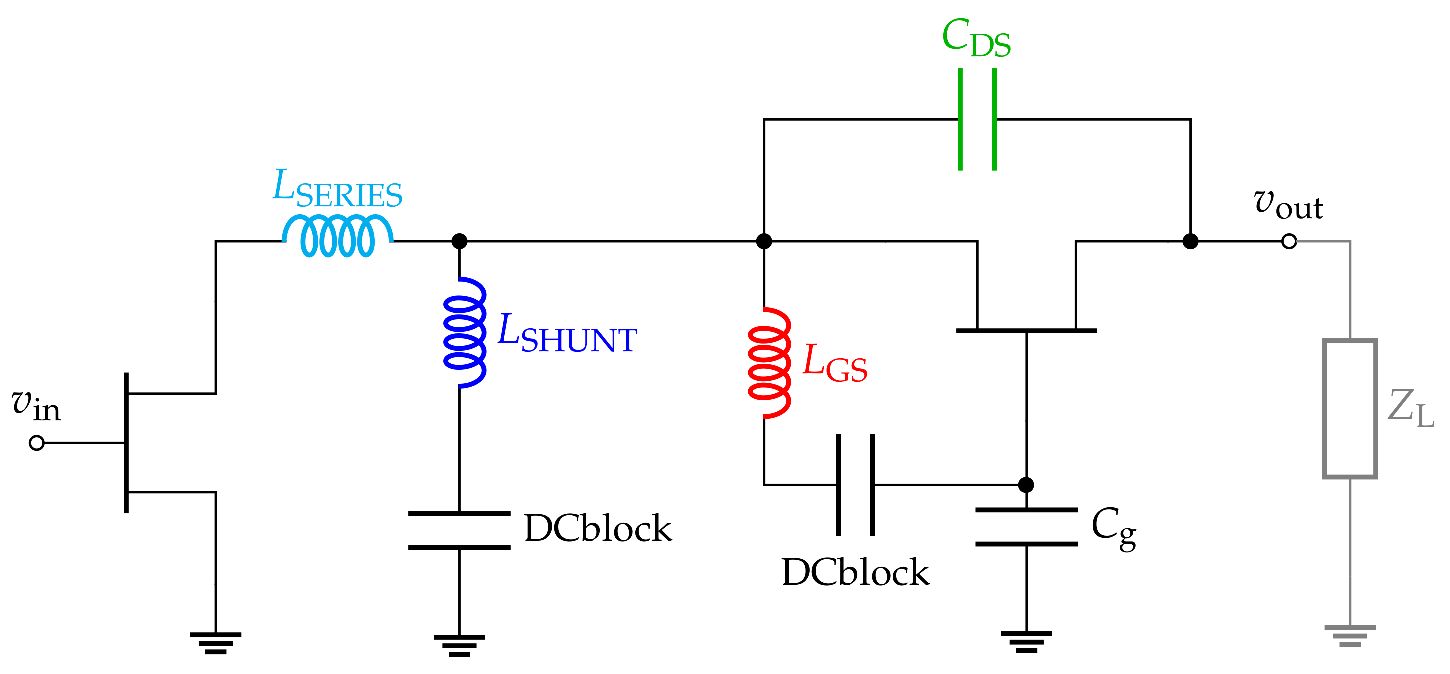

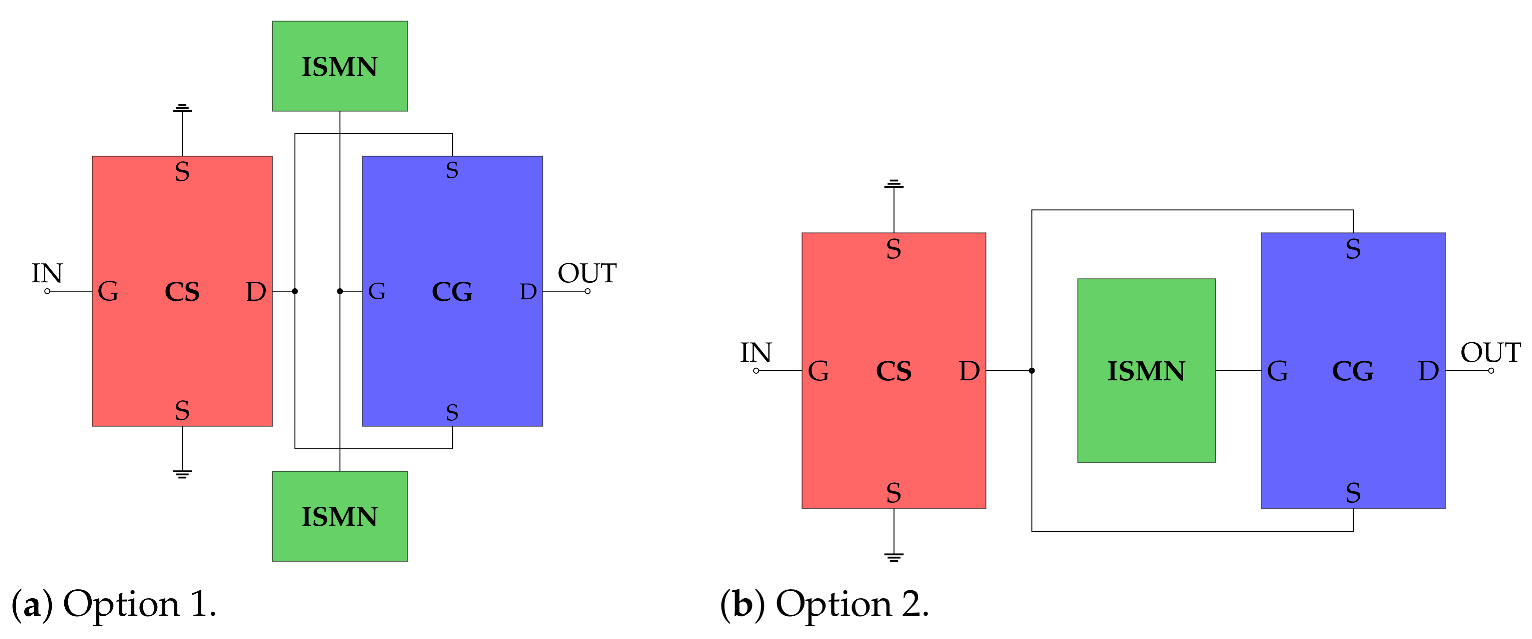

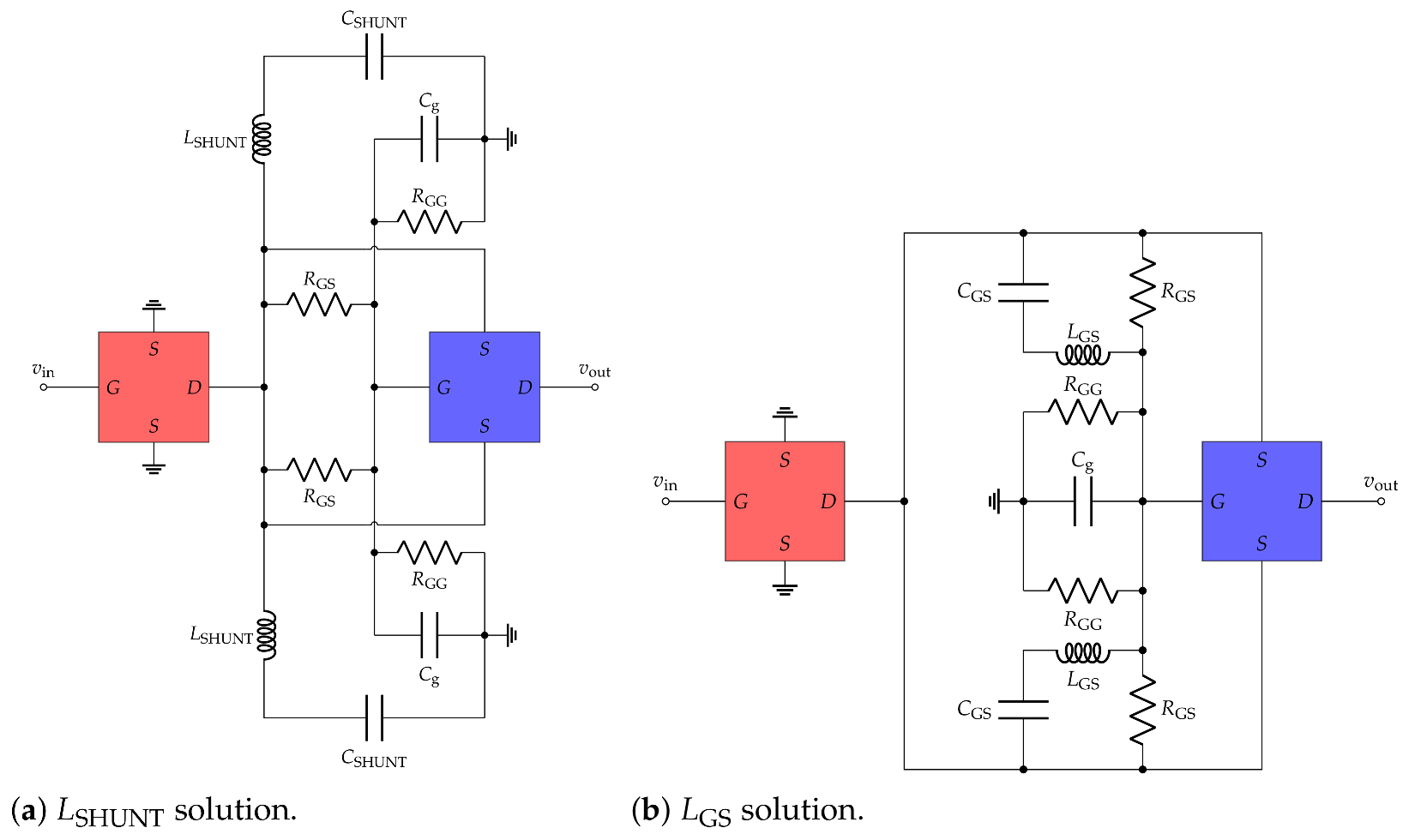

4.2. Stacked Inter-Stage Matching

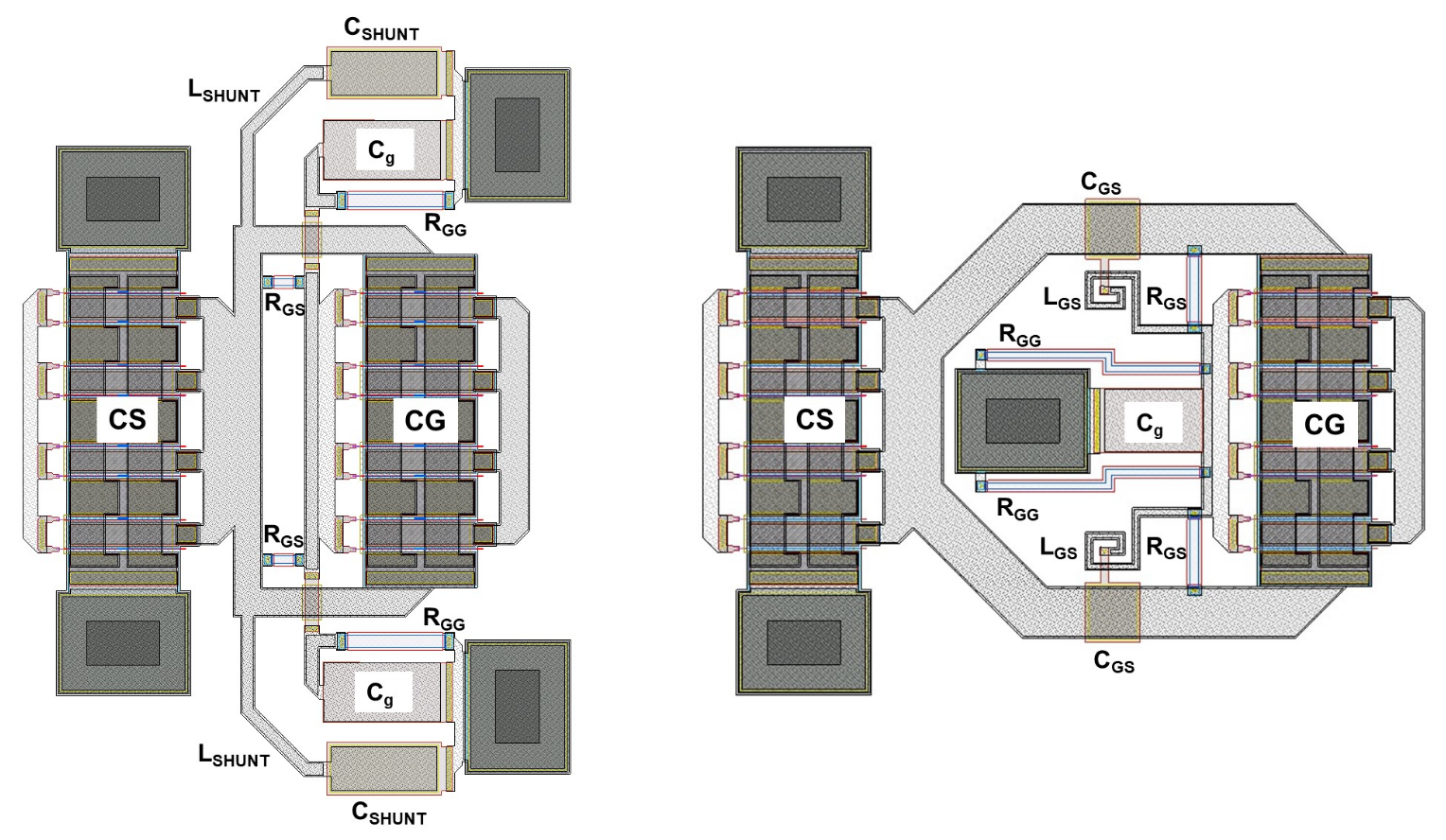

4.3. Layout Considerations

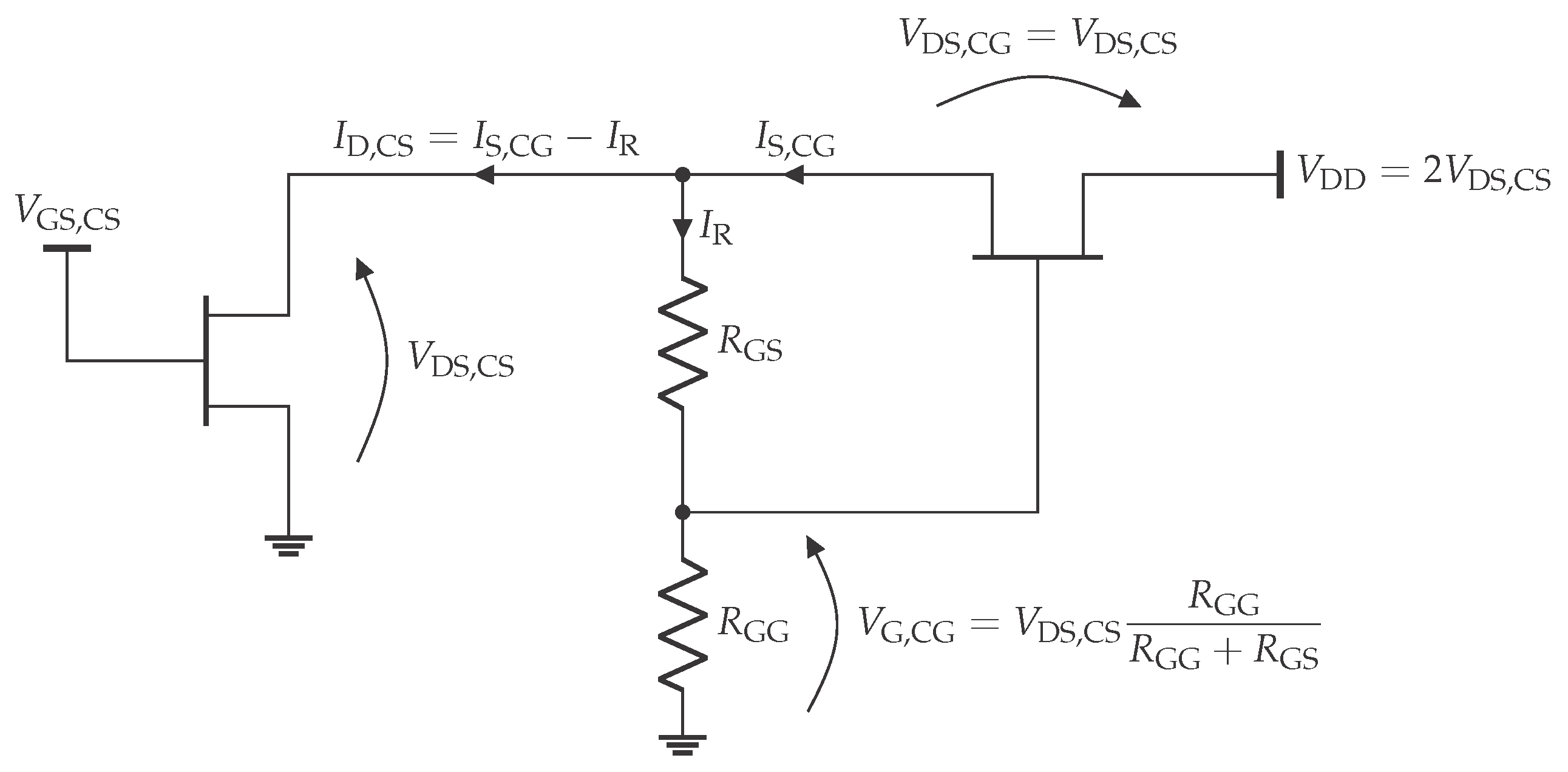

4.4. Self-Bias Network

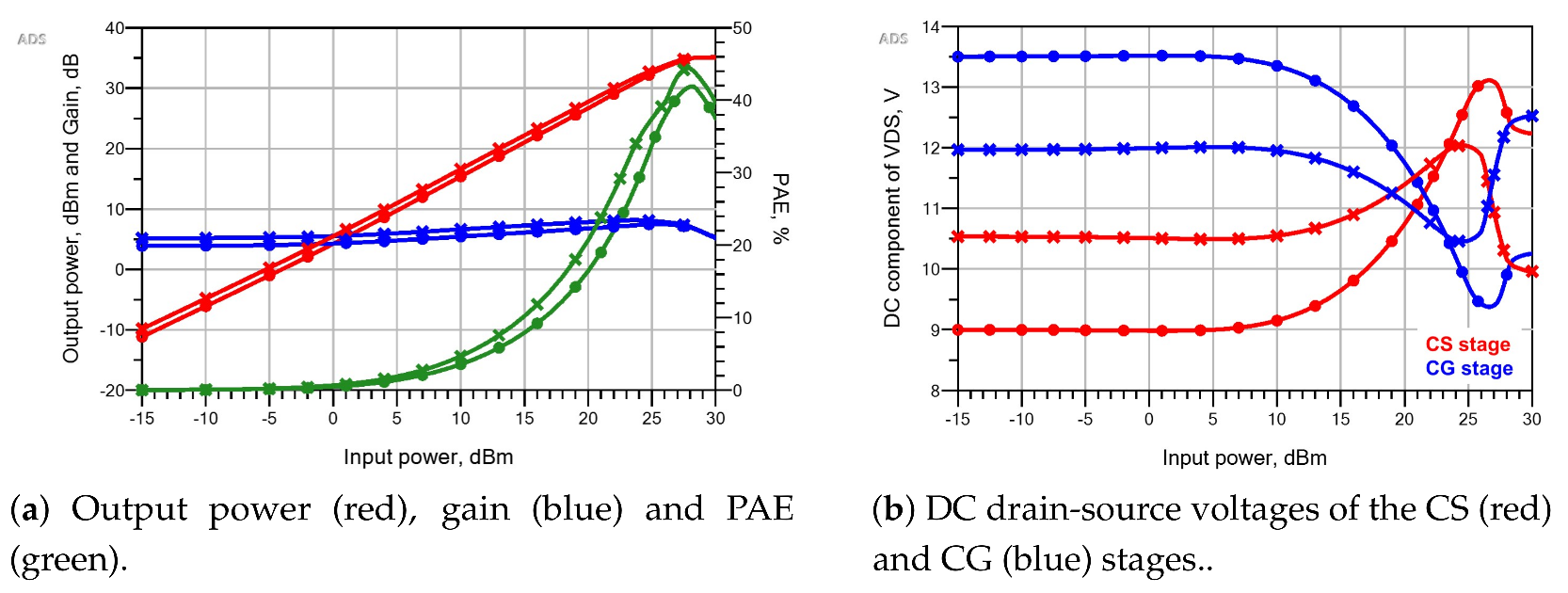

5. Circuit-Level (CL) Design

6. Electro-Magnetic (EM) Design

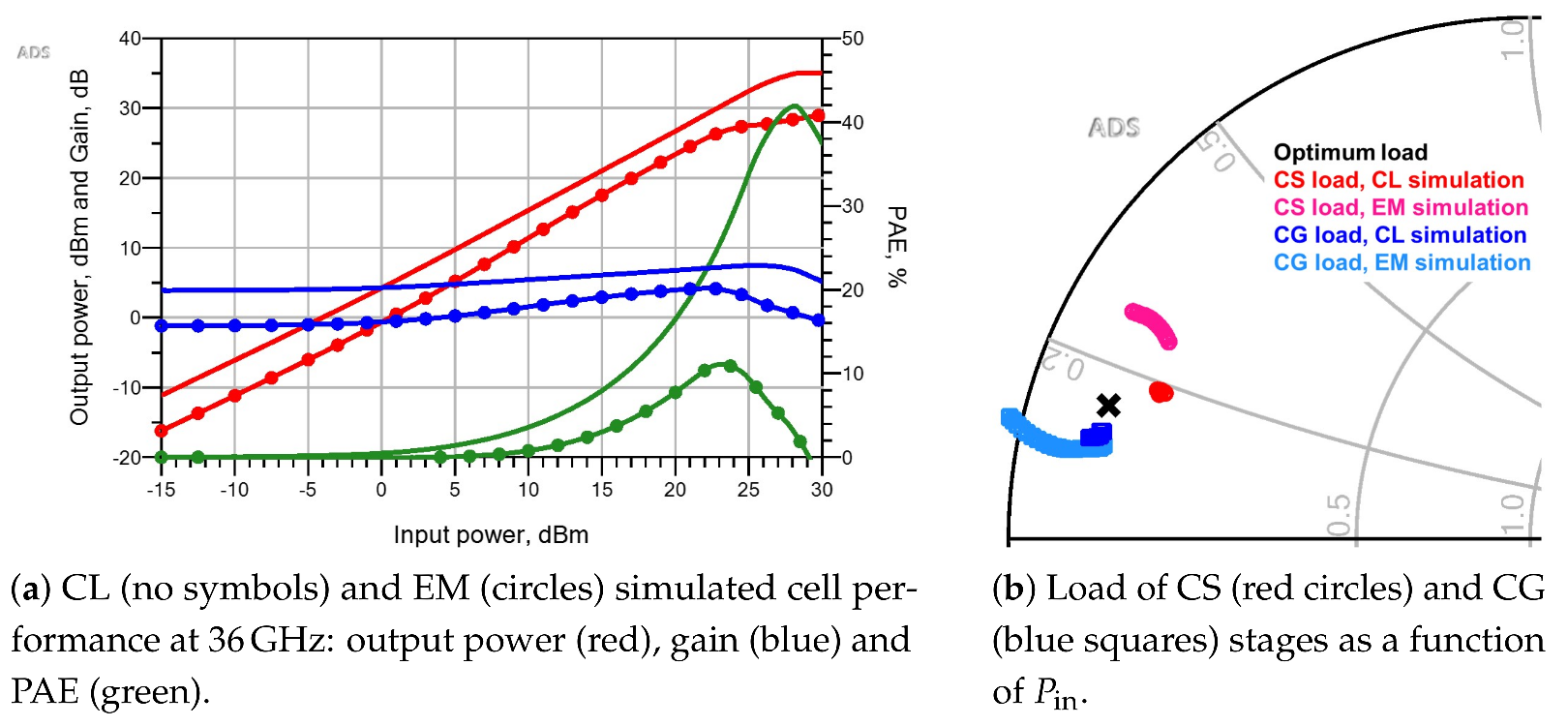

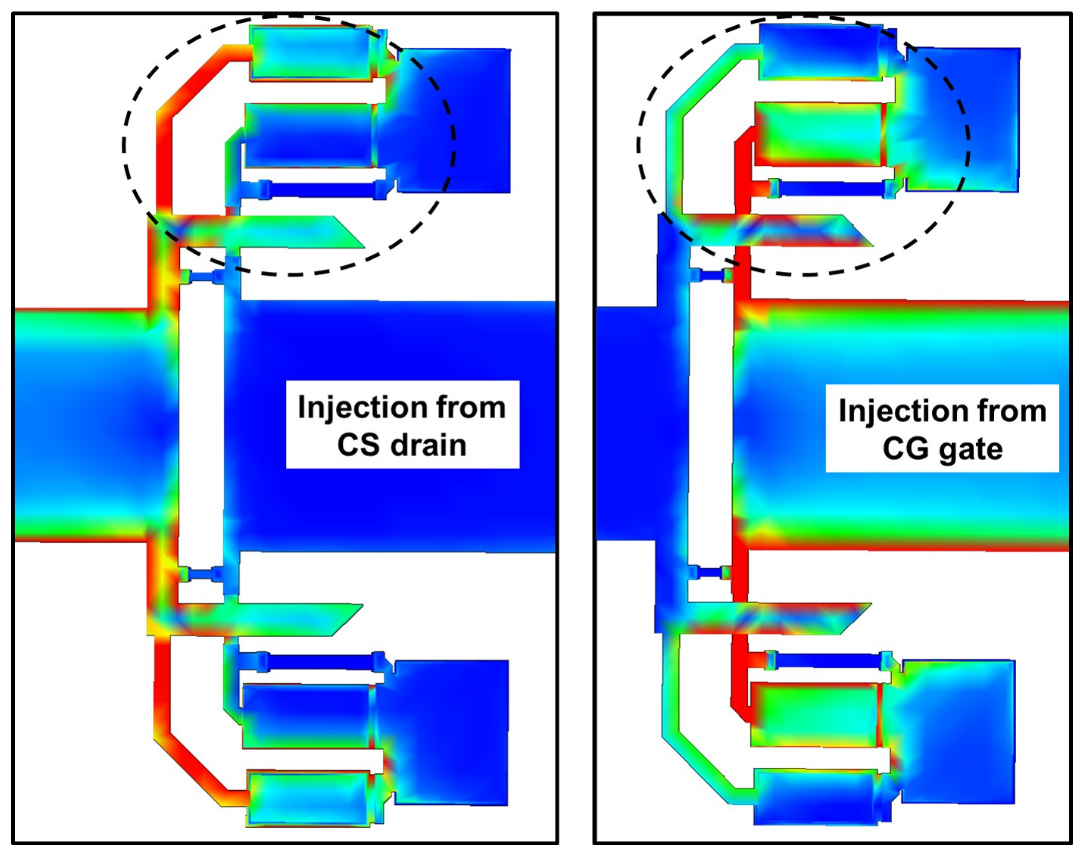

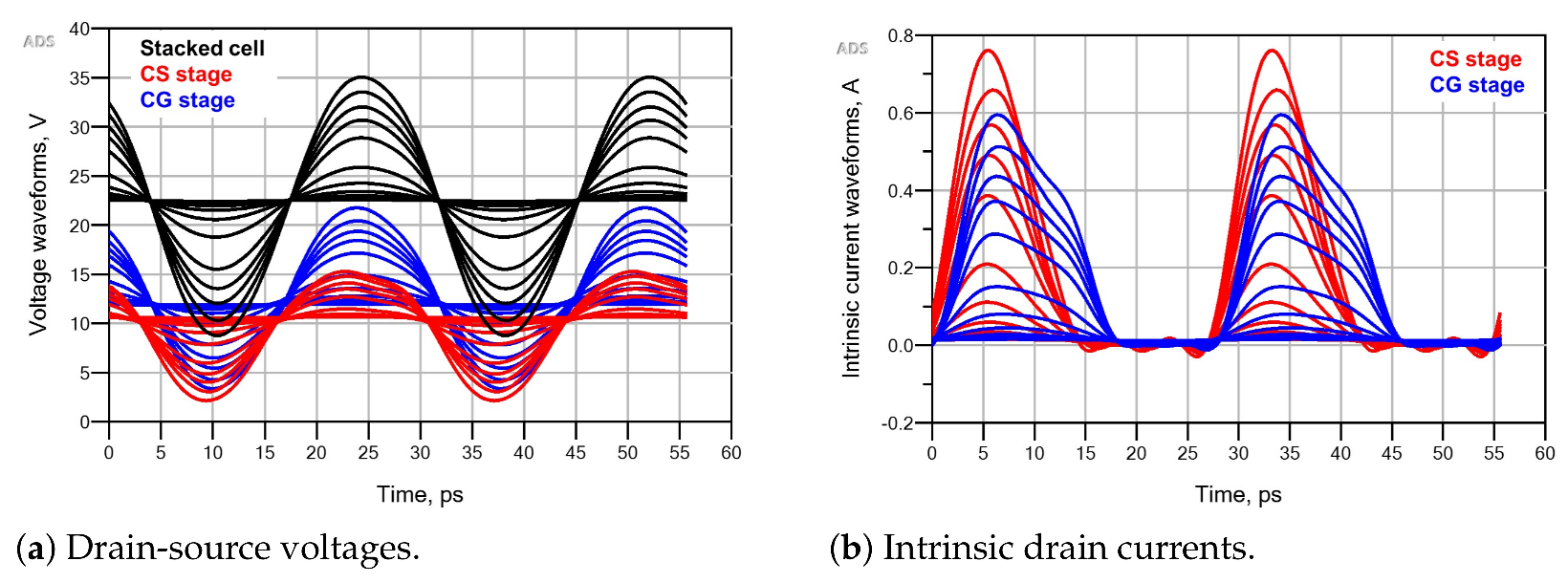

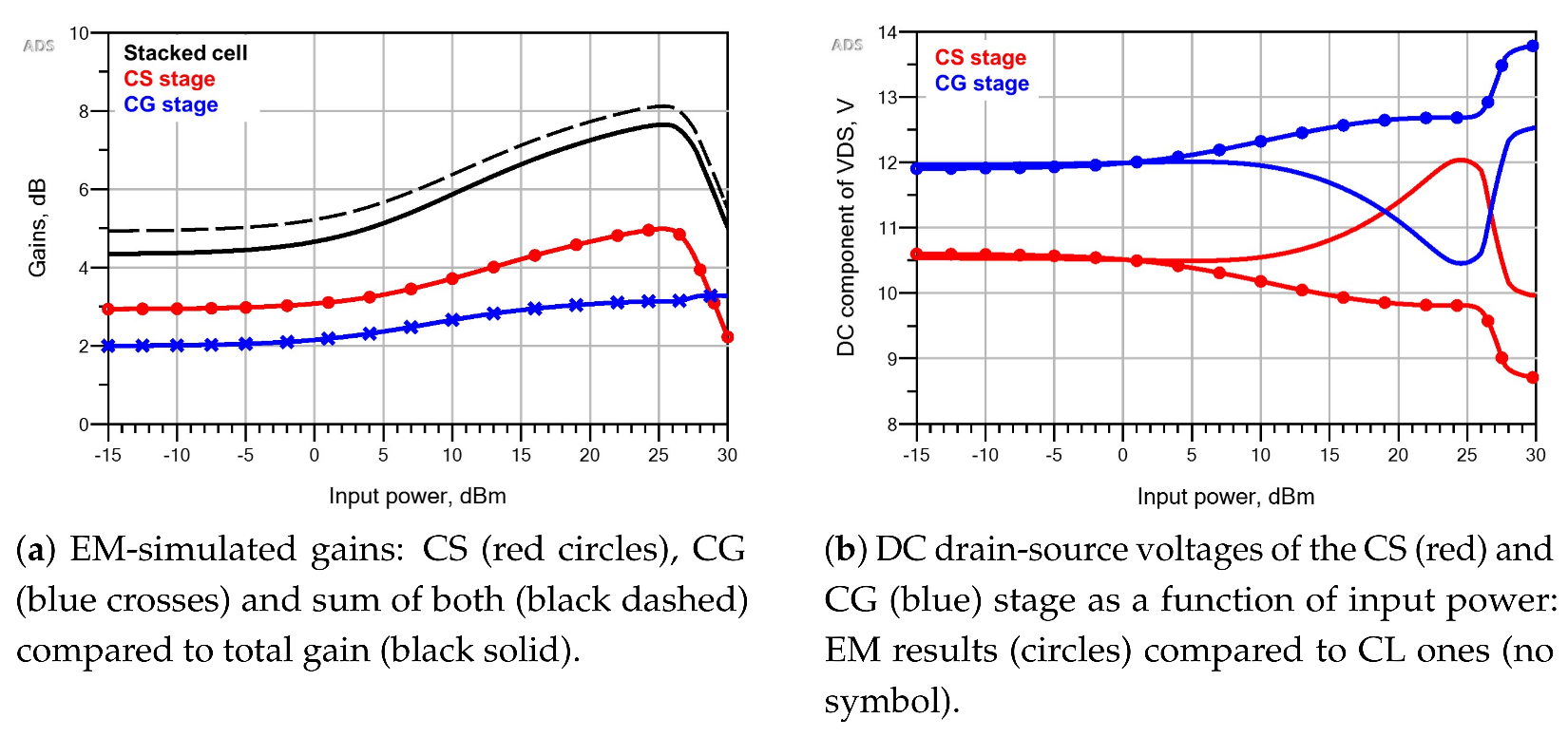

6.1. EM Simulation Results for the Shunt-Inductance-Based Cell

6.2. EM Simulation Results for the Gate-Source-Inductance-Based Cell

7. Stability, Linearity and Thermal Assessment

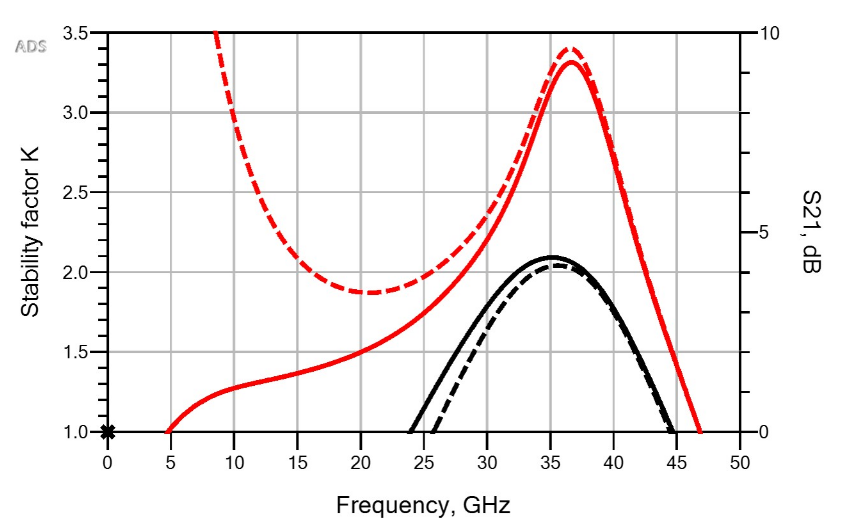

7.1. Stability Analysis

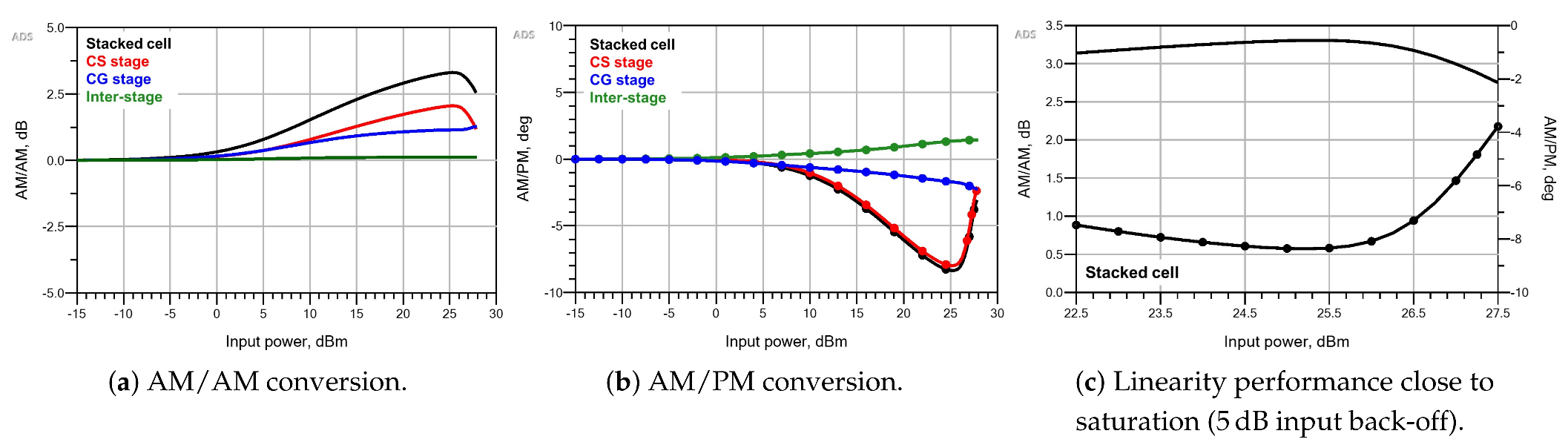

7.2. Linearity Analysis

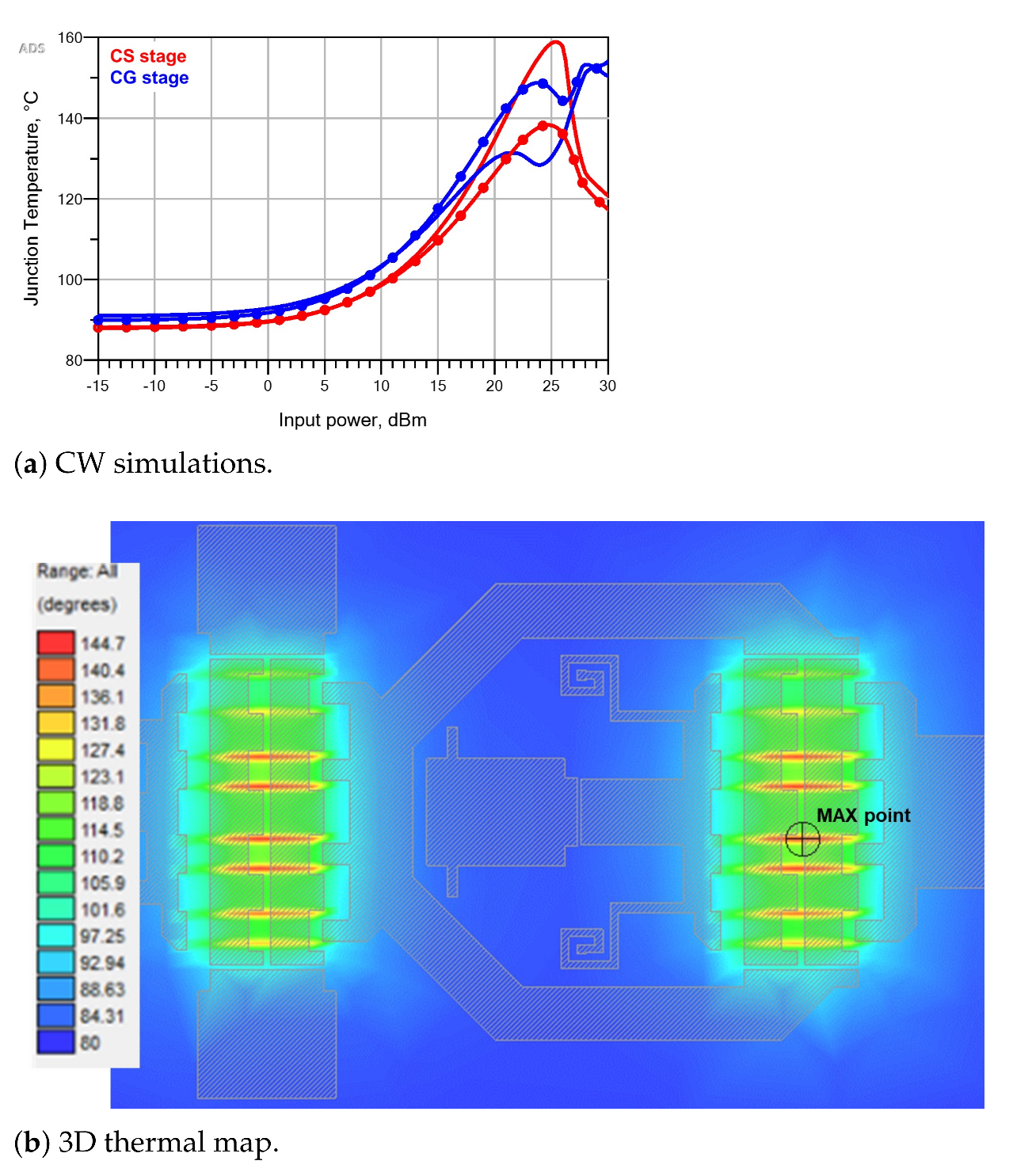

7.3. Thermal Analysis

8. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Chen, S.; Nayak, S.; Campbell, C.; Reese, E. High Efficiency 5 W/10 W 32–38 GHz Power Amplifier MMICs Utilizing Advanced 0.15 μm GaN HEMT Technology. In Proceedings of the 2016 IEEE Compound Semiconductor Integrated Circuit Symposium (CSICS), Austin, TX, USA, 23–26 October 2016; pp. 1–4. [Google Scholar] [CrossRef]

- Moron, J.; Leblanc, R.; Lecourt, F.; Frijlink, P. 12 W, 30% PAE, 40 GHz power amplifier MMIC using a commercially available GaN/Si process. In Proceedings of the 2018 IEEE/MTT-S International Microwave Symposium-IMS, Philadelphia, PA, USA, 10–15 June 2018; pp. 1457–1460. [Google Scholar] [CrossRef]

- Estella, N.; Camargo, E.; Schellenberg, J.; Bui, L. High-Efficiency, Ka-band GaN Power Amplifiers. In Proceedings of the 2019 IEEE MTT-S International Microwave Symposium (IMS), Boston, MA, USA, 2–7 June 2019; pp. 568–571. [Google Scholar] [CrossRef]

- Cidronali, A.; Passafiume, M.; Colantonio, P.; Collodi, G.; Florian, C.; Leuzzi, G.; Pirola, M.; Ramella, C.; Santarelli, A.; Traverso, P. System Level Analysis of Millimetre-wave GaN-based MIMO Radar for Detection of Micro Unmanned Aerial Vehicles. In Proceedings of the 2019 PhotonIcs & Electromagnetics Research Symposium-Spring (PIERS-Spring), Rome, Italy, 17–20 June 2019; pp. 438–450. [Google Scholar] [CrossRef]

- Ramella, C.; Florian, C.; Cipriani, E.; Pirola, M.; Giannini, F.; Colantonio, P. Ka-band 4 W GaN/Si MMIC power amplifier for CW radar applications. In Proceedings of the 2020 15th European Microwave Integrated Circuits Conference (EuMIC), Utrecht, The Netherlands, 10–15 January 2021; pp. 33–36. [Google Scholar] [CrossRef]

- Colantonio, P.; Giannini, F.; Limiti, E. High Efficiency RF and Microwave Solid State Power Amplifiers; Microwave and Optical Engineering; Wiley: New York, NY, USA, 2009. [Google Scholar]

- European Cooperation for Space Standardization. ECSS-Q-ST-30-11C Rev 1—Space Product Assurance—Derating EEE Components; European Cooperation for Space Standardization: Noordwijk, The Netherlands, 2011. [Google Scholar]

- European Space Agency. GaN Reliability Enhancement and Technology Transfer Initiative (GREAT2); European Space Agency/European Space Technology and Research Centre: Noordwijk, The Netherlands, 2008. [Google Scholar]

- Ramella, C.; Pirola, M.; Reale, A.; Ramundo, M.; Colantonio, P.; Maur, M.A.D.; Camarchia, V.; Piacibello, A.; Giofrè, R. Thermal-aware GaN/Si MMIC design for space applications. In Proceedings of the 2019 IEEE International Conference on Microwaves, Antennas, Communications and Electronic Systems (COMCAS), Tel-Aviv, Israel, 4–6 November 2019; pp. 1–6. [Google Scholar]

- Shifrin, M.; Ayasli, Y.; Katzin, P. A new power amplifier topology with series biasing and power combining of transistors. In Proceedings of the IEEE 1992 Microwave and Millimeter-Wave Monolithic Circuits Symposium Digest of Papers, Albuquerque, NM, USA, 1–3 June 1992; pp. 39–41. [Google Scholar] [CrossRef]

- Dabag, H.; Hanafi, B.; Golcuk, F.; Agah, A.; Buckwalter, J.F.; Asbeck, P.M. Analysis and Design of Stacked-FET Millimeter-Wave Power Amplifiers. IEEE Trans. Microw. Theory Tech. 2013, 61, 1543–1556. [Google Scholar] [CrossRef]

- Pornpromlikit, S.; Jeong, J.; Presti, C.D.; Scuderi, A.; Asbeck, P.M. A Watt-Level Stacked-FET Linear Power Amplifier in Silicon-on-Insulator CMOS. IEEE Trans. Microw. Theory Tech. 2010, 58, 57–64. [Google Scholar] [CrossRef]

- Kim, J.; Dabag, H.; Asbeck, P.; Buckwalter, J.F. Q-Band and W-Band Power Amplifiers in 45-nm CMOS SOI. IEEE Trans. Microw. Theory Tech. 2012, 60, 1870–1877. [Google Scholar] [CrossRef]

- Oßmann, P.; Fuhrmann, J.; Dufrêne, K.; Fritzin, J.; Moreira, J.; Pretl, H.; Springer, A. Design of a Fully Integrated Two-Stage Watt-Level Power Amplifier Using 28-nm CMOS Technology. IEEE Trans. Microw. Theory Tech. 2016, 64, 188–199. [Google Scholar] [CrossRef]

- Zhang, C.; Li, Z.; Cheng, G.; Wang, H.; Li, Z. A 26.5–40 GHz Stacked Power Amplifier in 130 nm SiGe BiCMOS Technology. In Proceedings of the 2018 IEEE International Conference on Integrated Circuits, Technologies and Applications (ICTA), Beijing, China, 21–23 November 2018; pp. 36–37. [Google Scholar] [CrossRef]

- Aikio, J.P.; Hietanen, M.; Tervo, N.; Rahkonen, T.; Pärssinen, A. Ka-Band 3-Stack Power Amplifier with 18.8 dBm Psat and 23.4% PAE Using 22nm CMOS FDSOI Technology. In Proceedings of the 2019 IEEE Topical Conference on RF/Microwave Power Amplifiers for Radio and Wireless Applications (PAWR), Orlando, FL, USA, 20–23 January 2019; pp. 1–3. [Google Scholar] [CrossRef] [Green Version]

- Mohammadi, S.; Shan, H.; Conrad, N.; Hathorn, S.; Peterson, J. High-Efficiency Stacked Cell CMOS SOI Power Amplifiers for 5G Applications. In Proceedings of the 2019 IEEE MTT-S International Microwave Conference on Hardware and Systems for 5G and Beyond (IMC-5G), Atlanta, GA, USA, 15–16 August 2019; pp. 1–4. [Google Scholar] [CrossRef]

- Chang, Y.; Lu, B.; Wang, Y.; Wang, H. A Ka-Band Stacked Power Amplifier with 24.8-dBm Output Power and 24.3% PAE in 65-nm CMOS Technology. In Proceedings of the 2019 IEEE MTT-S International Microwave Symposium (IMS), Boston, MA, USA, 2–7 June 2019; pp. 316–319. [Google Scholar] [CrossRef]

- Inoue, A.; Goto, S.; Kunii, T.; Ishikawa, T.; Matsuda, Y. A high efficiency, high voltage, balanced cascode FET. In Proceedings of the IEEE MTT-S International Microwave Symposium Digest 2005, Long Beach, CA, USA, 17 June 2005; pp. 4–672. [Google Scholar] [CrossRef]

- Lee, C.; Kim, Y.; Koh, Y.; Kim, J.; Seo, K.; Jeong, J.; Kwon, Y. A 18 GHz Broadband Stacked FET Power Amplifier Using 130 nm Metamorphic HEMTs. IEEE Microw. Wirel. Compon. Lett. 2009, 19, 828–830. [Google Scholar] [CrossRef]

- Park, Y.; Kim, Y.; Choi, W.; Woo, J.; Kwon, Y. X-to-K band broadband watt-level power amplifier using stacked-FET unit cells. In Proceedings of the 2011 IEEE Radio Frequency Integrated Circuits Symposium, Baltimore, MD, USA, 5–7 June 2011; pp. 1–4. [Google Scholar] [CrossRef]

- Kim, Y.; Kwon, Y. Analysis and Design of Millimeter-Wave Power Amplifier Using Stacked-FET Structure. IEEE Trans. Microw. Theory Tech. 2015, 63, 691–702. [Google Scholar] [CrossRef]

- Nguyen, D.P.; Pham, A. An Ultra Compact Watt-Level Ka-Band Stacked-FET Power Amplifier. IEEE Microw. Wirel. Components Lett. 2016, 26, 516–518. [Google Scholar] [CrossRef] [Green Version]

- Ramella, C.; Piacibello, A.; Camarchia, V.; Pirola, M.; Quaglia, R. Characterization-oriented design of a compact GaAs MMIC 3-stacked power cell. In Proceedings of the 2016 2016 21st International Conference on Microwave, Radar and Wireless Communications (MIKON), Krakow, Poland, 9–11 May 2016; pp. 1–4. [Google Scholar] [CrossRef]

- Piacibello, A.; Pirola, M.; Camarchia, V.; Ramella, C.; Quaglia, R. A Ku-band Compact MMIC PA based on Stacked GaAs pHEMT cells. In Proceedings of the 2018 International Workshop on Integrated Nonlinear Microwave and Millimetre-wave Circuits (INMMIC), Brive La Gaillarde, France, 5–6 July 2018; pp. 1–3. [Google Scholar] [CrossRef]

- Thome, F.; Leuther, A.; Schlechtweg, M.; Ambacher, O. Broadband High-Power W-Band Amplifier MMICs Based on Stacked-HEMT Unit Cells. IEEE Trans. Microw. Theory Tech. 2018, 66, 1312–1318. [Google Scholar] [CrossRef]

- van der Bent, G.; de Hek, P.; van Vliet, F.E. Design Procedure for Integrated Microwave GaAs Stacked-FET High-Power Amplifiers. IEEE Trans. Microw. Theory Tech. 2019, 67, 3716–3731. [Google Scholar] [CrossRef]

- Ezzeddine, B.A.; Hung, H.A.; Viveiros, E.; Huang, H. High-power GaN MMIC PA Over 40–4000 MHz. In Proceedings of the 2013 IEEE MTT-S International Microwave Symposium Digest (MTT), Seattle, WA, USA, 2–7 June 2013; pp. 1–4. [Google Scholar] [CrossRef]

- Martin, A.; Reveyrand, T.; Campovecchio, M.; Aubry, R.; Piotrowicz, S.; Floriot, D.; Quere, R. Design of GaN-based balanced cascode cells for wide-band distributed power amplifier. In Proceedings of the 2007 European Microwave Integrated Circuit Conference, Munich, Germany, 8–10 October 2007; pp. 154–157. [Google Scholar] [CrossRef] [Green Version]

- Costanzo, F.; Giofrè, R.; Camarchia, V.; Colantonio, P.; Limiti, E. A Ka-band Doherty Power Amplifier using an innovative Stacked-FET Cell. In Proceedings of the 2019 15th Conference on Ph.D Research in Microelectronics and Electronics (PRIME), Lausanne, Switzerland, 15–18 July 2019; pp. 165–168. [Google Scholar] [CrossRef]

- Ramella, C.; Pirola, M.; Colantonio, P. A Ka-band 33 dBm Stacked Power Amplifier Cell in 100 nm GaN-on-Si Technology. In Proceedings of the 2020 23rd International Microwave and Radar Conference (MIKON), Warsaw, Poland, 5–8 October 2020; pp. 204–208. [Google Scholar] [CrossRef]

- Sun, W.; Kuo, C. A 19.1% PAE, 22.4-dBm 53-GHz Parallel Power Combining Power Amplifier with Stacked-FET Techniques in 90-nm CMOS. In Proceedings of the 2019 IEEE MTT-S International Microwave Symposium (IMS), Boston, MA, USA, 2–7 June 2019; pp. 327–330. [Google Scholar] [CrossRef]

- Li, S.; Fritsche, D.; Carta, C.; Ellinger, F. Design and characterization of a 12–40 GHz power amplifier in SiGe technology. In Proceedings of the 2018 IEEE Topical Conference on RF/Microwave Power Amplifiers for Radio and Wireless Applications (PAWR), Anaheim, CA, USA, 14–17 January 2018; pp. 23–25. [Google Scholar] [CrossRef]

- Jayamon, J.; Gurbuz, O.; Hanafi, B.; Agah, A.; Buckwalter, J.; Rebeiz, G.; Asbeck, P. Spatially power-combined W-band power amplifier using stacked CMOS. In Proceedings of the 2014 IEEE Radio Frequency Integrated Circuits Symposium, Tampa, FL, USA, 1–3 June 2014; pp. 151–154. [Google Scholar] [CrossRef]

- Nguyen, D.P.; Pham, T.; Pham, A. A 28-GHz Symmetrical Doherty Power Amplifier Using Stacked-FET Cells. IEEE Trans. Microw. Theory Tech. 2018, 66, 2628–2637. [Google Scholar] [CrossRef]

- Ezzeddine, A.K.; Huang, H.C. The high voltage/high power FET (HiVP). In Proceedings of the IEEE Radio Frequency Integrated Circuits (RFIC) Symposium 2003, Philadelphia, PA, USA, 9–10 June 2003; pp. 215–218. [Google Scholar] [CrossRef]

- Ramella, C.; Piacibello, A.; Camarchia, V.; Pirola, M. Electro-magnetic Crosstalk Effects in a Millimeter-wave MMIC Stacked Cell. In Proceedings of the 2020 International Workshop on Integrated Nonlinear Microwave and Millimetre-Wave Circuits (INMMiC), Cardiff, UK, 16–17 July 2020; pp. 1–3. [Google Scholar] [CrossRef]

- Ezzeddine, A.K.; Huang, H.C.; Singer, J.L. UHiFET—A new high-frequency High-Voltage device. In Proceedings of the 2011 IEEE MTT-S International Microwave Symposium, Baltimore, MD, USA, 5–10 June 2011; p. 1. [Google Scholar] [CrossRef]

- Berroth, M.; Bosch, R. Broad-band determination of the FET small-signal equivalent circuit. IEEE Trans. Microw. Theory Tech. 1990, 38, 891–895. [Google Scholar] [CrossRef] [Green Version]

- Thome, F.; Maroldt, S.; Ambacher, O. Prospects and Limitations of Stacked-FET Approaches for Enhanced Output Power in Voltage-Controlled Oscillators. IEEE Trans. Microw. Theory Tech. 2016, 64, 836–846. [Google Scholar] [CrossRef]

- Gasmi, A.; El Kaamouchi, M.; Poulain, J.; Wroblewski, B.; Lecourt, F.; Dagher, G.; Frijlink, P.; Leblanc, R. 10W power amplifier and 3W transmit/receive module with 3 dB NF in Ka band using a 100 nm GaN/Si process. In Proceedings of the 2017 IEEE Compound Semiconductor Integrated Circuit Symposium (CSICS), Miami, FL, USA, 22–25 October 2017; pp. 1–4. [Google Scholar] [CrossRef]

- OMMIC. U-GaN Design Manual V1.2.4; OMMIC: Limeil-Brévannes, France, 2018. [Google Scholar]

- Fersch, T.; Quaglia, R.; Pirola, M.; Camarchia, V.; Ramella, C.; Khoshkholgh, A.J.; Ghione, G.; Weigel, R. Stacked GaAs pHEMTs: Design of a K-band power amplifier and experimental characterization of mismatch effects. In Proceedings of the 2015 IEEE MTT-S International Microwave Symposium, Phoenix, AZ, USA, 17–22 May 2015; pp. 1–4. [Google Scholar] [CrossRef]

| Feature | Value |

|---|---|

| Cut-off frequency | GHz |

| Saturation current | mA/mm |

| Threshold voltage | V |

| Output power | W/mm |

| Junction temperature | C |

| Breakdown voltage | >50 V |

| Quiescent | 15 V |

| Component | Value Solution | Value Solution |

|---|---|---|

| 165 fF (MIM) | 175 fF (MIM) | |

| 92.5 pH (transmission lines) | 170 pH (spiral inductors) | |

| 0.9 pF (MIM) | 0.8 pF (MIM) | |

| 1140 | 1320 | |

| 4400 | 6500 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ramella, C.; Pirola, M.; Florian, C.; Colantonio, P. Space-Compliant Design of a Millimeter-Wave GaN-on-Si Stacked Power Amplifier Cell through Electro-Magnetic and Thermal Simulations. Electronics 2021, 10, 1784. https://doi.org/10.3390/electronics10151784

Ramella C, Pirola M, Florian C, Colantonio P. Space-Compliant Design of a Millimeter-Wave GaN-on-Si Stacked Power Amplifier Cell through Electro-Magnetic and Thermal Simulations. Electronics. 2021; 10(15):1784. https://doi.org/10.3390/electronics10151784

Chicago/Turabian StyleRamella, Chiara, Marco Pirola, Corrado Florian, and Paolo Colantonio. 2021. "Space-Compliant Design of a Millimeter-Wave GaN-on-Si Stacked Power Amplifier Cell through Electro-Magnetic and Thermal Simulations" Electronics 10, no. 15: 1784. https://doi.org/10.3390/electronics10151784

APA StyleRamella, C., Pirola, M., Florian, C., & Colantonio, P. (2021). Space-Compliant Design of a Millimeter-Wave GaN-on-Si Stacked Power Amplifier Cell through Electro-Magnetic and Thermal Simulations. Electronics, 10(15), 1784. https://doi.org/10.3390/electronics10151784