Optimization of Self-Heating Driven Leakage Current Properties of Gate-All-Around Field-Effect Transistors Using Neural Network Modeling and Genetic Algorithm

Abstract

:1. Introduction

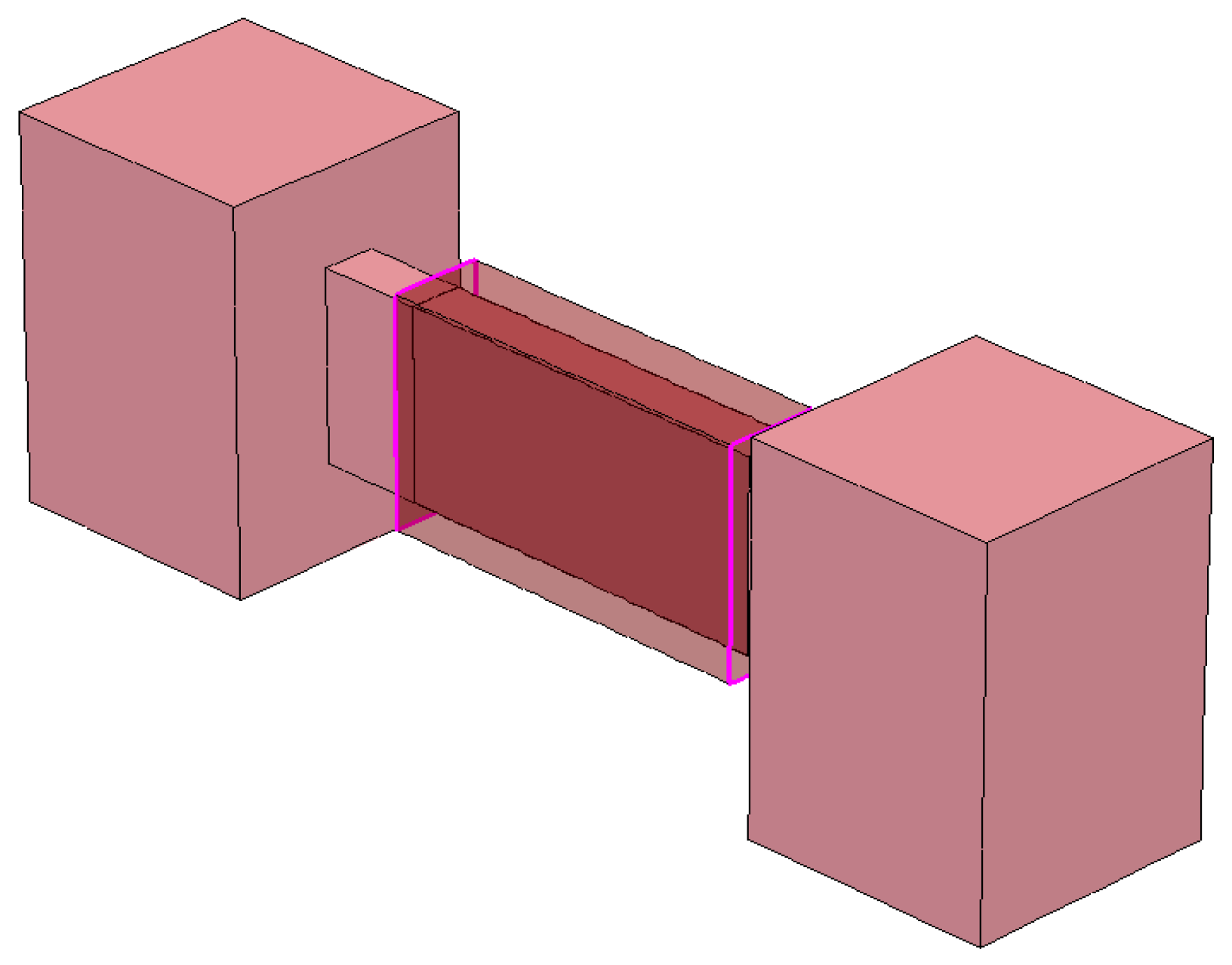

2. Modeling and Optimization Methods

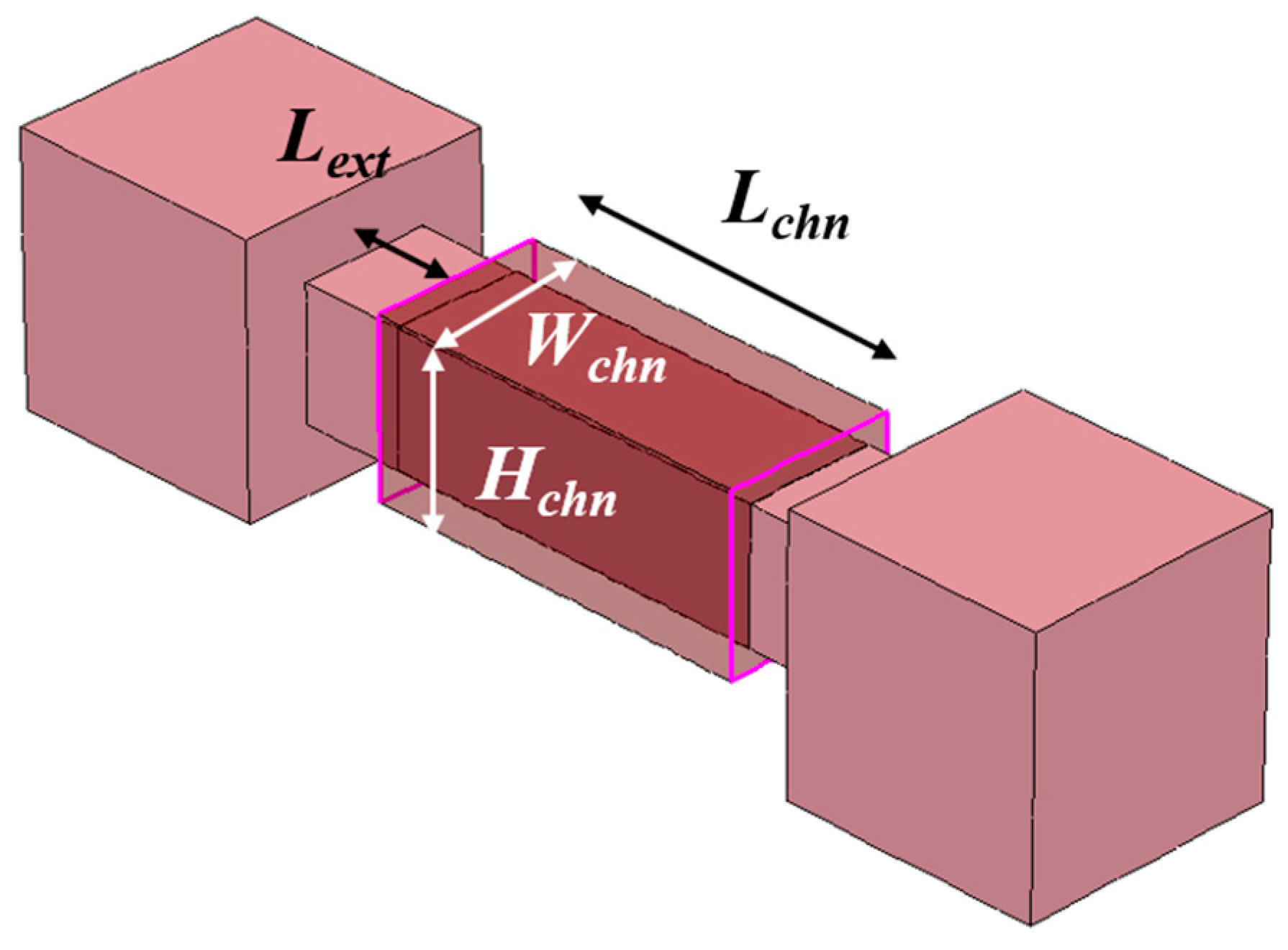

2.1. Simulation Environment

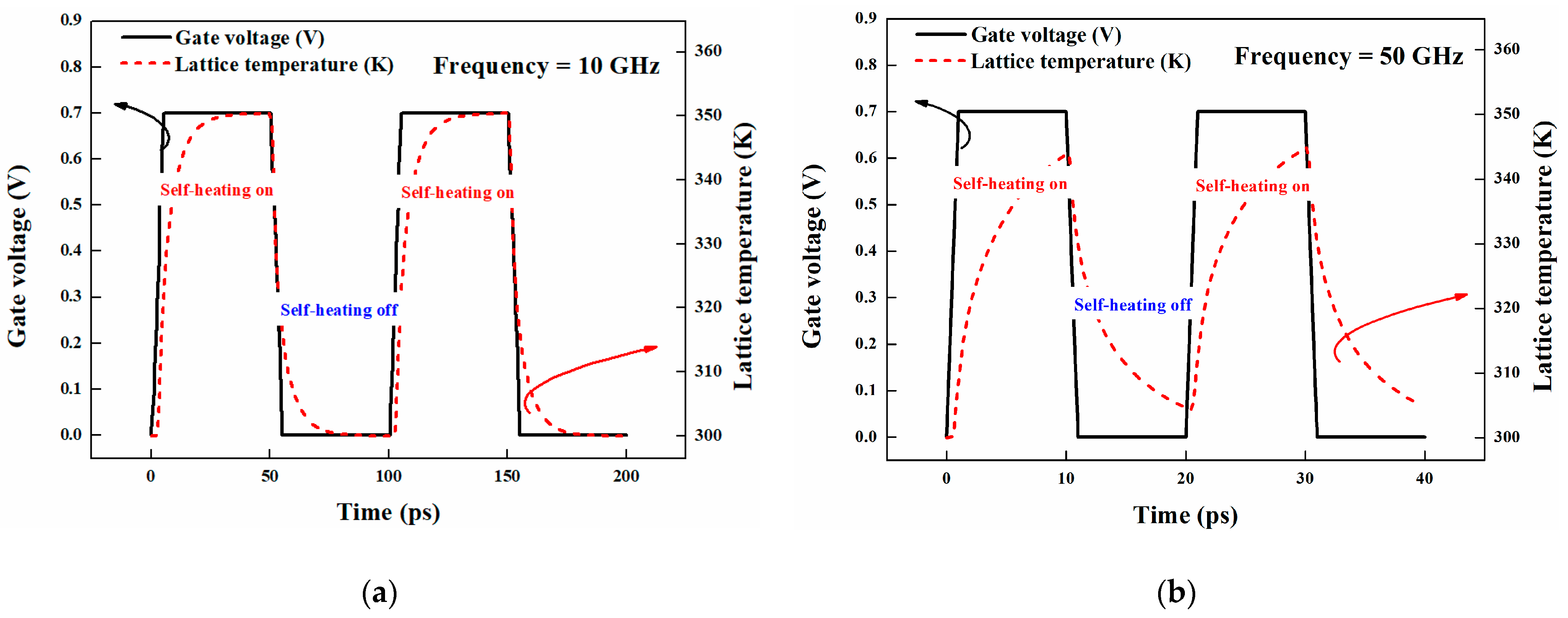

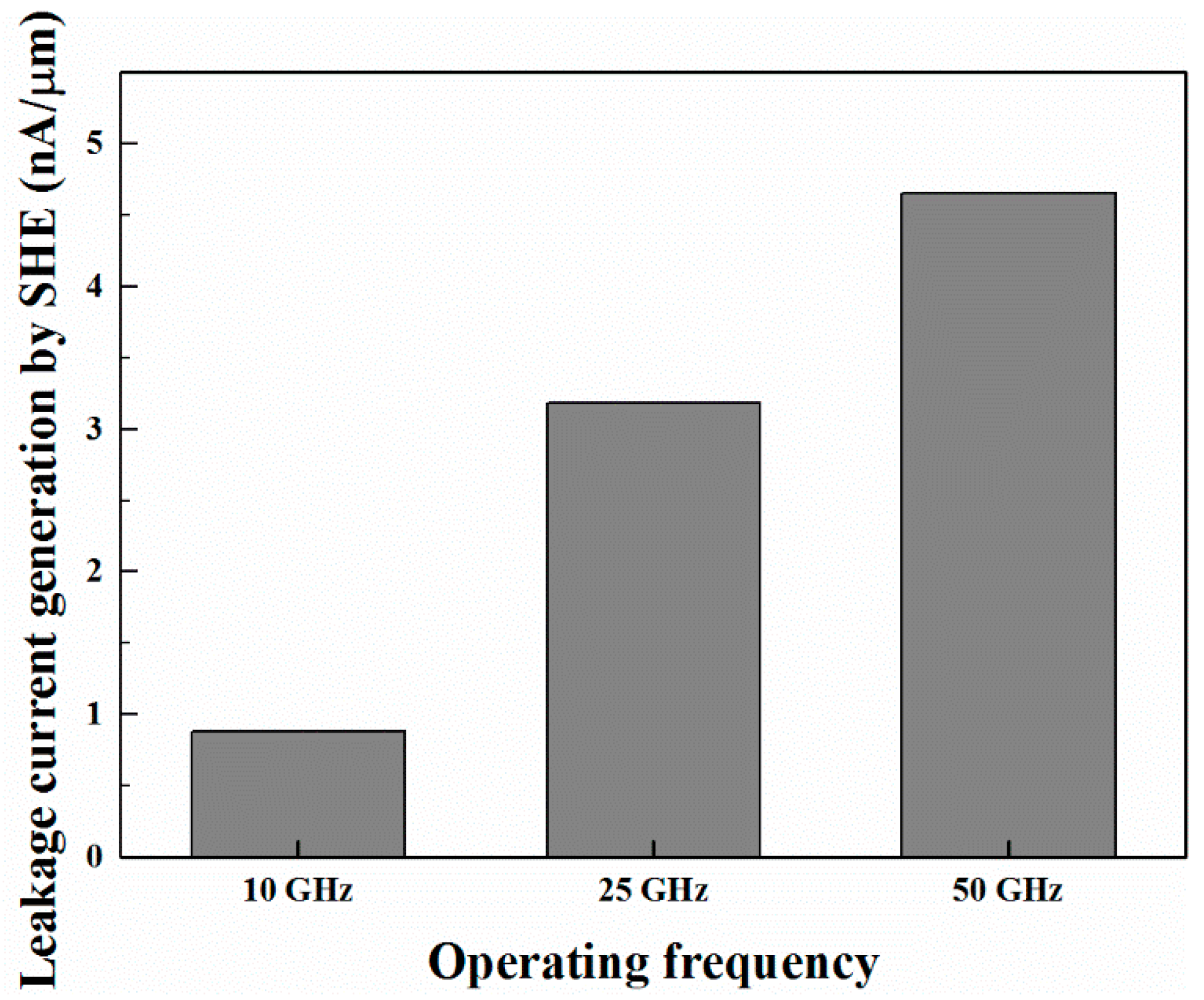

2.2. Thermal Characteristics of GAAFETs

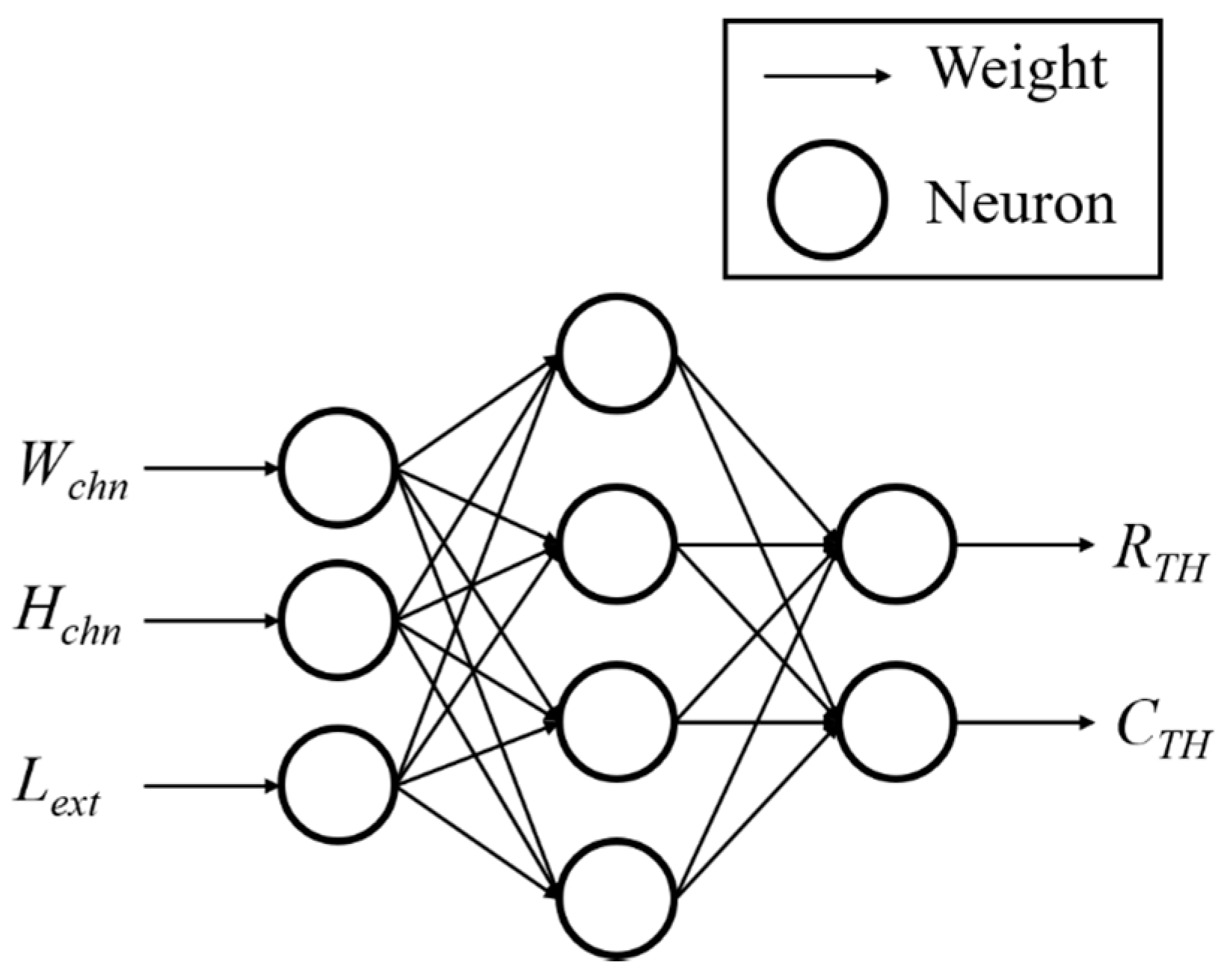

2.3. Neural Network Modeling

2.4. Optimization under Constrained Conditions

3. Results and Discussion

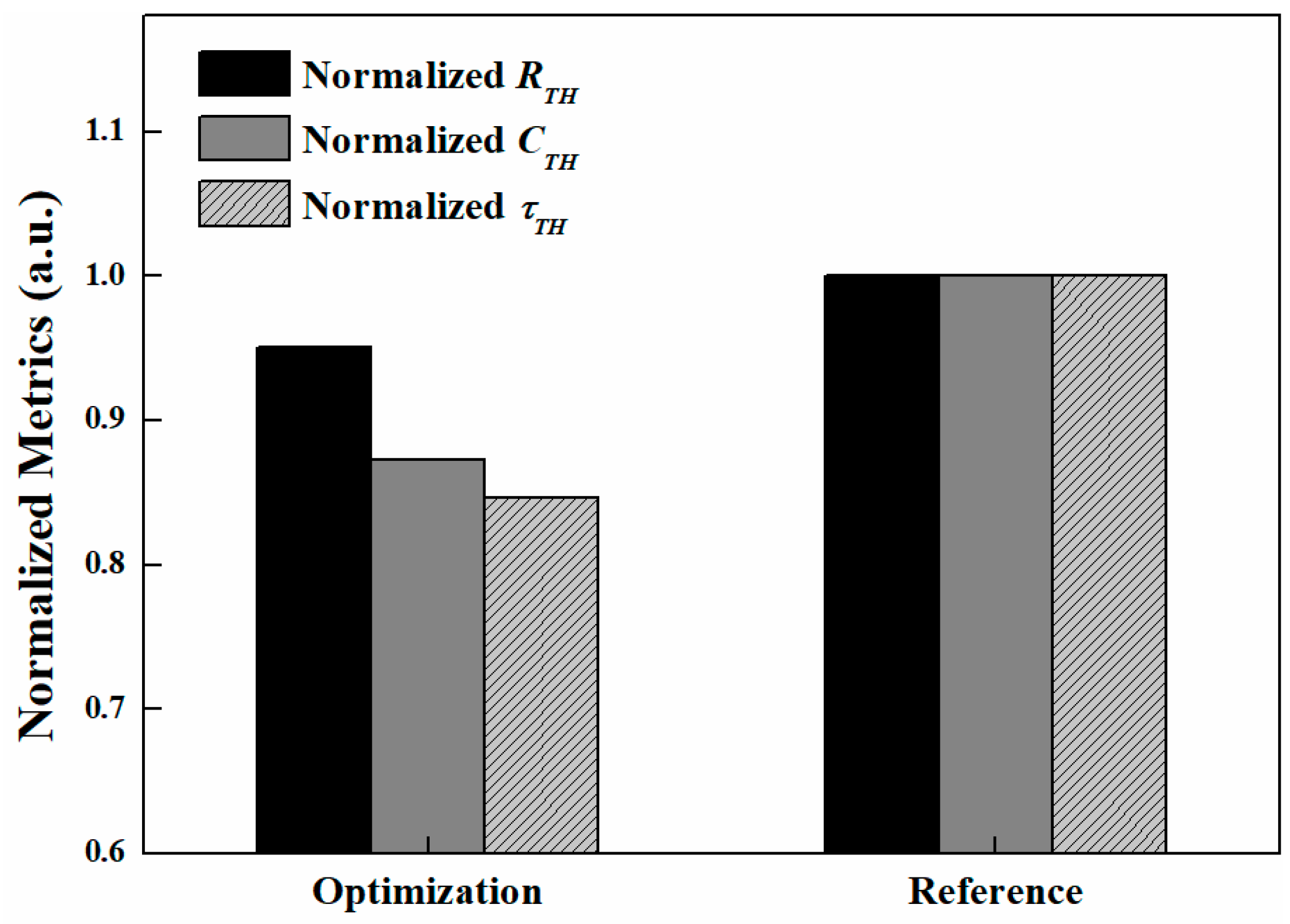

3.1. Optimization Results from Genetic Algorithm

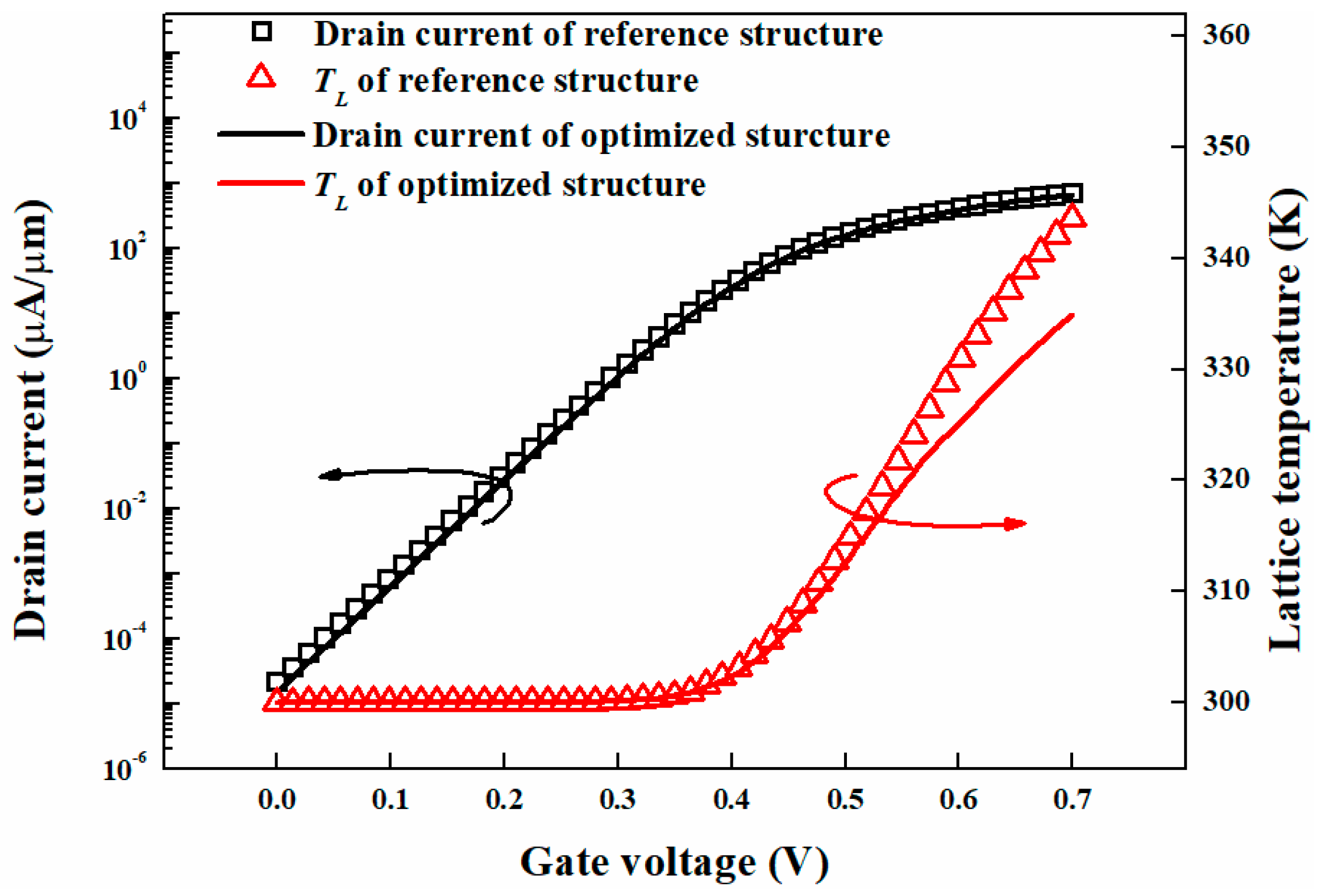

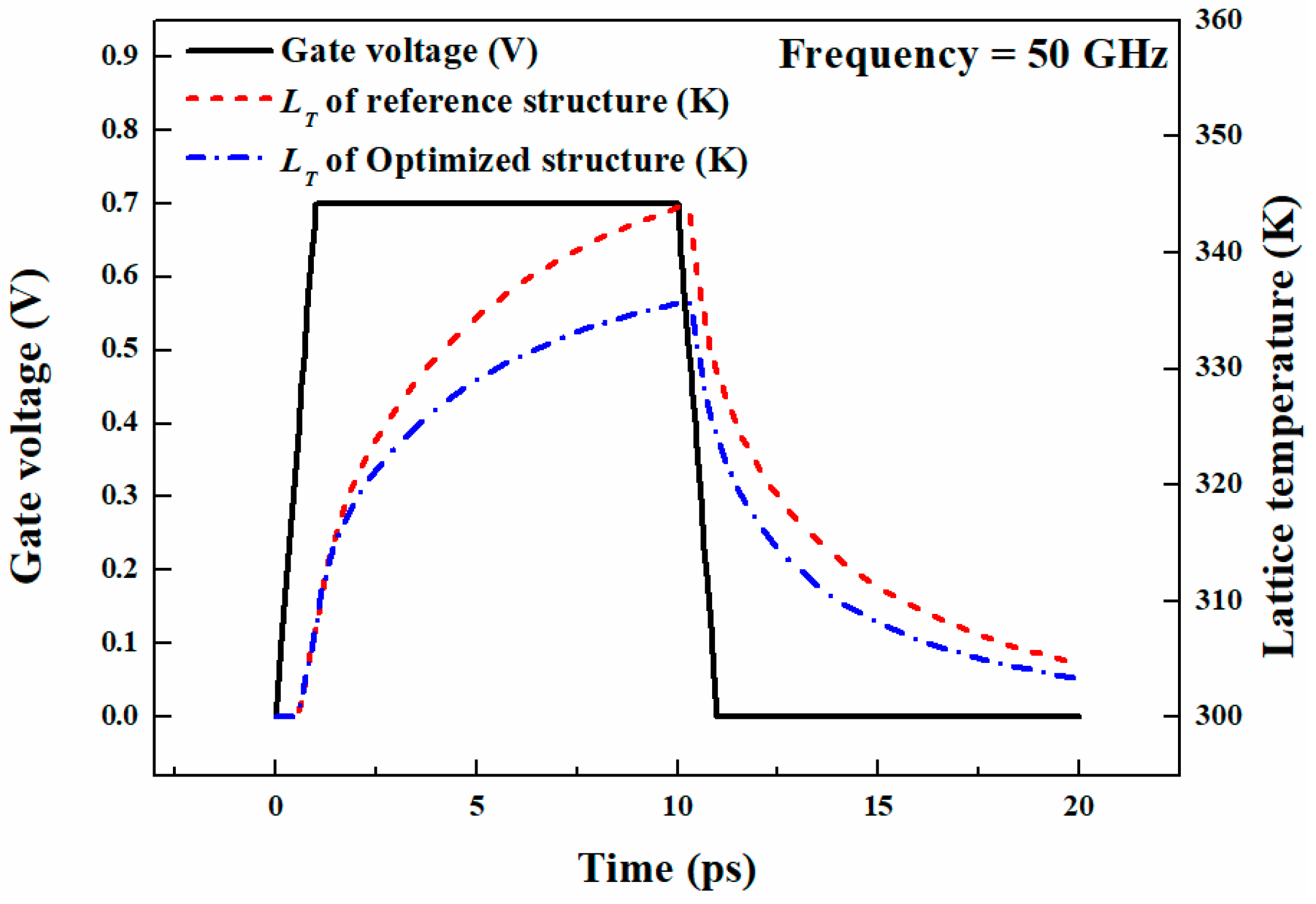

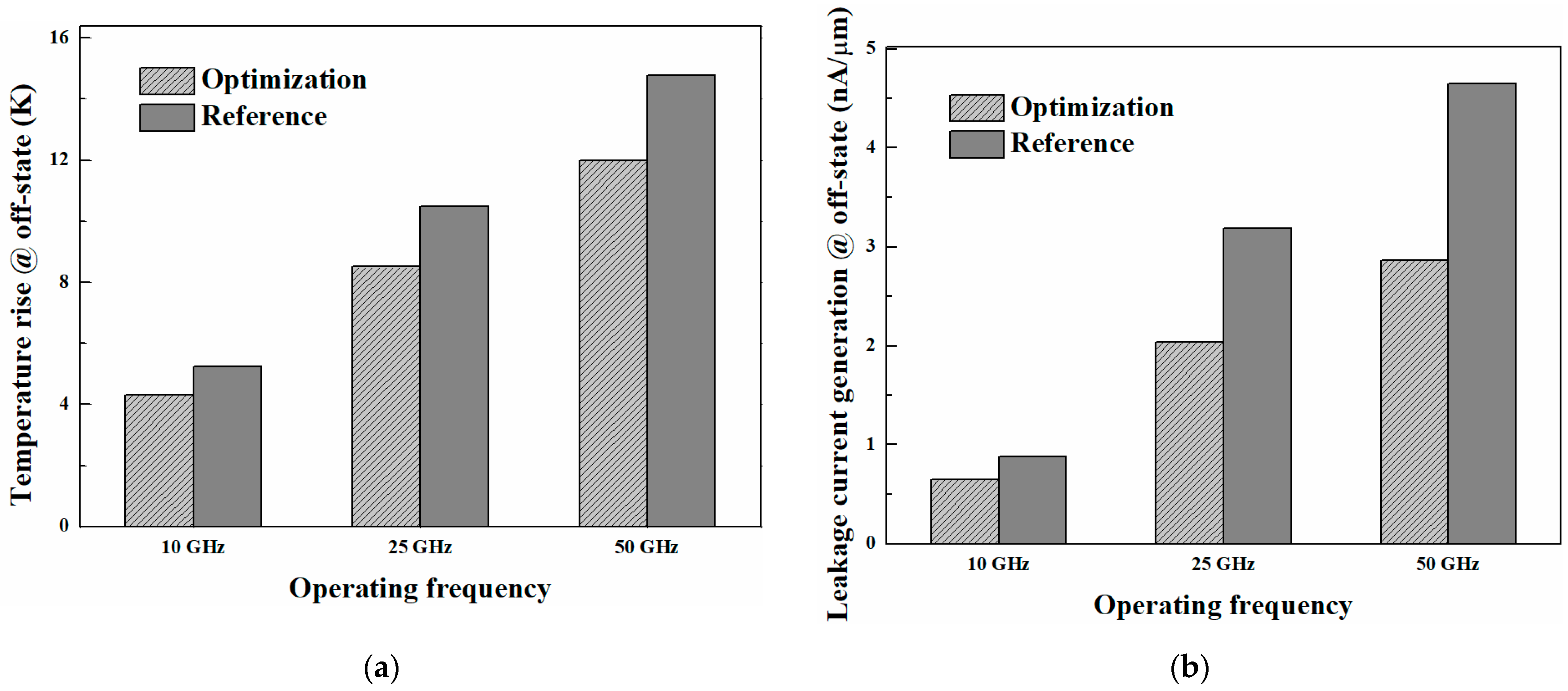

3.2. Thermal Characteristics after Optimization

4. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Ko, K.; Lee, J.K.; Kang, M.; Jeon, J.; Shin, H. Prediction of process variation effect for ultrascaled GAA vertical FET devices using a machine learning approach. IEEE Trans. Electron Devices 2019, 66, 4474–4477. [Google Scholar] [CrossRef]

- Lim, J.; Shin, C. Machine Learning (ML)-Based Model to Characterize the Line Edge Roughness (LER)-Induced Random Variation in FinFET. IEEE Access 2020, 8, 158237–158242. [Google Scholar] [CrossRef]

- Mehta, K.; Wong, H.-Y. Prediction of FinFET Current-Voltage and Capacitance-Voltage Curves using Machine Learning with Autoencoder. IEEE Electron Device Lett. 2020, 42, 136–139. [Google Scholar] [CrossRef]

- Moroz, V.; Smith, L.; Huang, J.; Choi, M.; Ma, T.; Liu, J.; Zhang, Y.; Lin, X.-W.; Kawa, J.; Saad, Y. Modeling and optimization of group IV and III–V FinFETs and nano-wires. In Proceedings of the 2014 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2014; pp. 7.4.1–7.4.4. [Google Scholar]

- Wong, H.Y.; Xiao, M.; Wang, B.; Chiu, Y.K.; Yan, X.; Ma, J.; Sasaki, K.; Wang, H.; Zhang, Y. TCAD-machine learning framework for device variation and operating temperature analysis with experimental demonstration. IEEE J. Electron Devices Soc. 2020, 8, 992–1000. [Google Scholar] [CrossRef]

- Park, J.; Lee, J.K.; Shin, H. Machine learning method to predict threshold voltage distribution by read disturbance in 3D NAND Flash Memories. Jpn. J. Appl. Phys. 2020, 59, 081003. [Google Scholar] [CrossRef]

- Sentaurus Device User Guide, Version L-2016.03; Synopsys TCAD Sentaurus: San Jose, CA, USA, 2016.

- Park, C.; Yun, I. Degradation of off-phase leakage current of FinFETs and Gate-All-Around FETs Induced by the self-heating effect in the high-frequency operation regime. IEEE Trans. Nanotechnol. 2020, 19, 308–314. [Google Scholar] [CrossRef]

- Wu, Y.-C.; Jhan, Y.-R. Introduction of synopsys sentaurus TCAD simulation. In 3D TCAD Simulation for CMOS Nanoeletronic Devices; Springer: Berlin/Heidelberg, Germany, 2018; pp. 1–17. [Google Scholar]

- Yoon, J.-S.; Lee, S.; Yun, H.; Baek, R.-H. Digital/Analog Performance Optimization of Vertical Nanowire FETs Using Machine Learning. IEEE Access 2021, 9, 29071–29077. [Google Scholar] [CrossRef]

- Zheng, P.; Connelly, D.; Ding, F.; Liu, T.-J.K. FinFET evolution toward stacked-nanowire FET for CMOS technology scaling. IEEE Trans. Electron Devices 2015, 62, 3945–3950. [Google Scholar] [CrossRef]

- Bude, J. MOSFET modeling into the ballistic regime. In Proceedings of the 2000 International Conference on Simulation Semiconductor Processes and Devices (Cat. No. 00TH8502), Seattle, WA, USA, 6–8 September 2000; pp. 23–26. [Google Scholar]

- Karlik, B.; Olgac, A.V. Performance analysis of various activation functions in generalized MLP architectures of neural networks. Int. J. Artif. Intell. Expert Syst. 2011, 1, 111–122. [Google Scholar]

- Khandelwal, S.; Duarte, J.P.; Medury, A.S.; Venugopalan, S.; Paydavosi, N.; Lu, D.D.; Lin, C.-H.; Dunga, M.; Yao, S.; Morshed, T. BSIM-CMG 110.0.0: Multi-Gate MOSFET Compact Model: Technical Manual; BSIM Group UC Berkeley: Berkeley, CA, USA, 2015. [Google Scholar]

- Kompala, B.K.; Kushwaha, P.; Agarwal, H.; Khandelwal, S.; Duarte, J.-P.; Hu, C.; Chauhan, Y.S. Modeling of nonlinear thermal resistance in FinFETs. Jpn. J. Appl. Phys. 2016, 55, 04ED11. [Google Scholar] [CrossRef]

- Kumar, U.S.; Rao, V.R. A thermal-aware device design considerations for nanoscale SOI and bulk FinFETs. IEEE Trans. Electron Devices 2015, 63, 280–287. [Google Scholar] [CrossRef]

- Lombardi, C.; Manzini, S.; Saporito, A.; Vanzi, M. A physically based mobility model for numerical simulation of nonplanar devices. IEEE Trans. Comput.-Aided Des. Integr. Circ. Syst. 1988, 7, 1164–1171. [Google Scholar] [CrossRef]

- Myeong, I.; Son, D.; Kim, H.; Shin, H. Analysis of self heating effect in DC/AC mode in multi-channel GAA-field effect transistor. IEEE Trans. Electron Devices 2019, 66, 4631–4637. [Google Scholar] [CrossRef]

- Reggiani, S.; Gnani, E.; Gnudi, A.; Rudan, M.; Baccarani, G. Low-field electron mobility model for ultrathin-body SOI and double-gate MOSFETs with extremely small silicon thicknesses. IEEE Trans. Electron Devices 2007, 54, 2204–2212. [Google Scholar] [CrossRef]

- Wang, L.; Brown, A.R.; Nedjalkov, M.; Alexander, C.; Cheng, B.; Millar, C.; Asenov, A. Impact of self-heating on the statistical variability in bulk and SOI FinFETs. IEEE Trans. Electron Devices 2015, 62, 2106–2112. [Google Scholar] [CrossRef] [Green Version]

- Foresee, F.D.; Hagan, M.T. Gauss-Newton approximation to Bayesian learning. In Proceedings of the International Conference on Neural Networks (ICNN’97), Houston, TX, USA, 12 June 1997; pp. 1930–1935. [Google Scholar]

- Hecht-Nielsen, R. Theory of the backpropagation neural network. In Neural Networks for Perception; Elsevier: Amsterdam, The Netherlands, 1992; pp. 65–93. [Google Scholar]

- Makovejev, S.; Olsen, S.; Raskin, J.-P. RF extraction of self-heating effects in FinFETs. IEEE Trans. Electron Devices 2011, 58, 3335–3341. [Google Scholar] [CrossRef]

- Park, C.; Yun, I. Thermal modeling of 7 nm node bulk fin-shaped field-effect transistors for device structure-aware design. Semicond. Sci. Technol. 2018, 33, 115014. [Google Scholar] [CrossRef]

| Parameter | GAAFET |

|---|---|

| Channel length (Lchn) | 15 nm |

| Channel Width (Wchn) | 5 nm |

| Channel Height (Hchn) | 5 nm |

| Extension length (Lext) | 4 nm |

| Effective Oxide Thickness (EOT) | 0.8 nm |

| Source/Drain Doping | cm−3 |

| Channel Doping | cm−3 |

| Parameter | GAAFET from [3,4,5] | GAAFET, Our Simulation |

|---|---|---|

| VDD | 0.7 V | 0.7 V |

| Ion.sat | 610–702 μA/μm | 695 μA/μm |

| Ioff.sat | 20 pA/μm | 21 pA/μm |

| Vth | 0.3–0.4 V | 0.35 V |

| SS | 64–71 mV/dec | 62.76 mV/dec |

| Wchn [nm] | Hchn [nm] | Lext [nm] | τTH [ps] |

|---|---|---|---|

| 7.00 | 3.00 | 23.15 | 58.96 |

| 6.88 | 3.12 | 23.09 | 58.70 |

| 5.96 | 4.04 | 21.85 | 57.11 |

| 5.45 | 4.45 | 18.64 | 55.53 |

| … | … | … | … |

| 3.10 | 6.90 | 9.55 | 43.46 |

| 3.06 | 6.94 | 4.25 | 33.09 |

| 3.00 | 7.00 | 4.00 | 32.25 |

| 3.00 | 7.00 | 4.00 | 32.25 |

| TCAD Result | GA Result | |

|---|---|---|

| Wchn [nm] | 3 | 3 |

| Hchn [nm] | 7 | 7 |

| Lext [nm] | 4 | 4 |

| RTH [K/μW] | 4.09 | 4.16 |

| CΤH [zJ/K] | 7.87 | 7.75 |

| τTH [ps] | 31.91 | 32.25 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Park, C.; Yun, I. Optimization of Self-Heating Driven Leakage Current Properties of Gate-All-Around Field-Effect Transistors Using Neural Network Modeling and Genetic Algorithm. Electronics 2021, 10, 2570. https://doi.org/10.3390/electronics10212570

Park C, Yun I. Optimization of Self-Heating Driven Leakage Current Properties of Gate-All-Around Field-Effect Transistors Using Neural Network Modeling and Genetic Algorithm. Electronics. 2021; 10(21):2570. https://doi.org/10.3390/electronics10212570

Chicago/Turabian StylePark, Chuntaek, and Ilgu Yun. 2021. "Optimization of Self-Heating Driven Leakage Current Properties of Gate-All-Around Field-Effect Transistors Using Neural Network Modeling and Genetic Algorithm" Electronics 10, no. 21: 2570. https://doi.org/10.3390/electronics10212570