A Low-Cost and Efficient Microstrip-Fed Air-Substrate-Integrated Waveguide Slot Array

Abstract

:1. Introduction

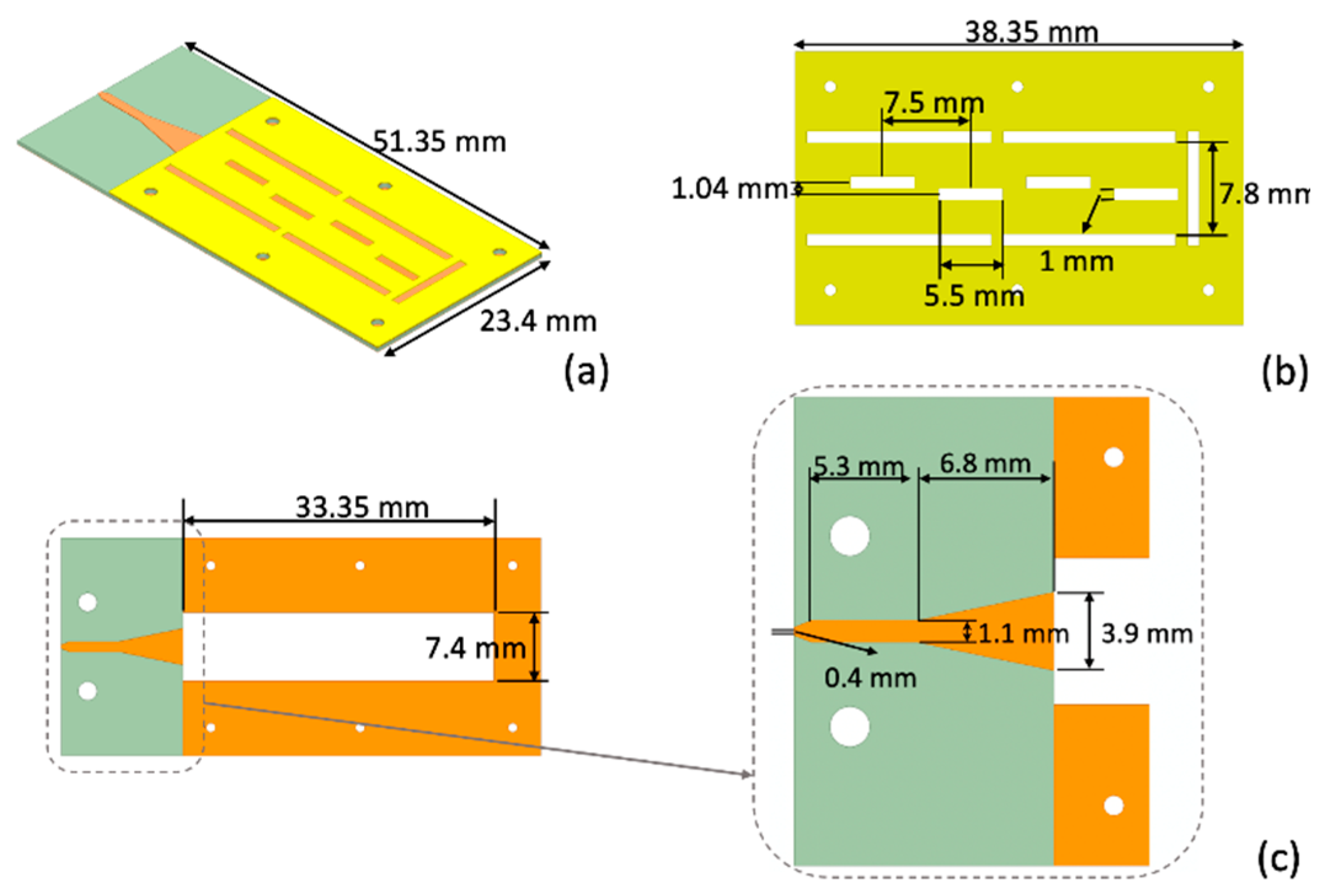

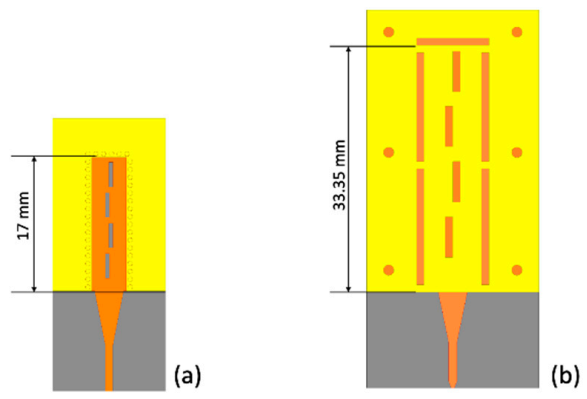

2. Antenna Array Design

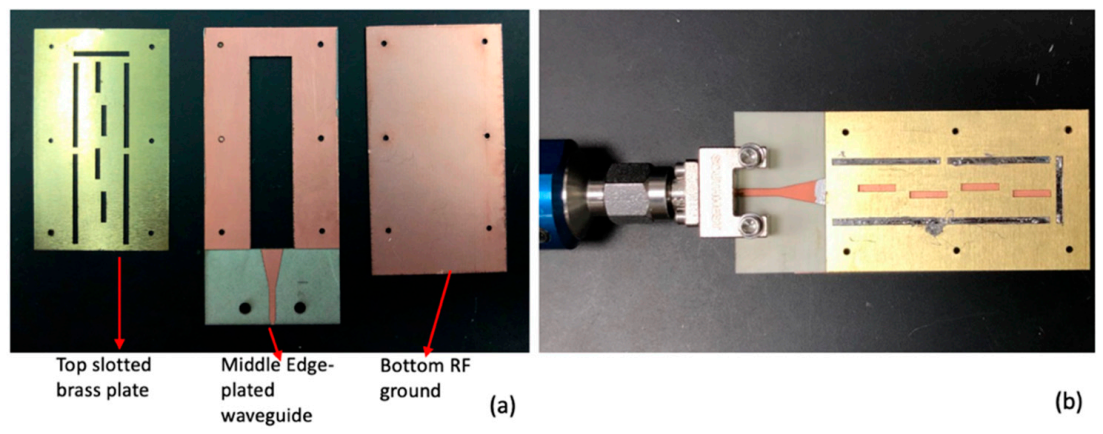

3. Antenna Array Fabrication

4. Results and Discussion

4.1. Simulated and Measured Antenna Performance

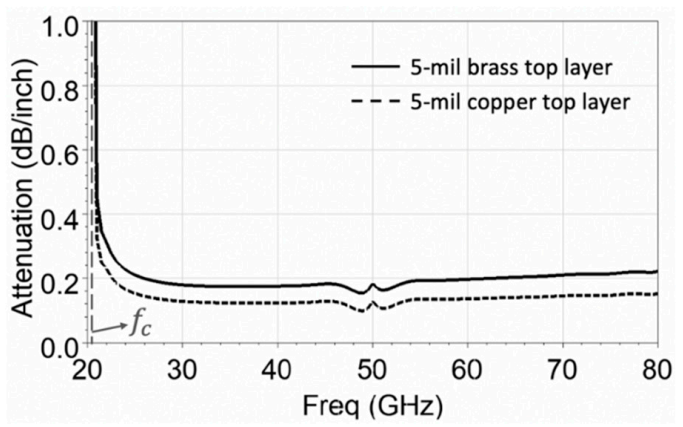

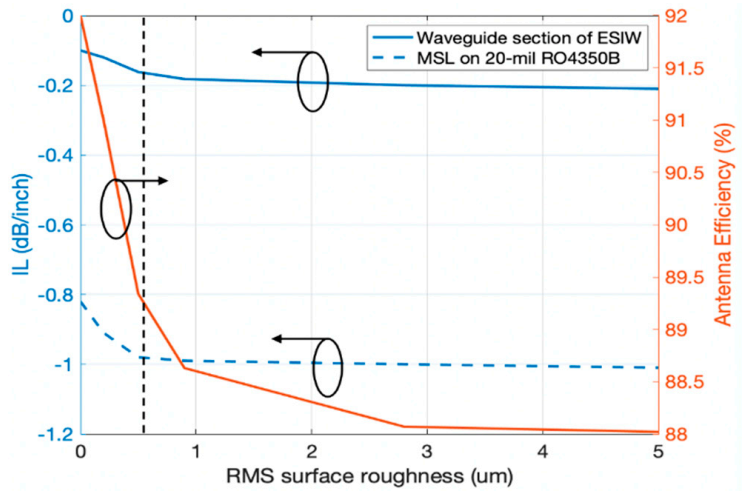

4.2. Surface Roughness Model

4.3. Antenna Performance Comparison

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Deslandes, D.; Wu, K. Integrated microstrip and rectangular waveguide in planar form. IEEE Microw. Wirel. Compon. Lett. 2001, 11, 68–70. [Google Scholar] [CrossRef]

- Yan, L.; Hong, W.; Hua, G.; Chen, J.; Wu, K.; Cui, T.J. Simulation and experiment on SIW slot array antennas. IEEE Microw. Wirel. Compon. Lett. 2004, 14, 446–448. [Google Scholar] [CrossRef]

- Ding, Y.; Wu, K. A 4 × 4 Ridge Substrate Integrated Waveguide (RSIW) Slot Array Antenna. IEEE Antennas Wirel. Propag. Lett. 2009, 8, 561–564. [Google Scholar] [CrossRef]

- Navarro, D.V.; Carrera, L.F.; Baquero, M. A SIW slot array antenna in Ku band. In Proceedings of the Fourth European Conference on Antennas and Propagation, Barcelona, Spain, 12–16 April 2010; pp. 1–4. [Google Scholar]

- Xu, J.; Chen, Z.N.; Qing, X.; Hong, W. 140-GHz TE20-Mode Dielectric-Loaded SIW Slot Antenna Array in LTCC. IEEE Trans. Antennas Propag. 2012, 61, 1784–1793. [Google Scholar] [CrossRef]

- Ranjkesh, N.; Shahabadi, M. Reduction of dielectric losses in substrate integrated waveguide. Electron. Lett. 2006, 42, 1230–1231. [Google Scholar] [CrossRef]

- Parment, F.; Ghiotto, A.; Vuong, T.-P.; Duchamp, J.-M.; Wu, K. Air-Filled Substrate Integrated Waveguide for Low-Loss and High Power-Handling Millimeter-Wave Substrate Integrated Circuits. IEEE Trans. Microw. Theory Tech. 2015, 63, 1228–1238. [Google Scholar] [CrossRef]

- Parment, F.; Ghiotto, A.; Vuong, T.-P.; Duchamp, J.-M.; Wu, K. Millimetre-wave air-filled substrate integrated waveguide slot array antenna. Electron. Lett. 2015, 53, 704–706. [Google Scholar] [CrossRef]

- Groiss, S.; Bardi, I.; Biro, O.; Preis, K.; Richter, K. Parameters of lossy cavity resonators calculated by the finite element method. IEEE Trans. Magn. 1996, 32, 894–897. [Google Scholar] [CrossRef]

- Horn, A.F.; Reynolds, J.W.; LaFrance, P.A. Sonnet Software: Effect of Conductor Profile on the Insertion Loss, Phase Constant, and Dispersion in Thin High Frequency Transmission Lines. Available online: https://www.sonnetsoftware.com/support/downloads/publications/5-TA1_Al_Horn.pdf (accessed on 9 January 2020).

- Qi, Z.; Li, X.; Xiao, J.; Zhu, H. Low-Cost Empty Substrate Integrated Waveguide Slot Arrays for Millimeter-Wave Applications. IEEE Antennas Wirel. Propag. Lett. 2019, 18, 1021–1025. [Google Scholar] [CrossRef]

- Xu, J.; Chen, Z.N.; Qing, X. CPW Center-Fed Single-Layer SIW Slot Antenna Array for Automotive Radars. IEEE Trans. Antennas Propag. 2014, 62, 4528–4536. [Google Scholar] [CrossRef]

- Miralles, E.; Belenguer, A.; Matéo, J.; Torres, A.; Esteban, H.; Borja, A.L.; Boria, V.E. Slotted ESIW antenna with high efficiency for a MIMO radar sensor. Radio Sci. 2018, 53, 605–610. [Google Scholar] [CrossRef]

| Slot Array Type | Realized Gain (dBi) | Number of Elements | Center Frequency (GHz) | Efficiency | Compatibility with Planar Circuits | |

|---|---|---|---|---|---|---|

| SIW [2] | 15.7 | 10.0 | n.a. | 6% | Yes | |

| SIW [12] | 22.8 | 24.0 | 67% | 1.7% | Yes | |

| AFSIW [8] | 11.5 1 | 30.5 | 97.4% 1,2 | 8.7% | Yes | |

| ESIW with Cavity Loading [11] | 15.5 | 38.5 | 90.7% | 12.7% | No | |

| ESIW [13] | 15 | 16.25 | 90.78% | 4.3% | Yes | |

| ASIW (this work) | 10.1 (11.3 1,2) | 28.15 | 84% 3 (98% 1,2) | 10.7% | Yes |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Li, L.; Yan, J.-B. A Low-Cost and Efficient Microstrip-Fed Air-Substrate-Integrated Waveguide Slot Array. Electronics 2021, 10, 338. https://doi.org/10.3390/electronics10030338

Li L, Yan J-B. A Low-Cost and Efficient Microstrip-Fed Air-Substrate-Integrated Waveguide Slot Array. Electronics. 2021; 10(3):338. https://doi.org/10.3390/electronics10030338

Chicago/Turabian StyleLi, Linfeng, and Jie-Bang Yan. 2021. "A Low-Cost and Efficient Microstrip-Fed Air-Substrate-Integrated Waveguide Slot Array" Electronics 10, no. 3: 338. https://doi.org/10.3390/electronics10030338

APA StyleLi, L., & Yan, J.-B. (2021). A Low-Cost and Efficient Microstrip-Fed Air-Substrate-Integrated Waveguide Slot Array. Electronics, 10(3), 338. https://doi.org/10.3390/electronics10030338