1. Introduction

Permanent magnet synchronous motors (PMSMs) have been used in high-performance AC motor drives in industrial as well as domestic applications due to the advantages of high efficiency, a high torque-to-weight ratio and a wide range of speed operations [

1,

2,

3]. The motor drive system needs to achieve the desired speed and a smooth transition corresponding to the change in the motor load condition, depending on its applications. With the progress of power electronics and microprocessor techniques, different control concepts have been proposed to achieve the desired PMSM response.

Conventional control techniques such as field-oriented control (FOC) and direct torque control (DTC) are widely used in industrial applications for PMSM control [

4,

5]. However, in the case of conventional control, the system complexity increases with the inclusion of the control parameters. DTC has good dynamic performance; however, it has poor steady-state performance. FOC has good steady-state performance compared to that of DTC. Due to the absence of the hysteresis band, the digital implementation of FOC is easier. However, FOC utilizes a cascaded PI controller for its implementation, and there are at least four parameters it needs to tune separately. With a change in working conditions, the drive performance may worsen [

6]. The inner current control loop has a crucial role in motor drive systems to generate the reference voltage, which ultimately generates the switching signal. For small- and medium-power motor drive systems, the current-loop bandwidth is restricted due to a limited switching frequency, which directly impacts the system dynamic performance [

7]. Moreover, the motor current is regulated by the terminal voltage applied by an inverter. Above the medium-speed range, if an abrupt change in the reference is applied, the reference voltage generated from the current control loop may undergo saturation, which, finally, leads to degradation in the current regulation [

8] and a worsened motor performance. To achieve a fast dynamic response with better current regulation, a better controller is always desirable.

Model predictive control (MPC) is an advanced control strategy. It has become an attractive solution for PMSM control and can improve the dynamic response by predicting the next step current [

9]. The MPC possesses attractive features such as direct use of the system model and a simultaneous multiple constraint handling nature to deal with multiple control parameters [

10,

11,

12]. Considering these appealing characteristics, MPC is gaining attention among researchers and also has been applied in a wide variety of drive applications. The MPC implementation methodology utilizes the mathematical model of the plant to predict its future behavior, and an optimization function is used for the selection of the switching signal. The two main categories of MPC are continuous-control-set MPC (CS-MPC) and finite-control-set MPC (FS-MPC) [

13]. CS-MPC generates switching signals to the power converter by calculating a continuous-controlled variable through a modulator with a constant switching frequency [

14]. On the other hand, FS-MPC considers the finite set of the possible switching states of the power converter for the generation of switching signals for the power devices [

15,

16]. Compared with CS-MPC, the major advantage of FS-MPC is that it can directly generate the switching signal by optimizing the control parameter without any modulation stage. Finite-set-predictive torque control (FS-PTC) with discrete space vector modulation (DSVM) for a PMSM drive is presented in [

17]. Moreover, a new preselection strategy is proposed to reduce the computational numerations from 37 to 6 voltage vectors, reduce the torque and flux ripples and ultimately achieve robust characteristics against parameter variations. In [

18], a total harmonic distortion (THD)-oriented FCS-MPC controller is designed for single-phase inverters. To achieve this goal, a modified cost function is constructed using a linear combination, with weight factors of the current fundamental tracking error and an instantaneous THD value. A FS-MPC strategy with distribution in harmonic spectra similar to a PWM controller is proposed in [

19]. This strategy reduces the number of commutations and also fixes the harmonic spectra. However, the cost function optimization problem is computed by predicting all the possible switching states of the power converter in every sampling period. With an increase in the complexity of the converter system, the system may undergo delays, which ultimately degrades the system performance [

20,

21].

The field-programmable gate array (FPGA) has the advantage of parallel processing, which shortens the computational time, ultimately to leading a decrease in the control delay and better system performance [

22,

23]. Moreover, the FPGA is considered the better option for controller designing and prototyping due to its fast computation ability, embedded processor and shorter design cycle [

24,

25]. In [

26], an implementation methodology using the hardware description language (HDL) coder from MathWorks is presented with an automated workflow for implementing long-horizon FCS-MPC for a PMSM drive system. At present, a model-based design (MBD) for the FPGA implementation of complex control systems is attractive because of its time-saving capacity and great flexibility in simulation and debugging [

27,

28,

29].

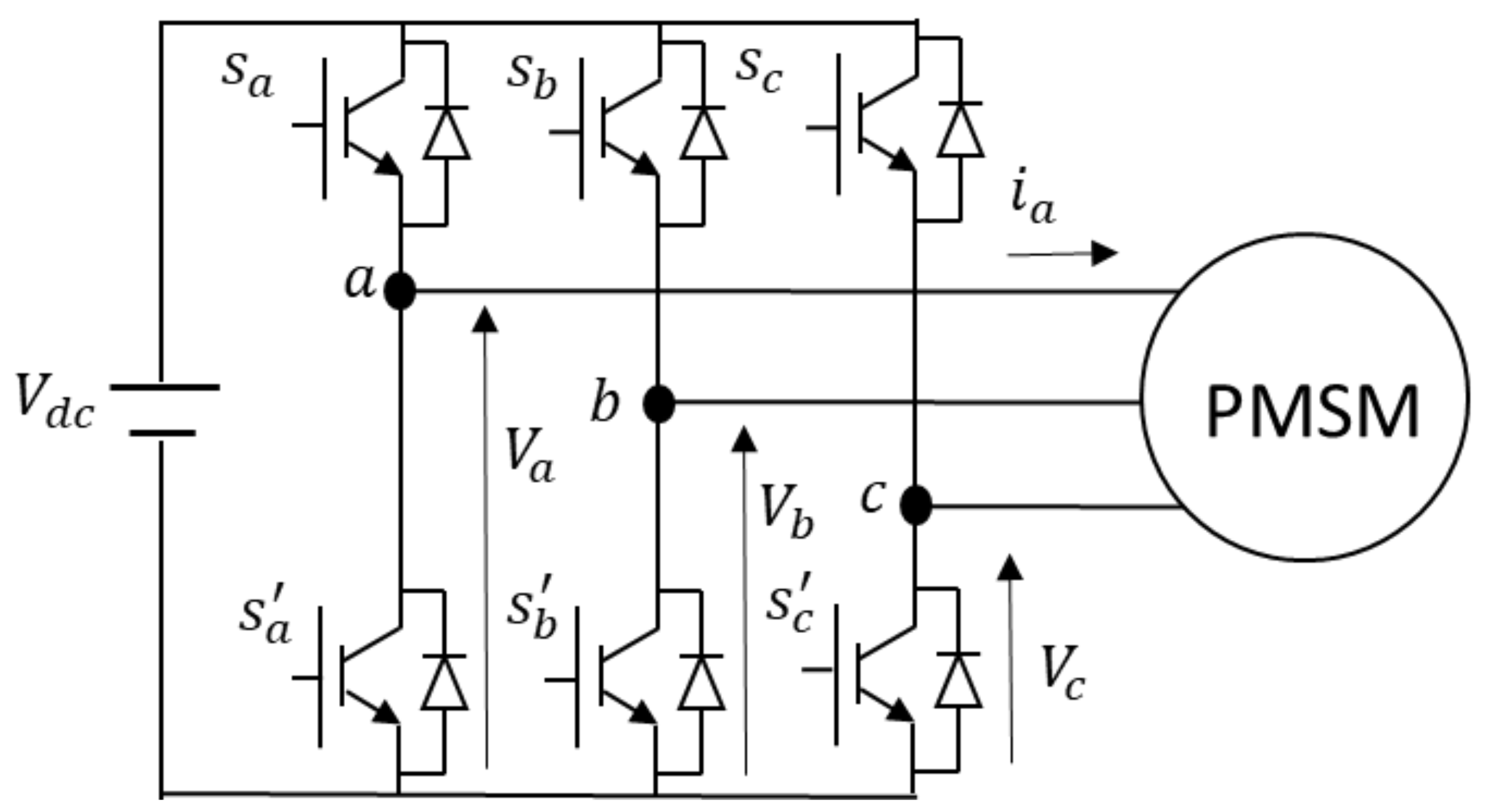

This paper presents the design and development of FS-MPC for a PMSM drive system that can be utilized in real-time FPGA implementations. The FS-MPC algorithm is developed for a three-phase, two-level voltage source inverter (VSI)-fed PMSM drive system using an optimization function in terms of current. The step-by-step design and development of the controller for the motor drive system are explained. The motor dynamics response is analyzed corresponding to different sampling frequencies. To analyze the dynamic behavior of the motor, a step change in the reference speed and load disturbance is introduced. Moreover, for the steady-state analysis, the steady-state error and harmonics in the motor current are considered corresponding to different sampling frequencies. The system performance is validated by comparing it with a linear PI controller. Furthermore, a model-based approach is adopted for the system implementation for the modeling of FS-MPC. For the real-time implementation of the FPGA, the controller is developed in the Xilinx system generator (XSG) environment integrated with MATLAB/Simulink, which automatically generates the HDL code.

The sections of this paper are organized as follows:

Section 2 describes the algorithm of FS-MPC for the PMSM drive system considering the discrete-time mathematical model of the motor and three-phase VSI. In

Section 3, the model-based design and development of the controller in the XSG environment are explained. A FPGA-based system implementation is explained in

Section 4. The real-time implementation of the controller and results, along with a detailed discussion, are presented in

Section 5. Finally,

Section 6 concludes the paper.

4. FPGA-Based System Implementation

The FS-MPC based PMSM drive system in

Figure 6 is designed and developed using the digital control environment of the FPGA. The control requires the sensed motor current and speed for its implementation in the FPGA. The three-phase motor current is sensed through a current sensor and passed through a level shifter. The shifted value of the measured current is fed to the FPGA by using an analog-to-digital converter (ADC). The digitized data from the ADC are synchronized at the rate of the sampling frequency through the ADC interface unit. The encoder is used to sense the motor position and motor angular speed as a pulse, with a resolution of 2048 pulses per revolution. The motor speed and positions can be obtained from this unit by using the position and speed detector. Finally, this parameter is fed to the control unit for the generation of the switching signal. For monitoring and validating, the digital signal is converted to an analog signal by using a digital-to-analog converter (DAC). The control unit, along with the position and speed detector and ADC (DAC) interface unit, is programmed to the FPGA board.

For the implementation of the control unit, the output of the speed control unit is responsible for the motor current prediction; therefore, sequential time synchronization is used within a sampling time. The timing diagram used for the FPGA implementation is shown in

Figure 7. The start signal has a time of 1 μs, and its width is defined by the sampling time

Ts. Consequently, the chip select and the done signal were switched to a high state, and the start signal was switched to a low state after the completion of the conversion of the analog signal to the digital signal by the ADC interface unit. The enable signal was generated with an on-time of

Ton and a delay time of

Td. The done signal in

Figure 7 as an enable signal enables the speed control loop as well as

abc-to-

dq conversion simultaneously to perform parallel computation. The output of the speed control unit (

) and

abc-to-

dq conversion (

idq) is fed to the FS-MPC unit for the implementation of the control algorithm. Furthermore, the enable1 signal with an on-time

Ton of 0.5 μs and a delay time

Td of 1.5 μs from the enable signal enables the FS-MPC unit, as shown in

Figure 8.

5. Experimental Results and Discussion

An experimental setup, as illustrated in

Figure 9, was developed for the real-time implementation and analysis of FS-MPC for a FPGA-based PMSM drive system. The FPGA code was generated automatically through the modeled controller and programmed using dedicated software (Xilinx VIVADO Design Suite) for the real-time operation of FS-MPC. Sampling frequencies of 25 kHz, 50 kHz and 100 kHz were used for the extensive analysis of the impacts of the sampling frequency on the motor performance. The speed controller gain K

pω and K

iω values were kept constant for all the cases. However, considering the different sampling frequencies, the sampling time T

s was multiplied by the K

iω value as: K

iω × T

s. A step change in the reference speed and motor load condition (load disturbance) was introduced to demonstrate the system performance (current and speed) under the transient operation and also analyzed corresponding to the different sampling frequencies. Moreover, the motor current steady-state error and the current harmonic distortion corresponding to the different sampling times were considered to demonstrate the system performance. The controller was validated by comparing it to a conventional control technique (FOC). The system parameters and the component specifications considered for the development of the experimental setup are explained in

Table 2 and

Table 3. For the FPGA-based system implementation, a clock frequency of 100 MHz was considered.

5.1. Change in the Reference Speed

Depending on the applications, the motor may undergo a change in the reference speed. The controller should attain the new reference smoothly with a lower settling time. A step change in the reference speed from 900 rpm to 1200 rpm (low to high speed) and 1200 rpm to 900 rpm (high to low speed) was considered to demonstrate and analyze the performance of the controller for the PMSM drive system.

Figure 10,

Figure 11 and

Figure 12 demonstrate the speed regulation of the PMSM for the sampling frequencies of 25 kHz, 50 kHz and 100 kHz, respectively. The response was expanded from 0.4 s to 0.8 s and 2.6 s to 3 s for a close view of the speed dynamic response for a change in the reference speed from low to high and high to low, respectively. The settling time performance of the speed regulation was better for 100 kHz and 50 kHz compared to 25 kHz. With an increase in the sampling frequency, the error between the reference and the predicted current decreases, which ultimately improves the dynamic performance of the speed response. Furthermore, the motor currents

id and

iq are shown corresponding to the sampling times. Current

iq for the sampling frequency of 100 kHz shows better transient performance. With an increase in the sampling frequency, the controller shows better transient performance. The settling time performance of speed regulation is summarized in

Table 4 in terms of the time required to attain the steady state.

5.2. Change in the Load Condition

The motor system can go under the load disturbance condition as well, and the transient performance of the motor drive system was of concern to attain the desired reference speed smoothly and with a lower settling time. A step change in the electronic load to introduce a load disturbance was employed, which ultimately resulted in a motor current change from 0.5 A to 1 A (low to high) and 1 A to 0.5 A (high to low). The motor speed was kept at 900 rpm for all the operating conditions.

The speed regulation of PMSM under load disturbance in

Figure 13,

Figure 14 and

Figure 15 is demonstrated for the sampling frequencies of 25 kHz, 50 kHz and 100 kHz. The response is expanded for a close view of the speed dynamic response for a change in the load disturbance from low to high and high to low. The settling time performance of the 100 kHz sampling frequency shows better performance for both high to low load and low to high load. The settling time performance of the speed under load disturbance is summarized in

Table 5 considering the time required to attain the steady state.

5.3. Steady-State Error Analysis

In order to analyze the accuracy of the controller, the steady-state error (SSE) of the motor current was considered. A comparative analysis of the SSE was performed corresponding to different sampling frequencies through bar graphs. The SSE is calculated by using the below equations [

30]:

where

and

are the mean values of the current error of the

dq-axis. This error can be calculated as follows:

where,

N is the number of the current samples considered for the calculation of the SSE. The SSE comparison for the sampling frequencies of 25 kHz, 50 kHz and 100 kHz is shown in

Figure 16. The motor was working at a speed of 900 rpm. The motor currents of 0.8 ampere were considered for the calculation of the steady-state error of motor current. The SSE with sampling frequency of 100 kHz and current of 0.8 ampere have the lowest steady state error. The steady-state error decreases with the increase in the sampling frequency and motor current.

5.4. System Performance in Terms of THD

The controller performance (three-phase current harmonics) depends on the switching frequency at which the power devices operate. In the case of FS-MPC, the switching frequency of the power devices is governed by the sampling frequency. Therefore, different sampling frequencies were considered to examine and analyze the controller performance. The maximum switching frequency of FS-MPC is half of the sampling frequency considered for the system implementation. The maximum switching frequency that could be taken for the inverter to use in the experimental system is 50 kHz. Considering this condition, a maximum sampling frequency of 100 kHz can be used for the system implementation. Different sampling frequencies were exercised to investigate the system performance, as shown in

Table 6. For all the cases, the motor was operated at a speed of 900 rpm. A current of 0.7 A was considered for the low-load case and 1.2 A for the high load case.

Under higher harmonic conditions, the motor has more iron losses, which ultimately reduce the motor efficiency and service life. Moreover, with an increase in the harmonics, the motor can have noise and vibration. As the switching frequency increases, the harmonics in the current decrease. Therefore, for better performance, the controller should work at a higher switching frequency, meaning a higher sampling frequency in the case of FS-MPC. However, with an increase in the switching frequency, the switching losses increase, which ultimately increases the size of the converter. According to the IEEE standard, a THD current of less than 5% is acceptable. Therefore, by considering both the system performance and the losses, the sampling frequency of 50 kHz can be a better option.

5.5. Comparison with FOC

In order to validate the system behavior of FS-MPC, the dynamic speed response was compared to that of the linear control, FOC. The sampling frequency for both the controllers was kept the same; that is, 100 kHz. The speed controller gain K

pω and K

iω were considered to be the same. The values of the controller gain (speed control and current control) are illustrated in

Table 7. The controller gain value was calculated from the current controller bandwidth by using the following equation:

where

Ti is the electromagnetic time constant of the motor, which can be represented as the ratio of the stator inductance and stator resistance (

Ls/

Rs =

Kp/

Ki);

Kpwm is the equivalent gain of the PWM inverter; and

TΣ = 1/2

fsw. f

sw is the switching frequency considered for the system implementation.

The comparative regulatory behavior of the speed control for the change in speed from 900 rpm to 1200 rpm is illustrated in

Figure 17a for a sampling frequency of 100 kHz. In the case of FOC, the overshoot for the speed change is higher compared to that of the FS-MPC. Moreover, the settling time is also more compared to that of the FCS-MPC. Similarly, the speed response corresponding to the change in the load disturbance is also illustrated in

Figure 17b. The speed response in the case of FOC has a slower response compared to that of the FS-MPC. Moreover, the speed undershoot and overshoot are more than twice as compared to that of FS-MPC. Further, a detailed comparison of the two controllers is presented in

Table 8.