Area Optimization Techniques for High-Density Spin-Orbit Torque MRAMs

Abstract

:1. Introduction

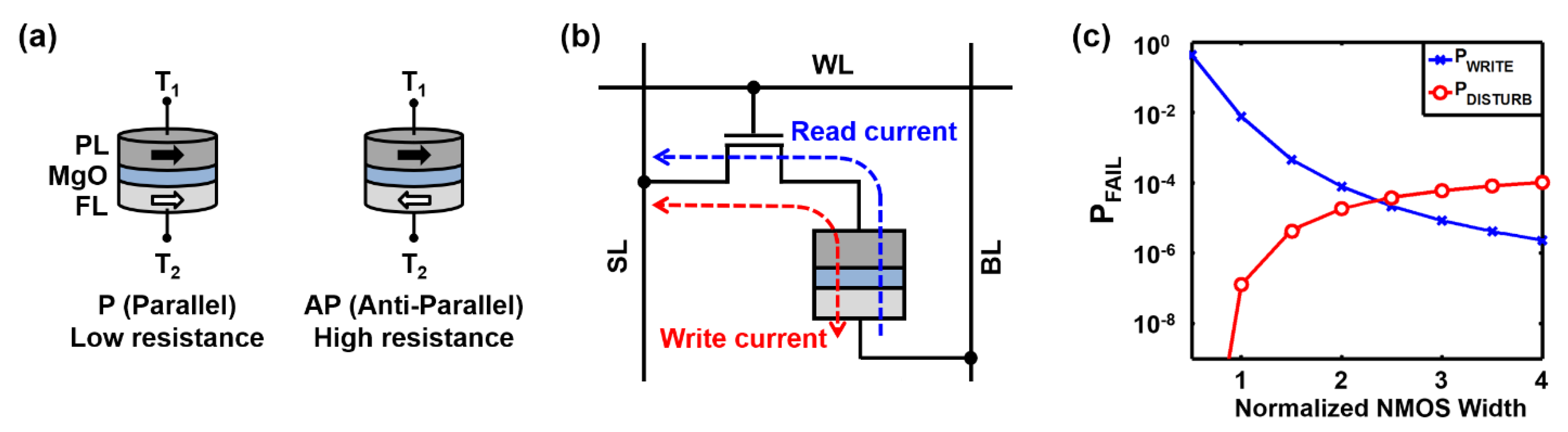

2. SOT-MRAM Fundamentals

3. Proposed SOT-MRAM Designs

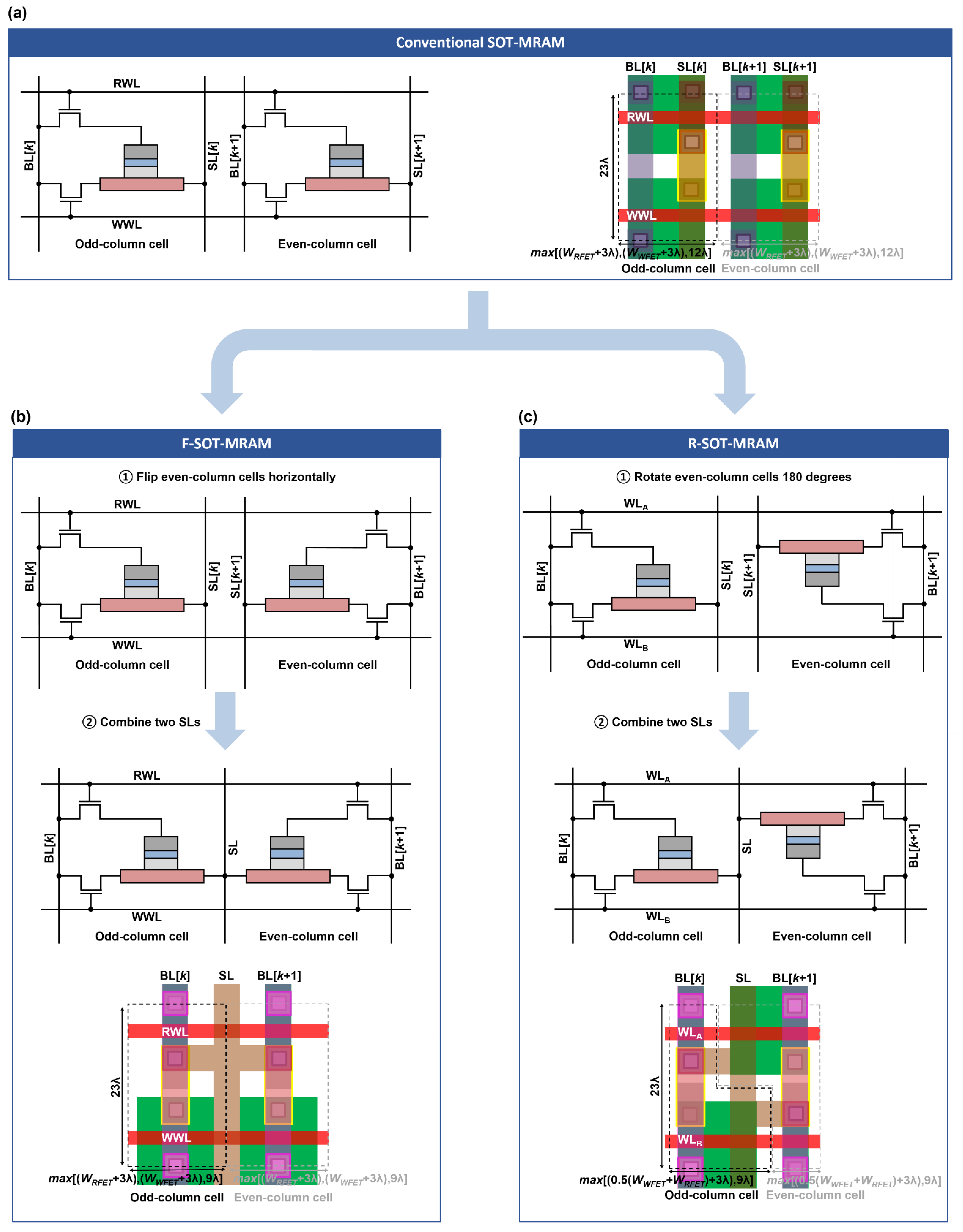

3.1. Basic Idea

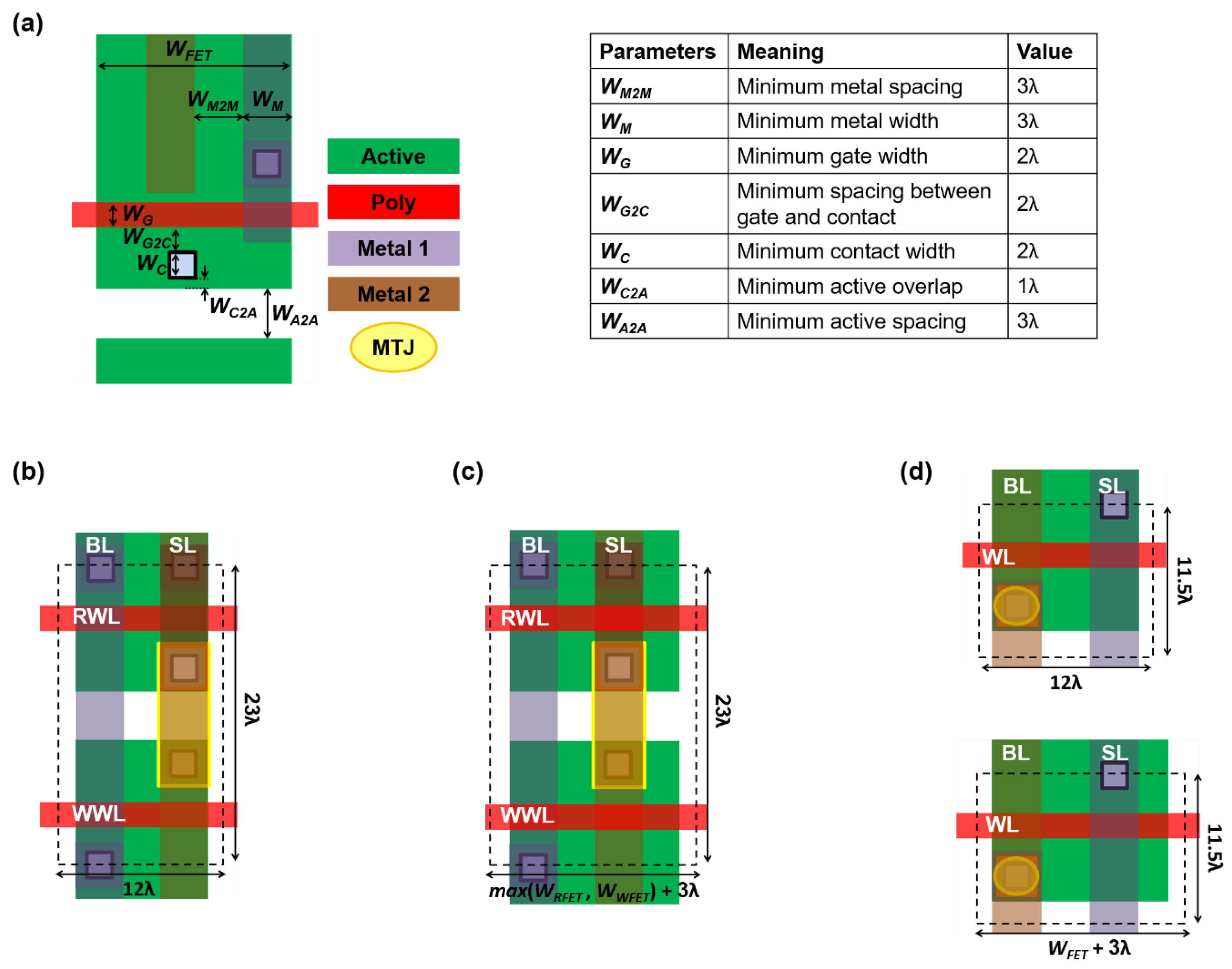

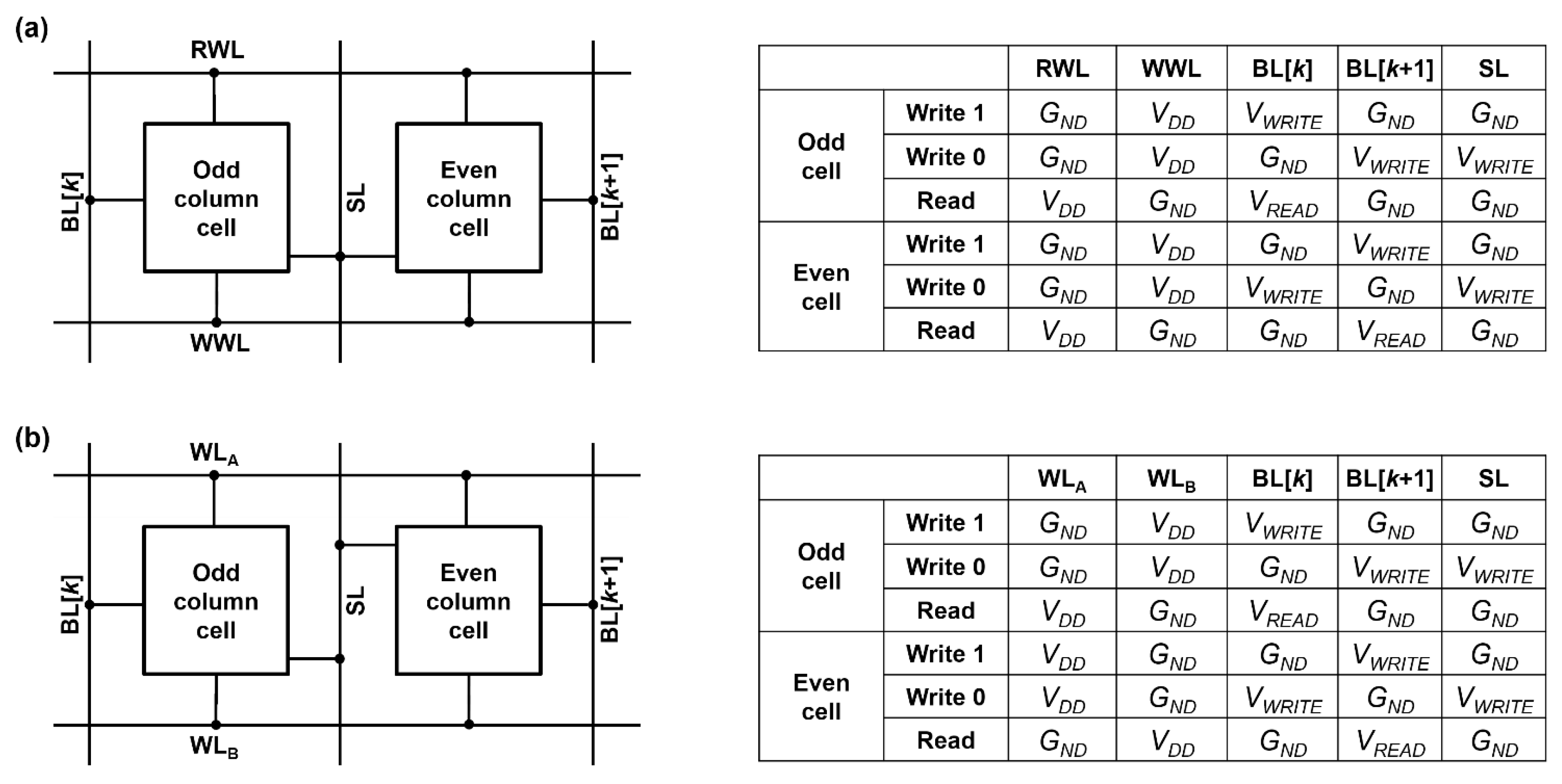

3.2. Proposed Bit-Cell Structures

4. Results

4.1. Simulation Framework

- (1)

- (2)

- Non-Equilibrium Green’s Function (NEGF) formalism to obtain the voltage-dependent resistance of MTJ [27];

- (3)

- SPICE simulator to model the memory bit-cell circuit.

4.2. Simulation Results

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Chun, K.C.; Zhao, H.; Harms, J.D.; Kim, T.-H.; Wang, J.-P.; Kim, C.H. A scaling roadmap and performance evaluation of in plane and perpendicular MTJ based STT-MRAMs for high-density cache memory. IEEE J. Solid State Circuits 2013, 48, 598–610. [Google Scholar] [CrossRef]

- Augustine, C.; Mojumder, N.; Fong, X.; Choday, H.; Park, S.P.; Roy, K. STT-MRAMs for future universal memories: Perspective and prospective. In Proceedings of the International Conference on Microelectronics, Nis, Serbia, 13–16 May 2012; pp. 349–355. [Google Scholar] [CrossRef]

- Li, J.; Ndai, P.; Goel, A.; Salahuddin, S.; Roy, K. Design paradigm for robust spin-torque transfer magnetic RAM (STT MRAM) from circuit/architecture perspective. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2009, 18, 1710–1723. [Google Scholar] [CrossRef]

- ITRS. 2011. Available online: http://www.itrs.net/links/2011itrs/home2011.htm (accessed on 21 August 2011).

- Sun, G.; Dong, X.; Xie, Y.; Li, J.; Chen, Y. A novel architecture of the 3D stacked MRAM L2 cache for CMPs. In Proceedings of the IEEE International Symposium on High Performance Computer Architecture, Raleigh, NC, USA, 14–18 February 2009; pp. 239–249. [Google Scholar] [CrossRef]

- Seo, Y.; Kwon, K.-W.; Fong, X.; Roy, K. High Performance and Energy-Efficient On-Chip Cache Using Dual Port (1R/1W) Spin-Orbit Torque MRAM. IEEE J. Emerg. Sel. Top. Circuits Syst. 2016, 6, 293–304. [Google Scholar] [CrossRef]

- Gordon-Ross, A.; Vahid, F.; Dutt, N.D. Fast Configurable-Cache Tuning With a Unified Second-Level Cache. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2009, 17, 80–91. [Google Scholar] [CrossRef] [Green Version]

- Fong, X.; Kim, Y.; Choday, S.H.; Roy, K. Failure mitigation techniques for 1T-1MTJ spin-transfer torque MRAM bit-cells. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2014, 22, 384–395. [Google Scholar] [CrossRef]

- Seo, Y.; Fong, X.; Roy, K. Domain wall coupling-based STT-MRAM for on-chip cache applications. IEEE Trans. Electron Devices 2015, 62, 554–560. [Google Scholar] [CrossRef]

- Lin., C.J.; Kang, S.H.; Wang, Y.J.; Lee, K.; Zhu, X.; Chen, W.C.; Li, X.; Hsu, W.N.; Kao, Y.C.; Liu, M.T.; et al. 45 nm low power CMOS logic compatible embedded STT MRAM utilizing a reverse-connection 1T/1MTJ cell. In Proceedings of the IEEE International Electron Devices Meeting, Baltimore, MD, USA, 7–9 December 2009; pp. 11.6.1–11.6.4. [Google Scholar] [CrossRef]

- Pai, C.-F.; Liu, L.; Li, Y.; Tseng, H.W.; Ralph, D.C.; Buhrman, R.A. Spin transfer torque devices utilizing the giant spin Hall effect of tungsten. Appl. Phys. Lett. 2012, 101, 122404. [Google Scholar] [CrossRef]

- Liu, L.; Pai, C.-F.; Li, Y.; Tseng, H.W.; Ralph, D.C.; Buhrman, R.A. Spin-torque switching with the giant spin Hall effect of tantalum. Science 2012, 336, 555–558. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Seo, Y.; Kwon, K.-W.; Roy, K. Area-Efficient SOT-MRAM with a Schottky Diode. IEEE Electron Device Lett. 2016, 37, 982–985. [Google Scholar] [CrossRef]

- Nayak, D.; Acharya, D.P.; Nanda, U. A high stable 8T-SRAM with bit interleaving capability for minimization of soft error rate. Microelectron. J. 2018, 73, 43–51. [Google Scholar] [CrossRef]

- Shi, Y.Q.; Zhang, X.M.; Ni, Z.-C.; Ansari, N. Interleaving for combating bursts of errors. IEEE Circuits Syst. Mag. 2004, 4, 29–42. [Google Scholar] [CrossRef]

- Baeg, S.; Wen, S.; Wong, R. SRAM Interleaving Distance Selection with a Soft Error Failure Model. IEEE Trans. Nucl. Sci. 2009, 56, 2111–2118. [Google Scholar] [CrossRef]

- Hoffmann, A. Spin Hall effects in metals. IEEE Trans. Magn. 2013, 49, 5172–5193. [Google Scholar] [CrossRef]

- Kim, Y.; Fong, X.; Kwon, K.-W.; Chen, M.-C.; Roy, K. Multilevel spin-orbit torque MRAMs. IEEE Trans. Electron Devices 2015, 62, 561–568. [Google Scholar] [CrossRef]

- Gupta, S.K.; Park, S.P.; Mojumder, N.N.; Roy, K. Layout-aware optimization of STT-MRAMs. In Proceedings of the Design, Automation & Test in Europe Conference & Exhibition, Dresden, Germany, 12–16 March 2012; pp. 1455–1458. [Google Scholar] [CrossRef]

- Liebman, L. DfM, the teenage years. In Proceedings of the SPIE Advanced Lithography, San Jose, CA, USA, 24–29 February 2008; Volume 6925, p. 692502. [Google Scholar] [CrossRef]

- Maiz, J.; Hareland, S.; Zhang, K.; Armstrong, P. Characterization of multi-bit soft error events in advanced SRAMs. In Proceedings of the IEEE International Electron Devices Meeting, Washington, DC, USA, 8–10 December 2003; pp. 21.4.1–21.4.4. [Google Scholar] [CrossRef]

- Yang, Y.; Wang, P.; Zhang, Y.; Cheng, Y.; Zhao, W.; Chen, Y.; Li, H.H. Radiation-Induced Soft Error Analysis of STT-MRAM: A Device to Circuit Approach. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2016, 35, 380–393. [Google Scholar] [CrossRef]

- Fong, X.; Gupta, S.K.; Mojumder, N.N.; Choday, S.H.; Augustine, C.; Roy, K. KNACK: A Hybrid Spin-Charge Mixed-Mode Simulator for Evaluating Different Genres of Spin Transfer Torque MRAM Bit-cells. In Proceedings of the International Conference on Simulation of Semiconductor Processes and Devices, Osaka, Japan, 8–10 September 2011; pp. 51–54. [Google Scholar] [CrossRef]

- Slonczewski, J.C. Current-driven excitation of magnetic multilayers. J. Magn. Magn. Mater. 1996, 159, L1–L7. [Google Scholar] [CrossRef]

- Sankey, J.C.; Cui, Y.-T.; Sun, J.Z.; Slonczewski, J.C.; Buhrman, R.A.; Ralph, D.C. Measurement of the spin-transfer-torque vector in magnetic tunnel junctions. Nat. Phys. 2007, 4, 67–71. [Google Scholar] [CrossRef] [Green Version]

- Gilbert, T.L. A phenomenological theory of damping in ferromagnetic materials. IEEE Trans. Magn. 2004, 40, 3443–3449. [Google Scholar] [CrossRef]

- Datta, D.; Behin-Aein, B.; Salahuddin, S.; Datta, S. Quantitative Model for TMR and Spin-Transfer Torque in MTJ Devices. In Proceedings of the International Electron Devices Meeting, San Francisco, CA, USA, 6–8 December 2010; pp. 22.8.1–22.8.4. [Google Scholar] [CrossRef]

- Manipatruni, S.; Nikonov, D.E.; Young, I.A. Voltage and energy-delay performance of giant spin hall effect switching for magnetic memory and logic. arXiv 2013, arXiv:1301.5374. [Google Scholar]

- Li, H.; Jagannathan, B.; Wang, J.; Su, T.-C.; Sweeney, S.; Pekarik, J.J.; Shi, Y.; Greenberg, D.; Jin, Z.; Groves, R.; et al. Technology Scaling and Device Design for 350 GHz RF Performance in a 45 nm Bulk CMOS Process. In Proceedings of the IEEE Symposium on VLSI Technology, Kyoto, Japan, 12–14 June 2007; pp. 56–57. [Google Scholar] [CrossRef]

- Guan, Z.; Marek-Sadowska, M.; Nassif, S. Statistical analysis of process variation induced SRAM electromigration degradation. In Proceedings of the International Symposium on Quality Electronic Design, Santa Clara, CA, USA, 3–5 March 2014; pp. 700–707. [Google Scholar] [CrossRef]

- Dong, Q.; Wang, Z.; Lim, J.; Zhang, Y.; Sinangil, M.E.; Shih, Y.-C.; Chih, Y.-D.; Chang, J.; Blaauw, D.; Sylvester, D. A 1-Mb 28-nm 1T1MTJ STT-MRAM with Single-Cap Offset-Cancelled Sense Amplifier and In Situ Self-Write-Termination. IEEE J. Solid State Circuits 2019, 54, 231–239. [Google Scholar] [CrossRef]

| Device Parameters | STT Device | SOT Device |

|---|---|---|

| Gilbert damping, α | 0.007 | 0.0122 |

| Saturation magnetization, MS | 1100 × 103 A/m | 1100 × 103 A/m |

| Dimension of FL (WFL × LFL × tFL) | 120 nm × 40 nm × 2.5 nm 1 | 120 nm × 40 nm × 2.5 nm 2 |

| Dimension of HM (WHM × LHM × tHM) | - | 120 nm × 80 nm × 2.7 nm |

| HM resistivity | - | 200 µΩ·cm |

| Spin Hall angle, θSH | - | 0.3 |

| Spin flip length, λsf | - | 1.40 nm |

| MgO thickness, tMgO | 1.05 nm | 1.30 nm |

| Critical current for 10 ns switching time | 206 µA | 121 µA |

| STT-MRAM | Conventional SOT-MRAM | F-SOT-MRAM | R-SOT-MRAM | |

|---|---|---|---|---|

| Transistor width (nm) | 430 | 155 (WWFET) 85 (WRFET) | 155 (WWFET) 85 (WRFET) | 155 (WWFET) 85 (WRFET) |

| Bit-cell area (µm2) | 0.0880 | 0.1104 | 0.0989 | 0.0828 |

| Write energy per bit (fJ) | 2737.3 | 1504.0 | 1508.4 | 1508.4 |

| Read energy per bit (fJ) | 267.4 | 42.3 | 42.3 | 42.3 |

| Read-disturb margin (%) | 41 | 93 | 93 | 93 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Seo, Y.; Kwon, K.-W. Area Optimization Techniques for High-Density Spin-Orbit Torque MRAMs. Electronics 2021, 10, 792. https://doi.org/10.3390/electronics10070792

Seo Y, Kwon K-W. Area Optimization Techniques for High-Density Spin-Orbit Torque MRAMs. Electronics. 2021; 10(7):792. https://doi.org/10.3390/electronics10070792

Chicago/Turabian StyleSeo, Yeongkyo, and Kon-Woo Kwon. 2021. "Area Optimization Techniques for High-Density Spin-Orbit Torque MRAMs" Electronics 10, no. 7: 792. https://doi.org/10.3390/electronics10070792

APA StyleSeo, Y., & Kwon, K.-W. (2021). Area Optimization Techniques for High-Density Spin-Orbit Torque MRAMs. Electronics, 10(7), 792. https://doi.org/10.3390/electronics10070792