Electronically Tunable First Order AP/LP and LP/HP Filter Topologies Using Electronically Controllable Second Generation Voltage Conveyor (CVCII)

Abstract

:1. Introduction

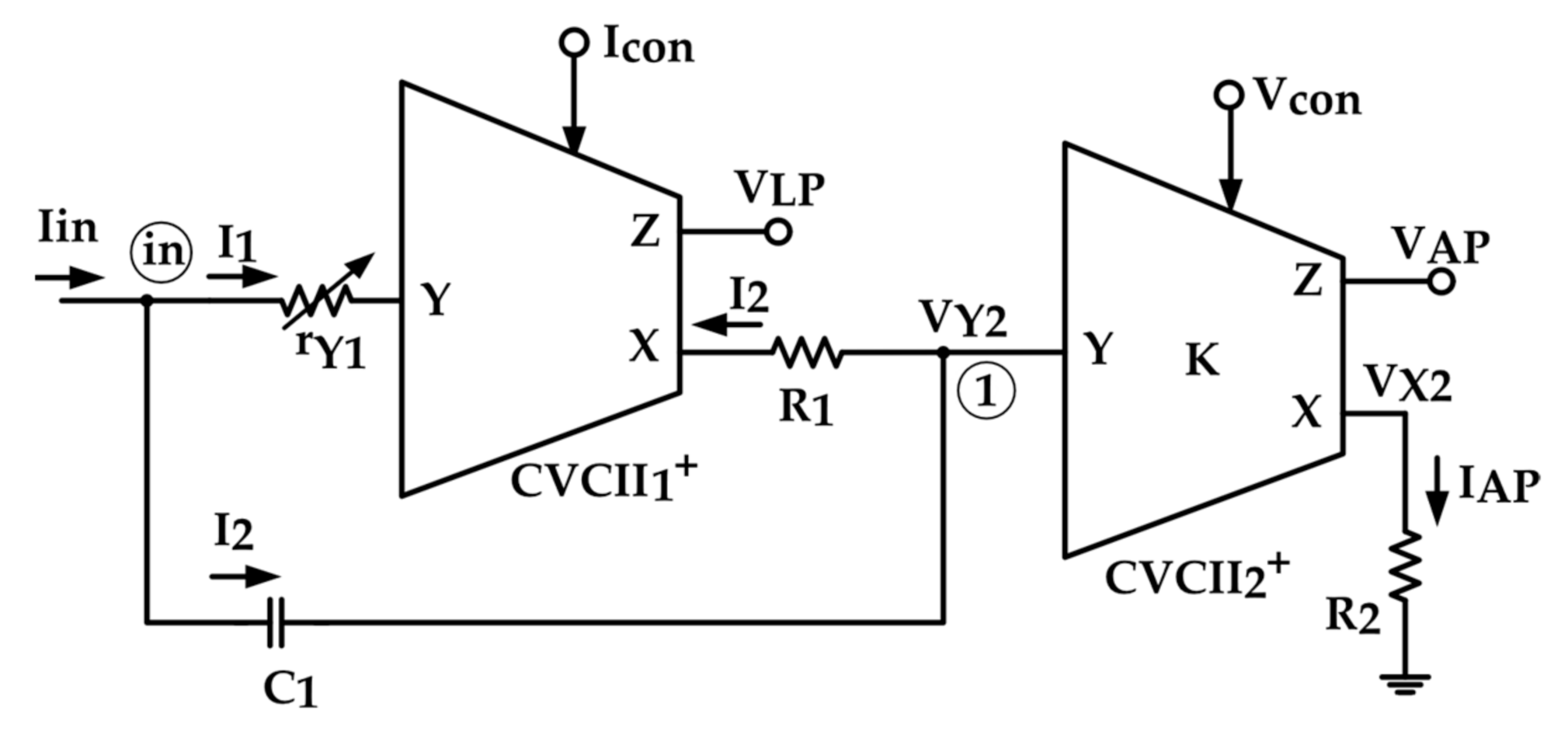

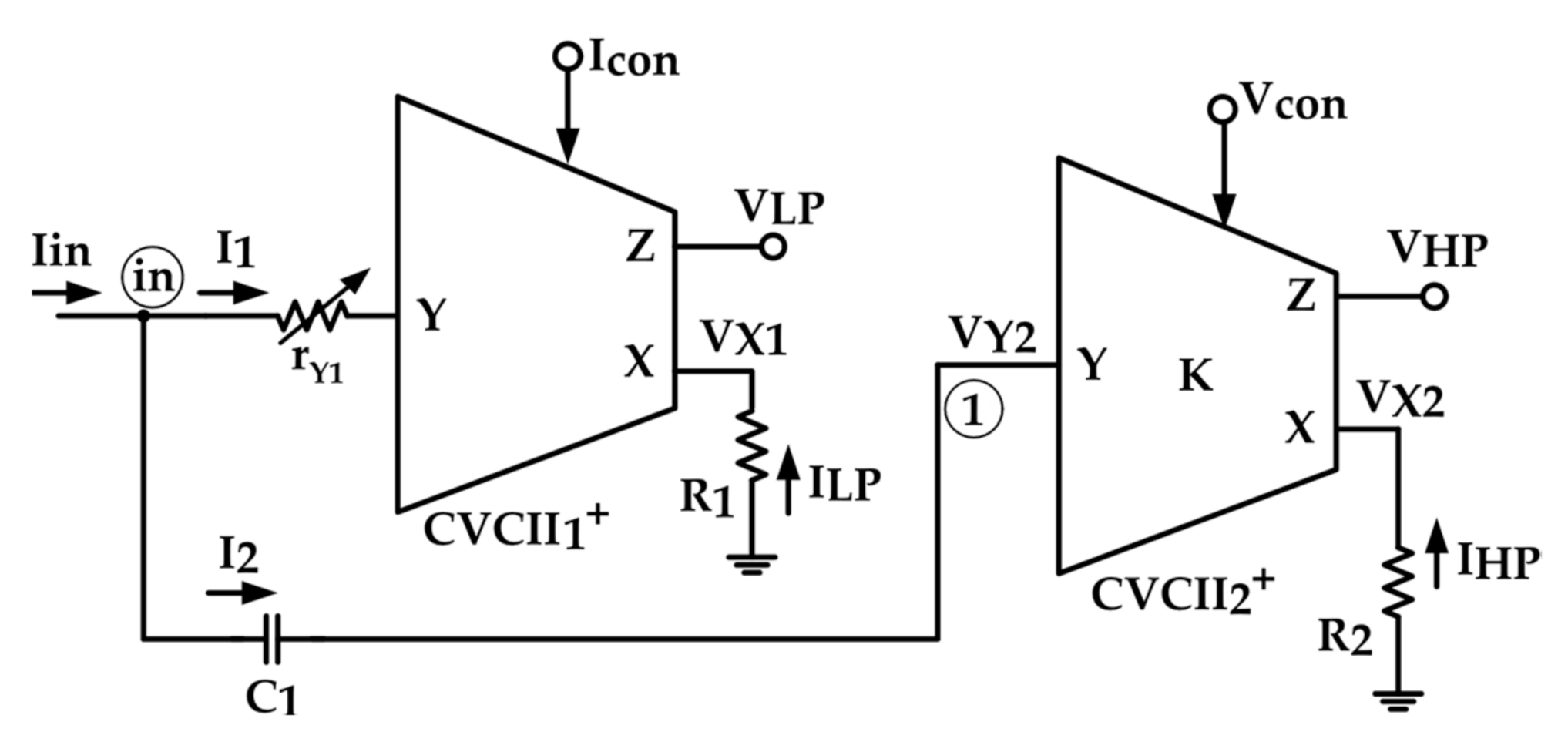

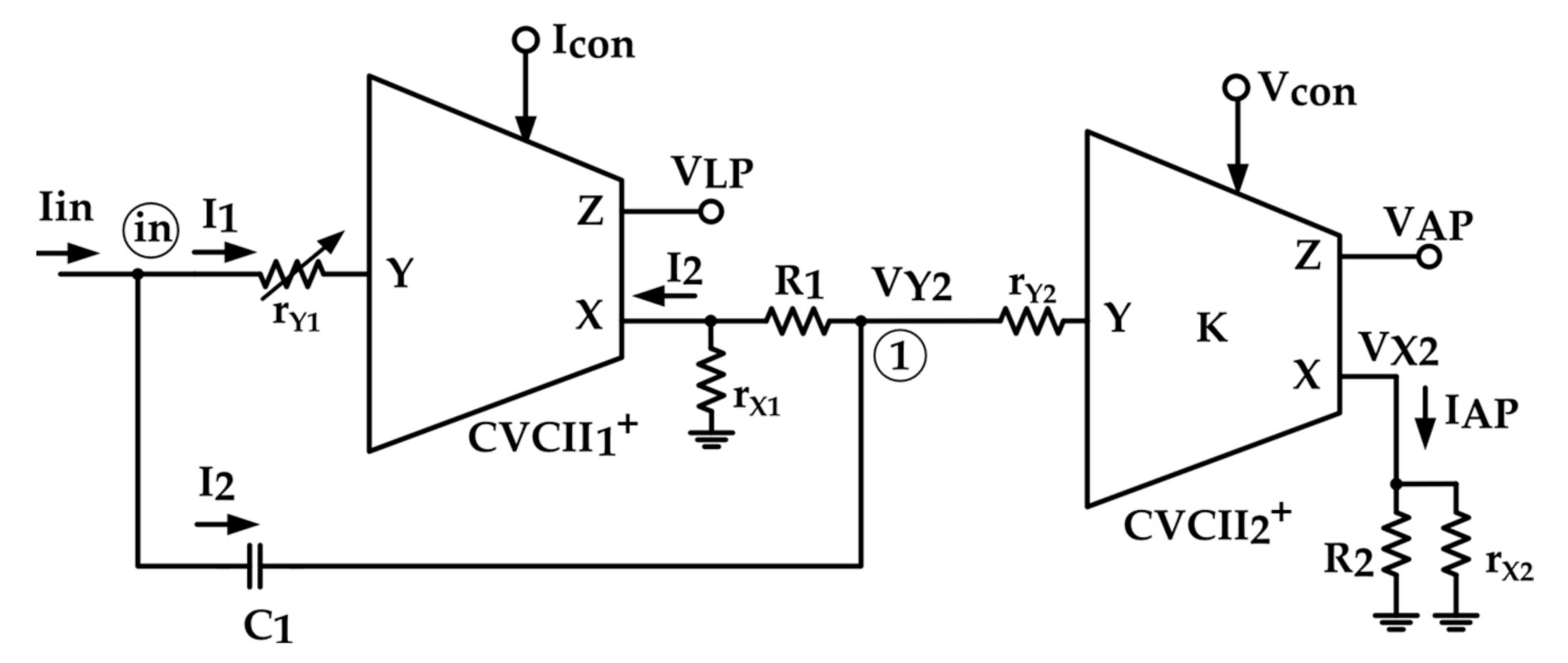

2. The Proposed Filters

3. Nonideal Analysis

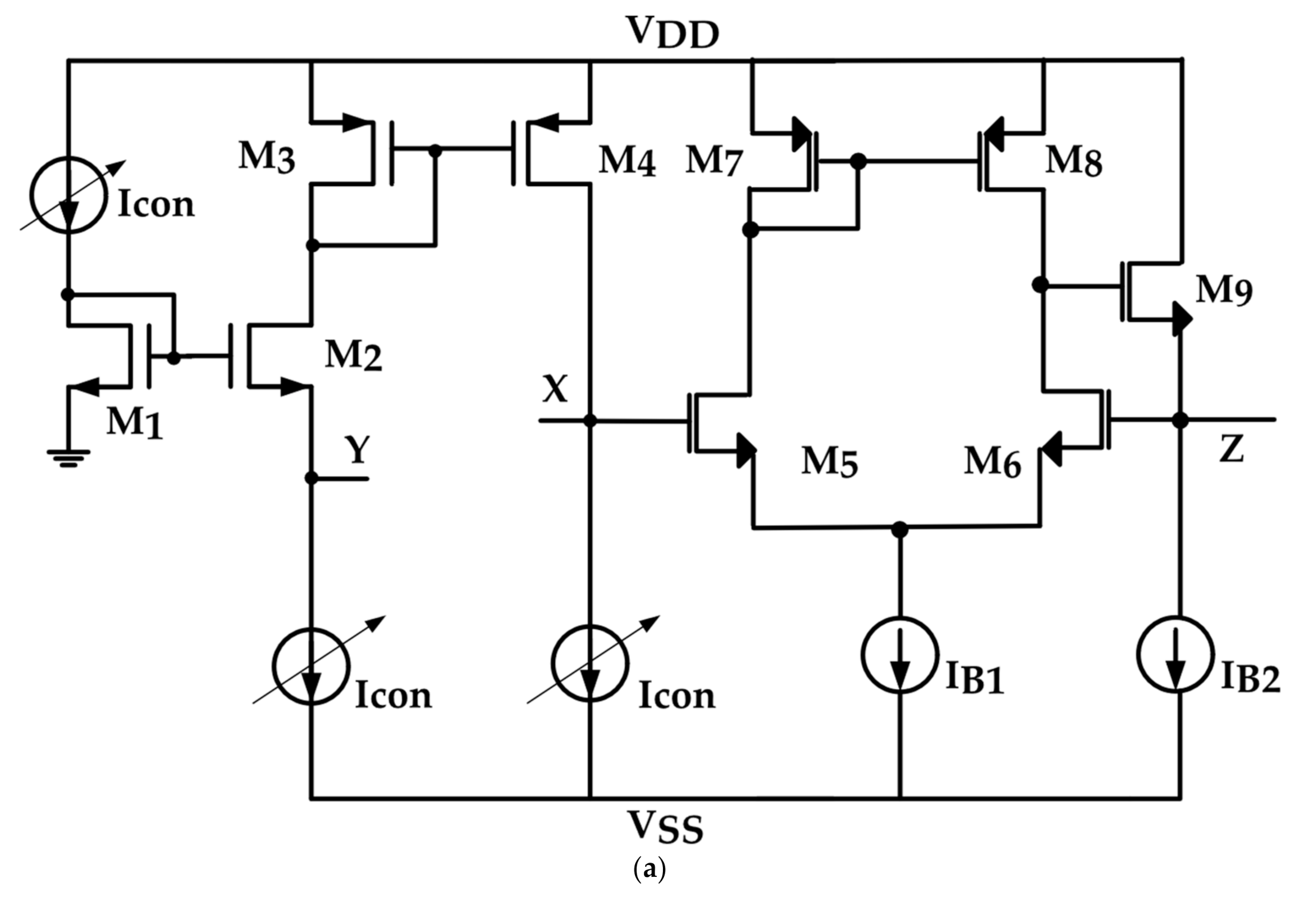

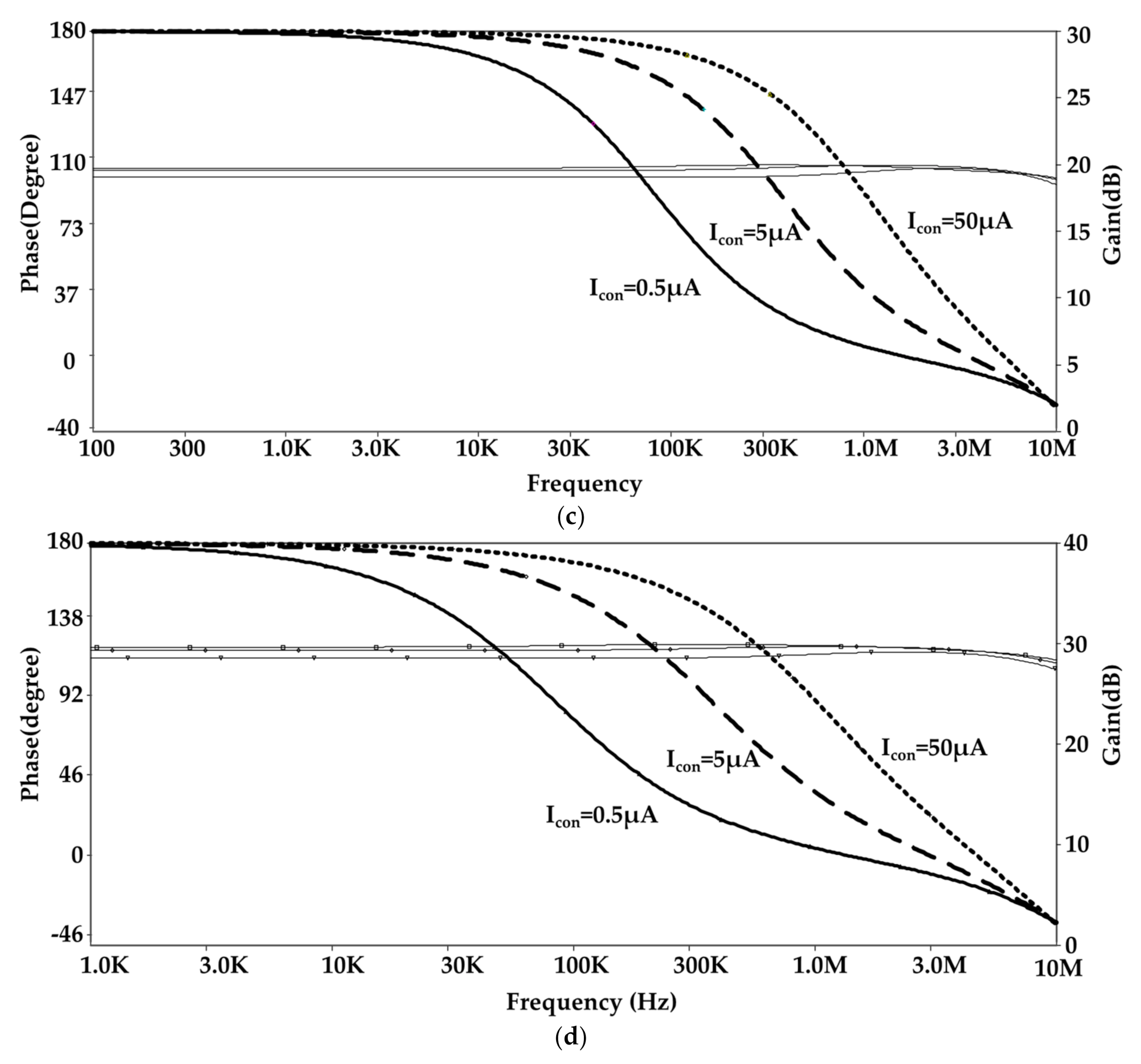

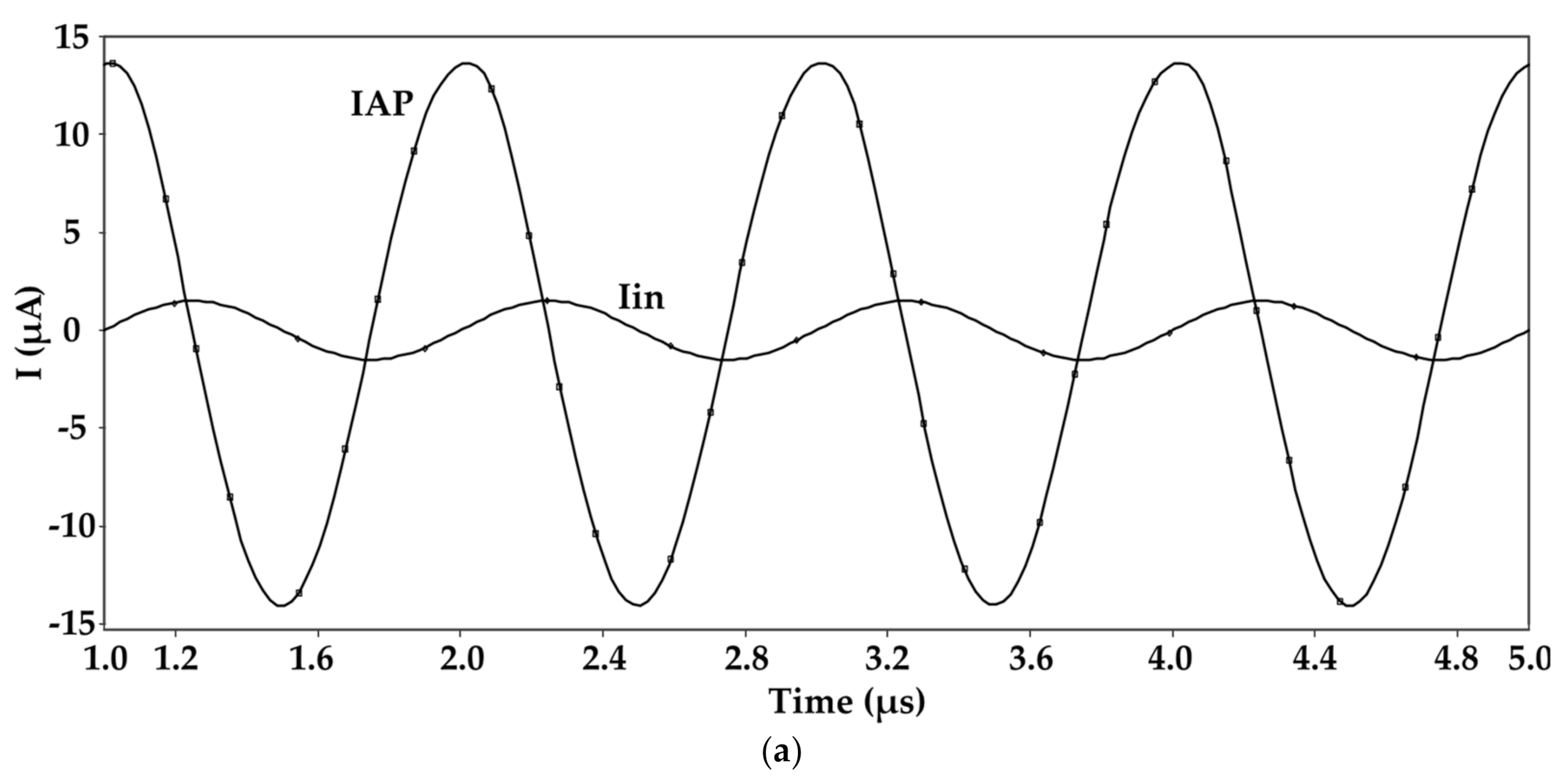

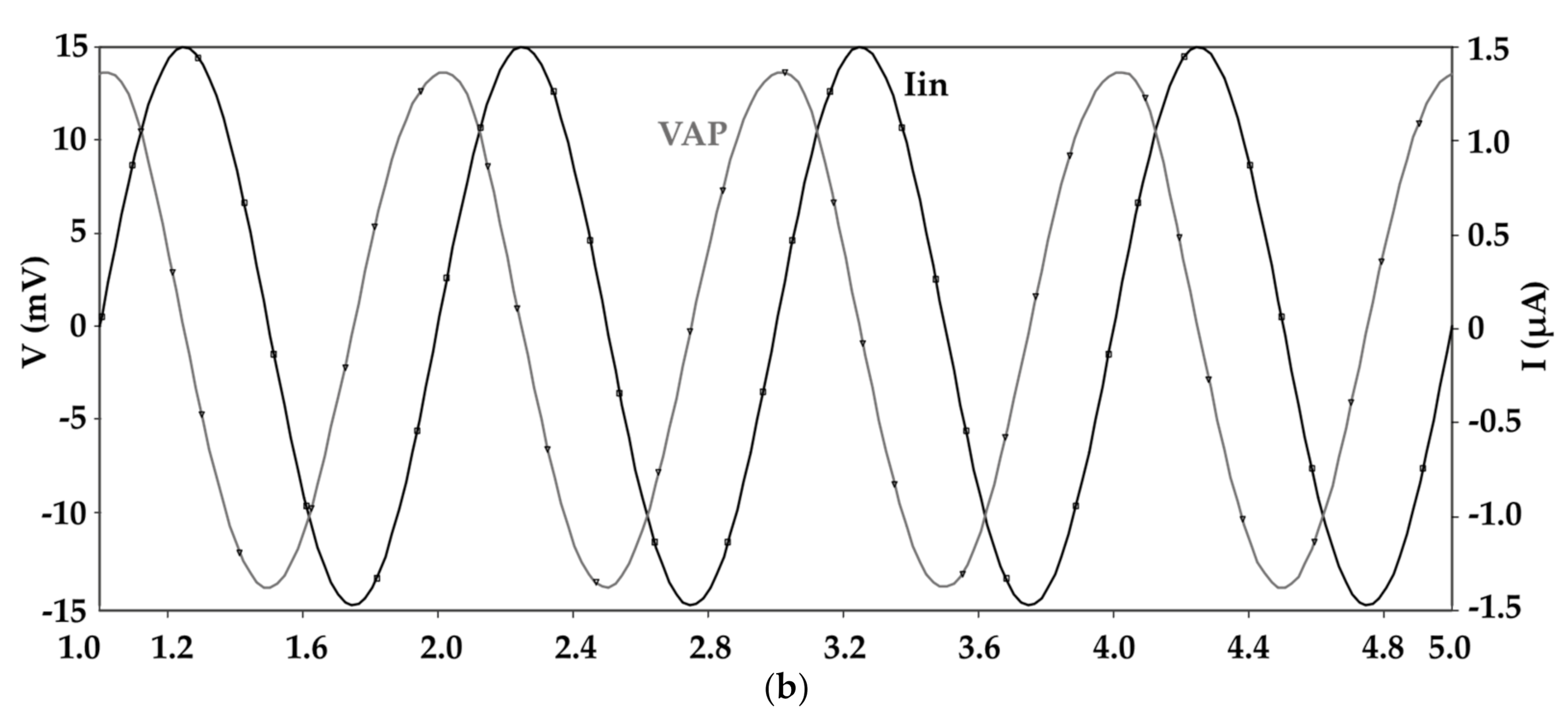

4. Internal Implementation of the Used CVCIIs

5. Simulation Results

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Minaei, S.; Yuce, E. Unity/Variable-Gain Voltage-Mode/Current-Mode First-Order All-Pass Filters Using Single Dual-X Second-Generation Current Conveyor. IETE J. Res. 2010, 56, 305–312. [Google Scholar] [CrossRef] [Green Version]

- Kaçar, F.; Özcelep, Y. CDBA Based Voltage-Mode First-Order All-Pass Filter Topologies. Istanb. Univ. J. Electric. Electron. Eng. 2011, 11, 1327–1332. [Google Scholar]

- Metin, B.; Pal, K.; Cicekoglu, O. CMOS-Controlled Inverting CDBA with a New All-Pass Filter Application. Int. J. Circuit Theory Appl. 2011, 39, 417–425. [Google Scholar] [CrossRef]

- Ibrahim, M.; Minaei, S.; Yuce, E. All-Pass Sections with High Gain Opportunity. Radio Eng. 2011, 20, 3–9. [Google Scholar]

- Das, R.; Paul, S.K. Voltage Mode First Order All Pass Filter Design Using Differential Difference Current Conveyor. In Proceedings of the 2016 International Conference on Microelectronics, Computing and Communications (MicroCom), Durgapur, India, 23–25 January 2016; pp. 1–4. [Google Scholar]

- Dixit, V.K.; Gupta, R.; Pal, K. High-Input Impedance First Order All-Pass Filters Using DDCC. In Proceedings of the 2013 Annual IEEE India Conference (INDICON), Mumbai, India, 13–15 December 2013; pp. 1–5. [Google Scholar]

- Toker, A.; Özcan, S.; Kuntman, H. Supplementary All-Pass Sections with Reduced Number of Passive Elements Using a Single Current Conveyor. Int. J. Electron. 2001, 88, 969–976. [Google Scholar] [CrossRef]

- Pal, K.; Rana, S. Some New First-Order All-Pass Realizations Using CCII. Act. Passive Electron. Compon. 2004, 27, 91–94. [Google Scholar] [CrossRef] [Green Version]

- Metin, B.; Cicekoglu, O. Novel First Order All-Pass Filter with a Single CCI. In Proceedings of the MELECON 2006—2006 IEEE Mediterranean Electrotechnical Conference, Malaga, Spain, 16–19 May 2006; Institute of Electrical and Electronics Engineers (IEEE); pp. 74–75. [Google Scholar]

- Beg, P.; Ansari, M.S. Fully-differential first-order all-pass filters using CMOS DV-DXCCII. In Proceedings of the 2017 International Conference on Multimedia, Signal Processing and Communication Technologies (IMPACT), Aligarh, India, 24–26 November 2017; Institute of Electrical and Electronics Engineers (IEEE); pp. 267–270. [Google Scholar]

- Horng, J.-W.; Hou, C.-L.; Chang, C.-M.; Chung, W.-Y.; Liu, H.-L.; Lin, C.-T. High output impedance current-mode first-order allpass networks with four grounded components and two CCIIs. Int. J. Electron. 2006, 93, 613–621. [Google Scholar] [CrossRef]

- Herencsar, N.; Lahiri, A.; Koton, J.; Vrba, K. First-order multifunction filter design using current amplifiers. In Proceedings of the 2016 39th International Conference on Telecommunications and Signal Processing (TSP), Vienna, Austria, 27–29 June 2016; Institute of Electrical and Electronics Engineers (IEEE); pp. 279–282. [Google Scholar]

- Kilinç, S.; Cam, U.; Kılınç, S. Current-Mode First-Order Allpass Filter Employing Single Current Operational Amplifier. Analog. Integr. Circuits Signal Process. 2004, 41, 47–53. [Google Scholar] [CrossRef]

- Ibrahim, M.A.; Kuntman, H.; Ozcan, S.; Suvak, O.; Cicekoglu, O. New first-order inverting-type second-generation current conveyor-based all-pass sections including canonical forms. Electr. Eng. 2003, 86, 299–301. [Google Scholar] [CrossRef]

- Maheshwari, S.; Khan, I.A. Novel first order all-pass sections using a single CCIII. Int. J. Electron. 2001, 88, 773–778. [Google Scholar] [CrossRef]

- Kacar, F. Operational Transresistance Amplifier Based Current-Mode All-Pass Filter Topologies. In Proceedings of the 2009 Applied Electronics, Pilsen, Czech Republic, 9–10 September 2009; pp. 149–152. [Google Scholar]

- Kumar, A.; Paul, S.K. Current mode first order universal filter and multiphase sinusoidal oscillator. AEU Int. J. Electron. Commun. 2017, 81, 37–49. [Google Scholar] [CrossRef]

- Nand, D.; Pandey, N. Transadmittance Mode First Order LP/HP/AP Filter and its Application as an Oscillator. IOP Conf. Series: Mater. Sci. Eng. 2017, 225, 012150. [Google Scholar] [CrossRef]

- Chaturvedi, B.; Mohan, J.; Jitender; Kumar, A. A Novel Realization of Current-Mode First Order Universal Filter. In Proceedings of the 2019 6th International Conference on Signal Processing and Integrated Networks (SPIN), Noida, India, 7–8 March 2019; Institute of Electrical and Electronics Engineers (IEEE); pp. 623–627. [Google Scholar]

- Fabre, A.; Saaid, O.; Wiest, F.; Boucheron, C. High frequency applications based on a new current controlled conveyor. IEEE Trans. Circuits Syst. I Regul. Pap. 1996, 43, 82–91. [Google Scholar] [CrossRef]

- Safari, L.; Minaei, S.; Yuce, E. CMOS First-Order Current-Mode All-Pass Filter with Electronic Tuning Capability and Its Applications. J. Circuits Syst. Comput. 2013, 22, 1350007. [Google Scholar] [CrossRef]

- Safari, L.; Yuce, E.; Minaei, S. A new ICCII based resistor-less current-mode first-order universal filter with electronic tuning capability. Microelectron. J. 2017, 67, 101–110. [Google Scholar] [CrossRef]

- Tangsrirat, W. On the Realization of First-Order Current-Mode AP/HP Filter. Radioengineering 2013, 22, 1007–1015. [Google Scholar]

- Maheshwari, S. A new current-mode current-controlled all-pass section. J. Circuits Syst. Comput. 2007, 16, 181–189. [Google Scholar] [CrossRef]

- Tangsrirat, W.; Pukkalanun, T.; Surakampontorn, W. Resistorless realization of current-mode first-order allpass filter using current differencing transconductance amplifiers. Microelectron. J. 2010, 41, 178–183. [Google Scholar] [CrossRef]

- Noppakarn, A.; Lawanwisut, S. New Gain Controllable Resistor-Less Current-Mode First Order Allpass Filter and Its Application. Radioengineering 2011, 21, 312–316. [Google Scholar]

- Maheshwari, S. Grounded capacitor cm-aps with high output impedance. J. Circuits Syst. Comput. 2007, 16, 567–576. [Google Scholar] [CrossRef]

- Maheshwari, S. New voltage and current-mode APS using current controlled conveyor. Int. J. Electron. 2004, 91, 735–743. [Google Scholar] [CrossRef]

- Öztayfun, S.; Kılınç, S.; Çelebi, A.; Çam, U. A new electronically tunable phase shifter employing current-controlled current conveyors. AEU Int. J. Electron. Commun. 2008, 62, 228–231. [Google Scholar] [CrossRef]

- Kumngern, M.; Chanwutitum, J. An Electronically Tunable Current-Mode First-Order Allpass Filter Using a CCCCTA. In Proceedings of the 2013 International Conference on Advanced Technologies for Communications (ATC 2013), Ho Chi Minh City, Vietnam, 16–18 October 2013; pp. 733–736. [Google Scholar]

- Chaichana, A.; Kumngern, M.; Siripruchyanun, M.; Jaikla, W. Amplitude Controllable Current-Mode First Order Allpass Filter Including Minimum Component Count Circuits. In Proceedings of the 2015 38th International Conference on Telecommunications and Signal Processing (TSP), Prague, Czech Republic, 9–11 July 2015; pp. 1–4. [Google Scholar]

- Herencsar, N.; Jerabek, J.; Koton, J.; Vrba, K.; Minaei, S.; Cem Goknar, I. Pole Frequency and Pass-Band Gain Tunable Novel Fully-Differential Current-Mode All-Pass Filter. In Proceedings of the 2015 IEEE International Symposium on Circuits and Systems (ISCAS), Lisbon, Portugal, 24–27 May 2015. [Google Scholar]

- Safari, L.; Barile, G.; Stornelli, V.; Ferri, G. An Overview on the Second Generation Voltage Conveyor: Features, Design and Applications. IEEE Trans. Circuits Syst. II Express Briefs 2018, 66, 547–551. [Google Scholar] [CrossRef]

- Safari, L.; Barile, G.; Ferri, G.; Stornelli, V. A New Low-Voltage Low-Power Dual-Mode VCII-Based SIMO Universal Filter. Electronics 2019, 8, 765. [Google Scholar] [CrossRef] [Green Version]

- Barile, G.; Ferri, G.; Safari, L.; Stornelli, V. A New High Drive Class-AB FVF-Based Second Generation Voltage Conveyor. IEEE Trans. Circuits Syst. II Express Briefs 2019, 67, 405–409. [Google Scholar] [CrossRef]

- Safari, L.; Barile, G.; Stornelli, V.; Ferri, G.; Leoni, A. New Current Mode Wheatstone Bridge Topologies with Intrinsic Linearity. In Proceedings of the PRIME 2018—14th Conference on Ph.D. Research in Microelectronics and Electronics, Prague, Czech Republic, 2–5 July 2018. [Google Scholar]

- Safari, L.; Barile, G.; Ferri, G.; Stornelli, V. High performance voltage output filter realizations using second generation voltage conveyor. Int. J. RF Microw. Comput. Eng. 2018, 28, 21534. [Google Scholar] [CrossRef]

- Yuce, E.; Safari, L.; Minaei, S.; Ferri, G.; Stornelli, V. New mixed-mode second-generation voltage conveyor based first-order all-pass filter. IET Circuits Devices Syst. 2020, 14, 901–907. [Google Scholar] [CrossRef]

- Safari, L.; Minaei, S. A Novel Resistor-Free Electronically Adjustable Current-Mode Instrumentation Amplifier. Circuits Syst. Signal Process. 2012, 32, 1025–1038. [Google Scholar] [CrossRef]

- Safari, L.; Minaei, S. New ECCII-Based Electronically Controllable Current-Mode Instrumentation Amplifier with High Frequency Performance. In Proceedings of the 2017 European Conference on Circuit Theory and Design (ECCTD), Catania, Italy, 4–6 September 2017; pp. 1–4. [Google Scholar]

| W, L | ||

|---|---|---|

| CVCII1+ | CVCII2+ | |

| 4.5 µm, 4.5 µm | 7.2 µm, 1.8 µm | |

| 90 µm, 1.8 µm | 9 µm, 1.8 µm | |

| 3.6 µm, 1.8 µm | 270 µm, 0.9 µm | |

| 3.6 µm, 1.8 µm | 5.04 µm, 0.54 µm | |

| 9 µm, 1.8 µm | 50.4 µm, 0.54 µm | |

| 9 µm, 1.8 µm | 7.2 µm, 1.8 µm | |

| 360 µm, 0.9 µm | 7.2 µm, 1.8 µm | |

| - | 270 µm, 0.9 µm | |

| - | 0.9 µm, 0.54 µm | |

| - | 9 µm, 0.54 µm | |

| - | 9 µm, 1.8 µm | |

| , | 30 µA,30 µA | 28 µA,7 µA |

| , | - | 70 µA, 28 µA, 7 µA |

| CVCII1+ | CVCII2+ | |

|---|---|---|

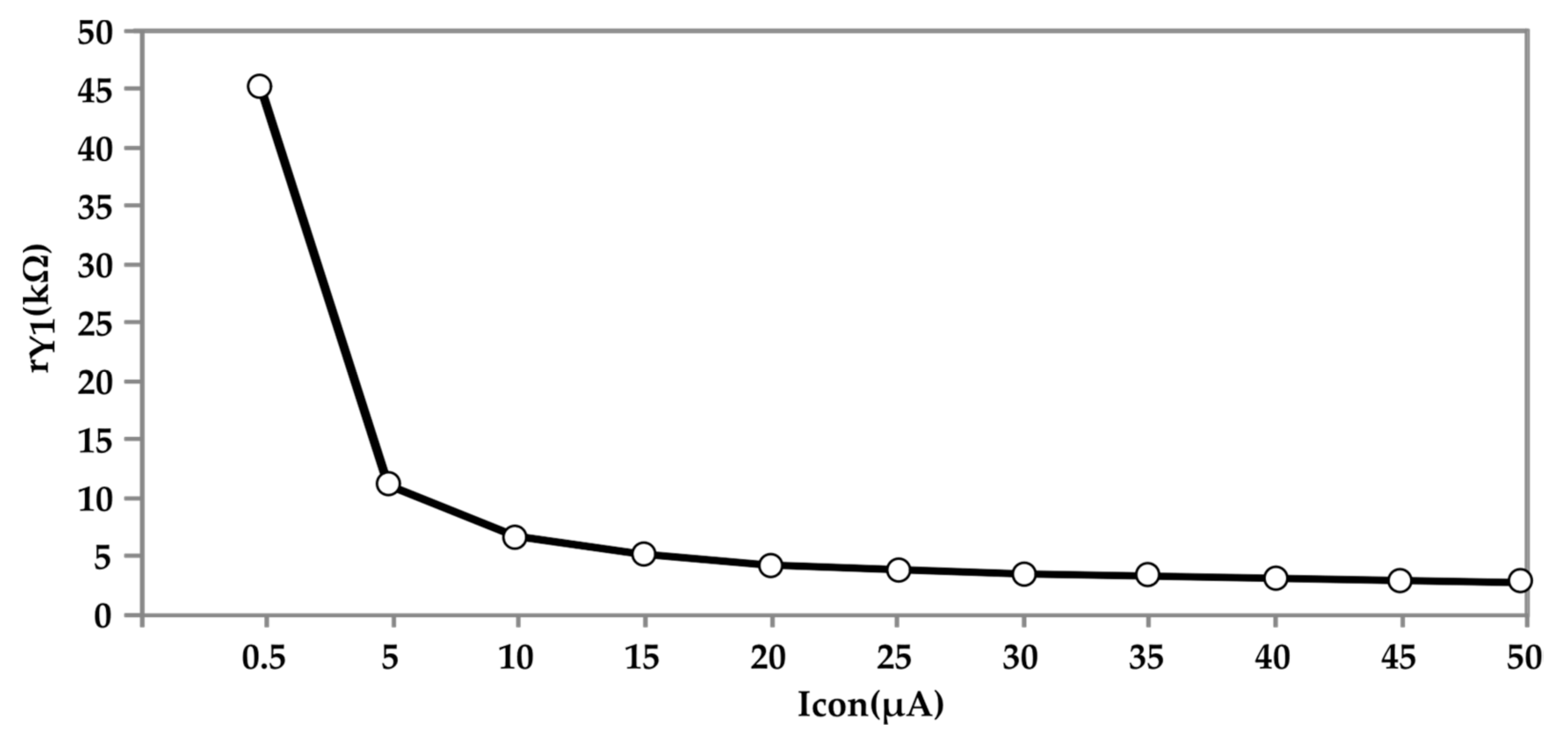

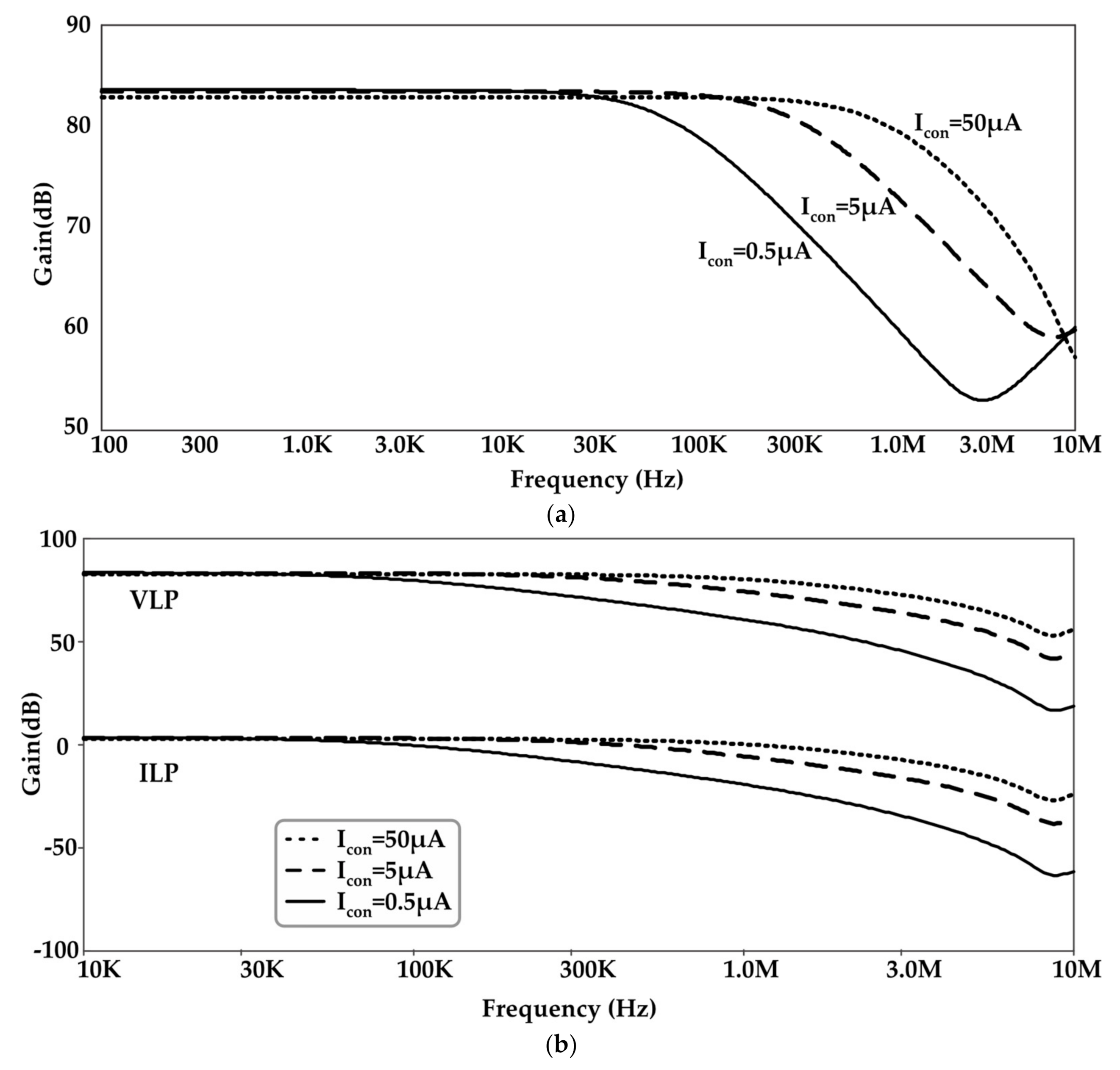

| = 0.5 µA) to = 50 µA) | 81 Ω | |

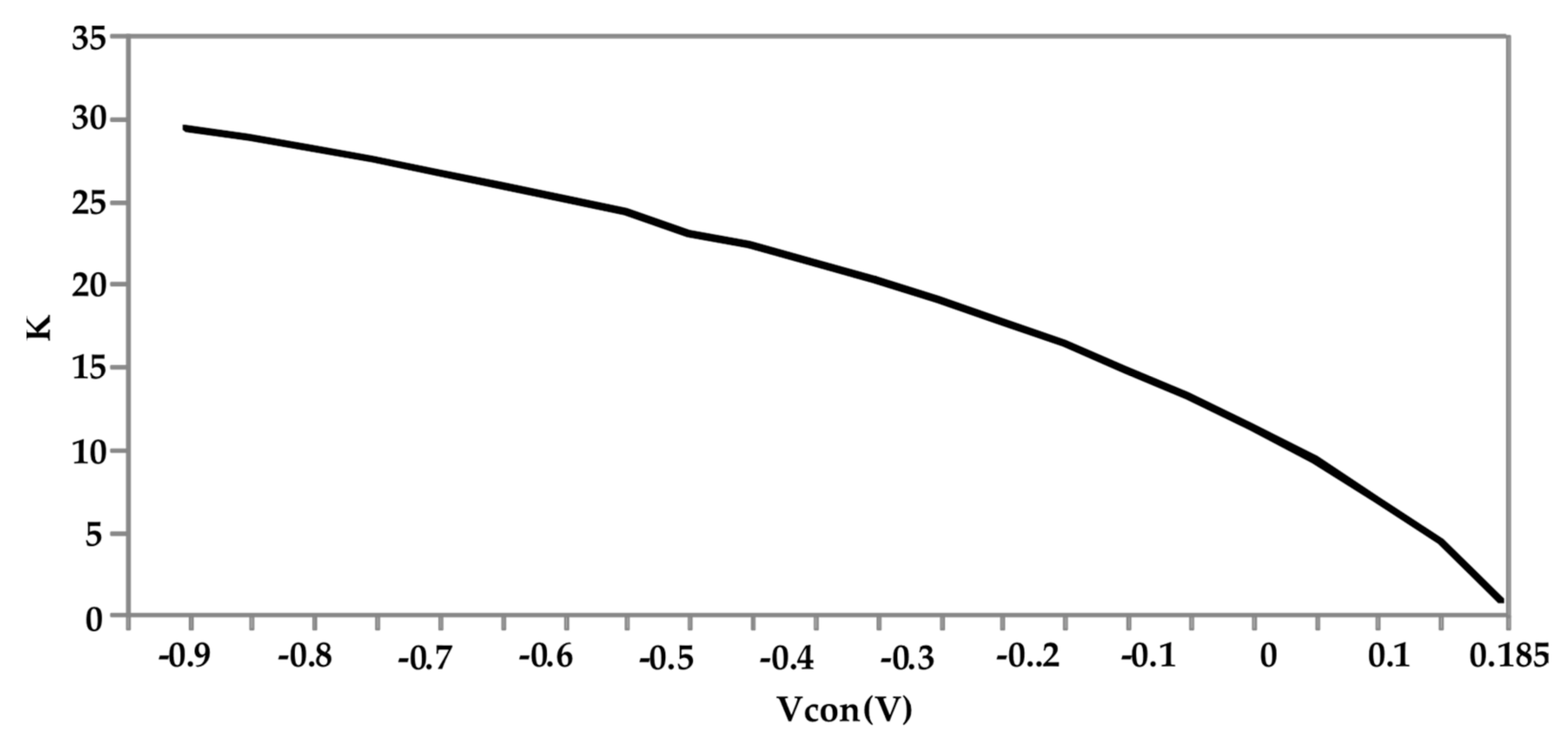

| = 0.5 µA) to = 50 µA) | = 0 V) to = −0.9 V) | |

| = 5 µA) to = 50 µA) | 3.3 fF | |

| 54 Ω | 57 Ω | |

| DC offset at Y | 11 mV | 2.6 mV |

| DC offset at Z | 5 mV | 6 mV |

| DC offset at X | 6 mV | −2.4 mV |

| 0.985 | 0.989 | |

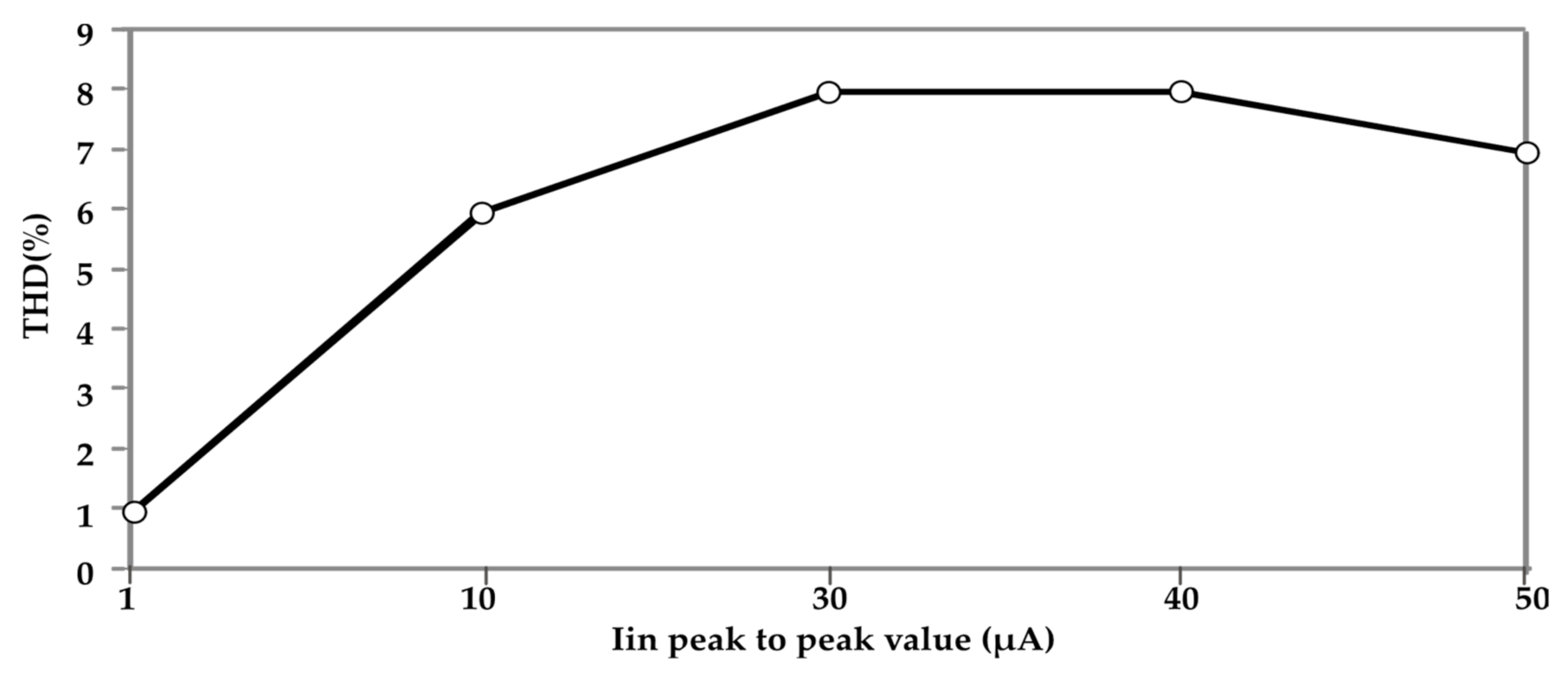

| = 0.5 µA and = 50 µA | 9.5 | |

| Power | = 0.5 µA to = 50 µW | = 0.185 V to = −0.9 V |

| Ref | ABB | #R | Floating C | # Transistors | VDD VSS | Pd (W) | Output | Match | Electronic Tunability | ||

|---|---|---|---|---|---|---|---|---|---|---|---|

| G | |||||||||||

| [1] | 1DXCCII | 2 | Yes 1 | 20 | ±1.25 V | 2.1 m | 2 | Yes | No | No | 1.59 M |

| [2] | 1DDCCII | 1 | Yes/No 3 | 18 | ±2.5 V | NA 4 | 2 | No | No | No | 10 M |

| [10] | DV-DXCCII | 2 | Yes 1 | 30 | ±1.25 V | NA | 2 | Yes | No | No | 6.133 M |

| [12] | 3CA | 1 | Yes | 120 | ±5 V | 25.7 m | No | No | Yes | 100 k | |

| [17] | 1Dx-MOCCII | 1 | Yes | 40 | ±1.25 V | NA | No | No | No | 7.962 M | |

| [18] | 2OFCC | 2 | No | 42 | ±1.5 V | NA | Yes | No | No | 159 K | |

| [19] | 1DD-DXCCII | 3 | Yes | 30 | ±1.2 V | NA | Yes | No | No | 6.43 M | |

| [21] | Current Mirror | 0 | No | 10 | ±0.9 V | 0.266 m | No | Yes | No | 3 M | |

| [22] | 1ICCII | 0 | Yes | 44 | ±0.75 V | 2.75 m | No | Yes | No | 2.6 M | |

| [23] | Current Mirror | 0 | No | 8 | +1.5 | 0.169 m | No | Yes | No | 159 k | |

| [24] | 2CCCII | 0 | Yes | 35 | ±2.5 V | NA | No | Yes | No | 4.8 M | |

| [25] | 2CDTA | 0 | Yes | 84 | ±2 V | 9 m | No | Yes | No | 1 M | |

| [26] | 2CCCCTA | 0 | No | 54 | ±2.5 V | NA | No | Yes | Yes | <1 M | |

| [27] | Modified CCCII | 0 | No | 42 | ±2.5 V | NA | No | Yes | No | 1 M | |

| [28] | 2CCCII | 0 | Yes | 38 | NA | NA | No | Yes | No | 58 k 200 kHz | |

| [29] | 1Do-CCCII | 0 | Yes 1 | 42 | ±3 V | NA | Yes | Yes | No | 1.632 M | |

| [30] | 1CCCTA | 1 | Yes 1 | 25 | ±1.5 V | NA | No | Yes | Yes | 1.66 M | |

| [31] | 1CFCTA | 1 | No | 35 | ±1.25 V | 5.5 m | No | Yes | Yes | 2 M | |

| [32] | 1CA+2CB | 0 | Yes | 46 | ±1.2 V | 3.88 m 5.29 m | No | Yes | Yes | 1.41 M | |

| [35] | 1VCII±+1VCII+ | 3 | No | 34 | ±0.9 V | 0.489 m | Yes | No | No | 1 M | |

| Proposed#1 | 2CVCII+ | 2 | Yes | 36 | ±0.9 V | 0.385 m 1.057 m | No | Yes 5 | Yes | 89 K–1 M | |

| Proposed#2 | 2CVCII+ | 2 | Yes | 36 | ±0.9 V | 0.385 m 1.057 m | No | Yes | Yes | 89 K–1 M | |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Barile, G.; Safari, L.; Pantoli, L.; Stornelli, V.; Ferri, G. Electronically Tunable First Order AP/LP and LP/HP Filter Topologies Using Electronically Controllable Second Generation Voltage Conveyor (CVCII). Electronics 2021, 10, 822. https://doi.org/10.3390/electronics10070822

Barile G, Safari L, Pantoli L, Stornelli V, Ferri G. Electronically Tunable First Order AP/LP and LP/HP Filter Topologies Using Electronically Controllable Second Generation Voltage Conveyor (CVCII). Electronics. 2021; 10(7):822. https://doi.org/10.3390/electronics10070822

Chicago/Turabian StyleBarile, Gianluca, Leila Safari, Leonardo Pantoli, Vincenzo Stornelli, and Giuseppe Ferri. 2021. "Electronically Tunable First Order AP/LP and LP/HP Filter Topologies Using Electronically Controllable Second Generation Voltage Conveyor (CVCII)" Electronics 10, no. 7: 822. https://doi.org/10.3390/electronics10070822