Ten-Bit 0.909-MHz 8-Channel Dual-Mode Successive Approximation ADC for a BLDC Motor Drive

Abstract

:1. Introduction

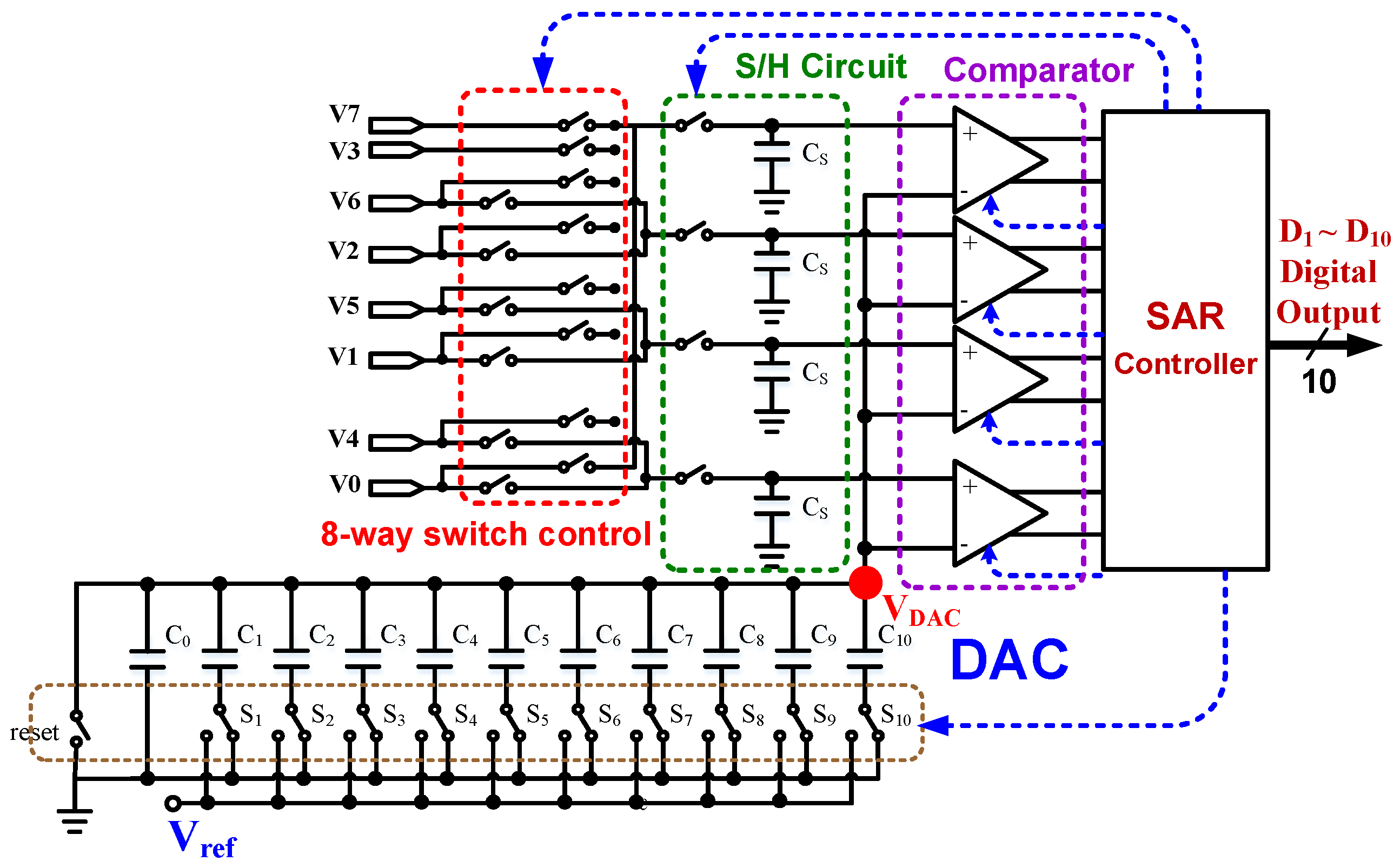

2. Circuit Design of the Proposed SAR ADC

2.1. 8-Way Switch Control System

2.2. Proposed Sample and Hold Circuit

2.3. Capacitive Digital-to-Analog Converter

2.4. Dynamic Comparator with Complementary Inputs

2.5. SAR Controller

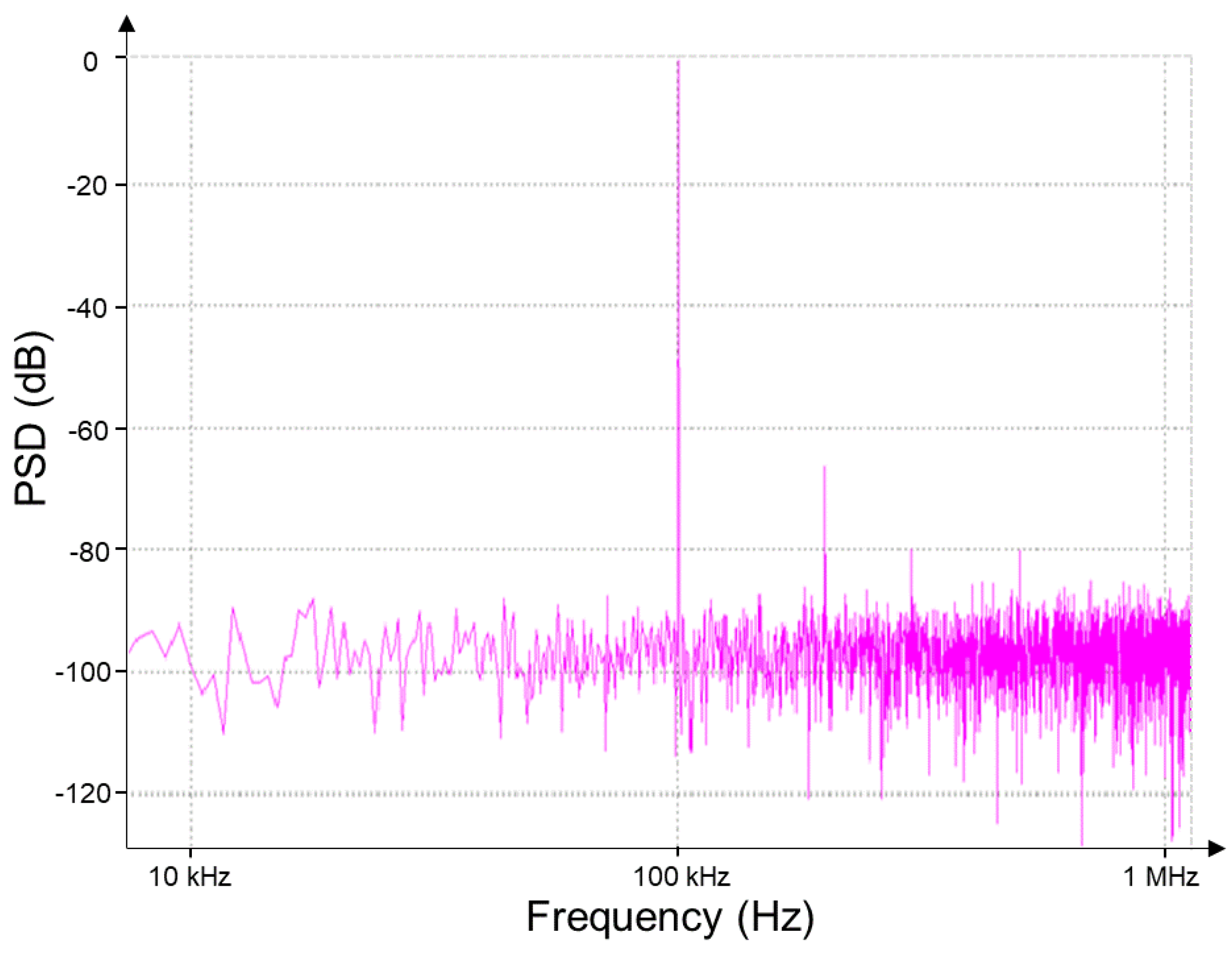

3. Simulated and Measurement Results

4. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Sathyan, A.; Milivojevic, N.; Lee, Y.J.; Krishnamurthy, M.; Emadi, A. An FPGA-based novel digital PWM control scheme for BLDC motor drives. IEEE Trans. Ind. Electron. 2009, 56, 3040–3049. [Google Scholar] [CrossRef]

- Hong, H.C.; Lee, G.M. A 65-fJ/conversion-step 0.9-V 200-kS/s rail-to-rail 8-bit successive approximation ADC. IEEE J. Solid-State Circuits 2007, 42, 2161–2168. [Google Scholar] [CrossRef]

- Oh, J.; Heo, S.; Kim, M.; Suk, J.H.; Yang, Y.; Kim, J. High performance of PMSM driver IC integrated sensorless and current sensing circuits. In Proceedings of the 28th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Prague, Czech Republic, 12–13 June 2016; pp. 251–254. [Google Scholar]

- Wang, Z.; Zhao, T.; Xu, D.; Chen, G.; Zhu, H.; Liang, F.; Zhang, G. Design of a low-power single-channel 8-Bit 1.25 GSPS SAR ADC. In Proceedings of the IEEE International Conference on Computation, Communication and Engineering (ICCCE), Longyan, Fujian, China, 8–10 November 2019; pp. 79–82. [Google Scholar]

- Mirzaie, N.; Alzahmi, A.; Lin, C.C.; Kim, I.; Byun, G.S. A low-power and performance-efficient SAR ADC design. In Proceedings of the International SoC Design Conference (ISOCC), Seoul, Korea, 5–8 November 2017; pp. 224–225. [Google Scholar]

- Cheng, K.Y. Novel architecture of a mixed-mode sensorless control IC for BLDC motors with wide speed ranges. In Proceedings of the Twenty-Fourth Annual IEEE Applied Power Electronics Conference and Exposition, Washington, DC, USA, 15–19 February 2009; pp. 2022–2027. [Google Scholar]

- Moskowitz, S.; Diven, L.; Feit, L. Cross-talk considerations in time-division multiplex systems. Proc. IRE 1950, 38, 1330–1336. [Google Scholar] [CrossRef]

- Liu, C.C.; Chang, S.J.; Huang, G.Y.; Lin, Y.Z. A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure. IEEE J. Solid-State Circuits 2010, 45, 731–740. [Google Scholar] [CrossRef]

- Singh, R.R.; Genov, R.; Kotamraju, R.T.; Mazhari, B. Multi-step binary-weighted capacitive digital-to-analog converter architecture. In Proceedings of the 51st Midwest Symposium on Circuits and Systems, Knoxville, TN, USA, 10–13 August 2008; pp. 370–373. [Google Scholar]

- Li, Y.; Zhang, Z.; Chua, D.; Lian, Y. Placement for binary-weighted capacitive array in SAR ADC using multiple weighting methods. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2014, 33, 1277–1287. [Google Scholar]

- Schinkel, D.; Mensink, E.; Klumperink, E.; Tuijl, E.V.; Nauta, B. A double-tail latch-type voltage sense amplifier with 18ps setup+hold time. In Proceedings of the IEEE International Solid-State Circuits Conf. (ISSCC), San Francisco, CA, USA, 11–15 February 2007; pp. 314–315. [Google Scholar]

- Lai, W.C.; Huang, J.F.; Lin, W.J. 1 MS/s low power successive approximations register ADC for 67-fJ/conversion-step. In Proceedings of the IEEE Asia Pacific Conference on Circuits and Systems, Kaohsiung, Taiwan, 2–5 December 2012; pp. 260–263. [Google Scholar]

- Baek, S.Y.; Lee, J.K.; Ryu, S.T. An 88-dB Max-SFDR 12-bit SAR ADC with speed-enhanced ADEC and dual registers. IEEE Trans. Circuits Syst. II Exp. Briefs 2013, 60, 562–566. [Google Scholar] [CrossRef]

- Thirunakkarasu, S.; Bakkaloglu, B. Built-in self-calibration and digital-trim technique for 14-bit SAR ADCs achieving ±1 LSB INL. IEEE Trans. Very Large Scale Integr. VLSI Syst. 2015, 23, 916–925. [Google Scholar] [CrossRef]

- Jiang, Y.; Xi, J.; He, L.; Sun, K. A 16-channel 12-bit rail-to-rail successive approximation register ADC for AFEs. In Proceedings of the IEEE International Conference on Electron Devices and Solid-State Circuits (EDSSC), Hong Kong, China, 3–5 August 2016; pp. 263–266. [Google Scholar]

- Hong, H.C.; Lin, L.Y.; Chiu, Y. Design of a 0.20–0.25-V, sub-nW, rail-to-rail, 10-bit SAR ADC for self-sustainable IoT applications. IEEE Trans. Circuits Syst.-I Regul. Pap. 2019, 6, 1840–1852. [Google Scholar] [CrossRef]

- Li, D.; Liu, M.; Zhao, L.; Mao, H.; Ding, R.; Zhu, Z. An 8-bit 2.1-mW 350-MS/s SAR ADC with 1.5 b/cycle redundancy in 65-nm CMOS. IEEE Trans. Circuits Syst. II Exp. Briefs 2020, 67, 2307–2311. [Google Scholar] [CrossRef]

- Verma, D.; Shehzad, K.; Khan, D.; Kim, S.J.; Pu, Y.G.; Yoo, S.-S.; Hwang, K.C.; Yang, Y.; Lee, K.-Y. A Design of Low-Power 10-bit 1-MS/s Asynchronous SAR ADC for DSRC Application. Electronics 2020, 9, 1100. [Google Scholar] [CrossRef]

- Gao, B.; Li, X.; Sun, J.; Wu, J. Modeling of high-resolution data converter: Two-step pipelined-SAR ADC based on ISDMA. Electronics 2020, 9, 137. [Google Scholar] [CrossRef] [Green Version]

- Lin, C.-H.; Wen, K.-A. An Innovative Successive Approximation Register Analog-to-Digital Converter for a Nine-Axis Sensing System. J. Low Power Electron. Appl. 2021, 11, 3. [Google Scholar] [CrossRef]

- Liu, C.C.; Huang, M.C.; Tu, Y.H. A 12 bit 100 MS/s SAR-assisted digital-slope ADC. IEEE J. Solid-State Circuits 2016, 51, 2941–2950. [Google Scholar] [CrossRef]

- Roh, Y.J.; Chang, D.J.; Ryu, S.T. A 40-nm CMOS 12b 120-MS/s nonbinary SAR-assisted SAR ADC with double clock-rate coarse decision. IEEE Trans. Circuits Syst. II Exp. Briefs 2020, 67, 2833–2837. [Google Scholar] [CrossRef]

- Aiello, O.; Crovetti, P.; Alioto, M. Fully synthesizable low-area analogue-to-digital converters with minimal design effort based on the dyadic digital pulse modulation. IEEE Accesss 2020, 8, 70890–70899. [Google Scholar] [CrossRef]

- Xue, X.; Teh, Y.K. Power quality evaluation of six-step commutation brushless DC motor implemented on 32-bit ARM cortex microcontroller. In Proceedings of the 2020 IEEE Conference on Technologies for Sustainability (SusTech), Santa Ana, CA, USA, 23–25 April 2020; pp. 1–4. [Google Scholar]

- Taşören, A.E.; Orenbaş, H.; Şahin, S. Analyze and comparison of different PID tuning methods on a brushless DC motor using Atmega328 based microcontroller unit. In Proceedings of the 2018 6th International Conference on Control Engineering & Information Technology (CEIT), Istanbul, Turkey, 25–27 October 2018; pp. 1–4. [Google Scholar]

| M. | se2 | se1 | se0 | t7 | t6 | t5 | t4 | t3 | t2 | t1 | t0 | ma | mb | SH0 | SH1 | SH2 | SH3 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | V7 | V6 | V5 | V4 |

| 1 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | V7 | V6 | V5 | V4 |

| 1 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | V7 | V6 | V5 | V4 |

| 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | V7 | V6 | V5 | V4 |

| 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | V3 | V2 | V1 | V0 |

| 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | V3 | V2 | V1 | V0 |

| 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | V3 | V2 | V1 | V0 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | V3 | V2 | V1 | V0 |

| 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | V7 | × | × | × |

| 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | V6 | × | × | × |

| 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | V5 | × | × | × |

| 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | V4 | × | × | × |

| 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | V3 | × | × | × |

| 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | V2 | × | × | × |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | V1 | × | × | × |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | V0 | × | × | × |

| Corners | TT | FF | SS | FS | SF |

|---|---|---|---|---|---|

| SNDR (dB) | 71.51 | 70.95 | 71.26 | 72.73 | 71.91 |

| ENOB (bits) | 11.59 | 11.49 | 11.54 | 11.78 | 11.65 |

| Max. DNL (LSB) | 0.937 | 0.997 | 0.561 | 0.937 | 0.937 |

| Min. DNL (LSB) | −0.563 | −0.938 | −0.001 | −0.563 | −0.563 |

| Max. INL (LSB) | 0.752 | 1.321 | 0.383 | 0.742 | 0.730 |

| Min. INL (LSB) | −0.185 | 0 | −0.551 | −0.195 | −0.207 |

| Power (μW) | 10.89 | 10.89 | 10.89 | 10.89 | 10.89 |

| Steps | S10 | S9 | S8 | S7 | S6 | S5 | S4 | S3 | S2 | S1 | S0 | D |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Q0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | - |

| Q10 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | D10 |

| Q9 | D10 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | D9 |

| Q8 | D10 | D9 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | D8 |

| Q7 | D10 | D9 | D8 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | D7 |

| Q6 | D10 | D9 | D8 | D7 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | D6 |

| Q5 | D10 | D9 | D8 | D7 | D6 | 1 | 0 | 0 | 0 | 0 | 0 | D5 |

| Q4 | D10 | D9 | D8 | D7 | D6 | D5 | 1 | 0 | 0 | 0 | 0 | D4 |

| Q3 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | 1 | 0 | 0 | 0 | D3 |

| Q2 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | 1 | 0 | 0 | D2 |

| Q1 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | 1 | 0 | D1 |

| Q0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | - |

| Corners | TT | FF | SS |

|---|---|---|---|

| Supply Voltage (V) | 3.3 | 3.96 | 2.64 |

| SNDR (dB) | 65.88 | 64.19 | 65.74 |

| ENOB (bits) | 10.65 | 10.37 | 10.63 |

| DNL (LSB) | 0.062/−0.501 | 0.062/−0.500 | 0.068/−0.500 |

| INL (LSB) | 0.936/−0.081 | 0.979/−0.040 | 0.936/−0.080 |

| Power (μW) | 833 | 1259 | 556 |

| Sampling Cap. (pF) | 2.01 | ||

| Chip Area (mm2) | 1.35 × 0.98 | ||

| Max. Frequency (MHz) | 25.0 | ||

| Reference (Year) | THIS WORK (2021) | [12] (2012) | [13] (2013) | [14] (2015) | [15] (2016) | [16] (2019) | [17] (2020) | [18] (2020) | [19] (2020) | [20] (2021) | [21] (2016) | [22] (2020) | [23] (2020) |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Technology | 0.25 m | 0.18 m | 0.35 m | 0.60 m | 0.13 m | 0.18 m | 65 nm | 55 nm | 40 nm | 0.18 m | 28 nm | 40 nm | 40 nm |

| Supply Voltage (V) (Analog/Digital) | 3.3/2.5 | 1.8/- | 2.3/- | 15 | 3.3/- | 0.225/- | 1.2/- | 1.0/- | 1.8/1.2 | 1.5/0.9 | 0.9/- | 1.0/- | 1.0/0.7 |

| Input Range (V) | 3.3 | - | - | 12 | - | - | - | - | 1.8 | - | 1.6 | - | 1.0 |

| Resolution (bits) | 10 | 8 | 12 | 14 | 12 | 10 | 8 | 10 | 16 | 12 | 12 | 12 | - |

| Sampling Frequency (MHz) | 0.909 | 1.0 | 3.0 | 0.4 | 1.0 | 0.0045 | 350 | 1.0 | 33.3 | 0.05 | 100 | 120 | 0.0028 |

| Signal Frequency (kHz) | 100 | 8.046 | 1490 | 5 | 100.34 | 0.017/0.22 | 170,000 | 251 | 2300 | - | 49,950 | 1400 | 0.00018 |

| Simulated ENOB (bits) | 10.65 | - | - | - | 10.48 | - | - | - | 14.04 | - | - | - | - |

| Measured ENOB (bits) | 8.11 | 7.23 | 10.12 | 11.9 | - | 7.88 | 7.30 | 9.74 | 10.76 | 10.41 | 9.36 | 6.70 | |

| Simulated DNL (LSB) | 0.06/−0.50 | - | - | - | 0.2/−0.4 | - | - | - | - | - | - | - | - |

| Measured DNL (LSB) | 0.99/−0.63 | 0.66 | 0.14 | 0.92 | - | 1.04/−0.66 | 0.90/−0.60 | −0.7142857 | - | 0.3–0.5 | - | 0.96/−0.93 | 1.9/0.3 |

| Simulated INL (LSB) | 0.94/−0.08 | - | - | - | 0.25/−0.33 | - | - | - | - | - | - | ||

| Measured INL (LSB) | 1.28/−0.17 | 0.61 | 0.38 | 0.95 | - | 0.97/−1.04 | 0.70/−0.70 | −1.1666667 | - | 0.3–0.5 | - | 1.6/−1.08 | 1.5/−1.5 |

| Power (W) | 833 | 10.3 | 1230 | 90,000 | 1800 | 0.00085 | 2100 | 14.8 | 19,200 | 2.7 | 350 | 1900 | 7.3 |

| Core Area (mm2) | 1.323 | 0.6901 | 0.34 | 9.76 | 0.3493 | 0.024 | 0.024 | 0.202 | 0.052 | 0.0047 | 0.0128 | 0.0375 | |

| Simulated FoM (pJ/conv.-step) | 0.57 | - | - | - | 1.26 | - | - | - | 175.5 | - | - | - | - |

| Measured FoM (pJ/conv.-step) | 3.316 | 0.0686 | 0.3684 | 0.05887 | - | 0.008 | 0.038 | 17.3 | - | 0.0305 | 0.0026 | 0.0243 | 30.9 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Huang, C.-C.; Sung, G.-M.; Xiao, X.; Sung, S.-H.; Huang, C.-H. Ten-Bit 0.909-MHz 8-Channel Dual-Mode Successive Approximation ADC for a BLDC Motor Drive. Electronics 2021, 10, 830. https://doi.org/10.3390/electronics10070830

Huang C-C, Sung G-M, Xiao X, Sung S-H, Huang C-H. Ten-Bit 0.909-MHz 8-Channel Dual-Mode Successive Approximation ADC for a BLDC Motor Drive. Electronics. 2021; 10(7):830. https://doi.org/10.3390/electronics10070830

Chicago/Turabian StyleHuang, Chong-Cheng, Guo-Ming Sung, Xiong Xiao, Shan-Hao Sung, and Chao-Hung Huang. 2021. "Ten-Bit 0.909-MHz 8-Channel Dual-Mode Successive Approximation ADC for a BLDC Motor Drive" Electronics 10, no. 7: 830. https://doi.org/10.3390/electronics10070830

APA StyleHuang, C.-C., Sung, G.-M., Xiao, X., Sung, S.-H., & Huang, C.-H. (2021). Ten-Bit 0.909-MHz 8-Channel Dual-Mode Successive Approximation ADC for a BLDC Motor Drive. Electronics, 10(7), 830. https://doi.org/10.3390/electronics10070830