Power Conversion Using Analytical Model of Cockcroft–Walton Voltage Multiplier Rectenna

Abstract

1. Introduction

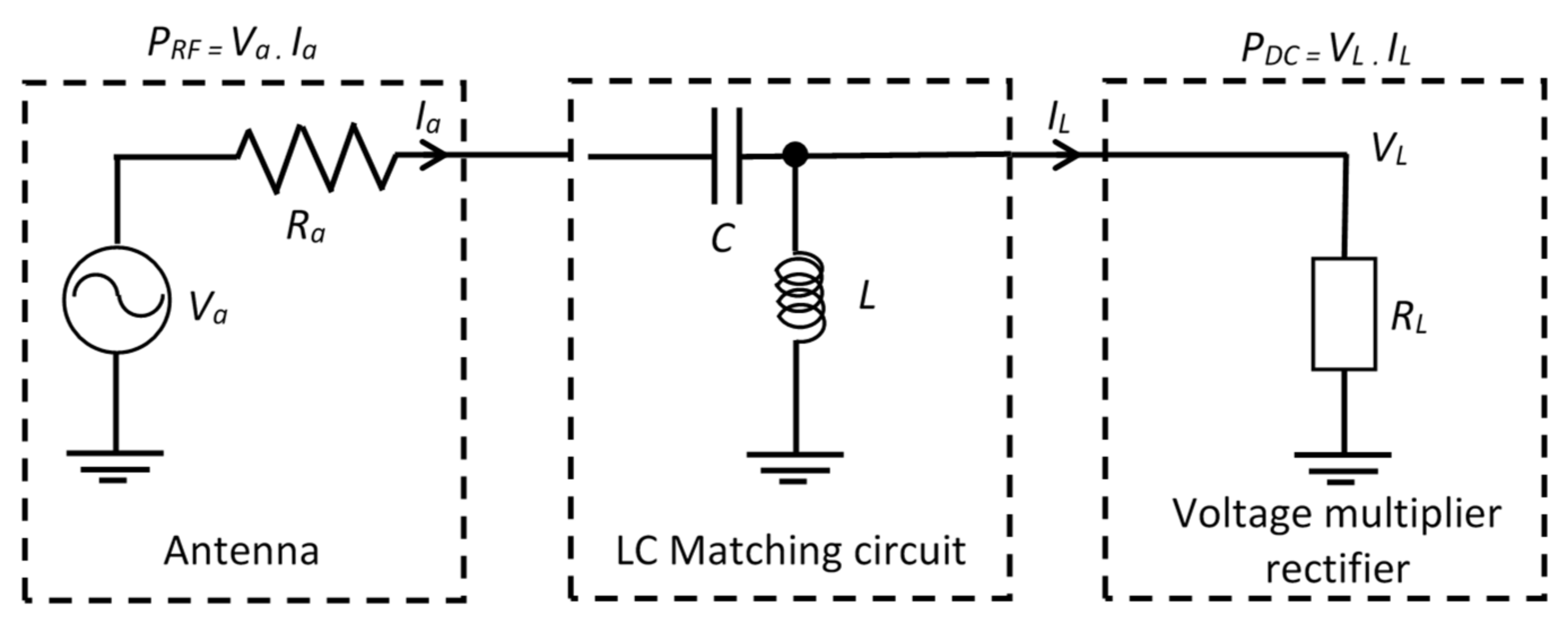

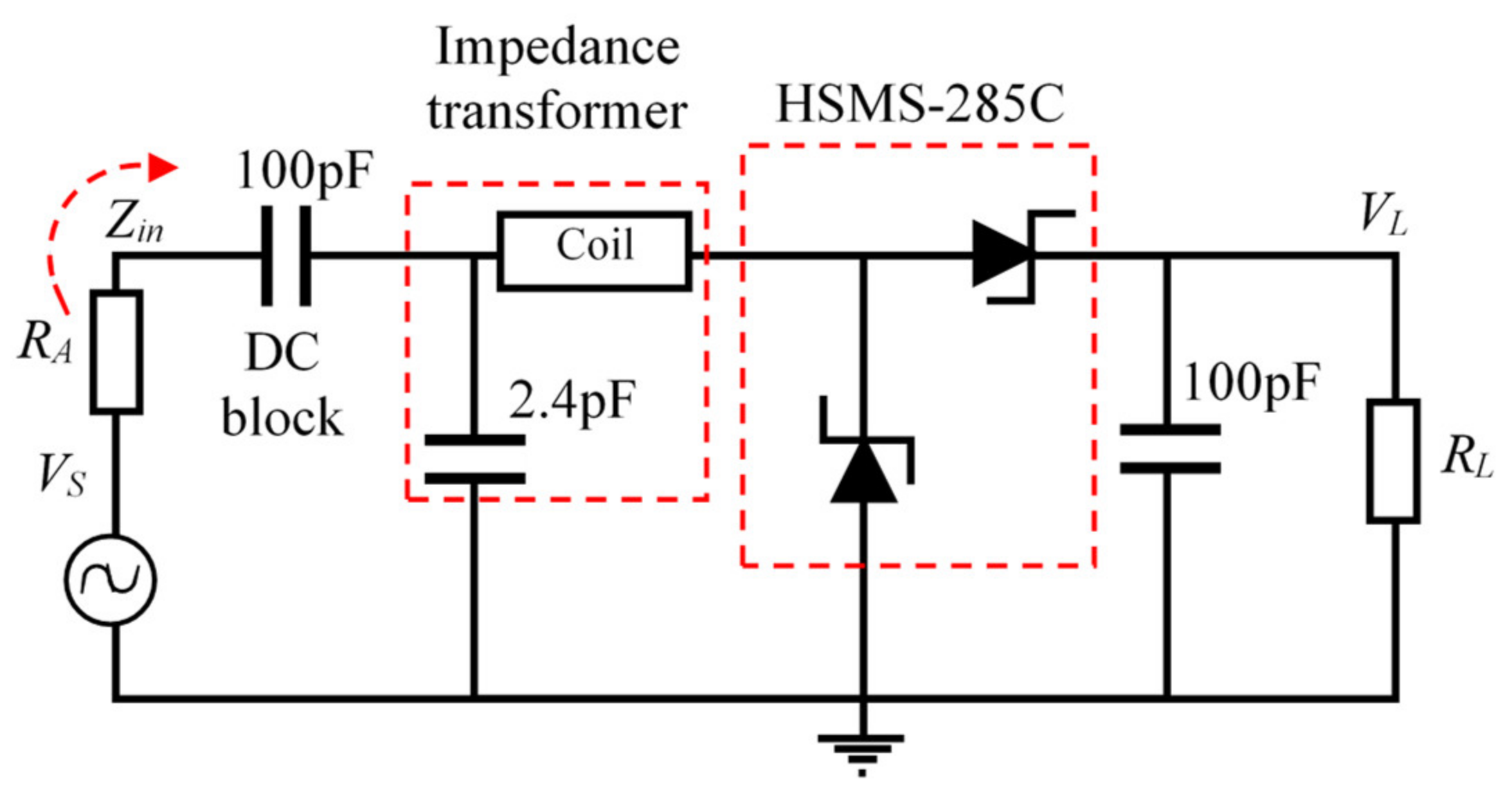

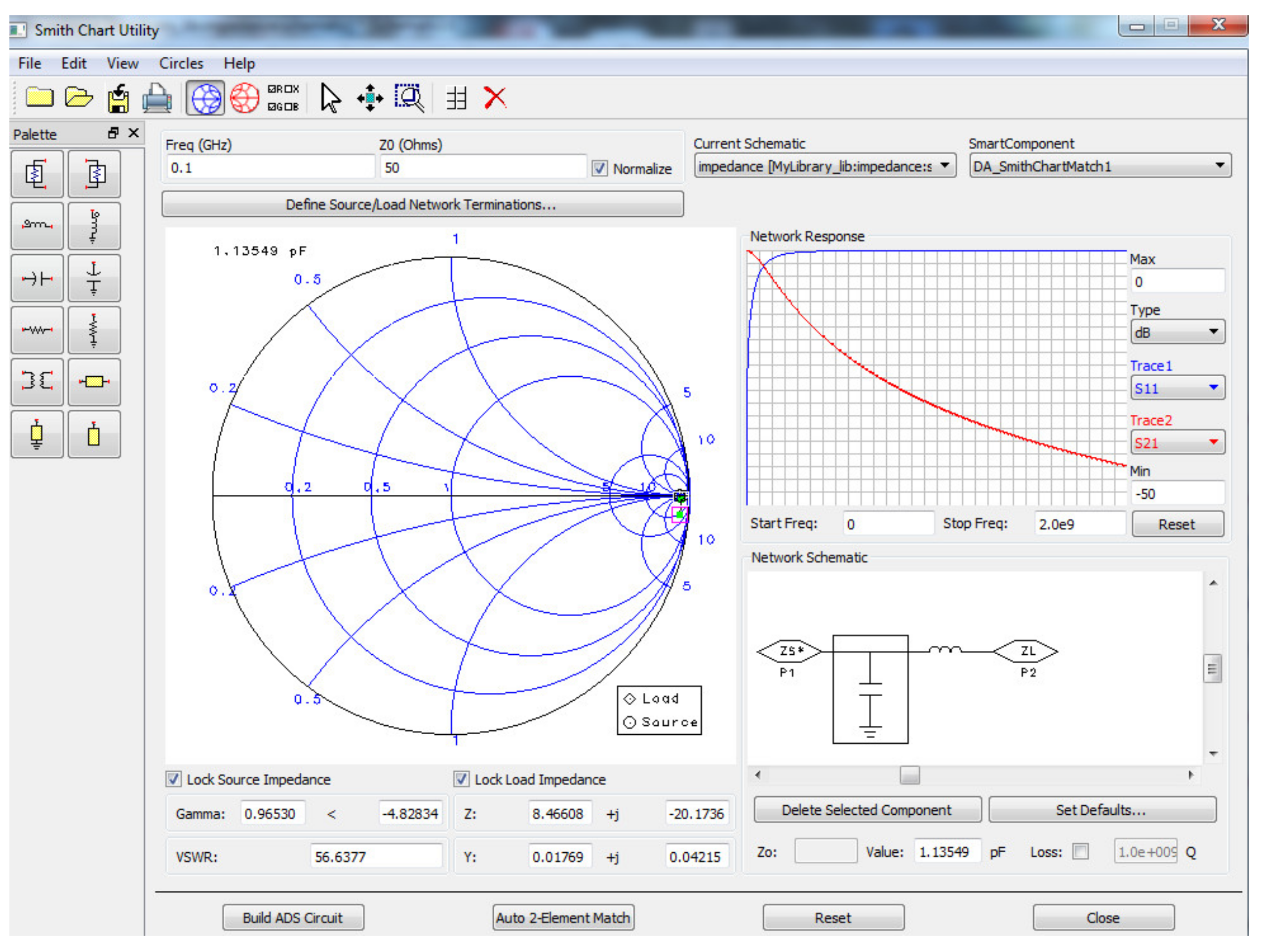

2. Methodology of Designing the Rectenna

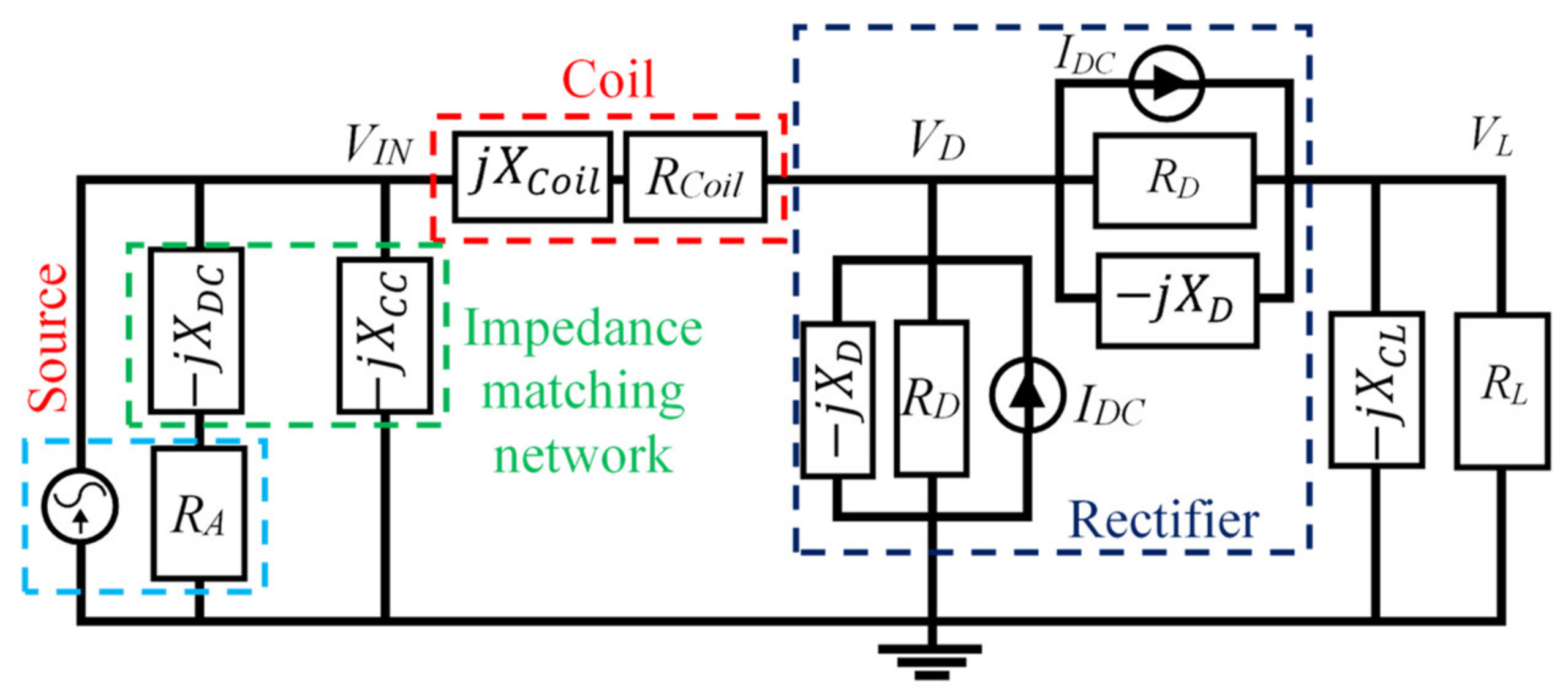

2.1. Linearized Analysis of Voltage Multiplier

2.2. Analytical Model of Cockcroft–Walton Voltage Multiplier Rectenna

- (1)

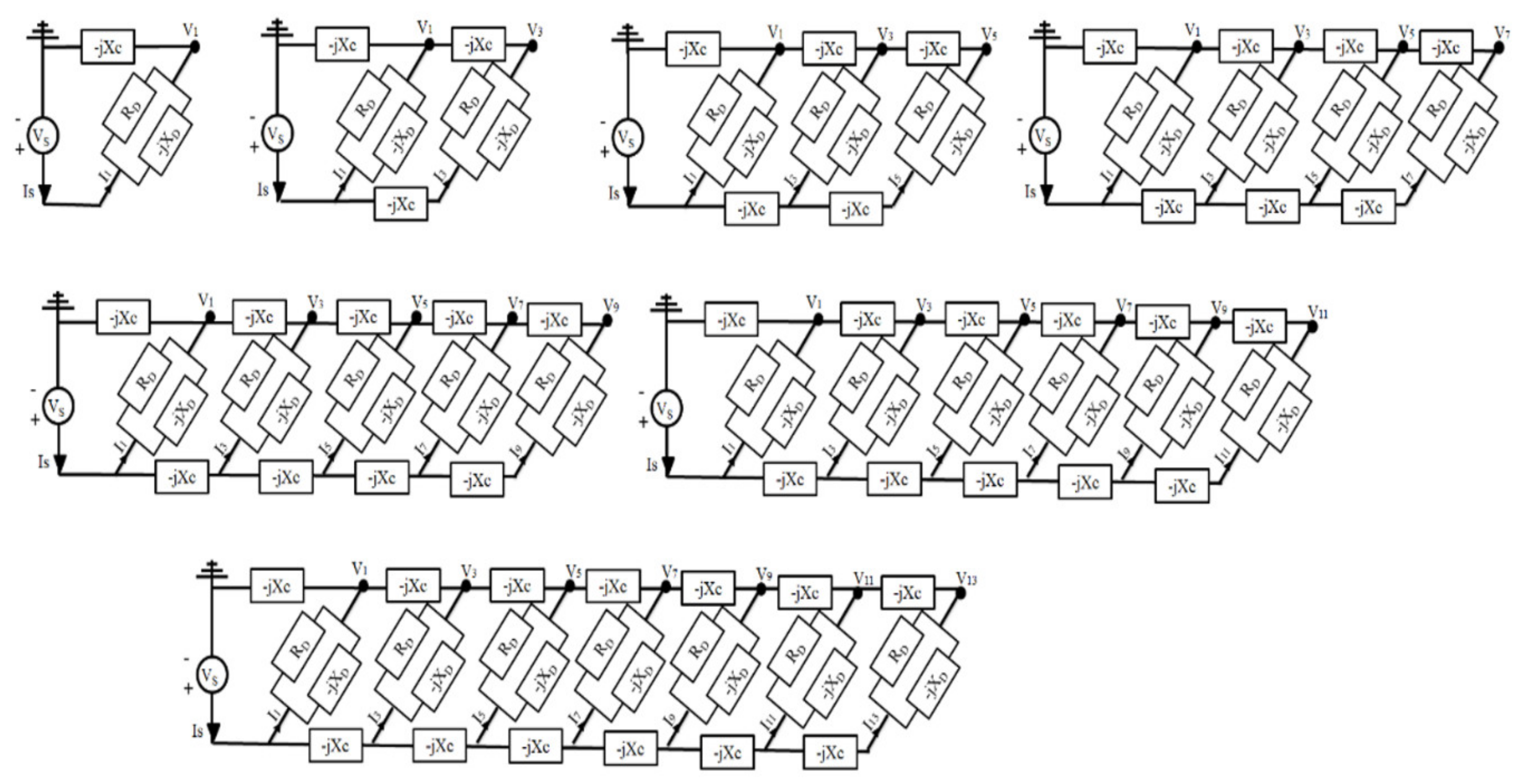

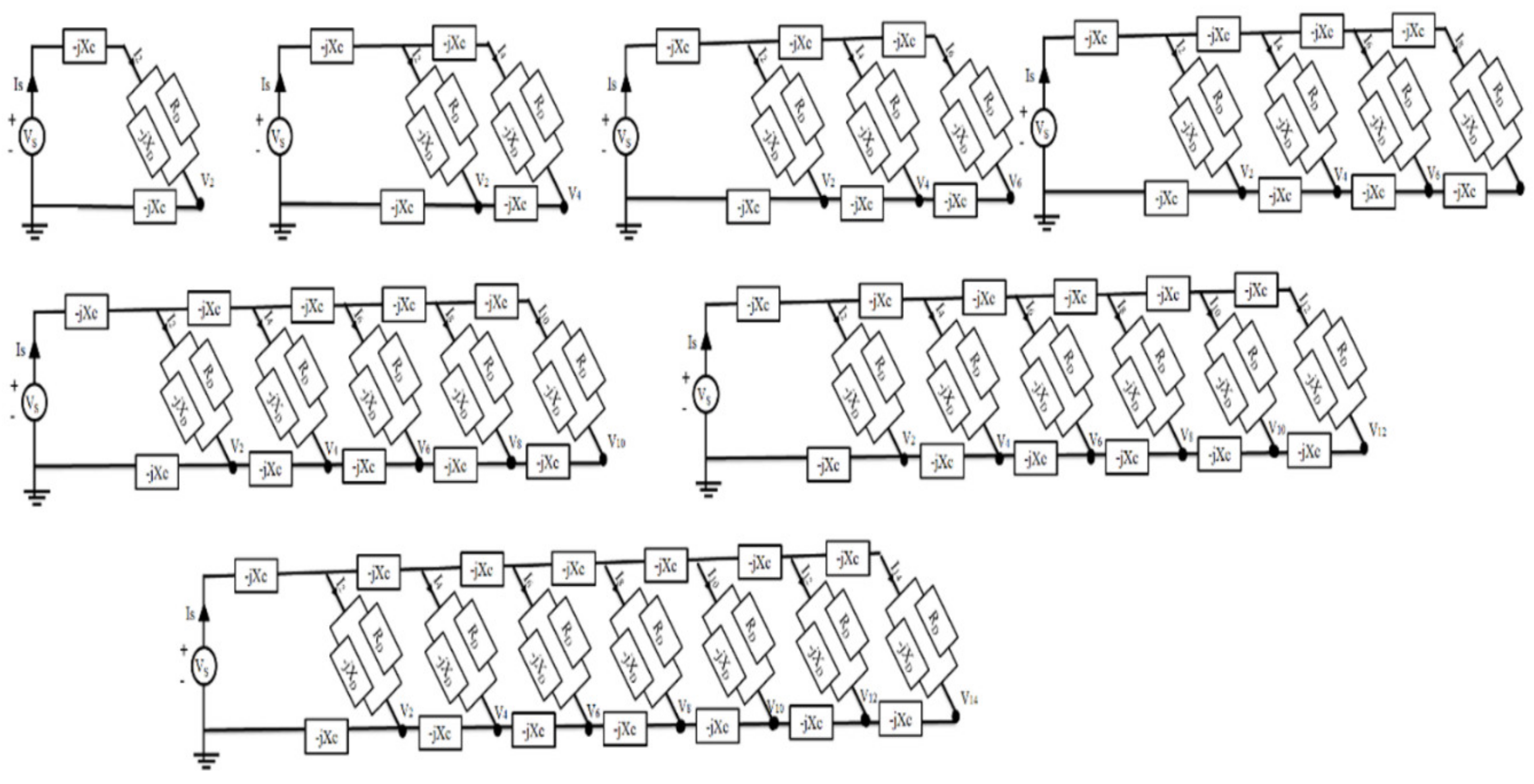

- MODE 1: During the negative half cycle of the first stage, when the first diode, D1, is ON state, the Id1 will pass through the diode D1. D2 is OFF at this stage, and the circuit behaves as an OPEN circuit. While in the second stage, D1 and D3 are in the ON state, while D2 and D4 are turned off. During stage three, D1, D3 and D5 are turned to the ON state, while D2, D4 and D6 are turned OFF. Until stage seven, “D1, D3, D5, D7, D9, D11 and D13” are turned ON, while “D2, D4, D6, D8, D10, D12 and D14” are turned OFF. Mode 1 is illustrated in Figure 8.

- (2)

- MODE 2: The same procedure is described in mode 2 since it represents the positive half cycle of the circuit. During the first stage, D2 is in the ON state while D1 is in the OFF state (the circuit is OPEN, and the diode D1 is OFF). During the second stage, D2 and D4 are turned ON while D1 and D3 are turned OFF. Until stage seven, “D2, D4, D6, D8, D10, D12 and D14” are turned ON and “D1, D3, D5, D7, D9, D11 and D13” are turned OFF. Mode 2 is represented in Figure 9.

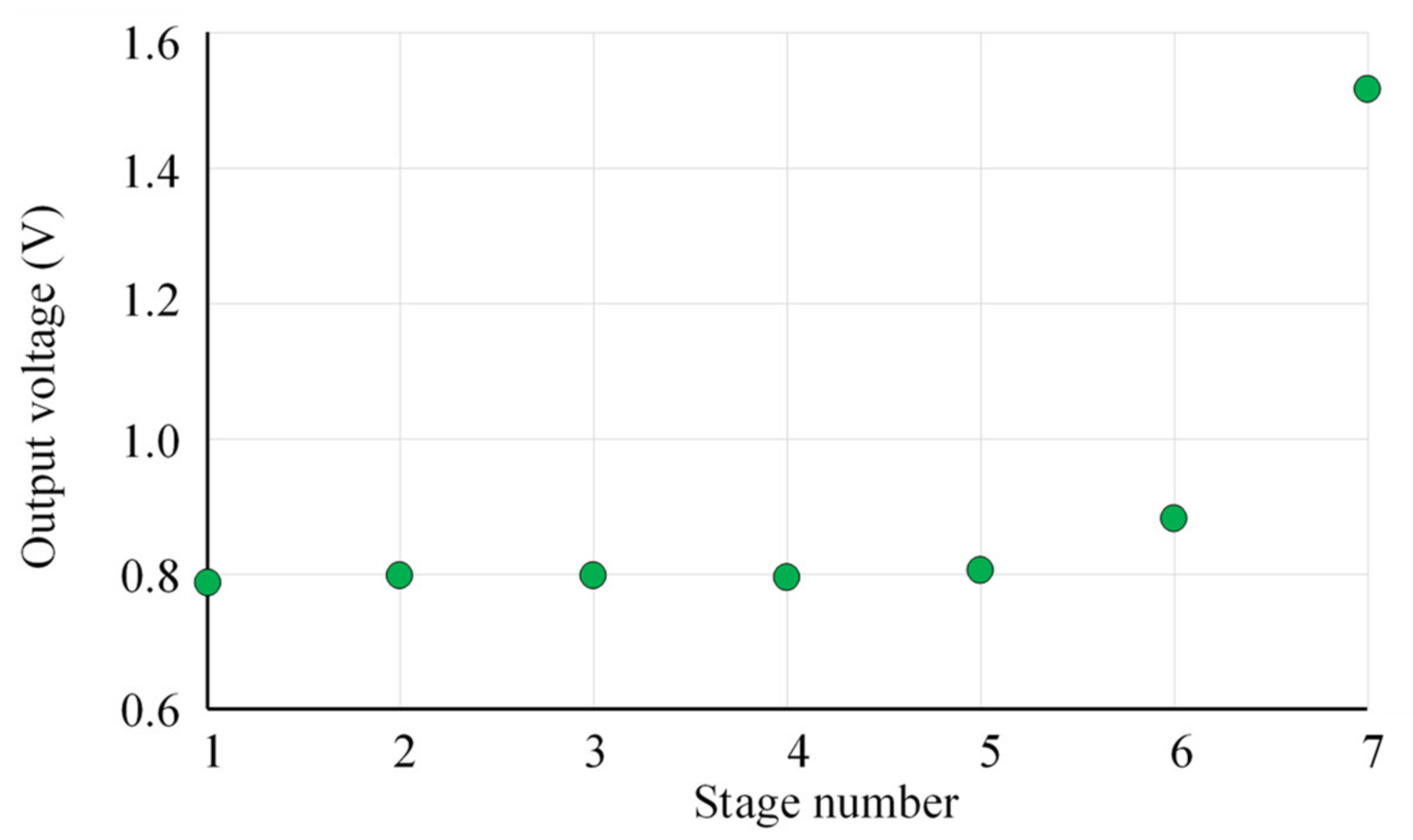

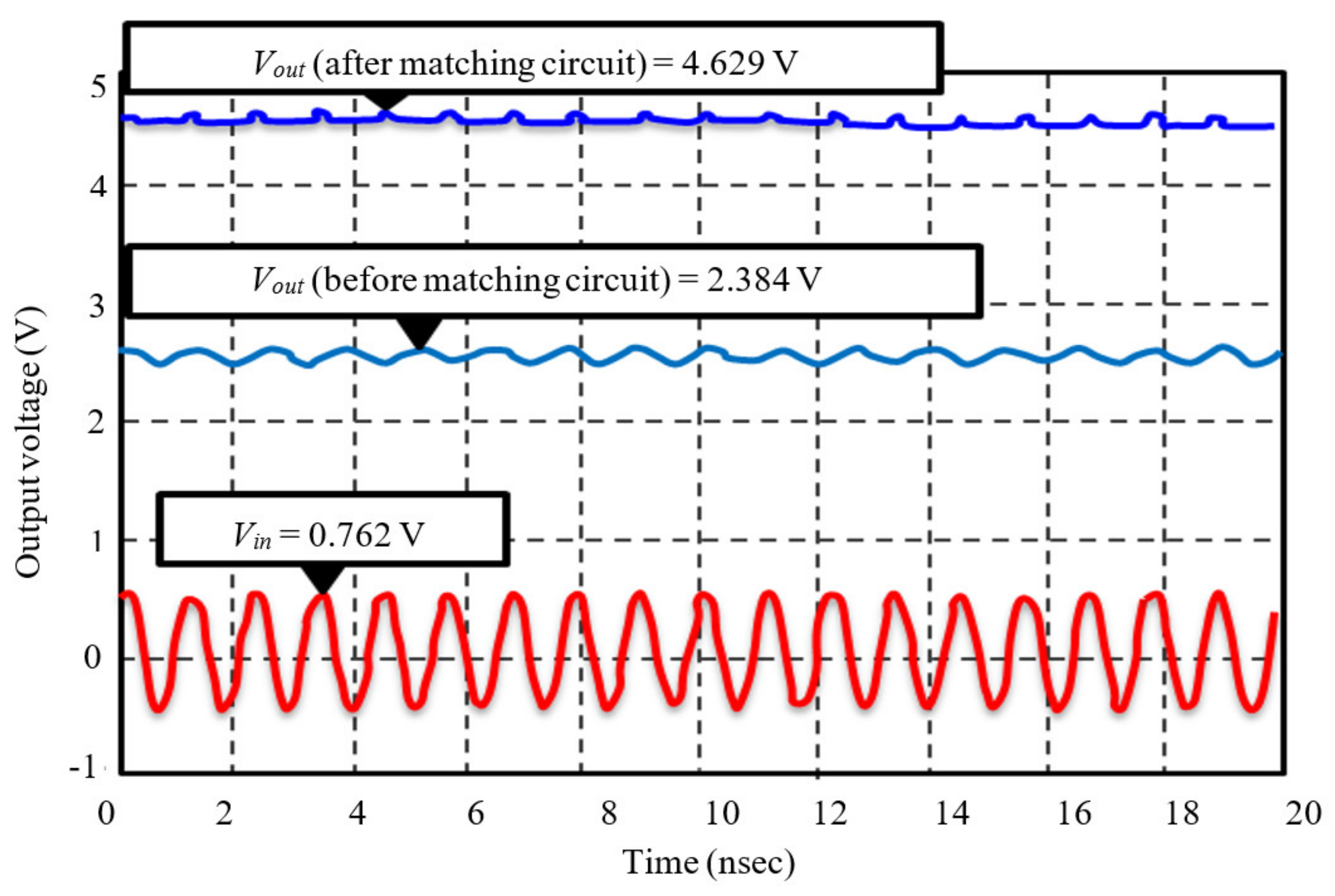

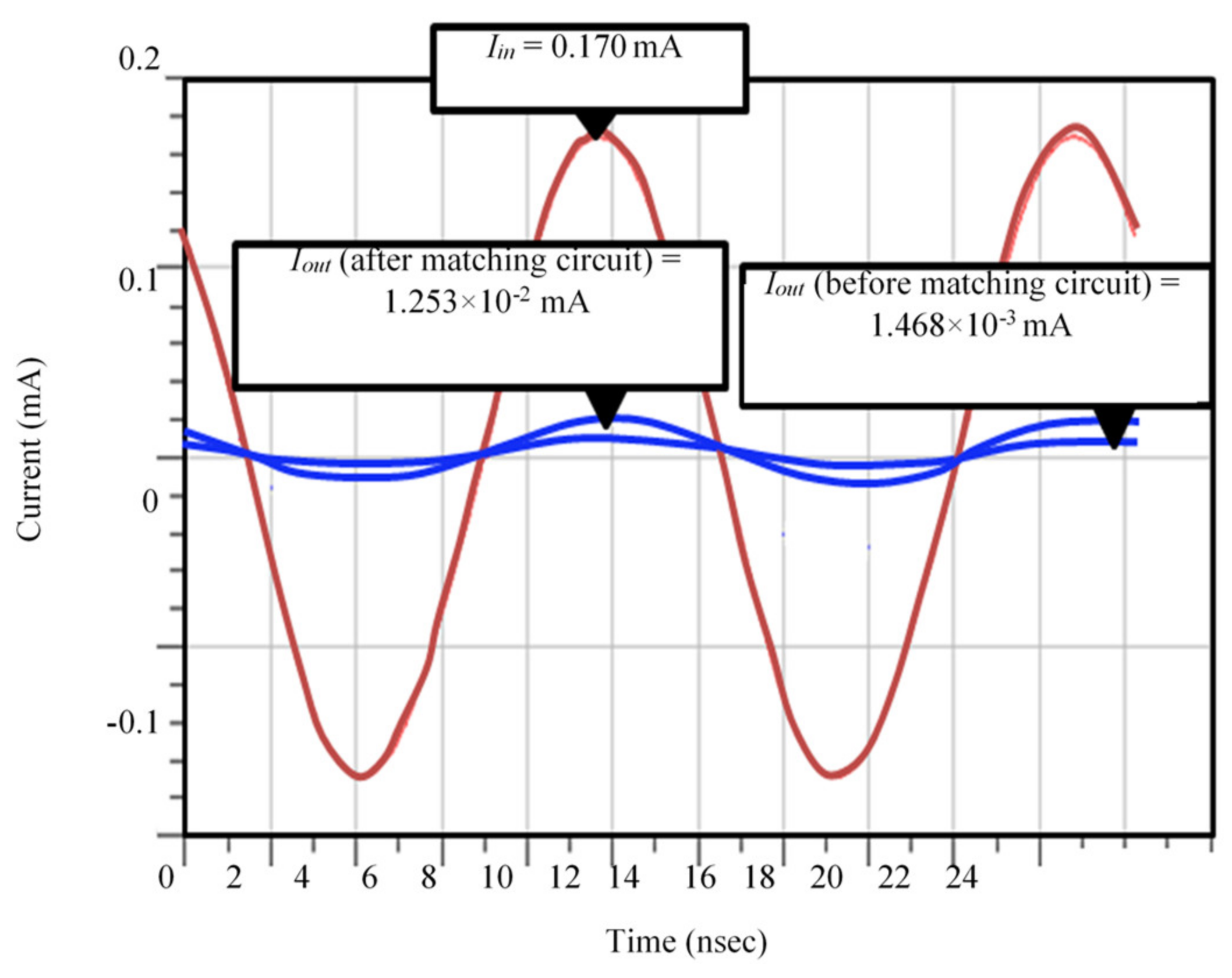

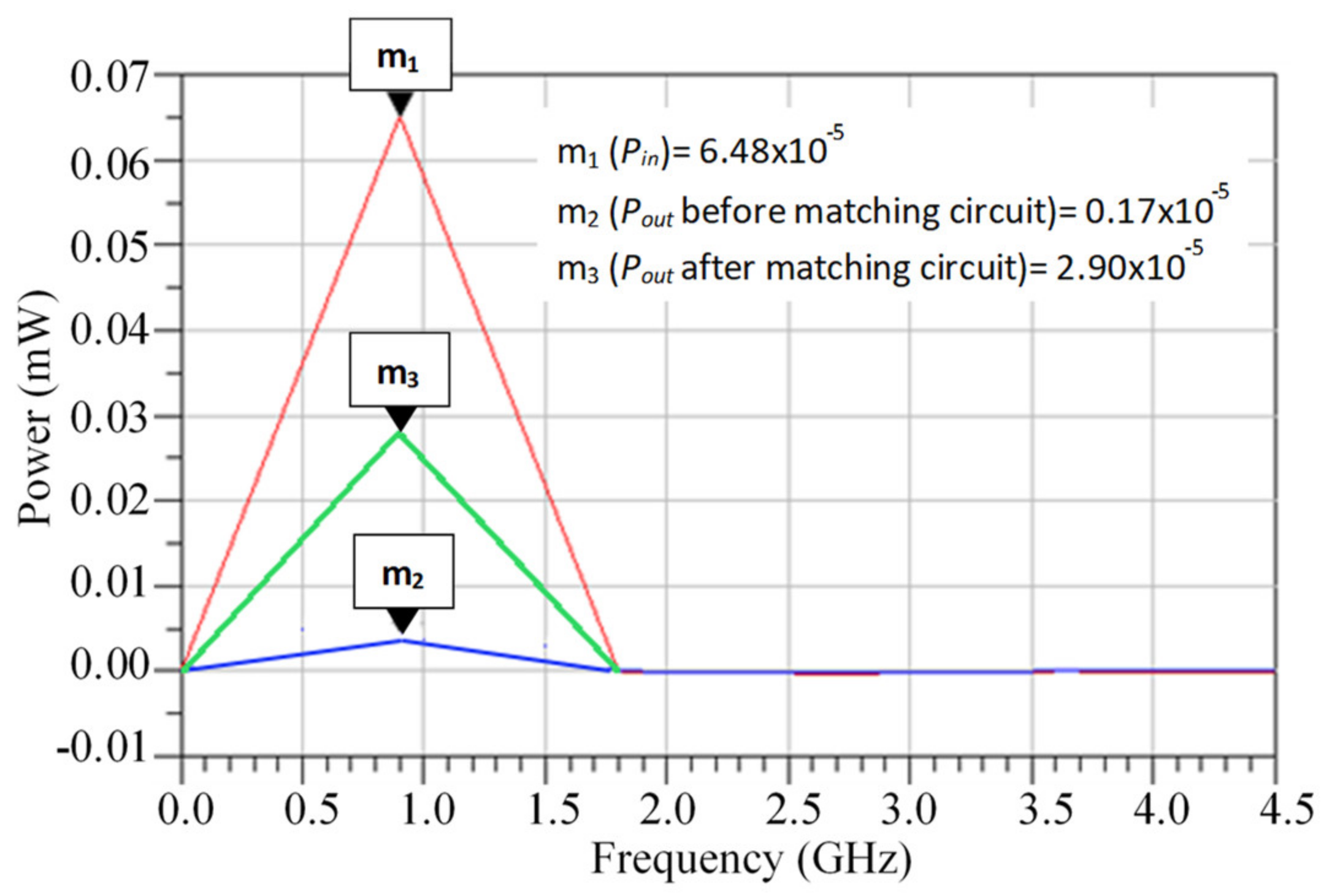

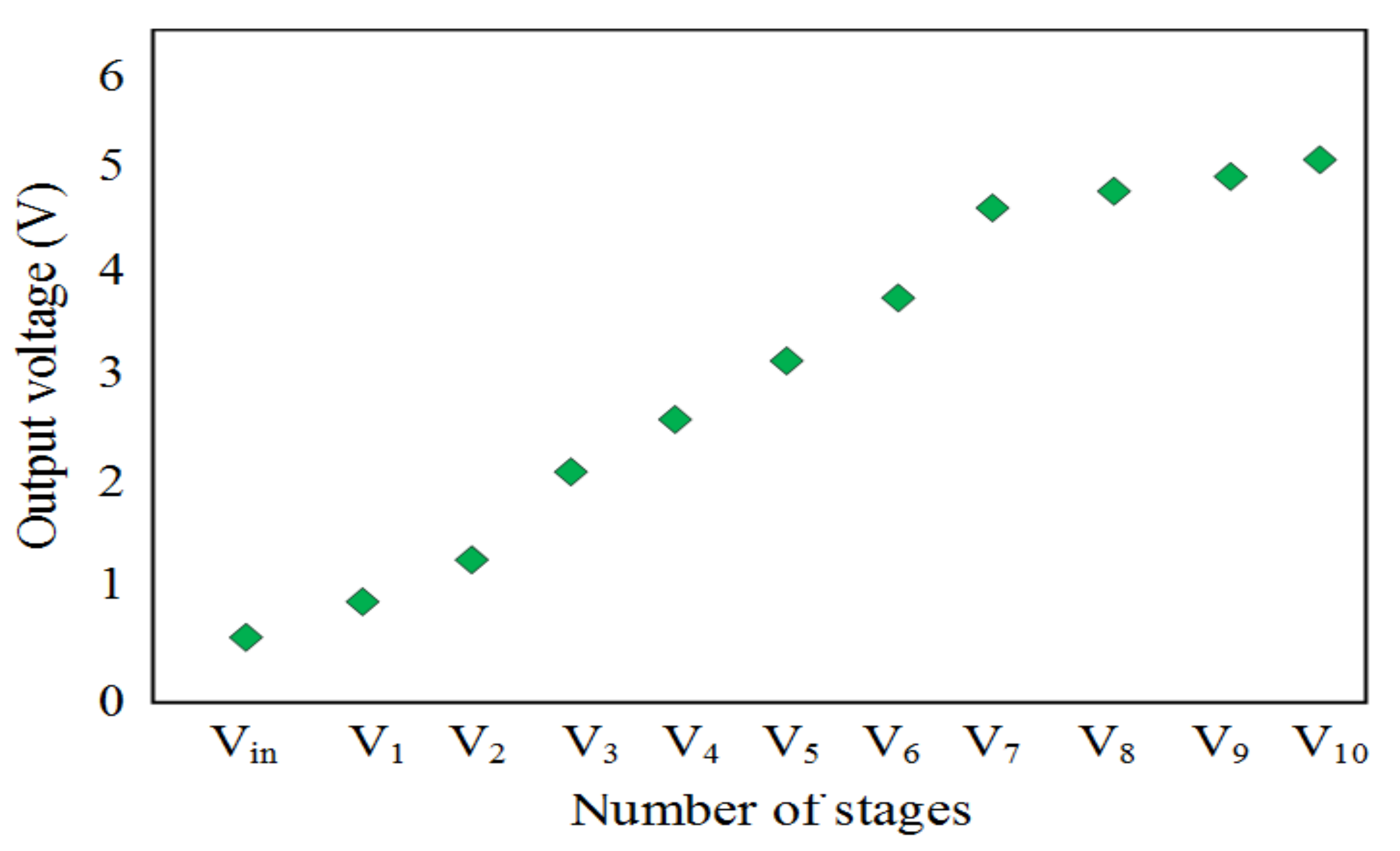

3. Simulation Results of Cockcroft–Walton Multiplier Voltage Rectifier

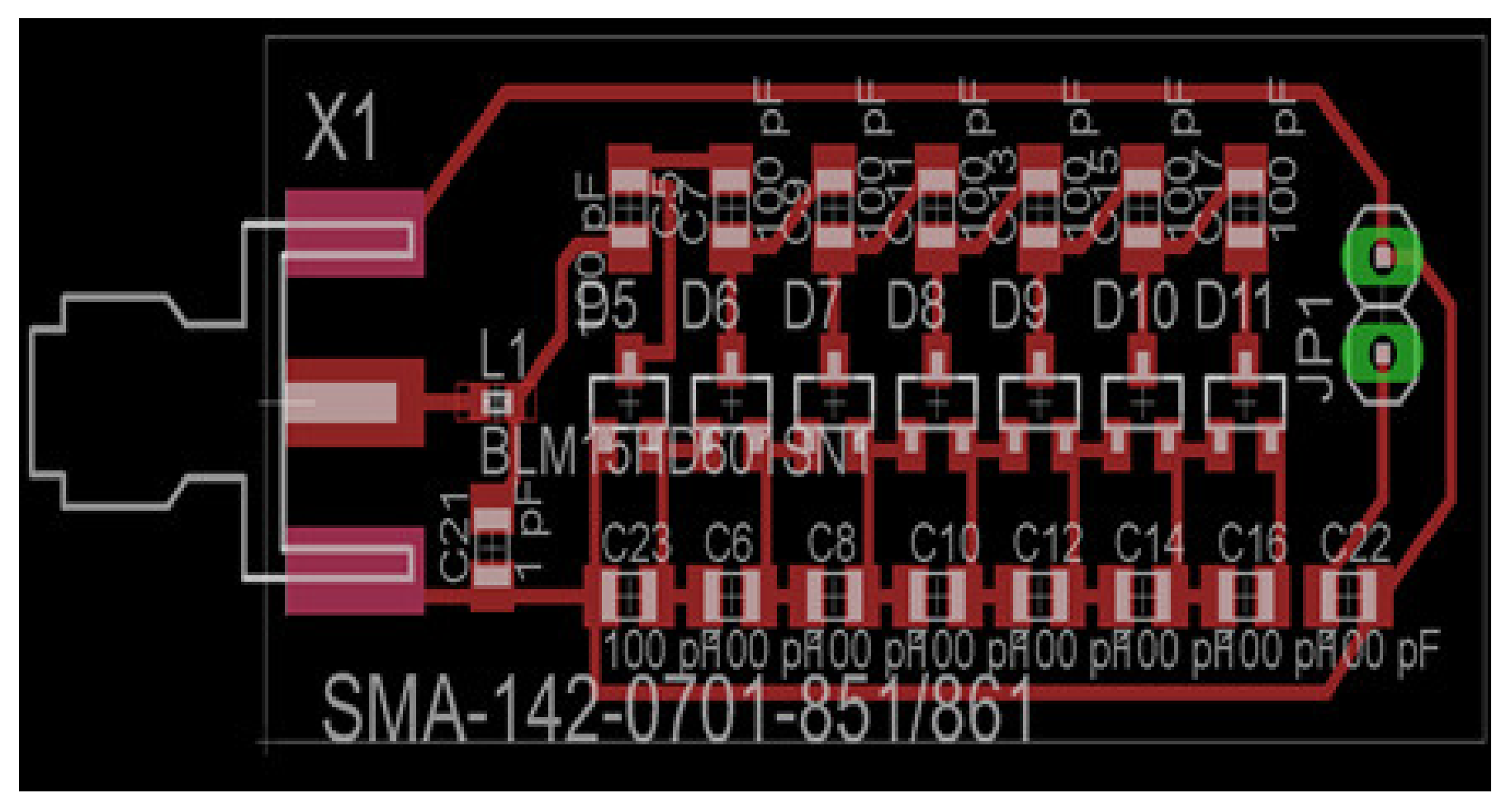

4. Fabrication of Cockcroft–Walton Multiplier Voltage Rectifier

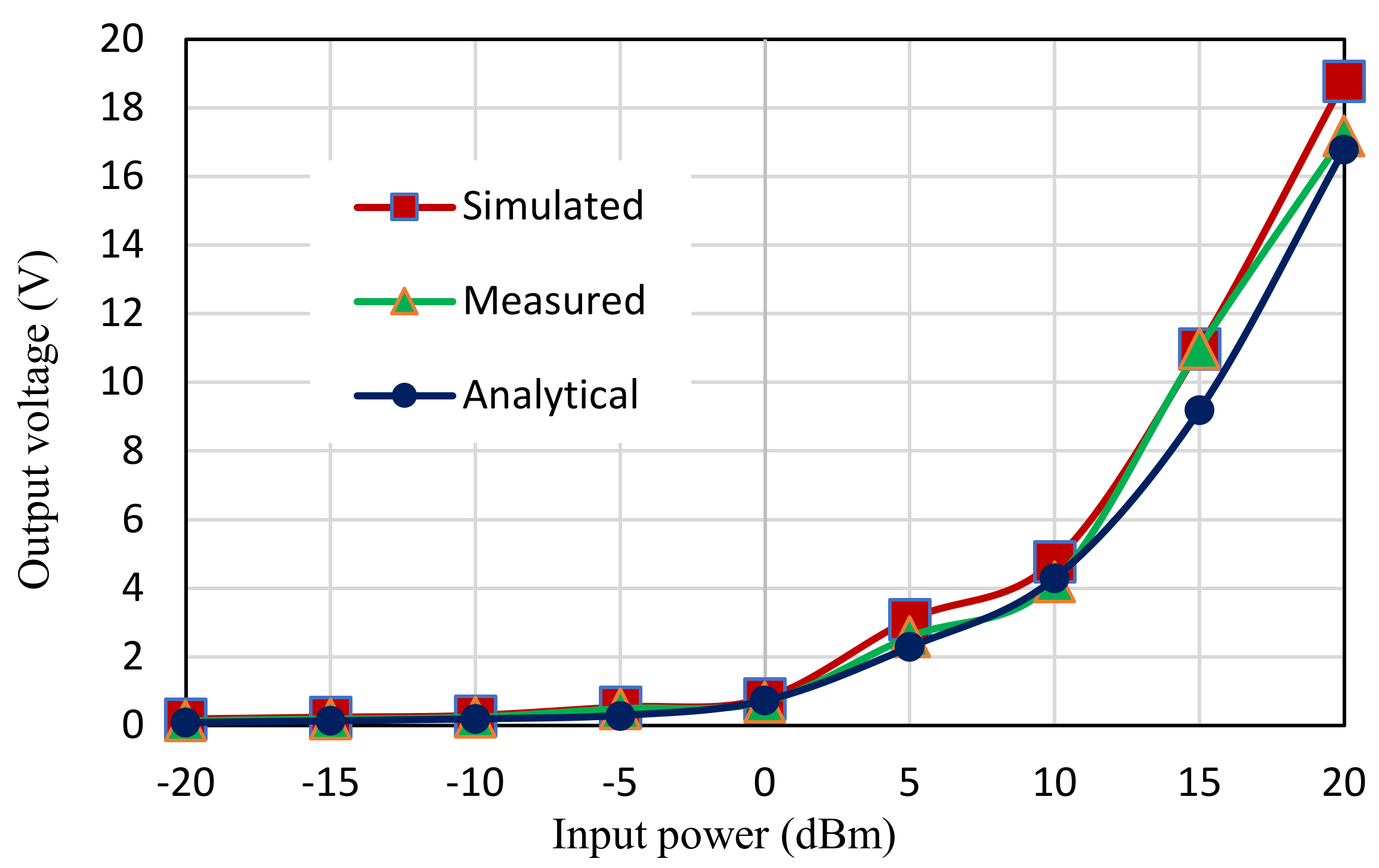

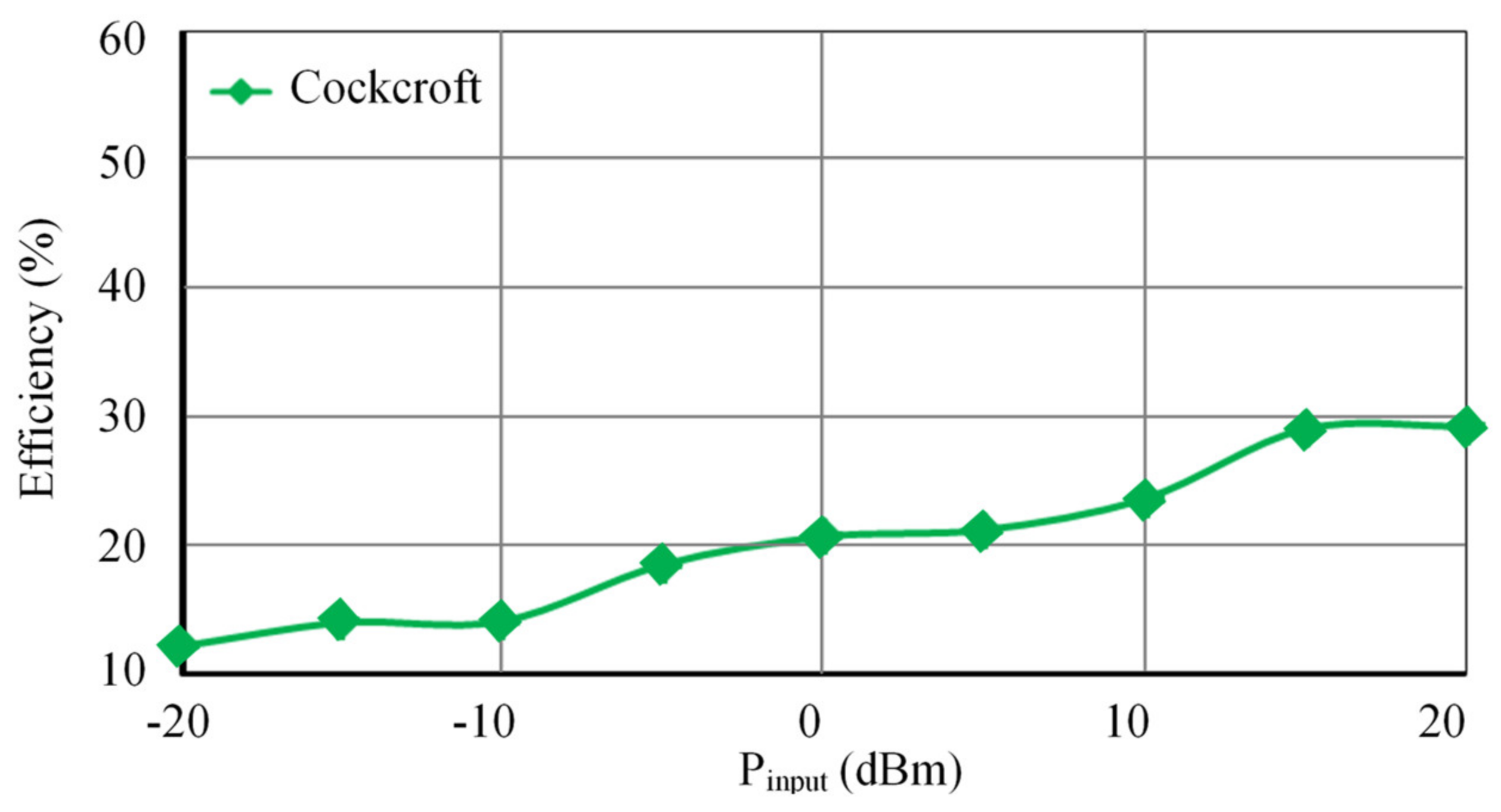

5. Results and Discussion

6. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Mandal, S.; Giri, S.K. Comparison of antennas for radio frequency energy harvesting in 0.2–2.4 GHz range. ICECT 2011, 1, 93–97. [Google Scholar]

- Ali, E.M.; Yahaya, N.Z.; al Assaf, A.H.; Alasali, F.; Patel, A.; Alqasem, B.H. Analysis and Maximizing RF Harvesting System based on Antenna Shapes for Aviation Applications. In Proceedings of the 2020 International Conference on Electrical Engineering and Control Technologies (CEECT), Swinburne, Australia, 10–13 December 2020; pp. 1–7. [Google Scholar]

- Kitazawa, S.; Ban, H.; Kobayashi, K. Energy harvesting from ambient RF sources. IMWS 2012, 34, 39–42. [Google Scholar]

- Sample, A.; Smith, J.R. Experimental results with two wireless power transfer systems. RWS 2009, 16–18. [Google Scholar]

- Papotto, G.; Carrara, F.; Palmisano, G.J. A 90-nm CMOS threshold-compensated RF energy harvester. IEEE J. Solid State Circuits 2011, 46, 1985–1997. [Google Scholar] [CrossRef]

- Ballo, A.; Bottaro, M.; Grasso, A.D.; Palumbo, G.J.E. Regulated charge pumps: A comparative study by means of verilog-AMS. Int. J. Sci. Eng. Res. 2020, 9, 998. [Google Scholar] [CrossRef]

- Piñuela, M.; Mitcheson, P.D.; Lucyszyn, S. Ambient RF energy harvesting in urban and semi-urban environments. IEEE Trans. Microw. Theory 2013, 61, 2715–2726. [Google Scholar] [CrossRef]

- Li, B.; Shao, X.; Shahshahan, N.; Goldsman, N.; Salter, T.; Metze, G.M. An antenna co-design dual band RF energy harvester. IEEE Trans. Circuits Syst. I Regul. Pap. 2013, 60, 3256–3266. [Google Scholar] [CrossRef]

- Visser, H.J.; Reniers, A.C.; Theeuwes, J.A. Ambient RF energy scavenging: GSM and WLAN power density measurements. EuMC 2008, 21, 721–724. [Google Scholar]

- Kundu, P.; Acharjee, J.; Mandal, K. Design of an efficient rectifier circuit for RF energy harvesting system. Int. J. Adv. Eng. Manag. 2017, 2, 94–97. [Google Scholar] [CrossRef]

- Waghamare, N.M.; Argelwar, R.P.J. High voltage generation by using Cockcroft-Walton multiplier. IJSETR 2015, 4, 256–259. [Google Scholar]

- Nimo, A.; Grgić, D.; Reindl, L.M.J.S. Optimization of passive low power wireless electromagnetic energy harvesters. Sensors 2012, 12, 13636–13663. [Google Scholar] [CrossRef]

- Tanzawa, T. An Analytical Model of AC-DC Charge Pump Voltage Multipliers. IEICE Trans. Electron. 2016, 99, 108–118. [Google Scholar] [CrossRef]

- Jia, P.; Yuan, Y.J. Analysis and implementation of LC series resonant converter with secondary Side clamp diodes under DCM operation for high step-up applications. J. Power Electron. 2019, 19, 363–379. [Google Scholar]

- Alghaythi, M.L.; O’Connell, R.M.; Islam, N.E.; Khan, M.M.S.; Guerrero, J.M. A High Step-Up Interleaved DC-DC Converter With Voltage Multiplier and Coupled Inductors for Renewable Energy Systems. IEEE Access 2020, 8, 123165–123174. [Google Scholar] [CrossRef]

- Rajaei, A.; Dehghanian, I.; Shahparasti, M.; Poursmaeil, E.J. Behavioral switching model for current-fed Cockcroft–Walton voltage multiplier. J. Power Electron. 2020, 20, 365–375. [Google Scholar] [CrossRef]

- Cardoso, A.J.; de Carli, L.G.; Galup-Montoro, C.; Schneider, M.C.J.; Papers, S.I.R. Analysis of the rectifier circuit valid down to its low-voltage limit. IEEE Trans. Circuits Syst. I 2011, 59, 106–112. [Google Scholar] [CrossRef]

- Ali, E.; Yahaya, N.; Perumal, N.; Zakariya, M. Design of RF to DC rectifier at GSM band for energy harvesting applications. J. Eng. Sci. Soc. 2014, 10, 15–22. [Google Scholar]

- Ali, E.; Yahaya, N.; Perumal, N.; Zakariya, M.; Sciences, A. Design and development of harvester rectenna at GSM band for battery charging applications. ARPN J. Eng. Appl. Sci. 2015, 10, 21. [Google Scholar]

- de Carli, L.G.; Juppa, Y.; Cardoso, A.J.; Galup-Montoro, C.; Schneider, M.C.J. Maximizing the power conversion efficiency of ultra-low-voltage CMOS multi-stage rectifiers. IEEE Trans. Circuits Syst. I 2015, 62, 967–975. [Google Scholar] [CrossRef]

- Ali, E.; Yahaya, N.; Perumal, N.; Zakariya, M.J. Development Development of Cockcroft-Walton voltage multiplier for RF energy harvesting applications. J. Sci. Res. Dev. 2016, 3, 47–51. [Google Scholar]

- Luo, Z.; Ker, M.-D.; Cheng, W.-H.; Yen, T.-Y.J. Regulated charge pump with new clocking scheme for smoothing the charging current in low voltage CMOS process. IEEE Trans. Circuits Syst. I 2016, 64, 528–536. [Google Scholar] [CrossRef]

- Ali, E.; Yahaya, N.; Perumal, N.; Zakariya, M.J.J. Design of microstrip patch antenna at 900 MHz for charging mobile applications. J. Eng. Appl. Sci. 2017, 12, 988–993. [Google Scholar]

- Ali, E.M.; Yahaya, N.Z.; Nallagownden, P.; Zakariya, M.A.J. A novel rectifying circuit for microwave power harvesting system. Int. J. RF Microw. Comput. Aided Eng. 2017, 27, e21083. [Google Scholar]

- Okba, A.; Takacs, A.; Aubert, H.; Charlot, S.; Calmon, P.-F.J. Multiband rectenna for microwave applications. Comptes Rendus Phys. 2017, 18, 107–117. [Google Scholar] [CrossRef]

- Shahabuddin, A.A.; Shalu, P.D.; Akter, N.J. Optimized Process Design of RF Energy Harvesting Circuit for Low Power Devices. Int. J. Appl. Eng. Res. 2018, 13, 849–854. [Google Scholar]

- Ali, E.M.; Yahaya, N.Z.; Nallagownden, P.; Alqasem, B.H.J.; Engineering, M.C.A. Enhanced Dickson voltage multiplier rectenna by developing analytical model for radio frequency harvesting applications. Int. J. RF Microw. Comput. Aided Eng. 2019, 29, e21657. [Google Scholar] [CrossRef]

- Nimo, A.; Beckedahl, T.; Ostertag, T.; Reindl, L.J. Analysis of passive RF-DC power rectification and harvesting wireless RF energy for micro-watt sensors. AIMS Energy 2015, 3, 184–200. [Google Scholar] [CrossRef]

- Agrawal, S.; Pandey, S.; Singh, J.; Kondekar, P.N. An efficient RF energy harvester with tuned matching circuit. VLSI Des. Test 2013, 382, 138–145. [Google Scholar]

- Devi, K.; Norashidah, M.D.; Chakrabarty, C.K.; Sadasivam, S. Design of an RF-DC conversion circuit for energy harvesting. In Proceedings of the 2012 IEEE International Conference on Electronics Design, Systems and Applications (ICEDSA), Kuala Lumpur, Malaysia, 5–6 November 2012; pp. 156–161. [Google Scholar]

- Nintanavongsa, P.; Muncuk, U.; Lewis, D.R. Circuits, and systems, Design optimization and implementation for RF energy harvesting circuits. IEEE J. Emerg. Sel. Top. Circuits Syst. 2012, 2, 24–33. [Google Scholar] [CrossRef]

- Ibrahim, R.B.; Mohd, S.H.S.B.; Khir, H.B.M.; Zakariya, M.A.B.; Daud, H. Powering LED from Wi-Fi: A qualitative assessment for rectenna design. In Proceedings of the 2014 15th International Conference on Sciences and Techniques of Automatic Control and Computer Engineering (STA), Hammamet, Tunisia, 21–23 December 2014; pp. 793–796. [Google Scholar]

- Nintanavongsa, P. A survey on RF energy harvesting: Circuits and protocols. Energy Procedia 2014, 56, 414–422. [Google Scholar] [CrossRef]

- Keyrouz, S.; Visser, H. Efficient direct-matching rectenna design for RF power transfer applications. J. Phys. Conf. Ser. 2013, 476, 12093–12097. [Google Scholar] [CrossRef]

- Chaour, I.; Fakhfakh, A.; Kanoun, O.J.S. Enhanced passive RF-DC converter circuit efficiency for low RF energy harvesting. Sensors 2017, 17, 546. [Google Scholar] [CrossRef]

- Hridayeta, B.; Singhal, P.J. RF Energy Harvesting from Cell Phone in GSM900 Band. Int. Res. J. of Eng. Technol. (IRJET) 2015, 2, 420–424. [Google Scholar]

- Arrawatia, M.; Baghini, M.S.; Kumar, G. RF energy harvesting system from cell towers in 900 MHz band. In Proceedings of the 2011 National Conference on Communications (NCC), Bangalore, India, 28–30 January 2011; pp. 1–5. [Google Scholar]

- Monti, G.; Congedo, F.; de Donno, D.; Tarricone, L.J. Monopole-based rectenna for microwave energy harvesting of UHF RFID systems. Prog. Electromagn. Res. 2012, 31, 109–121. [Google Scholar] [CrossRef][Green Version]

- Akter, N.; Hossain, B.; Kabir, H.; Bhuiyan, A.H.; Yeasmin, M.; Sultana, S. Design and performance analysis of 10-stage voltage doublers RF energy harvesting circuit for wireless sensor network. J. Commun. Eng. Netw. 2014, 2, 84–91. [Google Scholar] [CrossRef]

- Adam, I.; Malek, M.F.A.; Yasin, M.N.M.; Rahim, H.A.J.M.; Letters, O.T. Double band microwave rectifier for energy harvesting. Microw. Opt. Technol. Lett. 2016, 58, 922–927. [Google Scholar] [CrossRef]

- Lenin, A.; Abarna, P.J. Design and simulation of energy harvesting system using GSM signal. Int. J. Latest Trends Eng. 2014, 3, 13–25. [Google Scholar]

- Yuvaraj, K.; Samuel, A.A.J. Electronics A patch antenna to harvest ambient energy from multiband rf signals for low power devices. Int. J. Emerg. Technol. Comput. Sci. Electron. 2015, 13, 218. [Google Scholar]

- Ansari, T.R.; Khan, A.; Ansari, I.J. Wireless charging of mobile battery via optimization of RF energy harvesting system. Int. J. Sci. Eng. Res. 2015, 6, 7. [Google Scholar] [CrossRef]

- Jordana, J.; Reverter, F.; Gasulla, M.J. Power Efficiency Maximization of an RF Energy Harvester by Fine-tuning an L-matching Network and the Load. Procedia Eng. 2015, 120, 655–658. [Google Scholar] [CrossRef]

- Kasar, Ö.; Gözel, M.A.; Kahriman, M.J.M.; Letters, O.T. Analysis of rectifier stage number and load resistance in an RF energy harvesting circuit. Microw. Opt. Technol. Lett. 2020, 62, 1542–1547. [Google Scholar] [CrossRef]

| Design Parameters | Cockcroft–Walton Voltage Multiplier Circuit |

| Matching circuit parameters | L = 8.33 nH C = 1.135 pF |

| The used diodes | Seven Schottky diodes of HSMS-285C |

| Number of capacitors | 15 capacitors |

| Arrangement of capacitors | The capacitors and diodes are arranged in series |

| Pin (dBm) | Input Power | Output Voltage (V) | Output Current (A) | Output Power (Watt) | Ripple Voltage (V) |

|---|---|---|---|---|---|

| (Watt) | |||||

| −20 | 8.42 × 10−7 | 0.248 | 1.290 × 10−7 | 1.59 × 10–8 | 4.703 × 10–6 |

| −15 | 6.95 × 10−7 | 0.334 | 1.437 × 10−7 | 2.39 × 10−8 | 5.239 × 10−6 |

| −10 | 2.37 × 10−6 | 0.448 | 4.241 × 10−7 | 9.49 × 10−8 | 1.546 × 10−5 |

| −5 | 7.67 × 10−6 | 0.691 | 1.259 × 10−6 | 4.35 × 10−7 | 4.590 × 10−5 |

| 0 | 1.65 × 10−5 | 0.879 | 6.712 × 10−6 | 2.95 × 10−6 | 2.447 × 10−5 |

| 5 | 4.49 × 10−5 | 2.51 | 1.116 × 10−5 | 1.40 × 10−5 | 4.069 × 10−4 |

| 10 | 6.48 × 10−5 | 4.629 | 1.253 × 10−5 | 2.90 × 10−5 | 4.568 × 10−4 |

| 15 | 9.71 × 10−4 | 11.06 | 4.250 × 10−5 | 2.35 × 10−4 | 1.550 × 10−3 |

| 20 | 4.22 × 10−3 | 17.84 | 1.233 × 10−4 | 1.09 × 10−3 | 4.450 × 10−3 |

| Module | Analytical Results | Simulation Results | Experimental Results |

|---|---|---|---|

| Output voltage | 4.051 V | 4.629 V | 4.860 V |

| Output current | 69.31 µA | 65.46 µA | 68.73 µA |

| Output power | 0.2142 mW | 0.242 mW | 0.2362 mW |

| Ref. | Circuit Design | Output Voltage and Current | Power | Efficiency |

|---|---|---|---|---|

| [37] | Six stages voltage multiplier (Dickson) is combined with coupled square microstrip antenna | Output voltage of 2.78 V | Received power is 50.28 mW | - |

| [38] | Five stages voltage multiplier is combined with a T-shaped monopole antenna | The output voltage is 1.6 V | Input power density of 80 W/cm2 | Efficiency is 54% |

| [39] | Ten-stages voltage multiplier RF energy harvesting circuit | Output voltage range of 5–36.489 V | - | - |

| [41] | Nine stages of voltage doubler combined with matching circuit | Output voltage is 1.732 V, and output current is 0.1814 mA | Power level is 0.5206 dBm. | - |

| [42] | Seven-stage voltage doubler integrated with E-shaped microstrip antenna | Output voltage is 2.513 V, and output current is 25 µA | - | - |

| [43] | Nine stages of Greinacher voltage double combined with matching circuit | Output voltage is 1.732 V, and output current is 0.1814 mA | - | - |

| [44] | RF energy harvester was designed by fine-tuning an L-matching network- | - | - | The circuit achieved maximum power efficiencies of 10.9%, 30.7%, and 55.2% for input powers of −30 dBm, −20 dBm and −10 dBm |

| [40] | Seven-stage rectifier. A Villard configuration is chosen based on HSMS 2850 Schottky diodes. The size has a large profile (190 × 33 mm) | Voltages of 9.17 V and 3.78 V are obtained at 900 MHz and 550 MHz | - | - |

| [35] | RF- DC circuit converter, which contains from 3 stages voltage multiplier (Dickson) based on HSMS 285 | The design has an inductor in series with the input capacitance. The proposed design provides 19.43 μW output power and around 1 V output voltage | - | - |

| [45] | Three-stage Dickson rectifier circuit with HSMS-285C Schottky diode. | Output voltage is 5.16 V | - | Maximum 77% efficiency |

| This work | A proposed voltage multiplier rectifier circuit is developed using Schottky diodes | The output voltage range is (0.756–17.58) V | The maximum output power is 0.2577 mW | Maximum efficiency is 29.85% |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ali, E.M.; Yahaya, N.Z.; Saraereh, O.A.; Assaf, A.H.A.; Alqasem, B.H.; Iqbal, S.; Ibrahim, O.; Patel, A.V. Power Conversion Using Analytical Model of Cockcroft–Walton Voltage Multiplier Rectenna. Electronics 2021, 10, 881. https://doi.org/10.3390/electronics10080881

Ali EM, Yahaya NZ, Saraereh OA, Assaf AHA, Alqasem BH, Iqbal S, Ibrahim O, Patel AV. Power Conversion Using Analytical Model of Cockcroft–Walton Voltage Multiplier Rectenna. Electronics. 2021; 10(8):881. https://doi.org/10.3390/electronics10080881

Chicago/Turabian StyleAli, Esraa Mousa, Nor Zaihar Yahaya, Omar Aqeel Saraereh, Anwar Hamdan Al Assaf, Bilal Hasan Alqasem, Shahid Iqbal, Oladimeji Ibrahim, and Amit V Patel. 2021. "Power Conversion Using Analytical Model of Cockcroft–Walton Voltage Multiplier Rectenna" Electronics 10, no. 8: 881. https://doi.org/10.3390/electronics10080881

APA StyleAli, E. M., Yahaya, N. Z., Saraereh, O. A., Assaf, A. H. A., Alqasem, B. H., Iqbal, S., Ibrahim, O., & Patel, A. V. (2021). Power Conversion Using Analytical Model of Cockcroft–Walton Voltage Multiplier Rectenna. Electronics, 10(8), 881. https://doi.org/10.3390/electronics10080881