Reconfigurable Distributed Power Electronics Technique for Solar PV Systems

Abstract

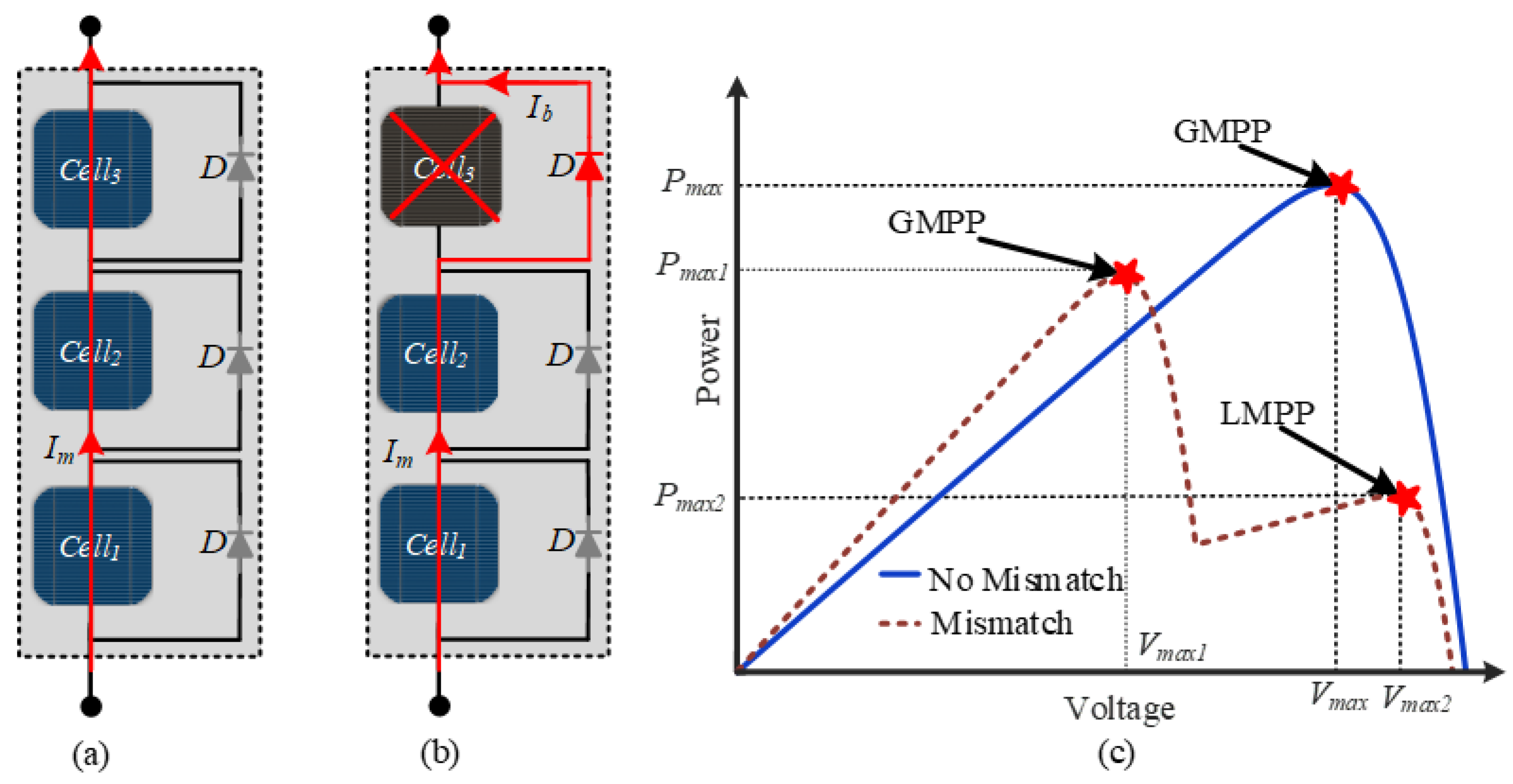

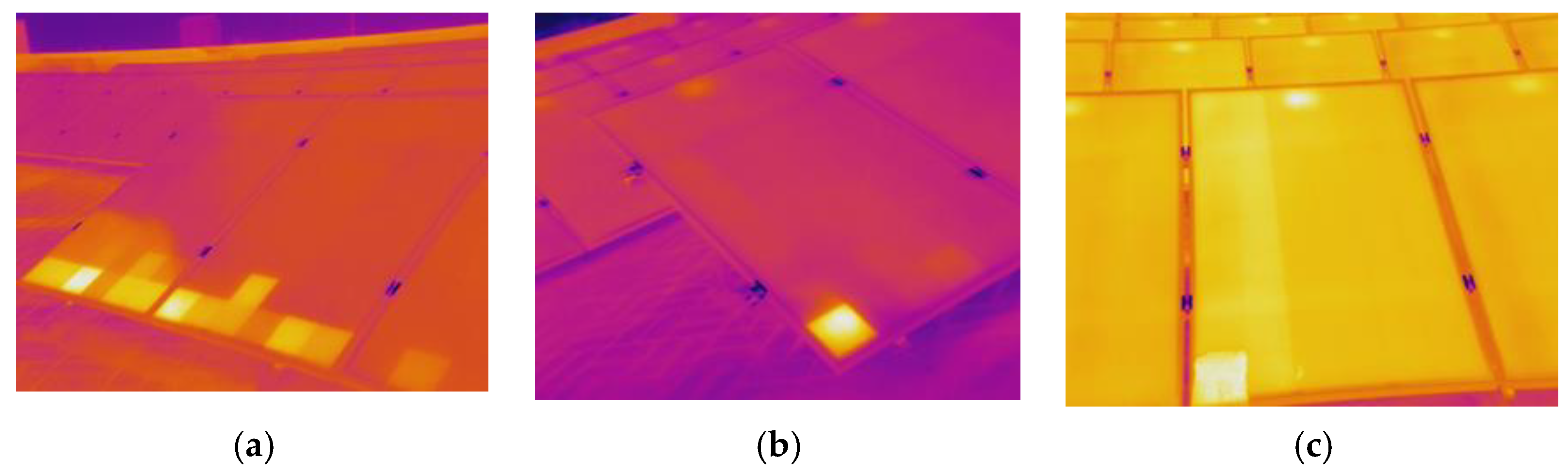

:1. Introduction

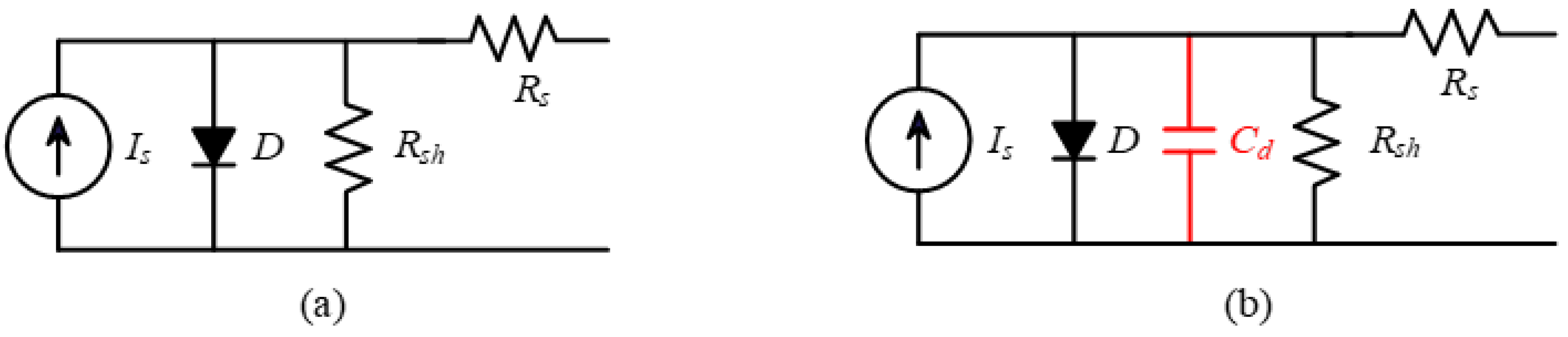

2. PV Cell Diffusion Capacitance

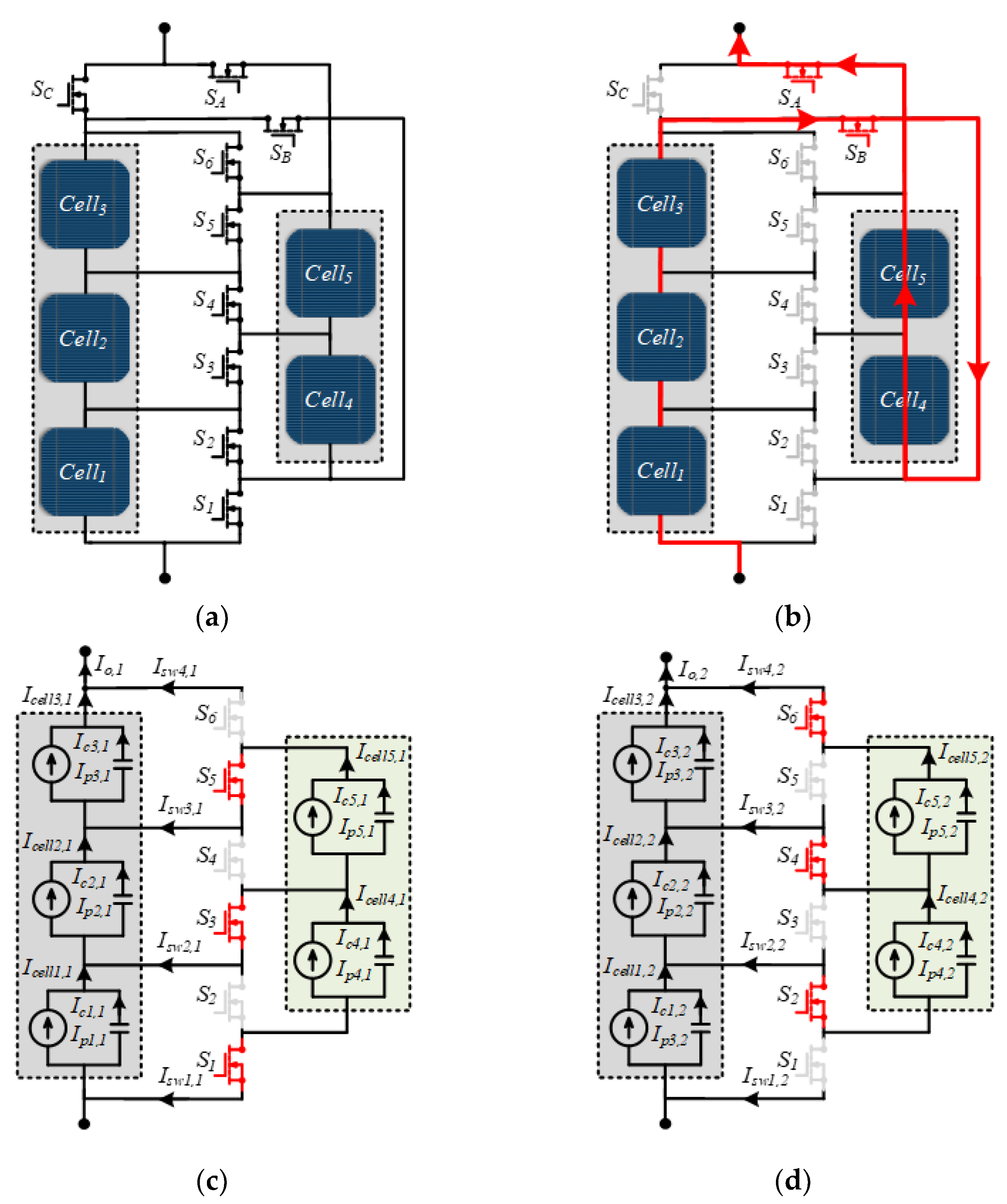

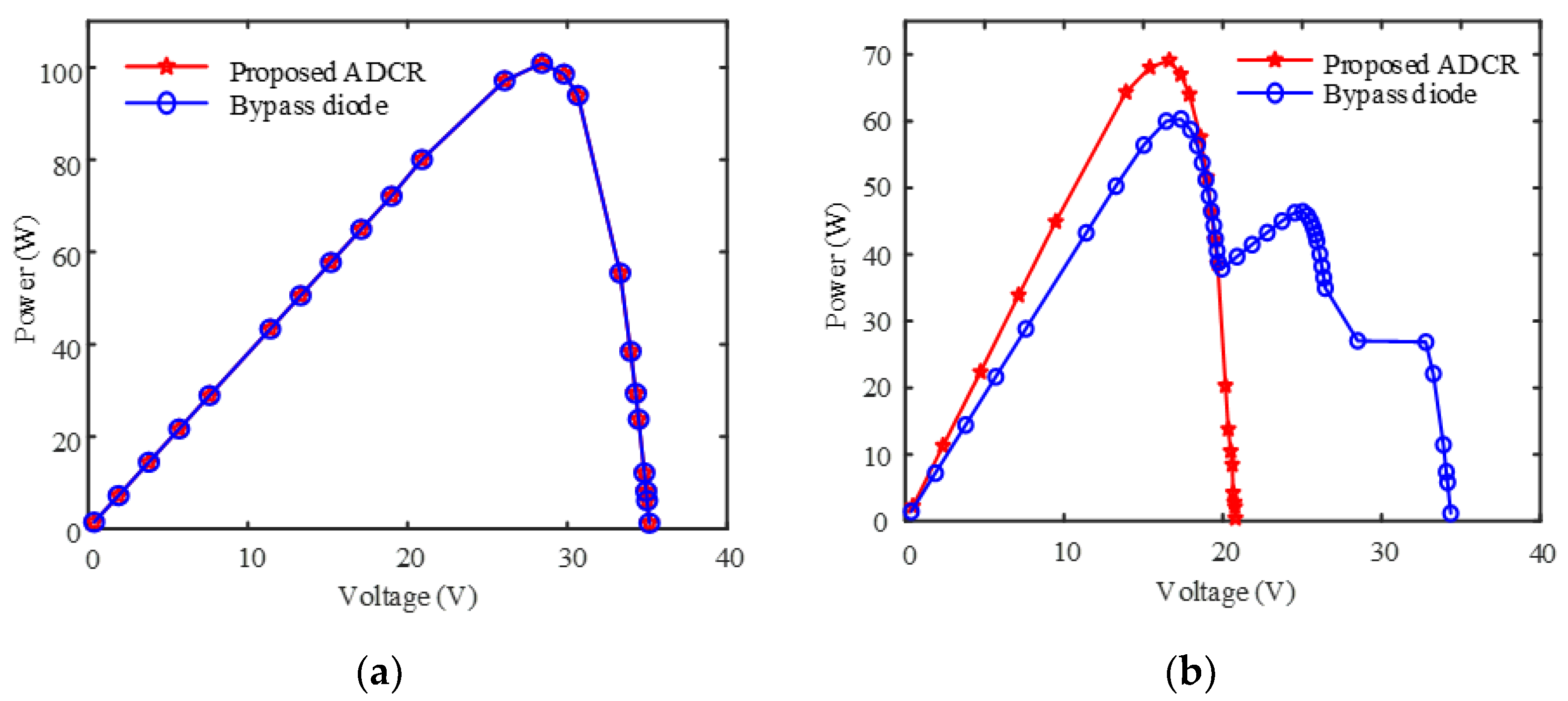

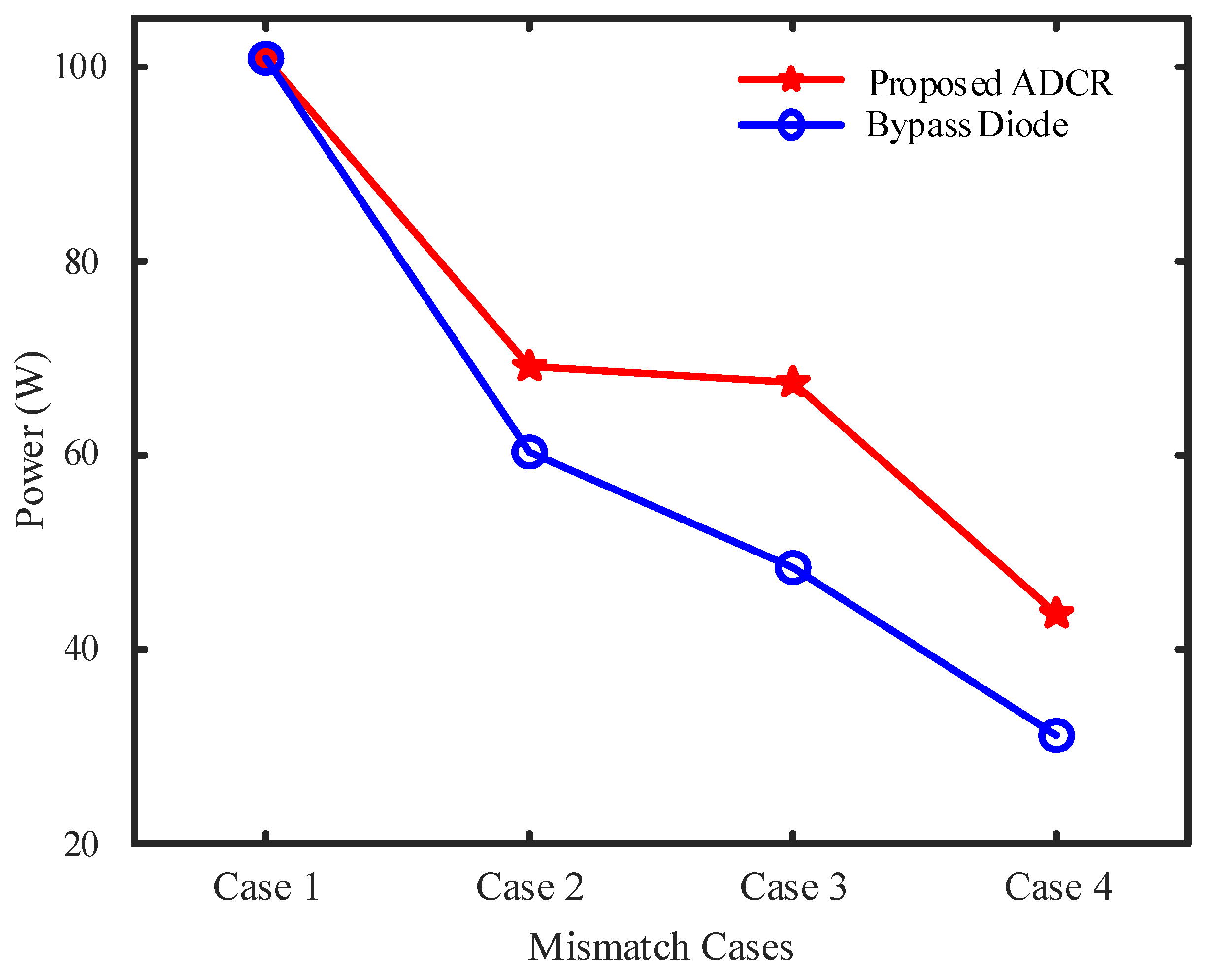

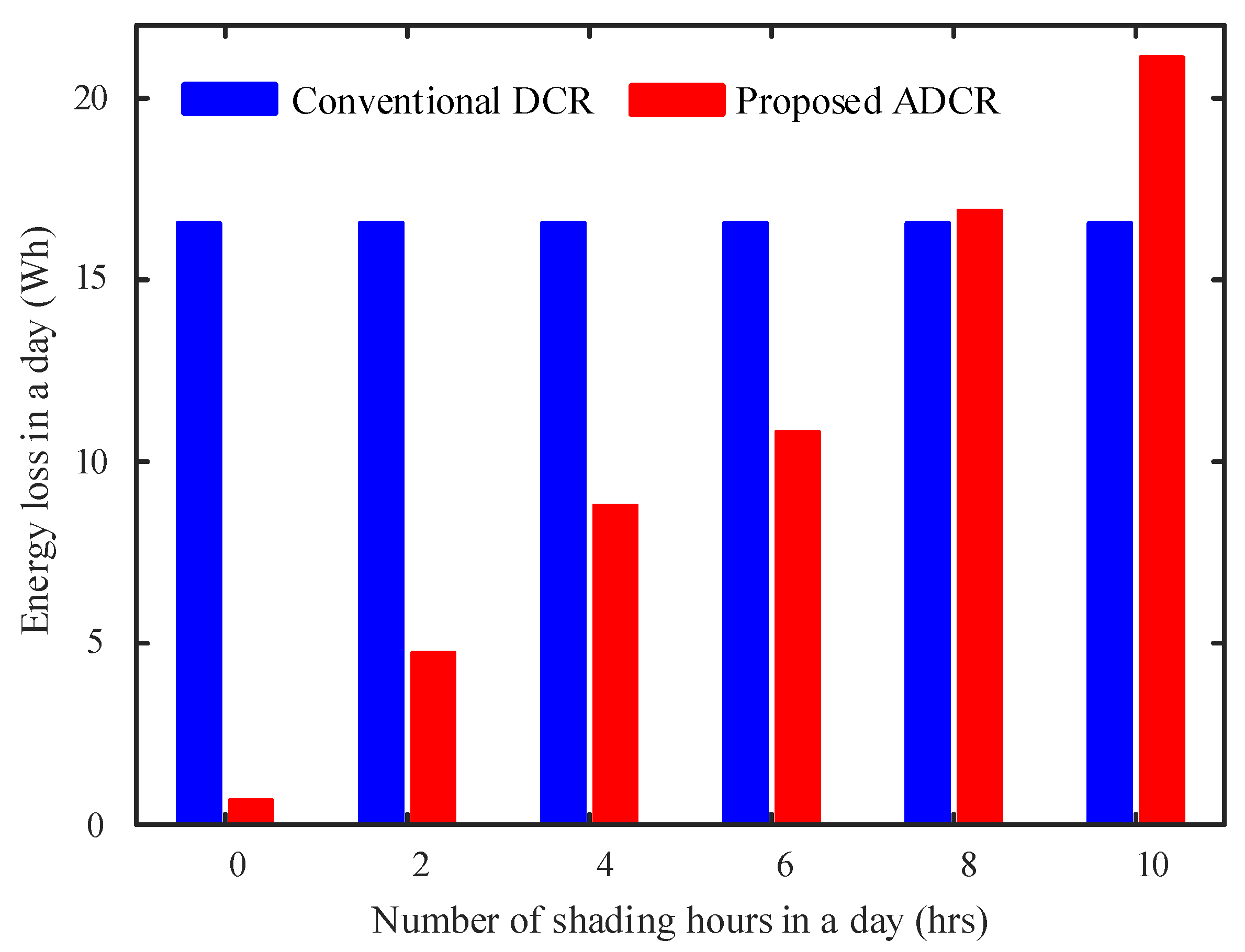

3. Proposed Technique

3.1. Mode of Operations

3.1.1. Mode 1

3.1.2. Mode 2

3.1.3. Mode 3

3.2. Power Loss Analysis

3.3. Proposed Reconfiguration Method

4. Results and Discussion

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- REN21. Renewable Energy Policy Network for the 21st Century Renewables 2017; Global Status Report—REN21; REN21: Paris, France, 2017; pp. 1–302. [Google Scholar]

- Fraunhofer ISE-Institut fur Solare Energiesysteme, 2021. In Recent Facts about Photovoltaics in Germany; Available online: https://www.ise.fraunhofer.de/ (accessed on 9 May 2021).

- Olalla, C.; Hasan, M.N.; Martínez-Salamero, L. Recoverable Energy in Photovoltaic Systems with Submodule Level Dispersion Losses. Sol. Energy 2020, 198, 376–384. [Google Scholar] [CrossRef]

- Silvestre, S.; Boronat, A.; Chouder, A. Study of Bypass Diodes Configuration on PV Modules. Appl. Energy 2009, 86, 1632–1640. [Google Scholar] [CrossRef]

- Niazi, K.A.K.; Yang, Y.; Khan, H.A.; Sera, D. Performance Benchmark of Bypassing Techniques for Photovoltaic Modules. In Proceedings of the 2019 IEEE Applied Power Electronics Conference and Exposition (APEC), Anaheim, CA, USA, 17–21 March 2019; pp. 3164–3168. [Google Scholar]

- Belhachat, F.; Larbes, C. A Review of Global Maximum Power Point Tracking Techniques of Photovoltaic System under Partial Shading Conditions. Renew. Sustain. Energy Rev. 2018, 92, 513–553. [Google Scholar] [CrossRef]

- Alonso-García, M.C.; Ruiz, J.M.; Chenlo, F. Experimental Study of Mismatch and Shading Effects in the I–V Characteristic of a Photovoltaic Module. Sol. Energy Mater. Sol. Cells 2005, 90, 329–340. [Google Scholar] [CrossRef]

- Kim, K.A.; Krein, P.T. Reexamination of Photovoltaic Hot Spotting to Show Inadequacy of the Bypass Diode. IEEE J. Photovolt. 2015, 5, 1435–1441. [Google Scholar] [CrossRef]

- Ahsan, S.; Niazi, K.A.K.; Khan, H.A.; Yang, Y. Hotspots and Performance Evaluation of Crystalline-Silicon and Thin-Film Photovoltaic Modules. Microelectron. Reliab. 2018, 88, 1014–1018. [Google Scholar] [CrossRef]

- Olalla, C.; Maksimovic, D.; Deline, C.; Martinez-Salamero, L. Impact of Distributed Power Electronics on the Lifetime and Reliability of PV Systems. Prog. Photovolt. Res. Appl. 2017, 25, 821–835. [Google Scholar] [CrossRef]

- Niazi, K.A.K.; Yang, Y.; Nasir, M.; Sera, D. Evaluation of Interconnection Configuration Schemes for PV Modules with Switched-Inductor Converters under Partial Shading Conditions. Energies 2019, 12, 2802. [Google Scholar] [CrossRef] [Green Version]

- Velasco-Quesada, G.; Guinjoan-Gispert, F.; Pique-Lopez, R.; Roman-Lumbreras, M.; Conesa-Roca, A. Electrical PV Array Reconfiguration Strategy for Energy Extraction Improvement in Grid-Connected PV Systems. IEEE Trans. Ind. Electron. 2009, 56, 4319–4331. [Google Scholar] [CrossRef] [Green Version]

- Sai Krishna, G.; Moger, T. Reconfiguration Strategies for Reducing Partial Shading Effects in Photovoltaic Arrays: State of the Art. Sol. Energy 2019, 182, 429–452. [Google Scholar] [CrossRef]

- Kaushika, N.D.; Gautam, N.K. Energy Yield Simulations of Interconnected Solar PV Arrays. IEEE Trans. Energy Convers. 2003, 18, 127–134. [Google Scholar] [CrossRef]

- Olalla, C.; Hasan, M.N.; Deline, C.; Maksimović, D. Mitigation of Hot-Spots in Photovoltaic Systems Using Distributed Power Electronics. Energies 2018, 11, 726. [Google Scholar] [CrossRef] [Green Version]

- Chu, G.; Wen, H.; Hu, Y.; Jiang, L.; Yang, Y.; Wang, Y. Low-Complexity Power-Balancing-Point Based Optimization for Photovoltaic Differential Power Processing. IEEE Trans. Power Electron. 2020, 10306–10322. [Google Scholar] [CrossRef]

- Kasper, M.; Bortis, D.; Kolar, J.W. Classification and Comparative Evaluation of PV Panel-Integrated DC–DC Converter Concepts. IEEE Trans. Power Electron. 2013, 29, 2511–2526. [Google Scholar] [CrossRef]

- Chang, A.H.; Avestruz, A.; Leeb, S.B. Capacitor-Less Photovoltaic Cell-Level Power Balancing Using Diffusion Charge Redistribution. IEEE Trans. Power Electron. 2014, 30, 537–546. [Google Scholar] [CrossRef]

- Jeon, Y.; Lee, H.; Kim, K.A.; Park, J. Least Power Point Tracking Method for Photovoltaic Differential Power Processing Systems. IEEE Trans. Power Electron. 2016, 32, 1941–1951. [Google Scholar] [CrossRef]

- Stauth, J.T.; Seeman, M.D.; Kesarwani, K. Resonant Switched-Capacitor Converters for Sub-Module Distributed Photovoltaic Power Management. IEEE Trans. Power Electron. 2012, 28, 1189–1198. [Google Scholar] [CrossRef]

- Kesarwani, K.; Stauth, J.T. A Comparative Theoretical Analysis of Distributed Ladder Converters for Sub-Module PV Energy Optimization. In Proceedings of the 2012 IEEE 13th Workshop on Control and Modeling for Power Electronics (COMPEL), Kyoto, Japan, 10–13 June 2012; pp. 1–6. [Google Scholar]

- Uno, M.; Kukita, A. PWM Switched Capacitor Converter with Switched-Capacitor-Inductor Cell for Adjustable High Step-Down Voltage Conversion. IEEE Trans. Power Electron. 2018, 34, 425–437. [Google Scholar] [CrossRef]

- Gokdag, M.; Akbaba, M.; Gulbudak, O. Switched-Capacitor Converter for PV Modules under Partial Shading and Mismatch Conditions. Sol. Energy 2018, 170, 723–731. [Google Scholar] [CrossRef]

- Bergveld, H.J.; Büthker, D.; Castello, C.; Doorn, T.; de Jong, A.; van Otten, R.; de Waal, K. Module-Level DC/DC Conversion for Photovoltaic Systems: The Delta-Conversion Concept. IEEE Trans. Power Electron. 2012, 28, 2005–2013. [Google Scholar] [CrossRef]

- Lavado Villa, L.F.; Ho, T.-P.; Crebier, J.-C.; Raison, B. A Power Electronics Equalizer Application for Partially Shaded Photovoltaic Modules. IEEE Trans. Ind. Electron. 2012, 60, 1179–1190. [Google Scholar] [CrossRef]

- Khan, O.; Xiao, W. Review and Qualitative Analysis of Submodule-Level Distributed Power Electronic Solutions in PV Power Systems. Renew. Sustain. Energy Rev. 2017, 76, 516–528. [Google Scholar] [CrossRef]

- Niazi, K.A.K.; Yang, Y.; Sera, D. Review of Mismatch Mitigation Techniques for PV Modules. IET Renew. Power Gener. 2019, 13, 2035–2050. [Google Scholar] [CrossRef]

- Ramli, M.Z.; Salam, Z. A Simple Energy Recovery Scheme to Harvest the Energy from Shaded Photovoltaic Modules during Partial Shading. IEEE Trans. Power Electron. 2014, 29, 6458–6471. [Google Scholar] [CrossRef]

- Shenoy, P.S.; Krein, P.T. Differential Power Processing for DC Systems. IEEE Trans. Power Electron. 2012, 28, 1795–1806. [Google Scholar] [CrossRef]

- Shimizu, T.; Hirakata, M.; Kamezawa, T.; Watanabe, H. Generation Control Circuit for Photovoltaic Modules. IEEE Trans. Power Electron. 2001, 16, 293–300. [Google Scholar] [CrossRef] [Green Version]

- Niazi, K.A.K.; Yang, Y.; Liu, W.; Sera, D. Sub-Module Level Differential Power Processing for Parallel-Connected Architecture in Photovoltaic Systems. In Proceedings of the 2019 21st European Conference on Power Electronics and Applications (EPE ’19 ECCE Europe), Marseille, France, 9 September–13 October 2019; pp. 1–9. [Google Scholar]

- Khan Niazi, K.A.; Yang, Y.; He, J.; Khan, A.Z.; Sera, D. Switched-Capacitor-Inductor-Based Differential Power Converter for Solar PV Modules. In Proceedings of the 2019 IEEE Energy Conversion Congress and Exposition (ECCE), Baltimore, MD, USA, 29 September–3 October 2019; pp. 4613–4618. [Google Scholar]

- Uno, M.; Kukita, A. Single-Switch Voltage Equalizer Using Multistacked Buck–Boost Converters for Partially Shaded Photovoltaic Modules. IEEE Trans. Power Electron. 2014, 30, 3091–3105. [Google Scholar] [CrossRef]

- Uno, M.; Kukita, A. Current Sensorless Equalization Strategy for a Single-Switch Voltage Equalizer Using Multistacked Buck–Boost Converters for Photovoltaic Modules under Partial Shading. IEEE Trans. Ind. Appl. 2016, 53, 420–429. [Google Scholar] [CrossRef]

- Uno, M.; Kukita, A. Single-Switch Single-Magnetic PWM Converter Integrating Voltage Equalizer for Partially Shaded Photovoltaic Modules in Standalone Applications. IEEE Trans. Power Electron. 2017, 33, 1259–1270. [Google Scholar] [CrossRef]

- Uno, M.; Kukita, A. PWM Converter Integrating Switched Capacitor Converter and Series-Resonant Voltage Multiplier as Equalizers for Photovoltaic Modules and Series-Connected Energy Storage Cells for Exploration Rovers. IEEE Trans. Power Electron. 2016, 32, 8500–8513. [Google Scholar] [CrossRef]

- Chu, G.; Wen, H.; Jiang, L.; Hu, Y.; Li, X. Bidirectional Flyback Based Isolated-Port Submodule Differential Power Processing Optimizer for Photovoltaic Applications. Sol. Energy 2017, 158, 929–940. [Google Scholar] [CrossRef] [Green Version]

- Peter, P.K.; Agarwal, V. Current Equalization in Photovoltaic Strings with Module Integrated Ground-Isolated Switched Capacitor DC–DC Converters. IEEE J. Photovolt. 2014, 4, 669–678. [Google Scholar] [CrossRef]

- Jeevandoss, C.R.; Kumaravel, M.; Kumar, V.J. A Novel Measurement Method to Determine the $C$–$V$ Characteristic of a Solar Photovoltaic Cell. IEEE Trans. Instrum. Meas. 2010, 60, 1761–1767. [Google Scholar] [CrossRef]

- Kim, K.A.; Xu, C.; Jin, L.; Krein, P.T. A Dynamic Photovoltaic Model Incorporating Capacitive and Reverse-Bias Characteristics. IEEE J. Photovolt. 2013, 3, 1334–1341. [Google Scholar] [CrossRef]

- Friesen, G.; Ossenbrink, H.A. Capacitance Effects in High-Efficiency Cells. Sol. Energy Mater. Sol. Cells 1997, 48, 77–83. [Google Scholar] [CrossRef]

- Kumar, R.A.; Suresh, M.S.; Nagaraju, J. Silicon (BSFR) Solar Cell AC Parameters at Different Temperatures. Sol. Energy Mater. Sol. Cells 2005, 85, 397–406. [Google Scholar] [CrossRef]

- Zaraket, J.; Aillerie, M.; Salame, C. Capacitance Evolution of Photovoltaic Solar Modules under the Influence of Electrical Stress. Energy Procedia 2015, 74, 1466–1475. [Google Scholar] [CrossRef]

- Satpathy, P.R.; Sharma, R. Diffusion Charge Compensation Strategy for Power Balancing in Capacitor-Less Photovoltaic Modules during Partial Shading. Appl. Energy 2019, 255, 113826. [Google Scholar] [CrossRef]

- Jayakrishnan, R.; Gandhi, S.; Suratkar, P. Correlation between Solar Cell Efficiency and Minority Carrier Lifetime for Batch Processed Multicrystalline Si Wafers. Mater. Sci. Semicond. Process. 2011, 14, 223–228. [Google Scholar] [CrossRef]

- Sharma, S.K.; Pavithra, D.; Sivakumar, G.; Srinivasamurthy, N.; Agrawal, B.L. Determination of Solar Cell Diffusion Capacitance and Its Dependence on Temperature and 1 MeV Electron Fluence Level. Sol. Energy Mater. Sol. Cells 1992, 26, 169–179. [Google Scholar] [CrossRef]

- Anil Kumar, R.; Suresh, M.S.; Nagaraju, J. Measurement and Comparison of AC Parameters of Silicon (BSR and BSFR) and Gallium Arsenide (GaAs/Ge) Solar Cells Used in Space Applications. Sol. Energy Mater. Sol. Cells 2000, 60, 155–166. [Google Scholar] [CrossRef]

- Uno, M.; Saito, Y.; Urabe, S.; Yamamoto, M. PWM Switched Capacitor-Based Cell-Level Power Balancing Converter Utilizing Diffusion Capacitance of Photovoltaic Cells. IEEE Trans. Power Electron. 2019, 34, 10675–10687. [Google Scholar] [CrossRef]

| Maximum power (Pmax) | 20.18 W |

| Voltage at maximum power (Vmp) | 5.68 V |

| Current at maximum power(Imp) | 3.55 A |

| Voltage at open-circuit (Voc) | 7.03 V |

| Current at short-circuit (Isc) | 3.80 A |

| Cases | Vc1 (V) | Vc2 (V) | Vc3 (V) | Vc4 (V) | Vc5 (V) |

|---|---|---|---|---|---|

| Case 1 | 5.68 | 5.68 | 5.68 | 5.68 | 5.68 |

| Case 2 | 6.36 | 6.74 | 6.67 | 6.36 | 5.74 |

| Case 3 | 6.65 | 6.58 | 6.40 | 6.65 | 6.58 |

| Case 4 | 6.12 | 6.27 | 6.21 | 6.27 | 6.21 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Niazi, K.A.K.; Yang, Y.; Kerekes, T.; Sera, D. Reconfigurable Distributed Power Electronics Technique for Solar PV Systems. Electronics 2021, 10, 1121. https://doi.org/10.3390/electronics10091121

Niazi KAK, Yang Y, Kerekes T, Sera D. Reconfigurable Distributed Power Electronics Technique for Solar PV Systems. Electronics. 2021; 10(9):1121. https://doi.org/10.3390/electronics10091121

Chicago/Turabian StyleNiazi, Kamran Ali Khan, Yongheng Yang, Tamas Kerekes, and Dezso Sera. 2021. "Reconfigurable Distributed Power Electronics Technique for Solar PV Systems" Electronics 10, no. 9: 1121. https://doi.org/10.3390/electronics10091121

APA StyleNiazi, K. A. K., Yang, Y., Kerekes, T., & Sera, D. (2021). Reconfigurable Distributed Power Electronics Technique for Solar PV Systems. Electronics, 10(9), 1121. https://doi.org/10.3390/electronics10091121