Fully Differential Current-Mode Configuration for the Realization of First-Order Filters with Ease of Cascadability

Abstract

:1. Introduction

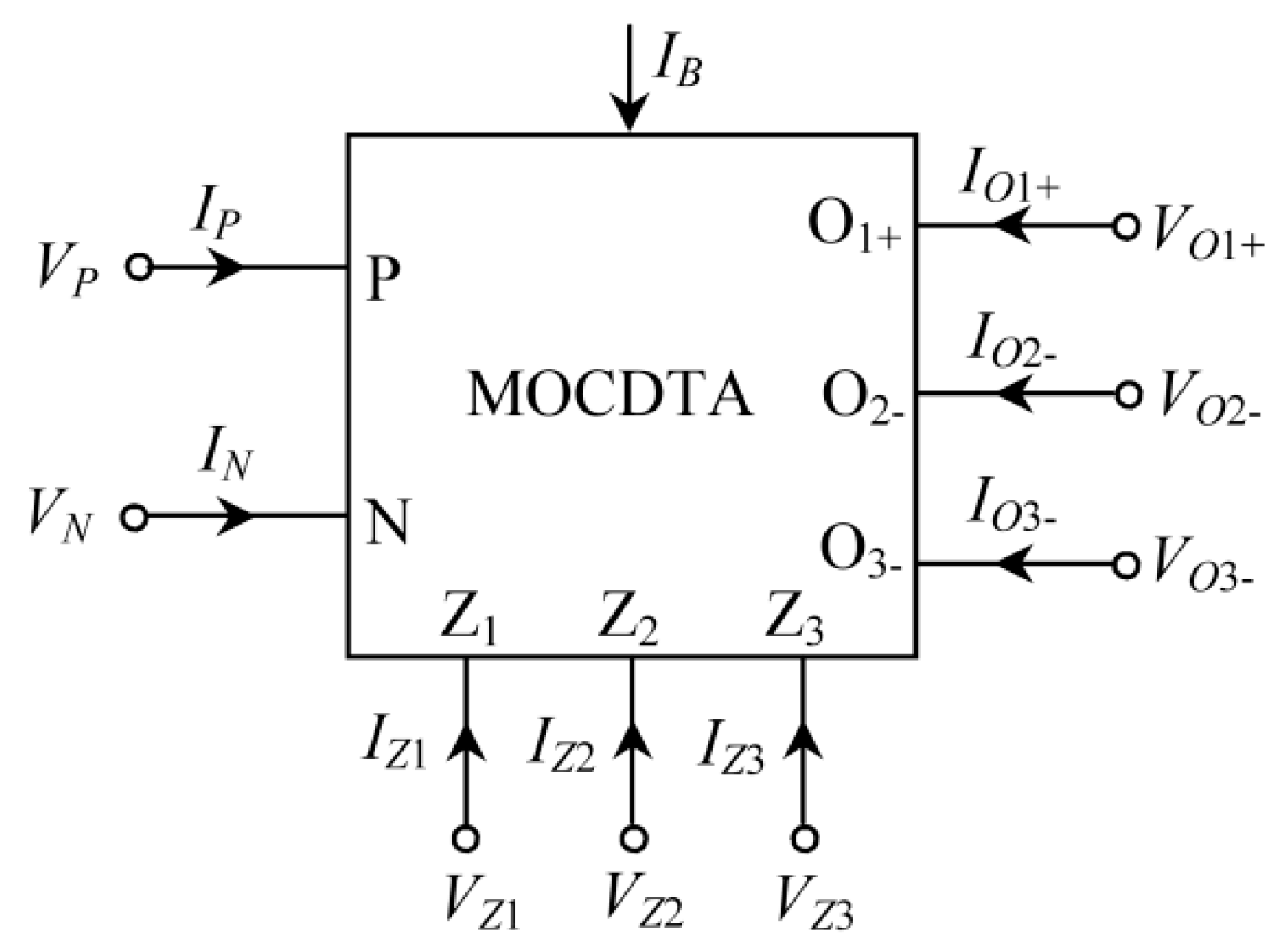

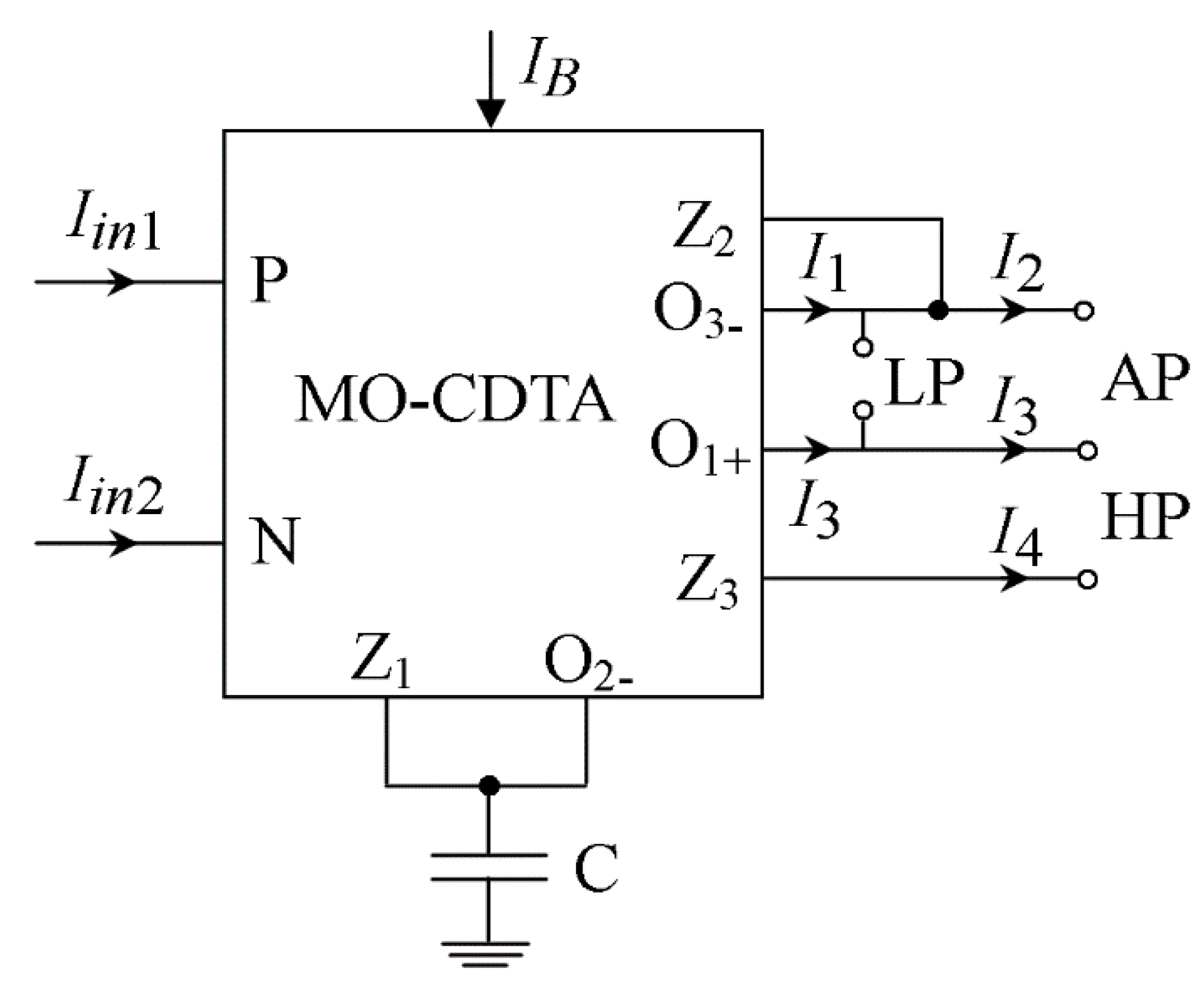

2. First-Order Fully Differential Configuration

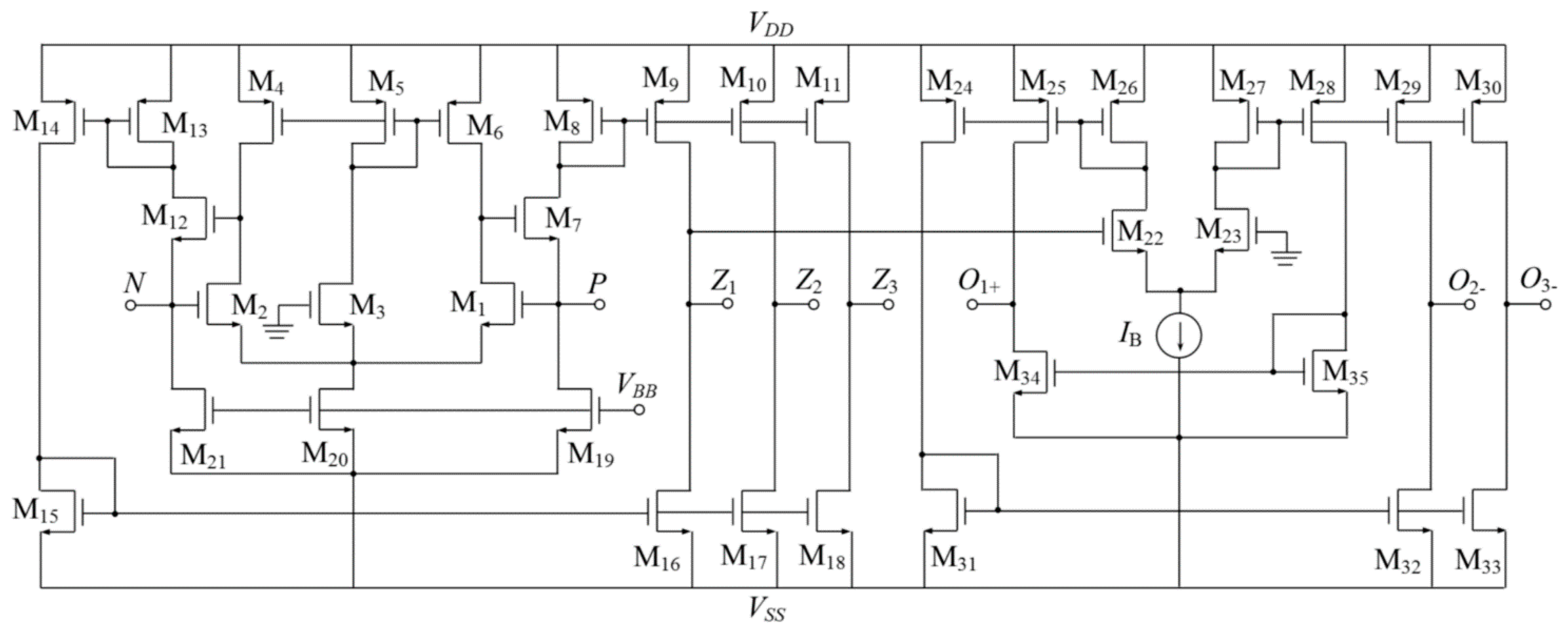

3. Non-Ideal and Parasitic Aspects

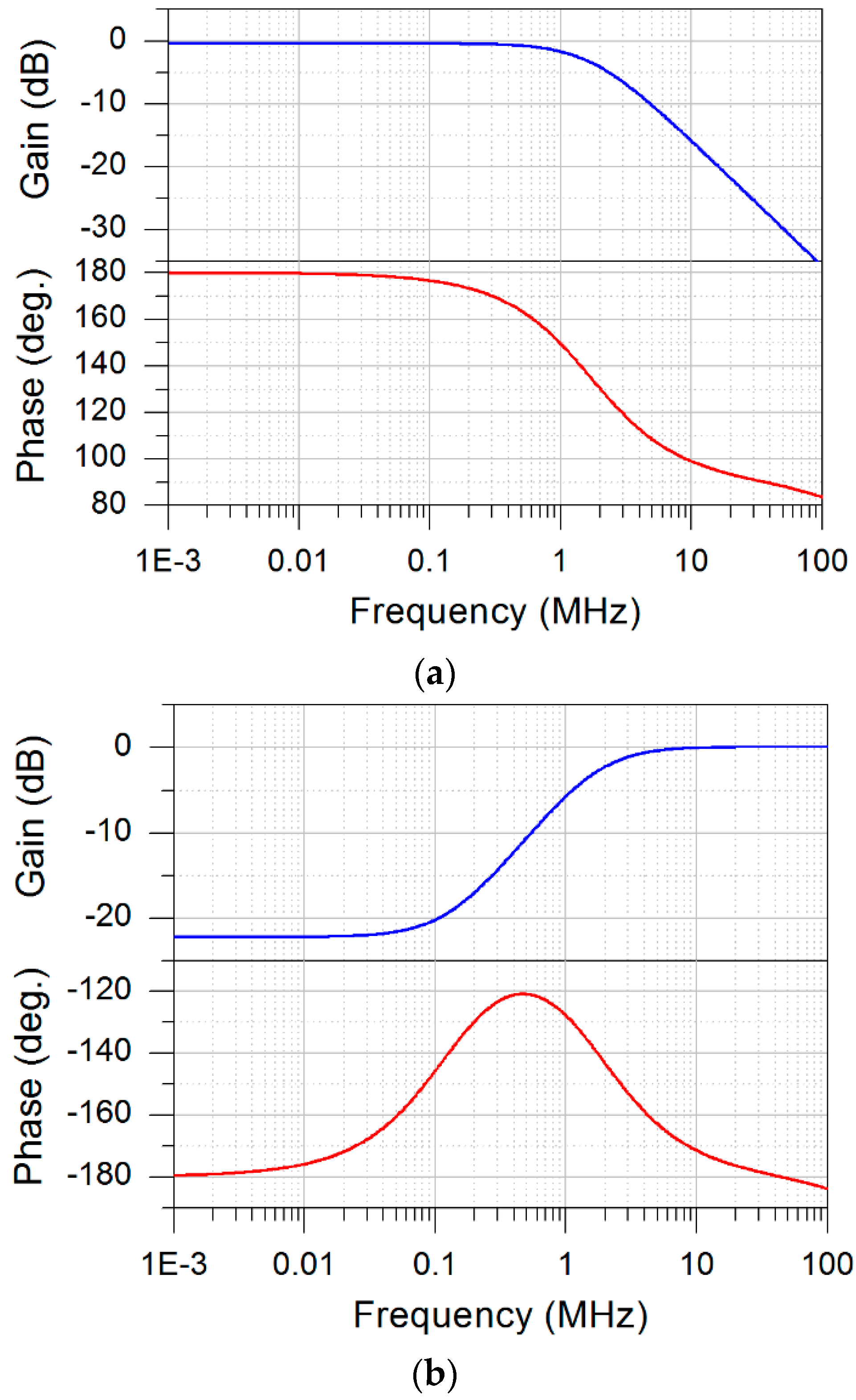

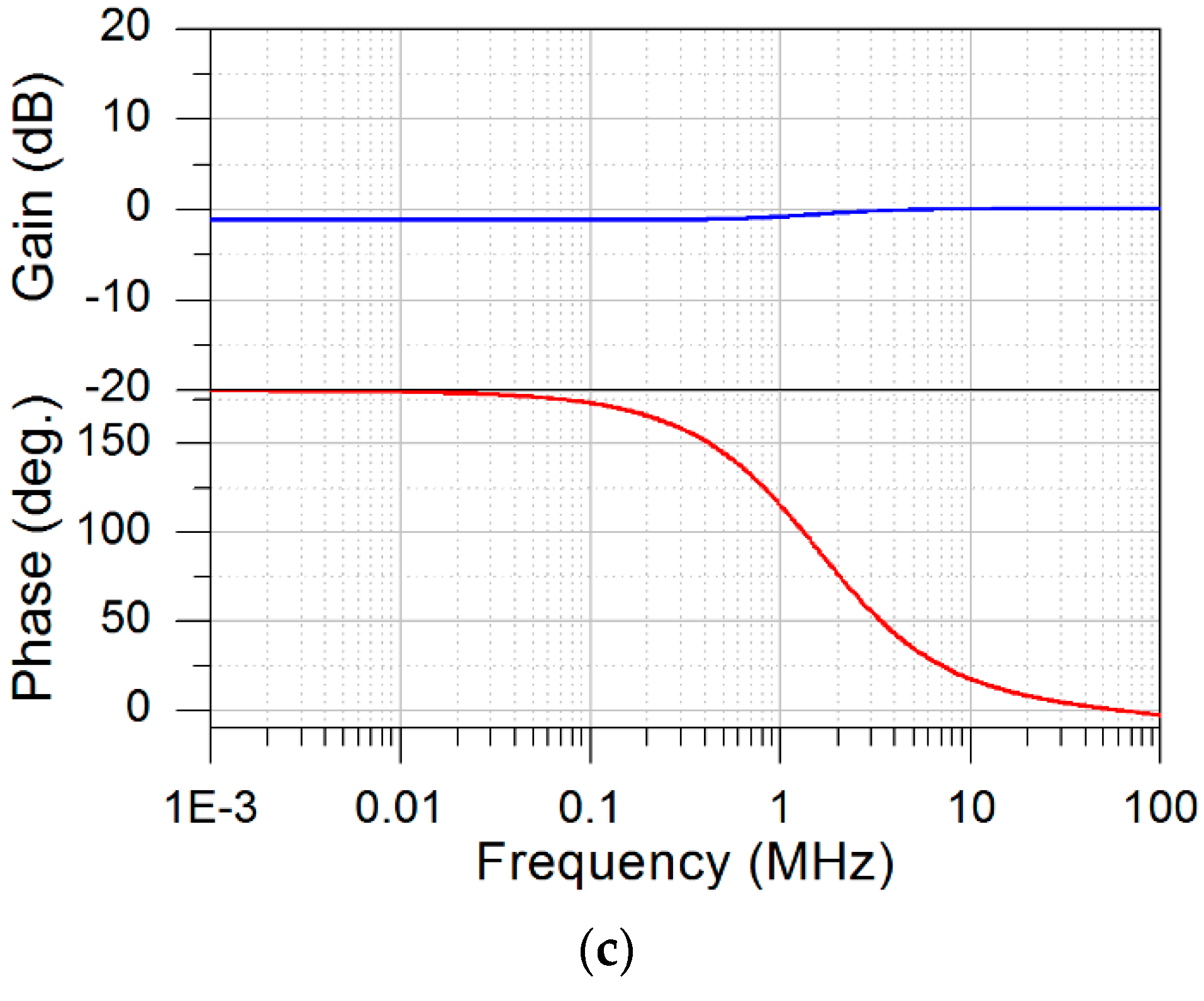

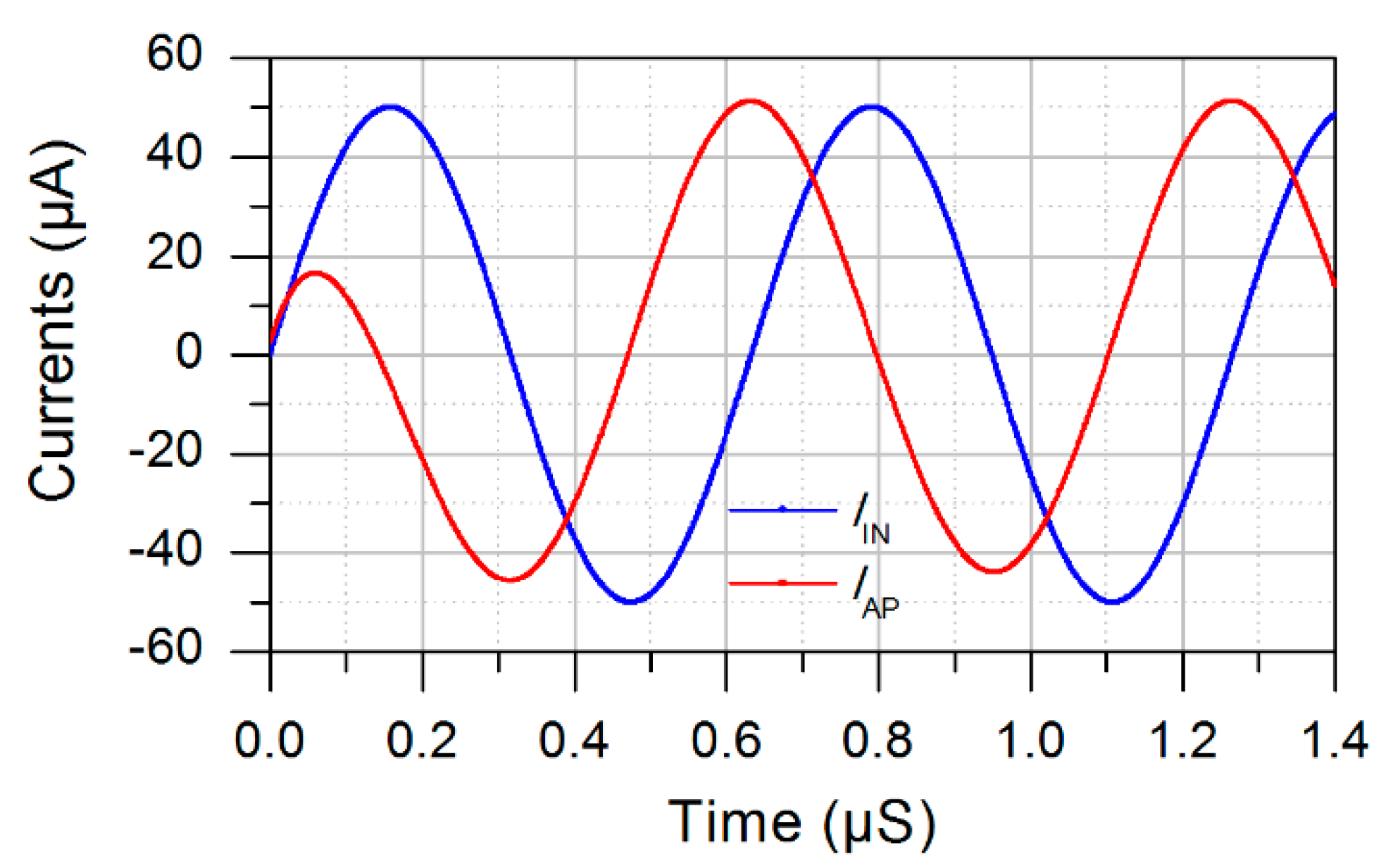

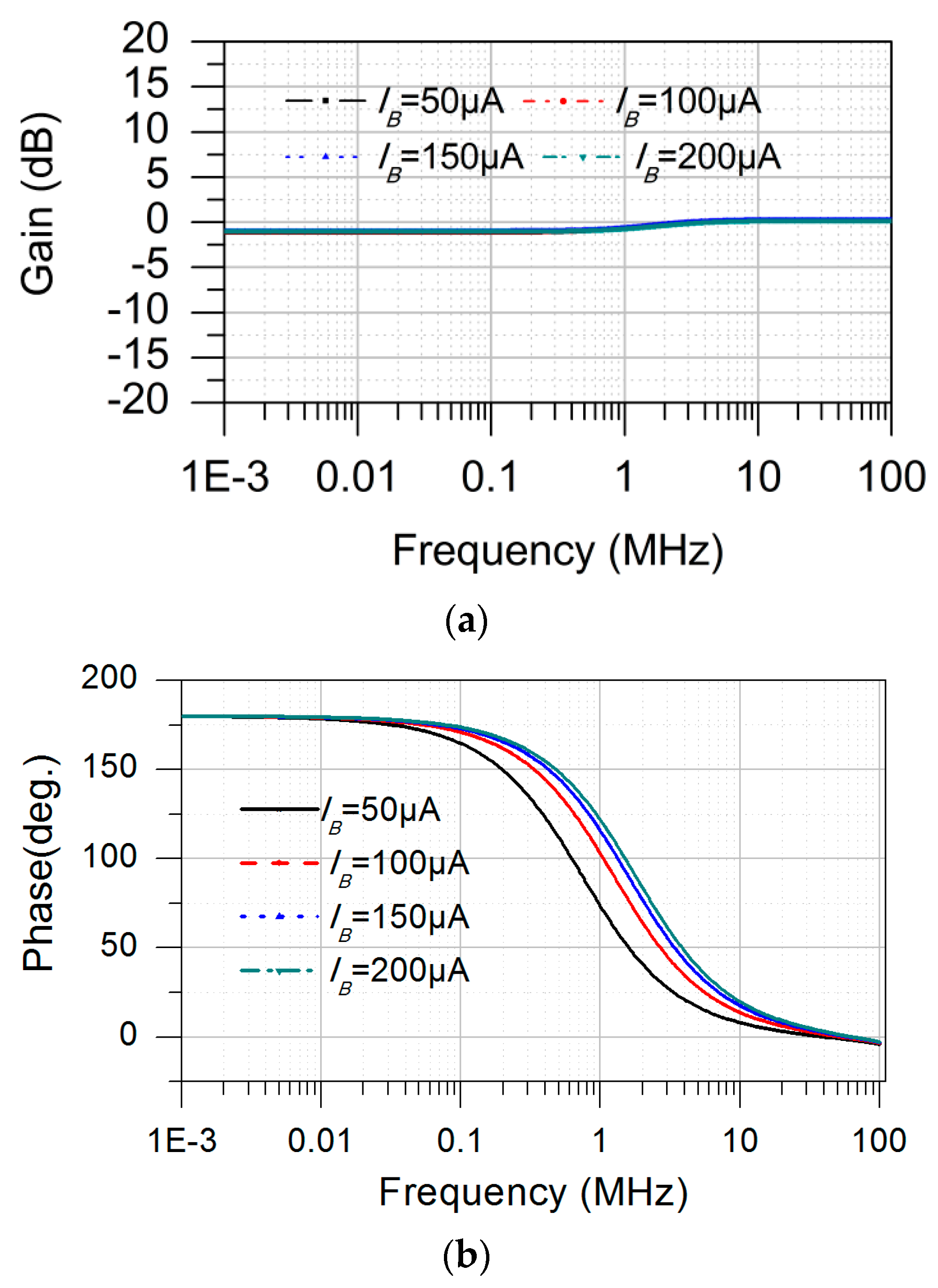

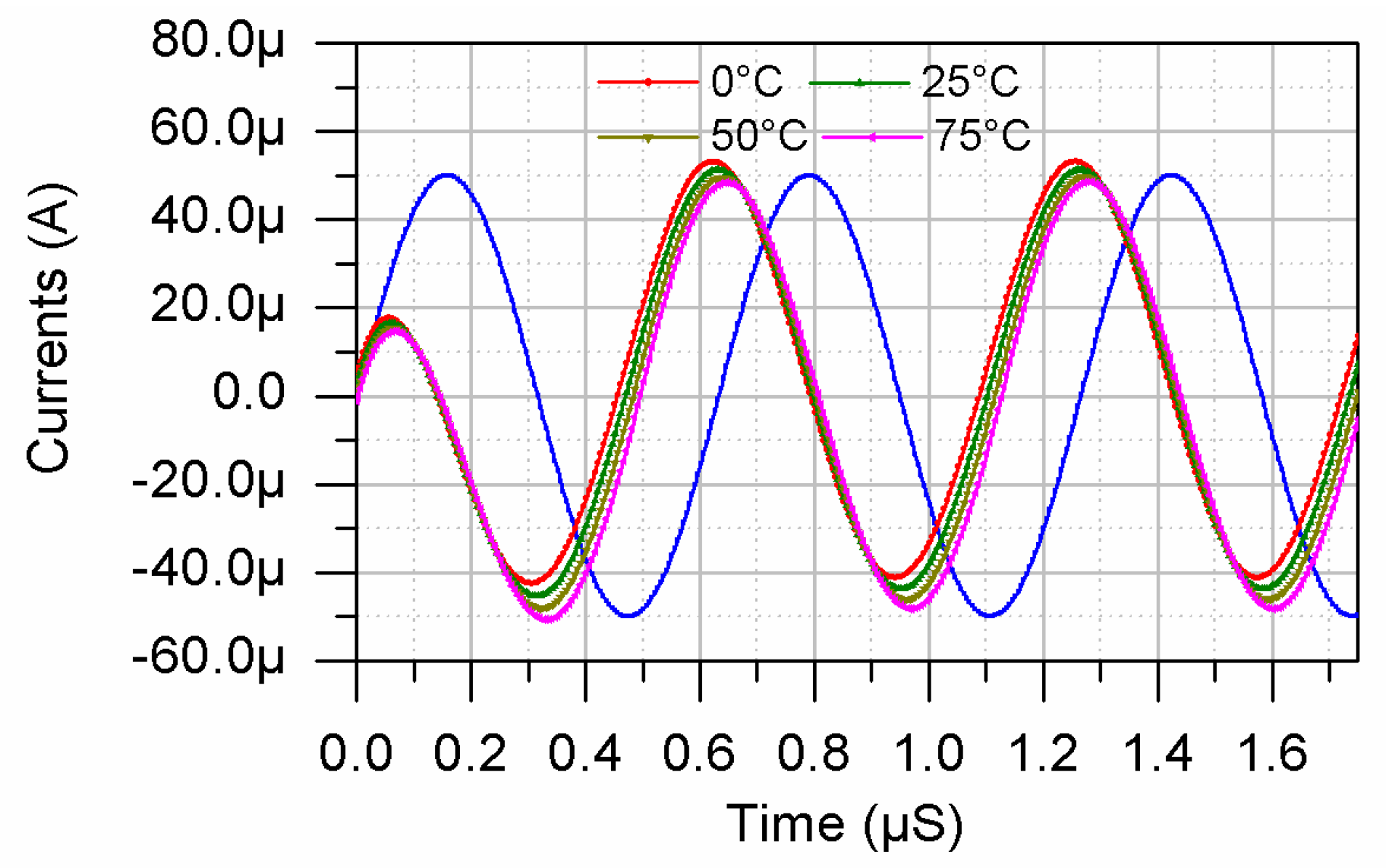

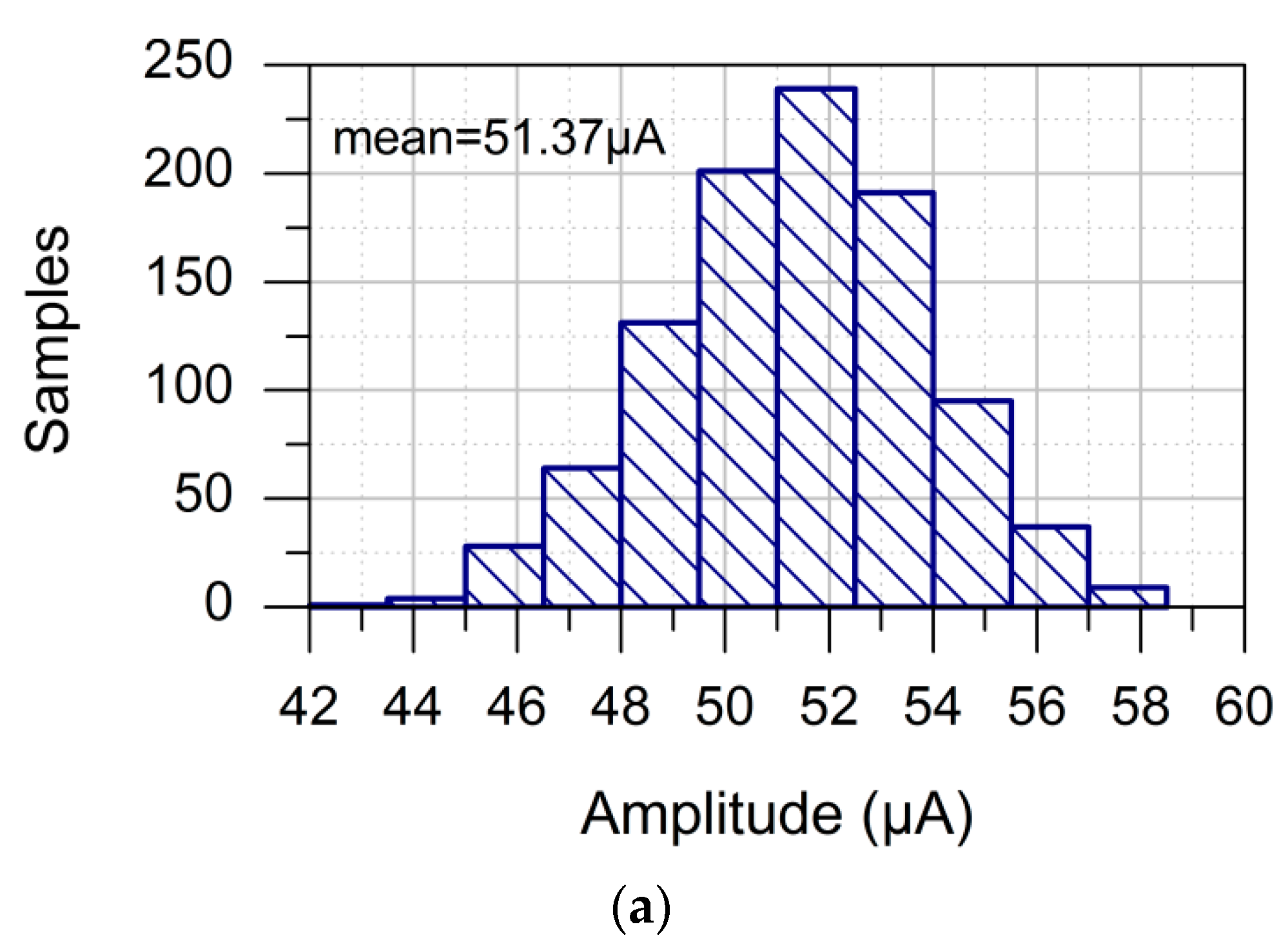

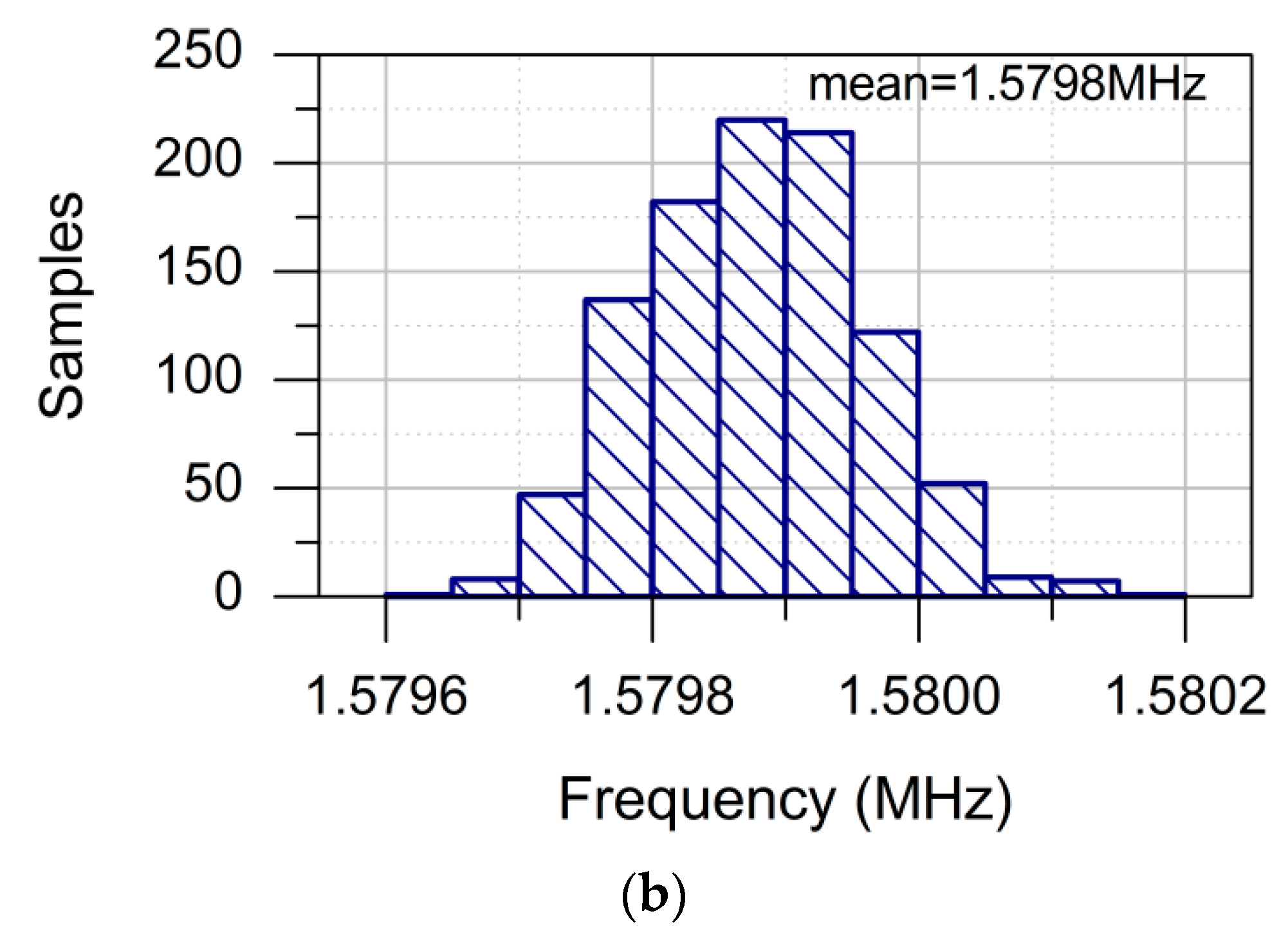

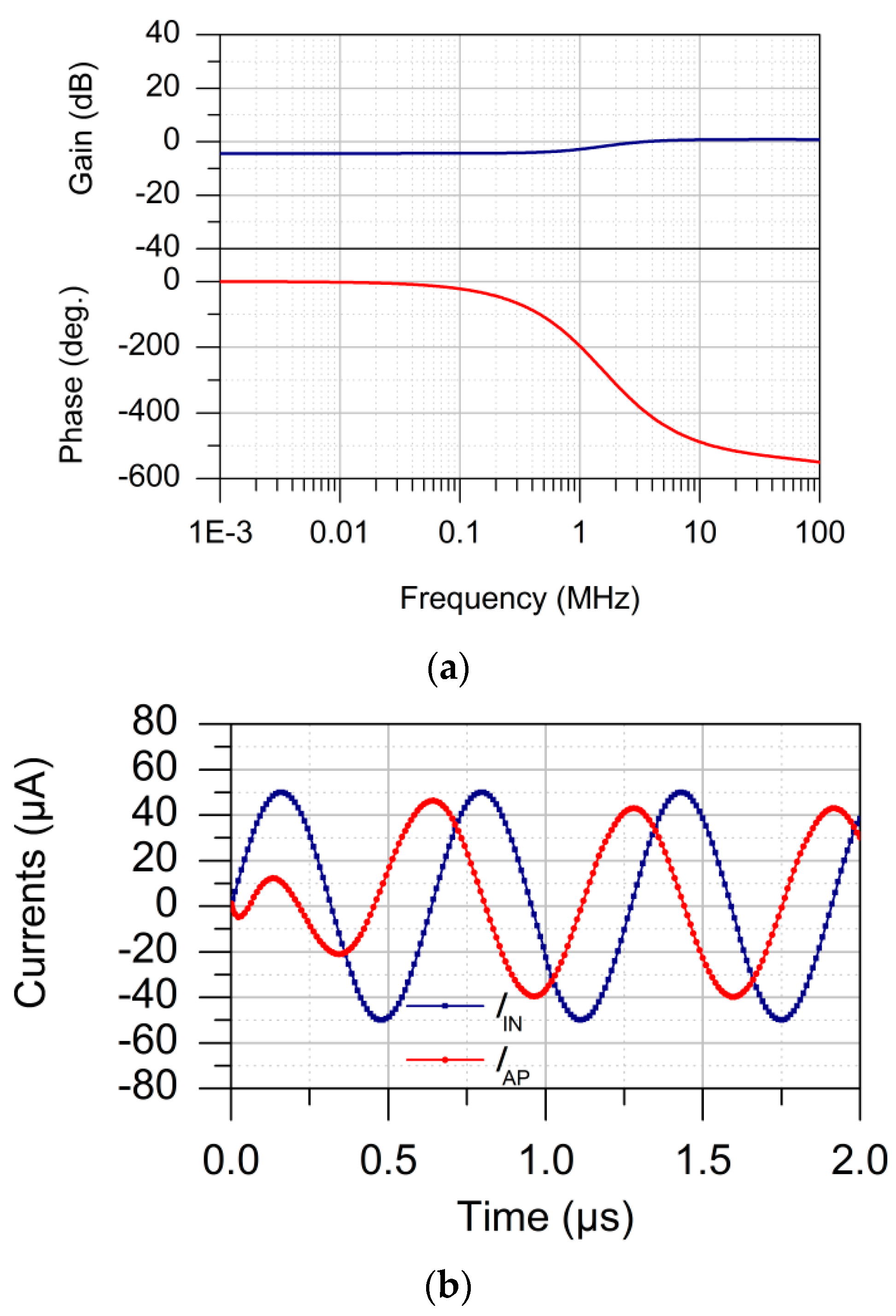

4. Simulation Results

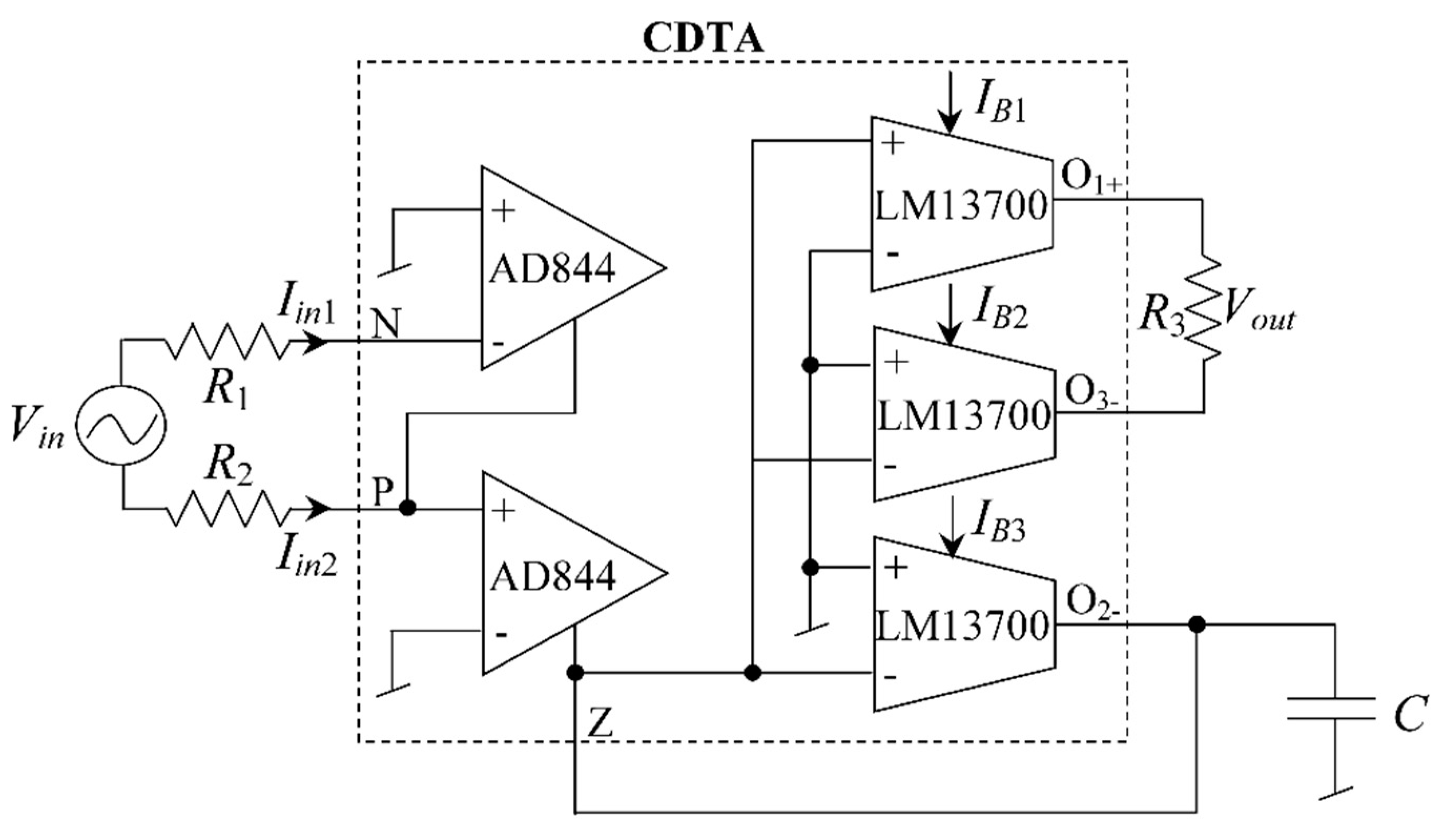

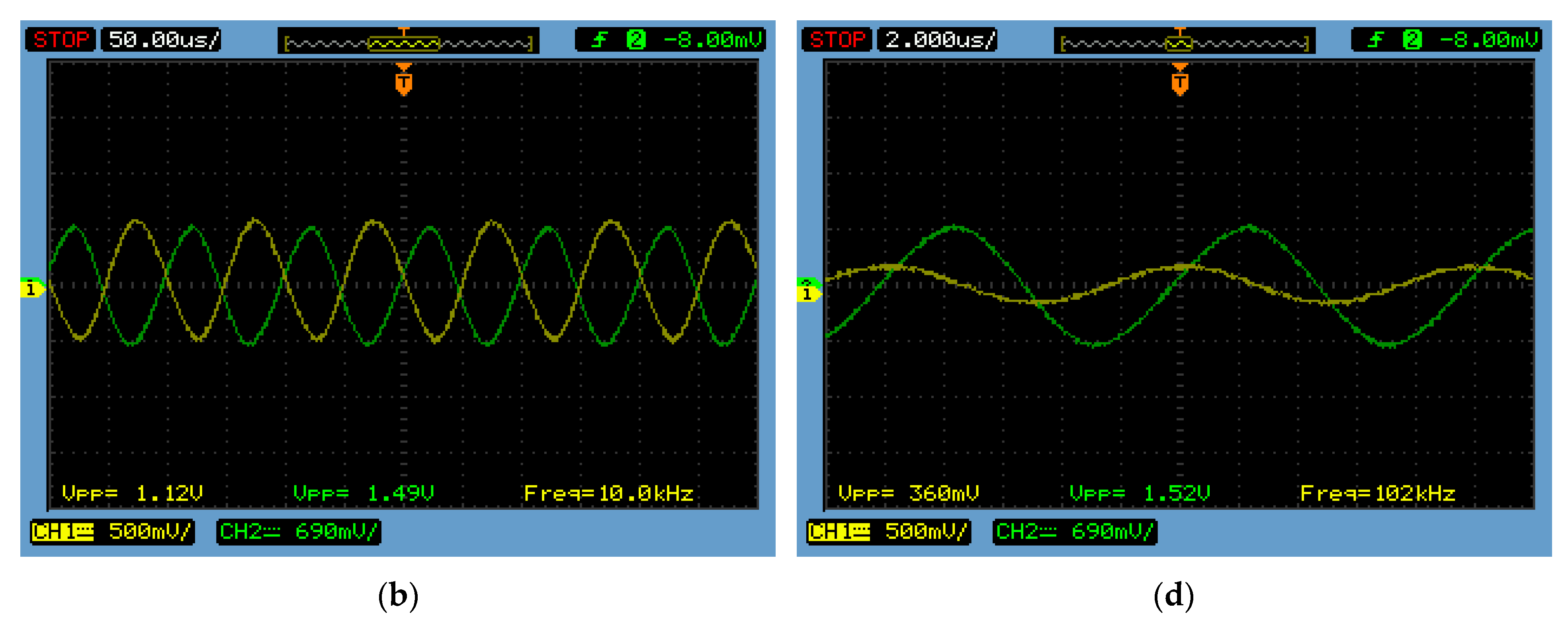

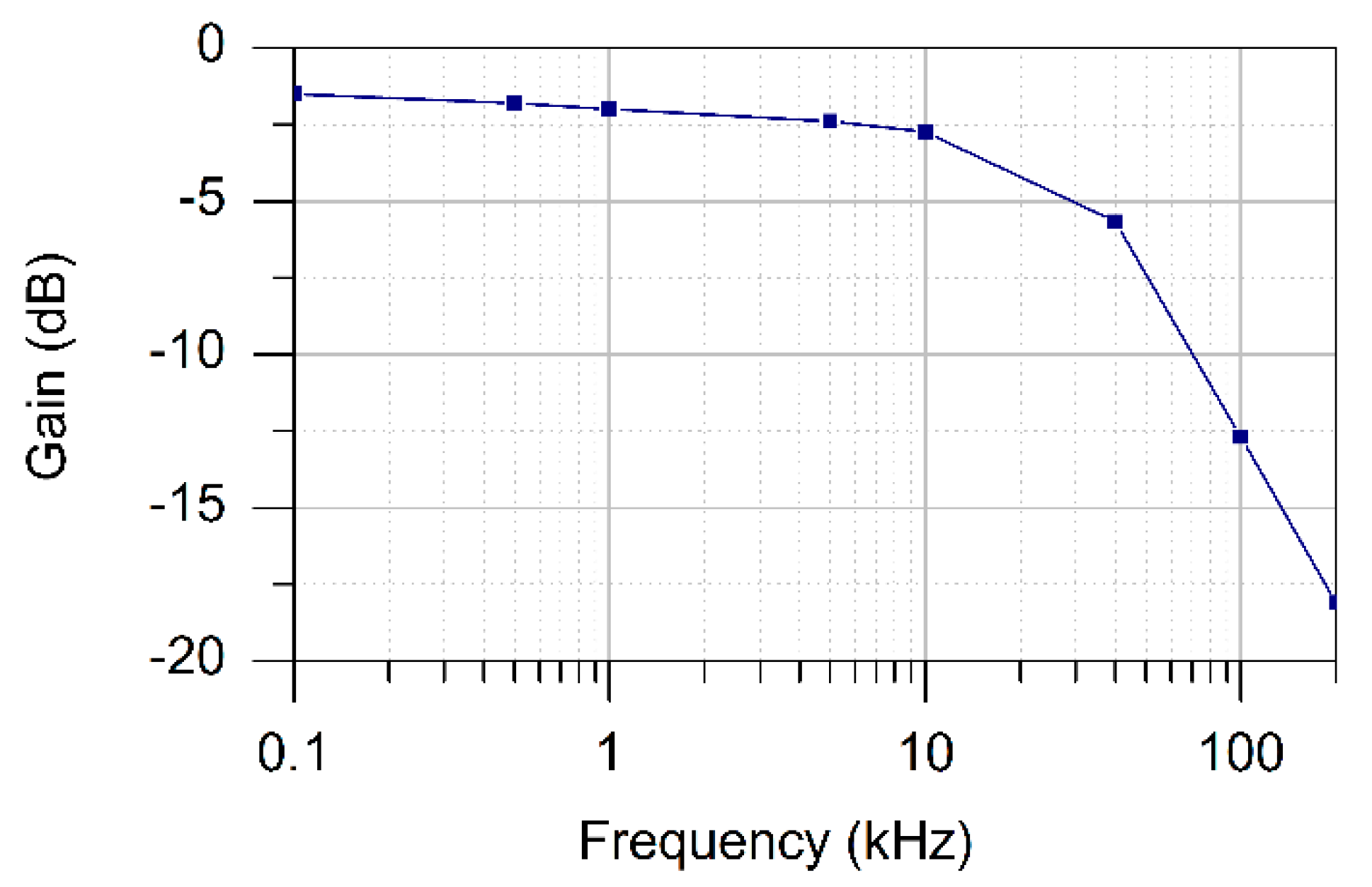

5. Experimental Results

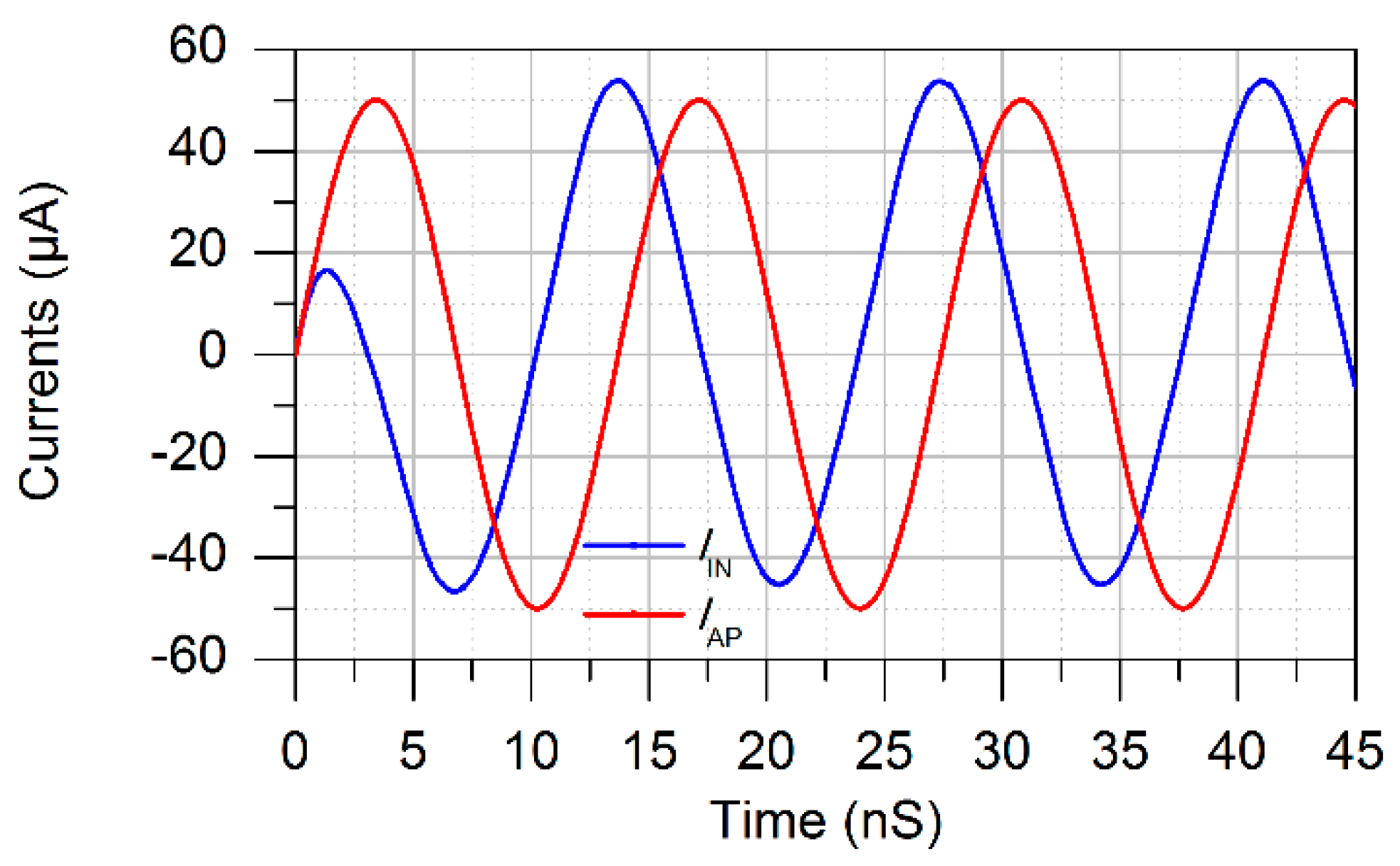

6. Cascading Feasibility

7. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Senani, R.; Bhaskar, D.R.; Kumar, P. Two-CFOA-grounded-capacitor first-order all-pass filter configurations with ideally infinite input impedance. AEU-Int. J. Electron. Commun. 2021, 137, 153742. [Google Scholar] [CrossRef]

- Chaturvedi, B.; Kumar, A. Realization of novel cascadable current-mode all-pass sections. Iran. J. Electr. Electron. Eng. 2018, 14, 162–169. [Google Scholar]

- Yucel, F. A DVCC-Based Current-Mode First-Order Universal Filter. J. Circuits Syst. Comput. 2021, 30, 2150305. [Google Scholar] [CrossRef]

- Maheshwari, S. Tuning approach for first-order filters and new current-mode circuit example. IET Circuits Devices Syst. 2018, 12, 478–485. [Google Scholar] [CrossRef]

- Chaturvedi, B.; Kumar, A. Electronically tunable first-order filters and dual-mode multiphase oscillator. Circuits Syst. Signal Process. 2019, 38, 2–5. [Google Scholar] [CrossRef]

- Tarunkumar, H.; Ranjan, A.; Pheiroijam, N.M. First Order and Second Order Universal Filter Using Four Terminal Floating Nullor. Int. J. Eng. Technol. 2018, 7, 192–198. [Google Scholar]

- Chaturvedi, B.; Kumar, A.; Mohan, J. Low voltage operated current-mode first-order universal filter and sinusoidal oscillator suitable for signal processing applications. AEU-Int. J. Electron. Commun. 2019, 99, 110–118. [Google Scholar] [CrossRef]

- Herencsar, N.; Koton, J.; Hanak, P. Universal voltage conveyor and its novel dual-output fully-cascadable VM APF application. Appl. Sci. 2017, 7, 307. [Google Scholar] [CrossRef]

- Barile, G.; Safari, L.; Pantoli, L.; Stornelli, V.; Ferri, G. Electronically tunable first order AP/LP and LP/HP filter topologies using electronically controllable second generation voltage conveyor (CVCII). Electronics 2021, 10, 822. [Google Scholar] [CrossRef]

- Jaikla, W.; Buakhong, U.; Siripongdee, S.; Khateb, F.; Sotner, R.; Silapan, P.; Suwanjan, P.; Chaichana, A. Single Commercially Available IC-Based Electronically Controllable Voltage-Mode First-Order Multifunction Filter with Complete Standard Functions and Low Output Impedance. Sensors 2021, 21, 7376. [Google Scholar] [CrossRef] [PubMed]

- Dogan, M.; Yuce, E. A first-order universal filter including a grounded capacitor and two CFOAs. Analog Integr. Circuits Signal Process. 2022, 26, 1–2. [Google Scholar] [CrossRef]

- Phatsornsiri, P.; Kumngern, M.; Khateb, F. 0.5-V fully differential allpass section. In Proceedings of the 2016 International Symposium on Intelligent Signal Processing and Communication Systems (ISPACS), Phuket, Thailand, 24–27 October 2016; IEEE: Piscataway, NJ, USA, 2016; pp. 1–4. [Google Scholar]

- Maheshwari, S.; Chaturvedi, B.; Tiwari, P.K.; Khan, I.A. Fully differential first order all-pass filter circuit. In Proceedings of the National Conference on Modern Trends in Electronic and Communication Systems (MTECS), Aligarh, India, 8–9 March 2008; pp. 131–134. [Google Scholar]

- Horng, J.W.; Wu, C.M.; Herencsar, N. Fully differential first-order allpass filters using a DDCC. Indian J. Eng. Mater. Sci. 2014, 21, 345–350. [Google Scholar]

- Khan, I.A.; Masud, M.I.; Moiz, S.A. Reconfigurable fully differential first order all pass filter using digitally controlled CMOS DVCC. In Proceedings of the 2015 IEEE 8th GCC Conference & Exhibition, Muscat, Oman, 1–4 February 2015; pp. 1–5. [Google Scholar]

- Beg, P.; Ansari, M.S. Fully-differential first-order all-pass filters using CMOS DV-DXCCII. In Proceedings of the 2017 International Conference on Multimedia, Signal Processing and Communication Technologies (IMPACT), Aligarh, India, 24–26 November 2017; pp. 267–270. [Google Scholar]

- Ansari, M.S.; Soni, G.S. Digitally-programmable fully-differential current-mode first-order LP, HP and AP filter sections. In Proceedings of the 2014 International Conference on Signal Propagation and Computer Technology (ICSPCT 2014), Ajmer, India, 12–13 July 2014; pp. 524–528. [Google Scholar]

- Herencsar, N.; Jerabek, J.; Koton, J.; Vrba, K.; Minaei, S.; Göknar, İ.C. Pole frequency and pass-band gain tunable novel fully-differential current-mode all-pass filter. In Proceedings of the 2015 IEEE International Symposium on Circuits and Systems (ISCAS), Lisbon, Portugal, 24–27 May 2015; pp. 2668–2671. [Google Scholar]

- Kumngern, M.; Khateb, F.; Kulej, T. Bulk-driven fully balanced second-generation current conveyor in 0.18 µm CMOS. AEU-Int. J. Electron. Commun. 2019, 104, 66–75. [Google Scholar] [CrossRef]

- İbrahim, M.A.; Minaei, S.; Kuntman, H. DVCC based differential-mode all-pass and notch filters with high CMRR. Int. J. Electron. 2006, 93, 231–240. [Google Scholar] [CrossRef]

- Biolek, D. CDTA-building block for current-mode analog signal processing. In Proceedings of the ECCTD’03, Krakow, Poland, 1–4 September 2003; Volume III, pp. 397–400. [Google Scholar]

- Keskin, A.Ü.; Biolek, D.; Hancioglu, E.; Biolková, V. Current-mode KHN filter employing current differencing transconductance amplifiers. AEU-Int. J. Electron. Commun. 2006, 60, 443–446. [Google Scholar] [CrossRef]

- Keskin, A.Ü.; Biolek, D. Current mode quadrature oscillator using current differencing transconductance amplifiers (CDTA). IEE Proc.-Circuits Devices Syst. 2006, 153, 214–218. [Google Scholar] [CrossRef] [Green Version]

- Biolek, D.; Hancioglu, E.; Keskin, A.Ü. High-performance current differencing transconductance amplifier and its application in precision current-mode rectification. AEU-Int. J. Electron. Commun. 2008, 62, 92–96. [Google Scholar] [CrossRef] [Green Version]

- Khateb, F.; Vavra, J.; Biolek, D. A Novel Current-Mode Full-Wave Rectifier Based on One CDTA and Two Diodes. Radioengineering 2010, 19, 437–445. [Google Scholar]

| MOS Transistors | W(μm)/L(μm) Ratio |

|---|---|

| M1–M3 | 26/0.26 |

| M4–M6, | 10.4/0.26 |

| M8–M11, M13–M18, M22, M23 | 3.9/0.26 |

| M7, M12 | 15.6/0.26 |

| M19–M21 | 13/0.26 |

| M24–M30 | 1.5/0.26 |

| M31–M35 | 1/0.26 |

| Parameter | Simulated Value |

|---|---|

| α1, α2, α3 | 0.99 |

| −3 dB bandwidth of α1, α2, α3 | 1 GHz |

| −3 dB bandwidth of γ1, γ2, γ3 | 2 GHz |

| RP, RN | 14 Ω |

| RZ1, RZ2 | 100 kΩ |

| RO1+, RO2−, RO3− | 125 kΩ |

| Ref. | Active Element/ Count | Passive Components with Count | All Grounded Passive Component | Passive Component Matching Restriction | Operating Mode | Cascadable | Availability of LP, HP and AP Responses | MOS Transistors Count | Technology (µm) | Max Operation Frequency | Supply Voltage(s) (V) |

|---|---|---|---|---|---|---|---|---|---|---|---|

| [12] | FDDTA/1 | 1-R, 2-C | No | Yes | VM | No | Only AP | 34 | 0.18 | 0.04 MHz | 0.5 |

| [13] | DVCC/1 | 3-R, 1-C | No | Yes | VM | No | Only AP | 18 | 0.5 | 2.27 MHz | ±2.5 |

| [14] | DDCC/1 | 3-R, 1-C | No | Yes | VM | No | Only AP | 12 | 0.18 | 0.32 MHz | ±0.9 |

| [15] | DPDVCC/2 | 2-R, 2-C | No | Yes | VM | No | AP and LP or AP and HP | 92 | 0.25 | 0.27 MHz | ±2.5 |

| [16] | DV-DXCCII/1 | 3-R, 2-C or 2-R, 3-C | No | Yes | VM | No | Only AP | 30 | 0.25 | 6.13 MHz | ±1.25 |

| [17] | DC-DVCC/1 | 2-R, 1-C | No | Yes | CM | Yes | LP and HP | 38 | 0.5 | 1.58 MHz | ±2.5 |

| DC-DVCC/2 | 4-R, 2-C | No | Yes | CM | Yes | Only AP | 76 | 0.5 | 1.58 MHz | ±2.5 | |

| [18] | ACA/1, CF/2 | 1-C | No | No | CM | Yes | Only AP | 50 | 0.18 | 0.94 MHz | ±1.2 |

| [19] | FBCCII/1 | 6-R, 2-C | No | Yes | VM | No | Only AP | 34 | 0.18 | 290 Hz | 0.5 |

| [20] | DVCC/1 | 1-R, 3-C | No | Yes | VM | No | Only AP | 18 | 0.5 | 3.18 MHz | ±2.5 |

| This work | MOCDTA/1 | 1-C | Yes | No | CM | Yes | All LP, HP and AP | 35 | 0.13 | 73 MHz | ±1 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kumar, A.; Kumar, S.; Elkamchouchi, D.H.; Urooj, S. Fully Differential Current-Mode Configuration for the Realization of First-Order Filters with Ease of Cascadability. Electronics 2022, 11, 2072. https://doi.org/10.3390/electronics11132072

Kumar A, Kumar S, Elkamchouchi DH, Urooj S. Fully Differential Current-Mode Configuration for the Realization of First-Order Filters with Ease of Cascadability. Electronics. 2022; 11(13):2072. https://doi.org/10.3390/electronics11132072

Chicago/Turabian StyleKumar, Atul, Sumit Kumar, Dalia H. Elkamchouchi, and Shabana Urooj. 2022. "Fully Differential Current-Mode Configuration for the Realization of First-Order Filters with Ease of Cascadability" Electronics 11, no. 13: 2072. https://doi.org/10.3390/electronics11132072