Error Detection and Correction of Mismatch Errors in M-Channel TIADCs Based on Genetic Algorithm Optimization

Abstract

:1. Introduction

2. Materials and Methods

2.1. Model of TIADCs’ Mismatch Errors

2.2. Sine-Fit-Based Estimation and the First Correction

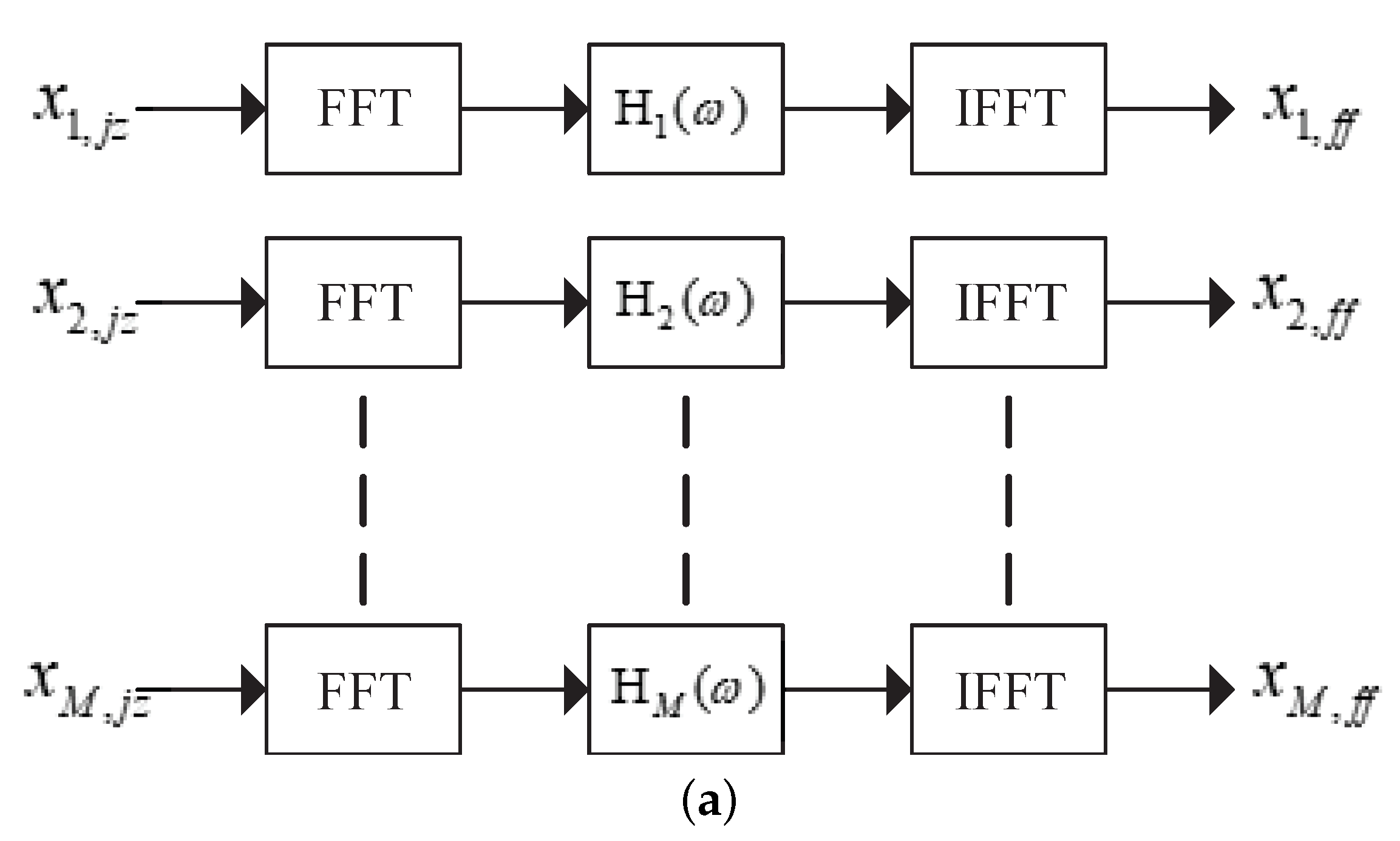

2.3. Frequency Domain Filtering Correction

2.4. Error Estimation and Correction Based on GA Optimization

2.5. The Second Fine Correction for Offset Error and Gain Error

2.6. Calibration of Farrow Fractional Delay Filters

3. Results

3.1. Detection of Mismatch Errors

3.2. Correction of Mismatch Errors

3.3. Comparison with Other Work

3.4. Hardware Validation

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Black, W.C.; Hodges, D.A. Time interleaved converter arrays. IEEE J. Solid-State Circuits 1980, 15, 1022–1029. [Google Scholar] [CrossRef]

- Razavi, B. Design Considerations for Interleaved ADCs. IEEE J. Solid-State Circuits 2013, 48, 1806–1817. [Google Scholar] [CrossRef] [Green Version]

- Wei, W.; Ye, P.; Yang, K.; Zeng, H.; Song, J.; Zhao, Y. Compensation of dynamic nonlinear mismatches in time-interleaved analog-to-digital converter. IEICE Electron. Express 2019, 16, 1–6. [Google Scholar] [CrossRef] [Green Version]

- Kurosawa, N.; Kobayashi, H.; Maruyama, K.; Sugawara, H.; Kobayashi, K. Explicit analysis of channel mismatch effects in time-interleaved ADC systems. IEEE Trans. Circuits Syst. I Fundam. Theory Appl. 2001, 48, 261–271. [Google Scholar] [CrossRef] [Green Version]

- Parkey, C.R.; Mikhael, W.B. Time interleaved analog to digital converters: Tutorial 44. IEEE Instrum. Meas. Mag. 2013, 16, 42–51. [Google Scholar] [CrossRef]

- Salib, A.; Flanagan, M.F.; Cardiff, B. A High-Precision Time Skew Estimation and Correction Technique for Time-Interleaved ADCs. IEEE Trans. Circuits Syst. I Regul. Pap. 2019, 66, 3747–3760. [Google Scholar] [CrossRef] [Green Version]

- Monsurro, P.; Trifiletti, A. Calibration of Time-Interleaved ADCs via Hermitianity Preserving Taylor Approximations. IEEE Trans. Circuits Syst. II Express Briefs 2017, 64, 357–361. [Google Scholar] [CrossRef]

- Buchwald, A. High-speed time interleaved ADCs. IEEE Commun. Mag. 2016, 54, 71–77. [Google Scholar] [CrossRef]

- Razavi, B. Problem of timing mismatch in interleaved ADCs. In Proceedings of the 2012 IEEE Custom Integrated Circuits Conference (CICC), San Jose, CA, USA, 9–12 September 2012. [Google Scholar]

- Yin, M.; Ye, Z. First Order Statistic Based Fast Blind Calibration of Time Skews for Time-Interleaved ADCs. IEEE Trans. Circuits Syst. II Express Briefs 2020, 67, 162–166. [Google Scholar] [CrossRef]

- Huang, L.; Lin, B.Y.; Zhang, S.D. A Digital-Background TIADC Calibration Architecture and A Fast Calibration Algorithm for Timing-Error Mismatch. In Proceedings of the 2007 7th International Conference on ASIC, Guilin, China, 26–29 October 2007. [Google Scholar] [CrossRef]

- Li, J.; Wu, S.Y.; Liu, Y.; Ning, N.; Yu, Q. A Digital Timing Mismatch Calibration Technique in Time-Interleaved ADCs. IEEE Trans. Circuits Syst. II Express Briefs 2014, 61, 486–490. [Google Scholar] [CrossRef]

- Elbornsson, J.; Eklund, J.E. Blind estimation of timing errors in interleaved AD converters. In Proceedings of the 2001 IEEE International Conference on Acoustics, Speech, and Signal Processing, Salt Lake City, UT, USA, 7–11 May 2001. [Google Scholar]

- Elbornsson, J.; Gustafsson, F.; Eklund, J.-E. Blind equalization of time errors in a time-interleaved ADC system. IEEE Trans. Signal Process. 2005, 53, 1413–1424. [Google Scholar] [CrossRef] [Green Version]

- Zou, Y.X.; Xu, X.J. Blind Timing Skew Estimation Using Source Spectrum Sparsity in Time-Interleaved ADCs. IEEE Trans. Instrum. Meas. 2012, 61, 2401–2412. [Google Scholar] [CrossRef]

- El-Chammas, M.; Murmann, B. A 12-GS/s 81-mW 5-bit Time-Interleaved Flash ADC With Background Timing Skew Calibration. IEEE J. Solid-State Circuits 2011, 46, 838–847. [Google Scholar] [CrossRef]

- Guo, M.Q.; Sin, S.W.; Seng-Pan, U.; Martins, R.P. Split-based time-interleaved ADC with digital background timing-skew calibration. In Proceedings of the 2017 13th Conference on Ph.D. Research in Microelectronics and Electronics (PRIME), Taormina, Italy, 12–15 June 2017. [Google Scholar]

- Guo, M.Q.; Mao, J.J.; Sin, S.W.; Wei, H.G.; Martins, R.P. A 1.6-GS/s 12.2-mW Seven-/Eight-Way Split Time-Interleaved SAR ADC Achieving 54.2-dB SNDR With Digital Background Timing Mismatch Calibration. IEEE J. Solid-State Circuits 2020, 55, 693–705. [Google Scholar] [CrossRef]

- Hung, T.C.; Liao, F.W.; Kuo, T.H. A 12-Bit Time-Interleaved 400-MS/s Pipelined ADC With Split-ADC Digital Background Calibration in 4000 Conversions/Channel. IEEE Trans. Circuits Syst. II Express Briefs 2019, 66, 1810–1814. [Google Scholar] [CrossRef]

- Prendergast, R.S.; Levy, B.C.; Hurst, P.J. Reconstruction of band-limited periodic nonuniformly sampled signals through multirate filter banks. IEEE Trans. Circuits Syst. I Regul. Pap. 2004, 51, 1612–1622. [Google Scholar] [CrossRef]

- Li, D.; Zhu, Z.; Zhang, L.; Yang, Y. A background fast convergence algorithm for timing skew in time-Interleaved ADCs. Microelectron. J. 2016, 47, 45–52. [Google Scholar] [CrossRef]

- Ye, F.; Zhang, P.; Yu, B.; Chen, C.X.; Zhu, Y.; Ren, J.Y. A 14-bit 200-MS/s time-interleaved ADC calibrated with LMS-FIR and interpolation filter. In Proceedings of the 2011 IEEE International Conference of Electron Devices and Solid-State Circuits (EDSSC), Tianjin, China, 17–18 November 2011. [Google Scholar]

- Matsuno, J.; Yamaji, T.; Furuta, M.; Itakura, T. All-Digital Background Calibration Technique for Time-Interleaved ADC Using Pseudo Aliasing Signal. IEEE Trans. Circuits Syst. I Regul. Pap. 2013, 60, 1113–1121. [Google Scholar] [CrossRef]

- Qiu, Y.; Liu, Y.J.; Zhou, J.; Zhang, G.; Chen, D.; Du, N. All-Digital Blind Background Calibration Technique for Any Channel Time-Interleaved ADC. IEEE Trans. Circuits Syst. I Regul. Pap. 2018, 65, 2503–2514. [Google Scholar] [CrossRef]

- Liu, C.; Luo, X.; Niu, G.; Li, X.; Zhang, J. Error detection and correction of TIADC based on GA optimization. In Proceedings of the 2021 International Conference on Electronics, Circuits and Information Engineering (ECIE), Zhengzhou, China, 22–24 January 2021. [Google Scholar]

- Vucijak, N.M.; Radojevic, N.M. Three, Four and Seven Parameters Sine-fitting Algorithms Applied in the Electric Power Calibrations. In Proceedings of the International Conference on Computer as a Tool (EUROCON 2005), Belgrade, Serbia Monteneg, 21–24 November 2005. [Google Scholar]

- Belega, D.; Dallet, D.; Petri, D. Performance comparison of the three-parameter and the four-parameter sine-fit algorithms. In Proceedings of the 2011 IEEE International Instrumentation and Measurement Technology Conference (I2MTC), Hangzhou, China, 10–12 May 2011. [Google Scholar]

- IEEE Std 1241–2000; Std I. IEEE Standard for Terminology and Test Methods for Analog-to-Digital Converters. IEEE: New York, NY, USA, 2001; pp. 1–98. [CrossRef] [Green Version]

- Yang, K.J.; Shi, J.L.; Yang, H.Z. A TIADC mismatch calibration method for digital storage oscilloscope. In Proceedings of the 2017 13th IEEE International Conference on Electronic Measurement & Instruments (ICEMI), Yangzhou, China, 20–22 October 2017. [Google Scholar]

- Walden, R.H. Analog-to-digital converter survey and analysis. IEEE J. Sel. Areas Commun. 1999, 17, 539–550. [Google Scholar] [CrossRef] [Green Version]

- Duc, H.L.; Nguyen, D.M.; Jabbour, C.; Graba, T.; Desgreys, P.; Jamin, O.; Nguyen, V.T. All-Digital Calibration of Timing Skews for TIADCs Using the Polyphase Decomposition. IEEE Trans. Circuits Syst. II Express Briefs 2016, 63, 99–103. [Google Scholar] [CrossRef]

- Centurelli, F.; Monsurro, P.; Trifiletti, A. Efficient Digital Background Calibration of Time-Interleaved Pipeline Analog-to-Digital Converters. IEEE Trans. Circuits Syst. I Regul. Pap. 2012, 59, 1373–1383. [Google Scholar] [CrossRef]

- Kang, H.W.; Hong, H.K.; Park, S.; Kim, K.J.; Ahn, K.H.; Ryu, S.T. A Sign-Equality-Based Background Timing-Mismatch Calibration Algorithm for Time-Interleaved ADCs. IEEE Trans. Circuits Syst. II Express Briefs 2016, 63, 518–522. [Google Scholar] [CrossRef]

| Sub-ADC | Error Type | ||||||||

|---|---|---|---|---|---|---|---|---|---|

| ADC0 | 0.1 | 0.1000 | 0.0049 × | 0.0 | 0.0000 | −0.0001 × | 10 | 7.0251 | −0.0998 |

| ADC1 | 0.2 | 0.2000 | 0.0098 × | 0.4 | 0.4000 | 0.0195 × | 40 | 37.9693 | 0.4000 |

| ADC2 | 0.1 | 0.1000 | 0.1610 × | 0.3 | 0.3000 | −0.2488 × | 50 | 48.9833 | −0.2502 |

| ADC3 | 0.3 | 0.3000 | −0.0146 × | 0.4 | 0.4000 | −0.1366 × | 40 | 40.0438 | −0.0004 |

| Characteristics | Ref. [21] | Ref. [31] | Ref. [32] | Ref. [33] | Ref. [22] | This Work |

|---|---|---|---|---|---|---|

| All digital | no | yes | yes | yes | yes | yes |

| Mismatch type | timing | timing | offset, gain and timing | timing | offset, gain, timing and bandwidth | offset, gain and timing |

| Add ref. channel | no | no | yes | no | no | no |

| M (# of channels) | 4 | 4 | 4 | 8 | 2 | 4 |

| Wide freq. range | yes | yes | no | yes | yes | yes |

| Resolution (bit) | 8 | 11 | 12 | 10 | 14 | 18 |

| Family | Virtex VII |

|---|---|

| Device | xc7vx485tffg1157-1 |

| LUT | 30480/303600 (10%) |

| LUTRAM | 13768/130800 (11%) |

| Flip-Flop | 30576/607200 (5%) |

| DSP | 516/2800 (18%) |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Li, Y.; Liu, C.; Niu, G.; Luo, X.; Ma, H.; Zhao, Y. Error Detection and Correction of Mismatch Errors in M-Channel TIADCs Based on Genetic Algorithm Optimization. Electronics 2022, 11, 2366. https://doi.org/10.3390/electronics11152366

Li Y, Liu C, Niu G, Luo X, Ma H, Zhao Y. Error Detection and Correction of Mismatch Errors in M-Channel TIADCs Based on Genetic Algorithm Optimization. Electronics. 2022; 11(15):2366. https://doi.org/10.3390/electronics11152366

Chicago/Turabian StyleLi, Yuehui, Cong Liu, Guangshan Niu, Xiangdong Luo, Haocheng Ma, and Yiqiang Zhao. 2022. "Error Detection and Correction of Mismatch Errors in M-Channel TIADCs Based on Genetic Algorithm Optimization" Electronics 11, no. 15: 2366. https://doi.org/10.3390/electronics11152366