Electronically Adjustable Multiphase Sinusoidal Oscillator with High-Output Impedance at Output Current Nodes Using VDCCs

Abstract

:1. Introduction

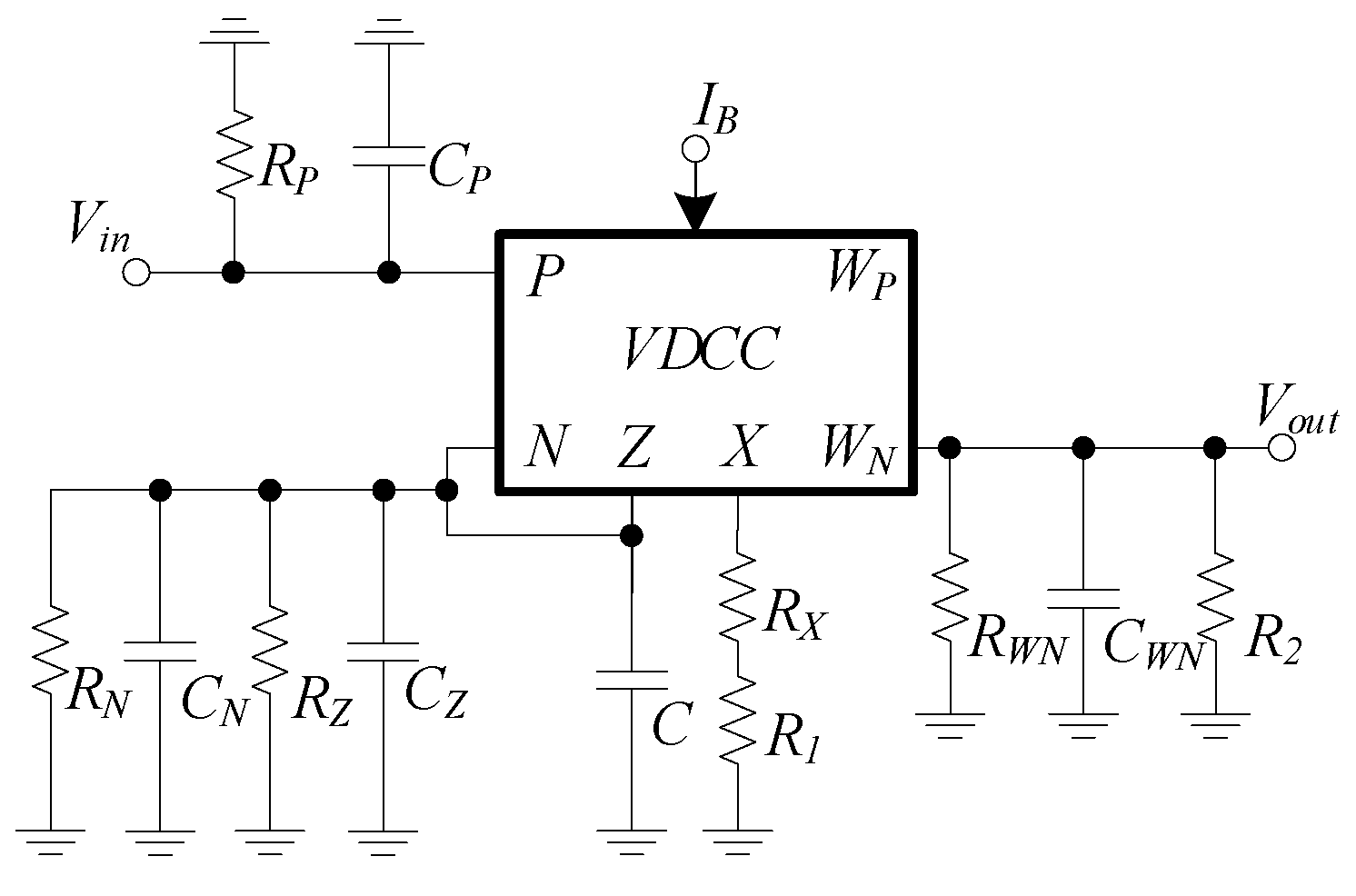

2. Principle of Operation

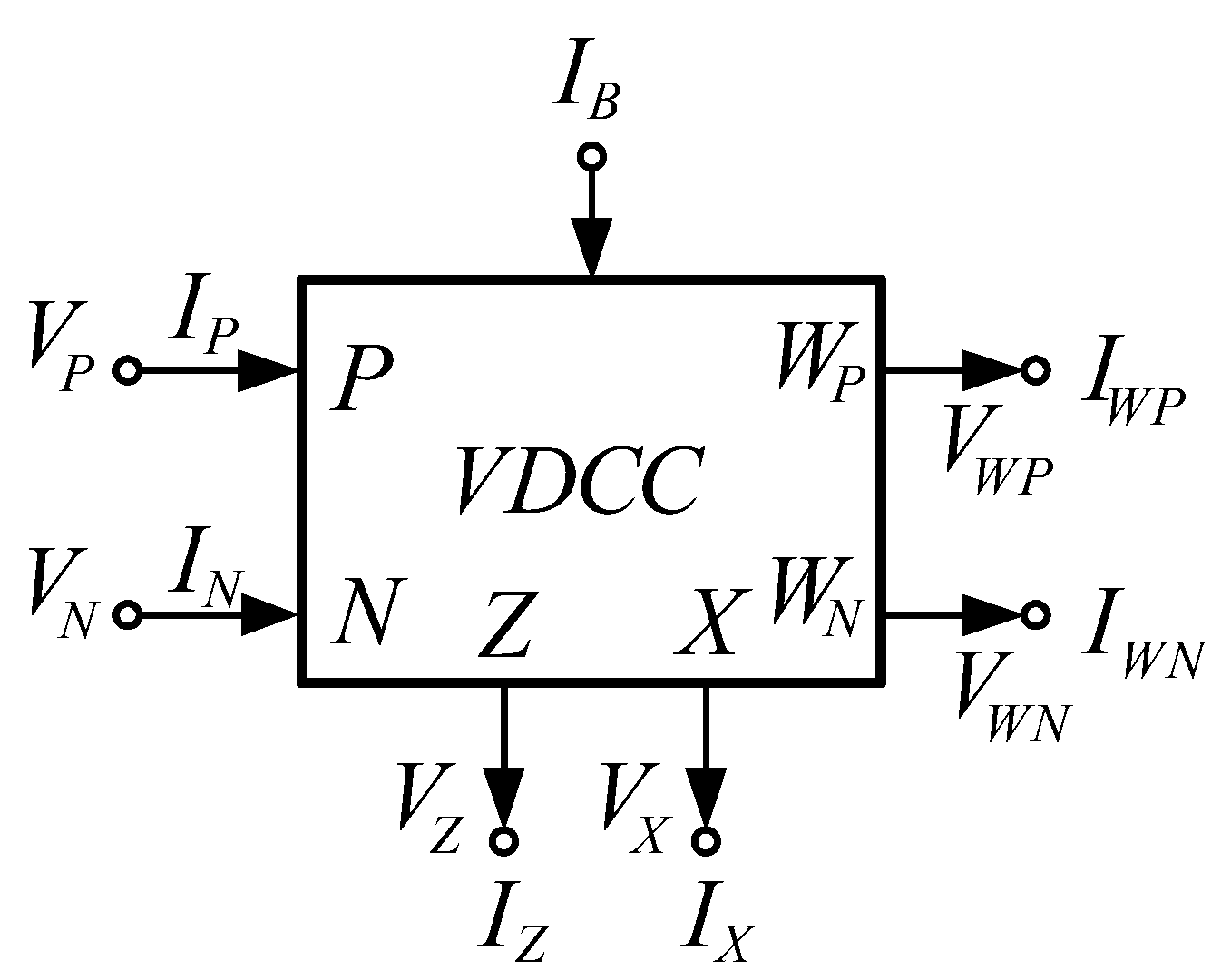

2.1. Basic Concept of VDCC

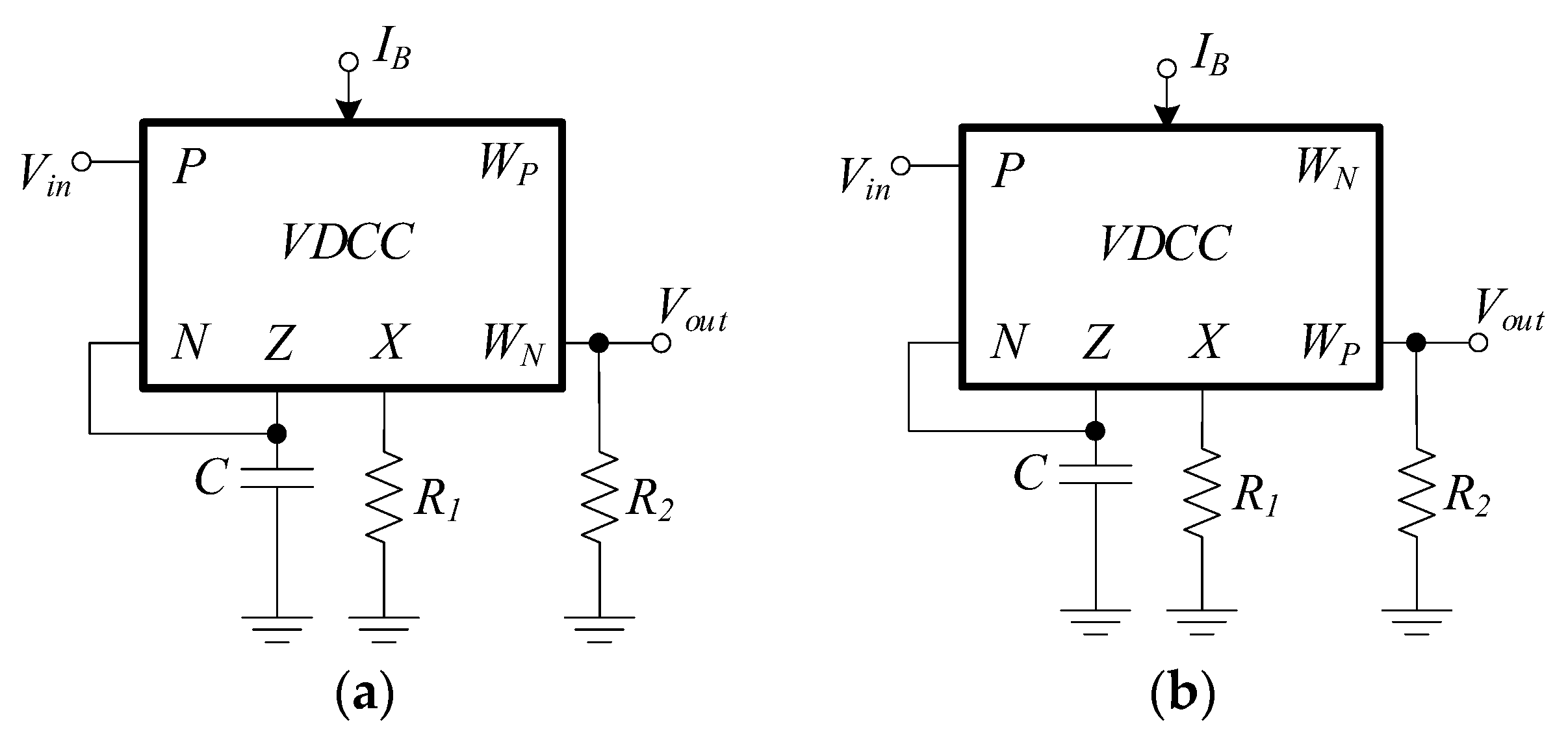

2.2. Design of MSOs Using Lossy Integrator Circuit

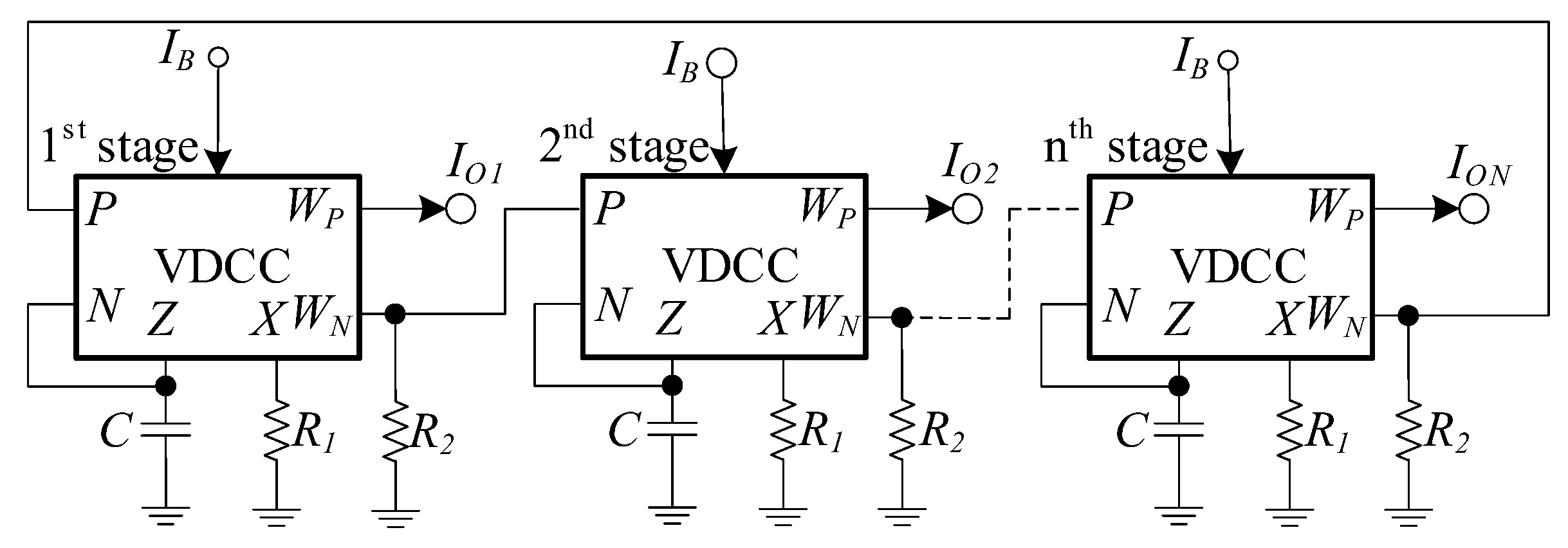

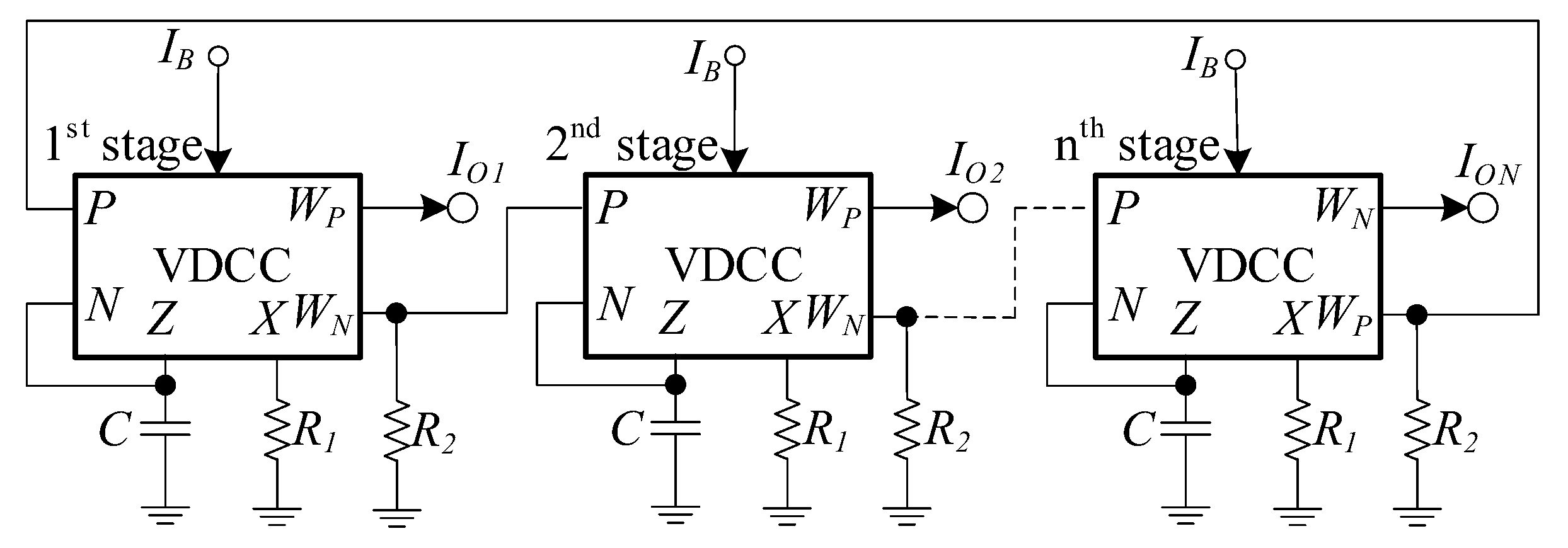

2.3. Implementation of n-Cascaded Lossy Integrator-Based Multiphase Sinusoidal Oscillator

2.4. Non-Ideal Analysis

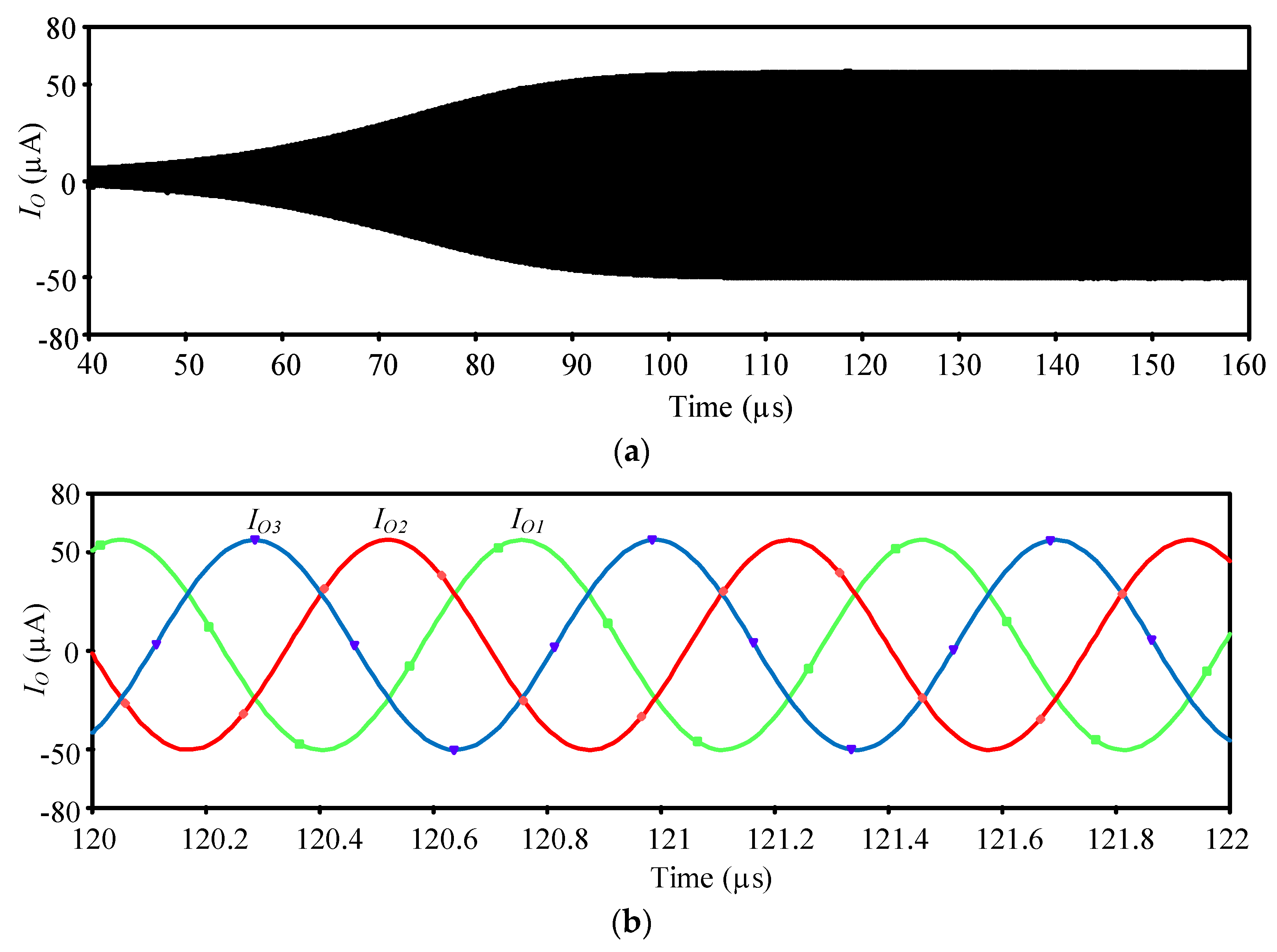

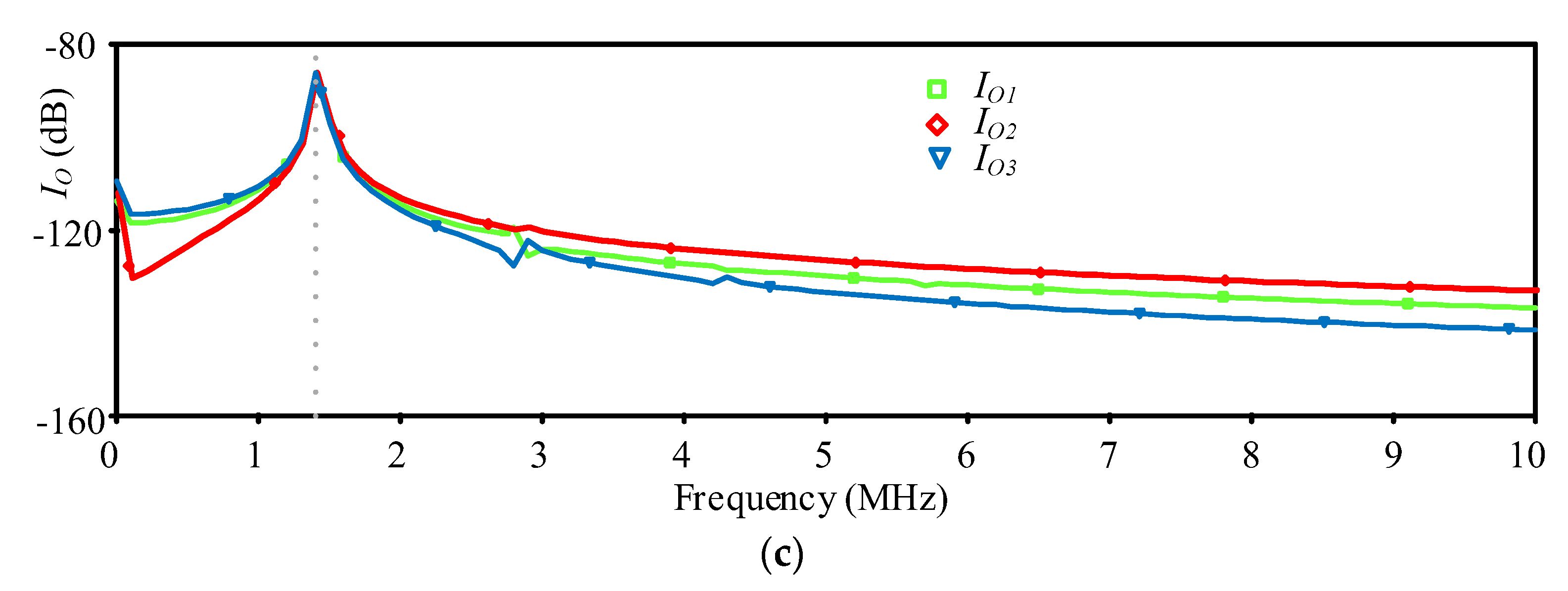

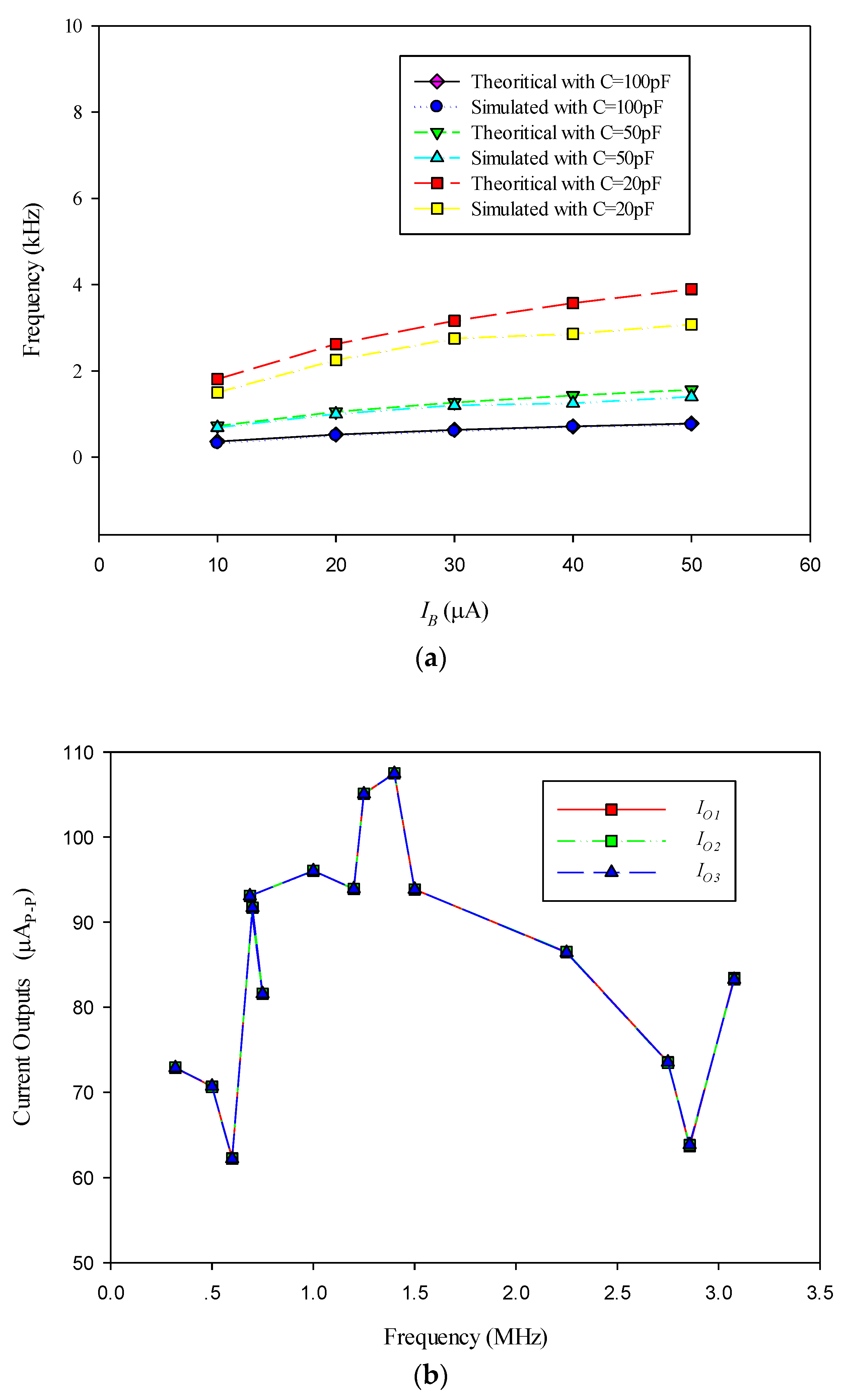

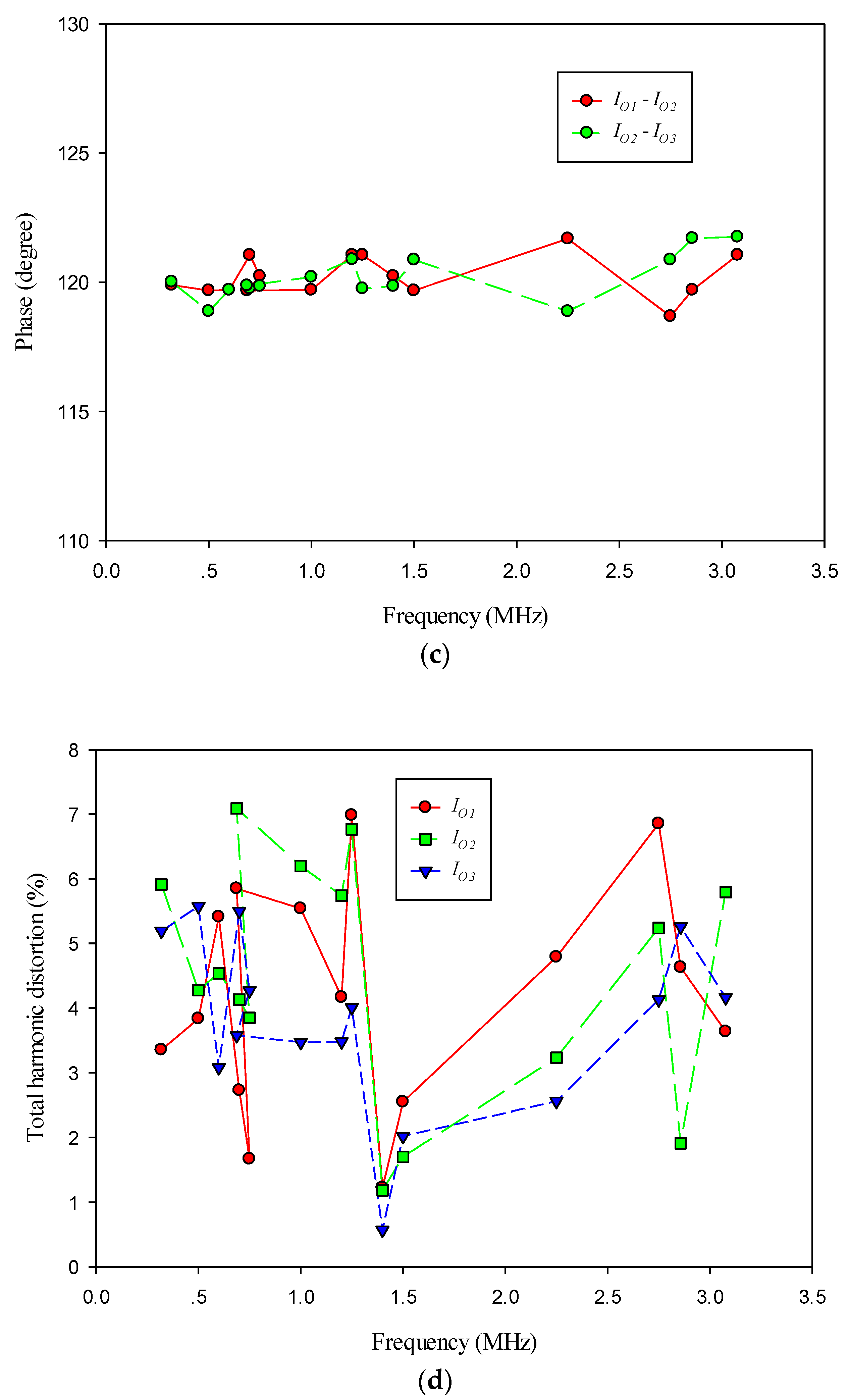

3. Simulation Results

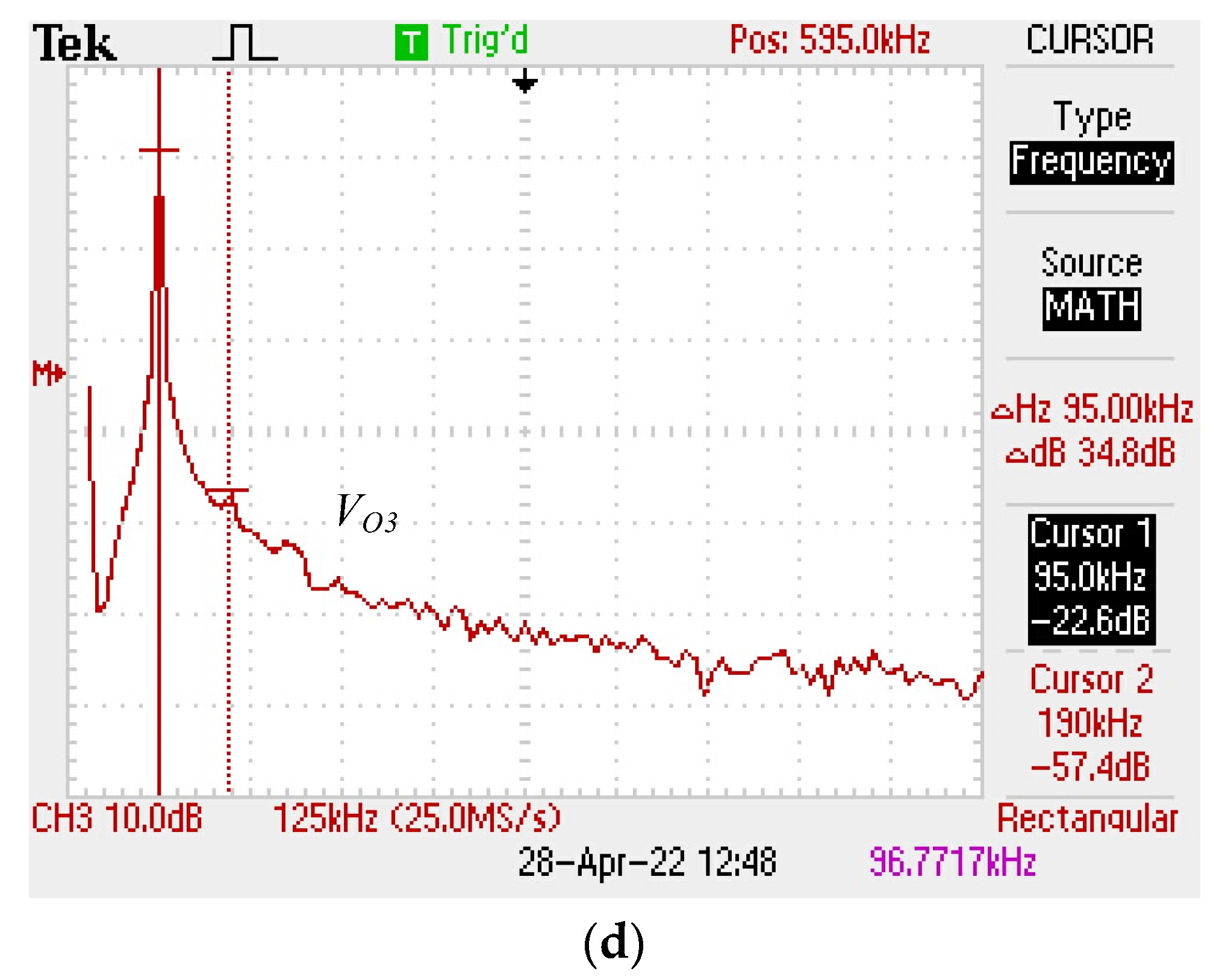

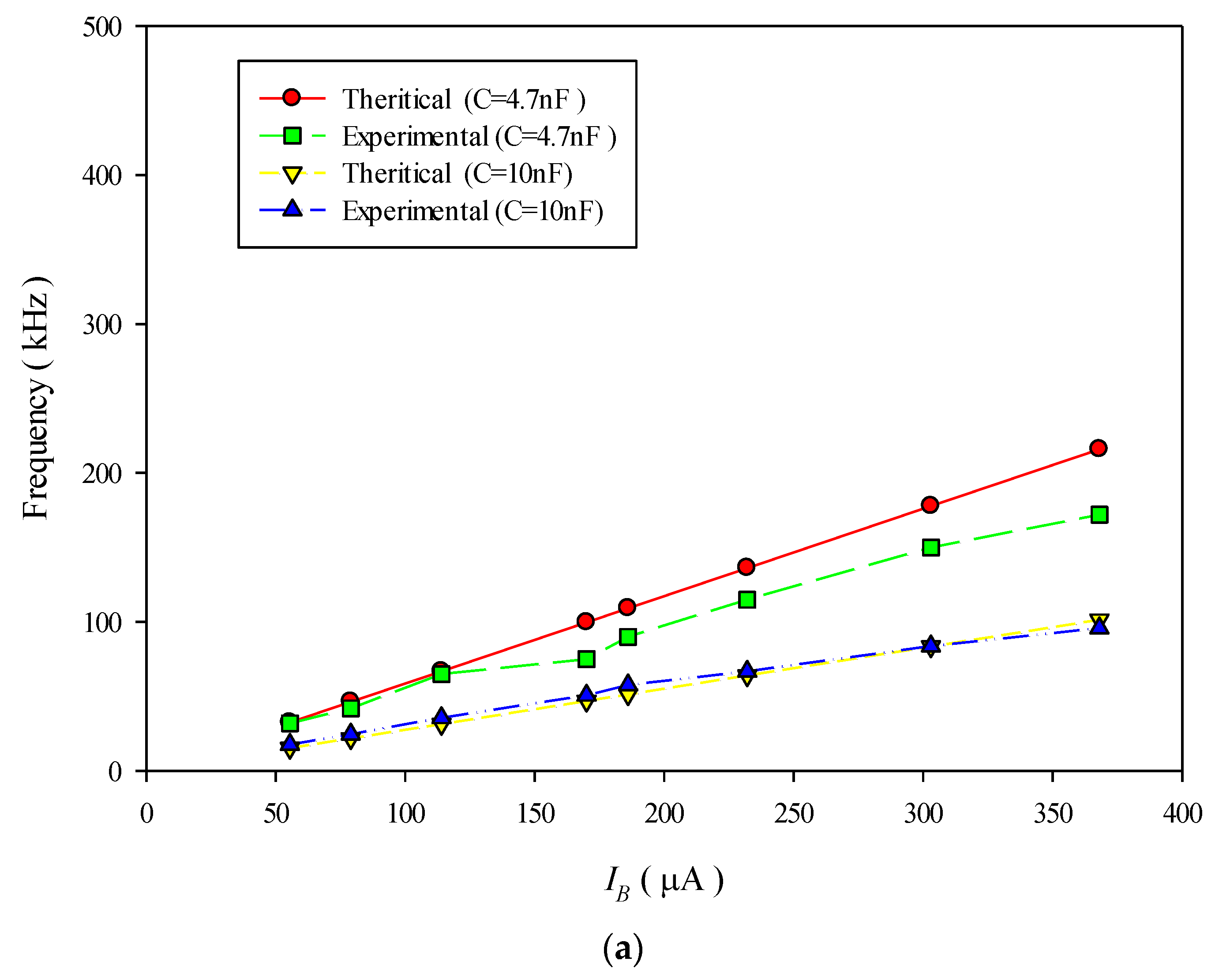

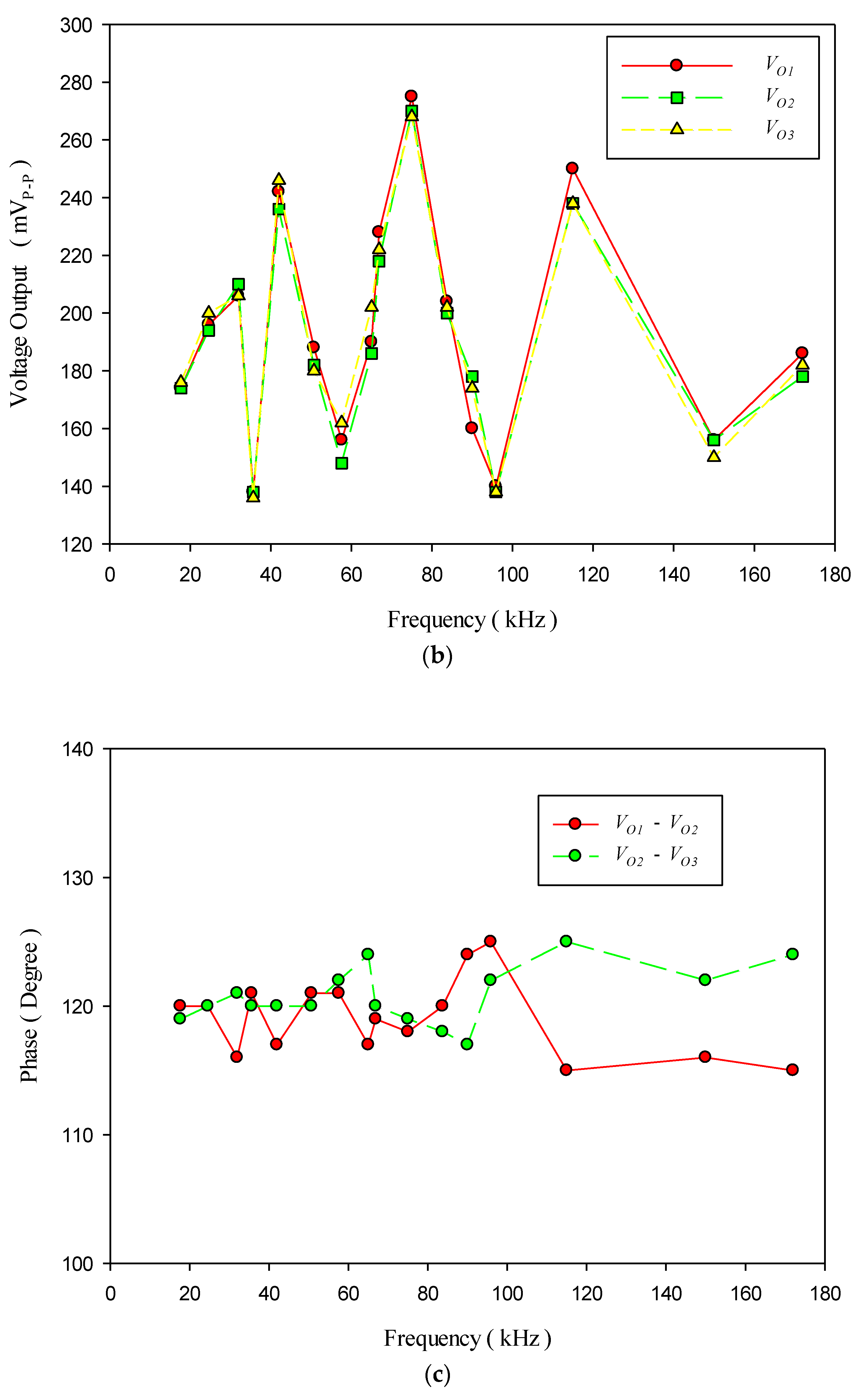

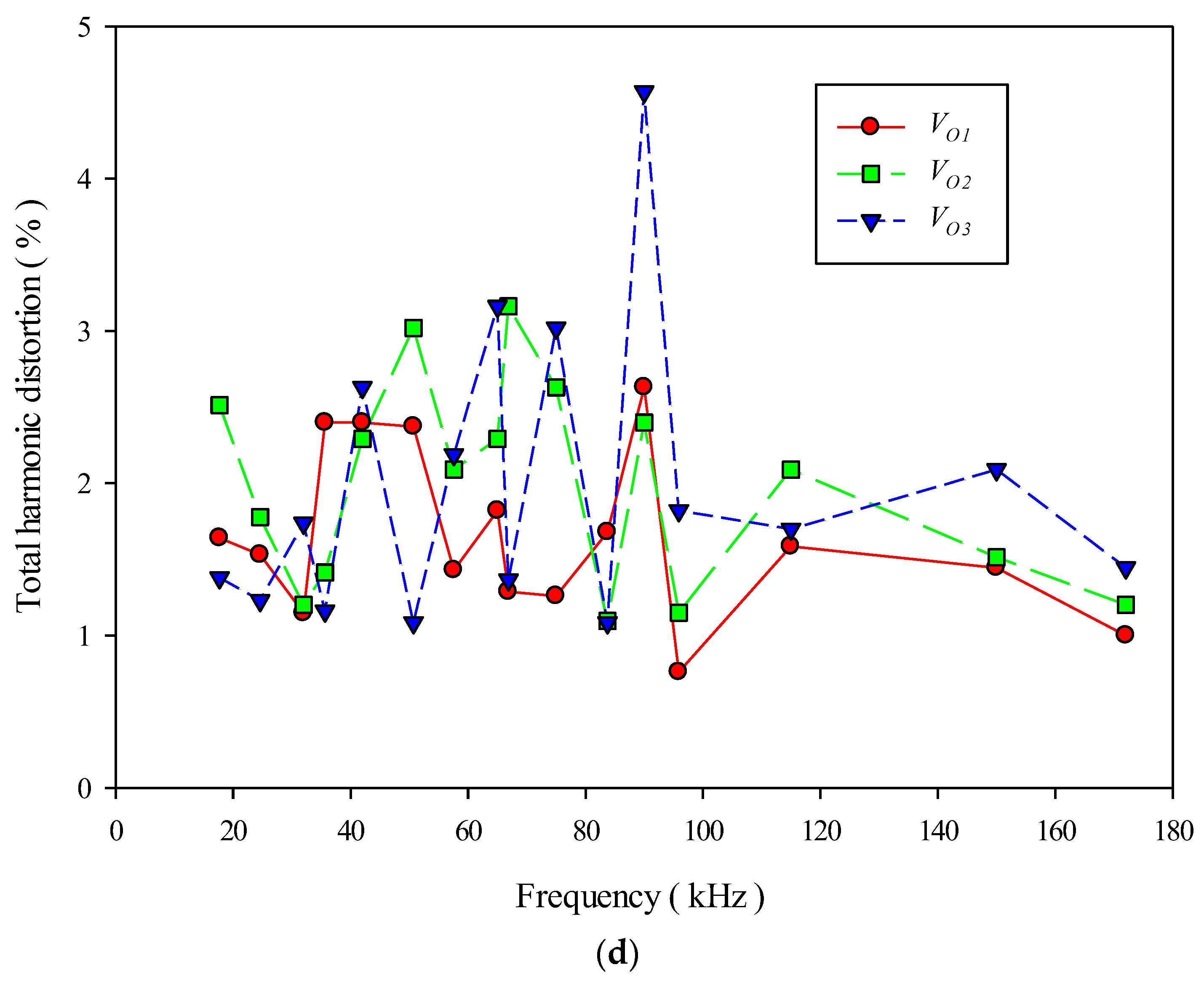

4. Experimental Results

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Fouda, M.E.; Soltan, A.; Radwan, A.G.; Soliman, A.M. Fractional-order multi-phase oscillators design and analysis suitable for higher-order PSK applications. Analog Integr. Circuits Signal Process. 2016, 87, 301–312. [Google Scholar] [CrossRef]

- Jang, Y.; Jovanovic, M.M.; Panov, Y. Multiphase buck converters with extended duty cycle. In Proceedings of the Twenty-First Annual IEEE Applied Power Electronics Conference and Exposition (APEC’06), Dallas, TX, USA, 19–23 March 2006; pp. 38–44. [Google Scholar]

- Domansky, O.; Sotner, R.; Langhammer, L.; Jerabek, J.; Psychalinos, C.; Tsirimokou, G. Practical design of RC approximants of constant phase elements and their implementation in fractional-order PID regulators using CMOS voltage differencing current conveyors. Circuits Syst. Signal Process. 2019, 38, 1520–1546. [Google Scholar] [CrossRef]

- Özer, E.; Kaçar, F. Design of voltage-mode PID controller using a single voltage differencing current conveyor (VDCC). Analog Integr. Circuits Signal Process. 2021, 109, 11–27. [Google Scholar] [CrossRef]

- Prasad, D.; Ahmad, J.; Srivastava, M. New CM/VM 3rd-order quadrature oscillator using VDCCs. In Proceedings of the International Conference on Applied System Innovation (ICASI), Sapporo, Japan, 13–17 May 2017; pp. 1328–1330. [Google Scholar]

- Roy, S.; Pal, R.R. Electronically tunable third-order dual-mode quadrature sinusoidal oscillators employing VDCCs and all grounded components. Integration 2021, 76, 99–112. [Google Scholar] [CrossRef]

- Srivastava, M.; Prasad, D. VDCC based dual-mode quadrature sinusoidal oscillator with outputs at appropriate impedance levels. Adv. Electr. Electron. Eng. 2016, 14, 168–177. [Google Scholar] [CrossRef]

- Arora, T.S. Realization of current-mode universal filter utilising minimum active elements and only grounded passive components. In Proceedings of the 2020 7th International Conference on Signal Processing and Integrated Networks (SPIN), Noida, India, 27–28 February 2020; pp. 681–686. [Google Scholar]

- Lamun, P.; Phatsornsiri, P.; Torteanchai, U. Single VDCC-based current-mode universal biquadratic filter. In Proceedings of the 2015 7th International Conference on Information Technology and Electrical Engineering (ICITEE), Chiang Mai, Thailand, 29–30 October 2015; pp. 122–125. [Google Scholar]

- Rana, S.; Kumawat, A.K.; Kumar, P. A universal current mode KHN biquad filter using voltage differencing current conveyor. In Proceedings of the 2016 IEEE 1st International Conference on Power Electronics, Intelligent Control and Energy Systems (ICPEICES), Delhi, India, 4–6 July 2016; pp. 1–5. [Google Scholar]

- Cheta, W.; Siripruchyanun, M.; Trachu, K.; Suwanjan, P.; Sotner, R.; Jaikla, W. Single VDCC based voltage-mode first-order allpass filter with electronic controllability. In Proceedings of the 2018 18th International Symposium on Communications and Information Technologies (ISCIT), Bangkok, Thailand, 26–29 September 2018; pp. 255–260. [Google Scholar]

- Uttaphut, P. Voltage-Mode first-order allpass filter with grounded capacitor and electronic controllability. Przegląd Elektrotechniczny 2019, 95, 101–104. [Google Scholar] [CrossRef]

- Prasad, D.; Ahmad, A.; Shukla, A.; Mukhopadhyay, A.; Sharma, B.B.; Srivastava, M. Novel VDCC based low-pass and high-pass ladder filters. In Proceedings of the 2015 Annual IEEE India Conference (INDICON), New Delhi, India, 17–20 December 2015; pp. 1–3. [Google Scholar]

- Kartci, A.; Ayten, U.E.; Herencsar, N.; Sotner, R.; Jerabek, J.; Vrba, K. Floating capacitance multiplier simulator for grounded RC colpitts oscillator design. In Proceedings of the 2015 International Conference on Applied Electronics (AE), Pilsen, Czech Republic, 8–9 September 2015; pp. 93–96. [Google Scholar]

- Kumar, R.; Kumar, A.; Bhardwaj, K.; Srivastava, M. Active realization of series inductor and shunt capacitor and their applications in electronically tunable wave active filters. In Proceedings of the 2021 5th International Conference on Computing Methodologies and Communication (ICCMC), Erode, India, 8–10 April 2021; pp. 683–688. [Google Scholar]

- Srivastava, M.; Roy, A.; Singh, R.; Gupta, P. New VDCC based electronically tunable grounded frequency dependent negative resistance simulator employing grounded passive elements. In Proceedings of the 2017 Recent Developments in Control, Automation & Power Engineering (RDCAPE), Noida, India, 26–27 October 2017; pp. 313–317. [Google Scholar]

- Kumar, K.N.; Mouli, P.C.; Das, K.S.; Srivastava, M. Novel Electronic/Resistance Adjustable Capacitance Multiplier Circuit with VDCCs and Grounded Resistances. In Proceedings of the 2019 6th International Conference on Signal Processing and Integrated Networks (SPIN), Noida, India, 7–8 March 2019; pp. 1112–1115. [Google Scholar]

- Jerabek, J.; Sotner, R.; Dostal, T.; Vrba, K. Simple resistor-less generator utilizing z-copy controlled gain voltage differencing current conveyor for PWM generation. Elektron. Ir Elektrotechnika 2015, 21, 28–34. [Google Scholar] [CrossRef] [Green Version]

- Sotner, R.; Jerabek, J.; Herencsar, N.; Dostal, T.; Vrba, K. Design of Z-copy controlled-gain voltage differencing current conveyor based adjustable functional generator. Microelectron. J. 2015, 46, 143–152. [Google Scholar] [CrossRef]

- Gift, S.J. Multiphase sinusoidal oscillator system using operational amplifiers. Int. J. Electron. 1997, 83, 61–68. [Google Scholar] [CrossRef]

- Gift, S.J.G. The application of all-pass filters in the design of multiphase sinusoidal systems. Microelectron. J. 2000, 31, 9–13. [Google Scholar] [CrossRef]

- Minhaj, N. Second-generation current conveyor-based even/odd multiphase sinusoidal oscillators. In Proceedings of the 2009 International Conference on Advances in Recent Technologies in Communication and Computing, Kottayam, India, 27–28 October 2009; pp. 231–235. [Google Scholar]

- Hou, C.L.; Shen, B. Second-generation current conveyor-based multiphase sinusoidal oscillators. Int. J. Electron. 1995, 78, 317–325. [Google Scholar] [CrossRef]

- Wu, D.S.; Liu, S.I.; Hwang, Y.S.; Wu, Y.P. Multiphase sinusoidal oscillator using second-generation current conveyors. Int. J. Electron. 1995, 78, 645–651. [Google Scholar] [CrossRef]

- Abuelmaatti, M.T.; Al-Qahtani, M.A. A new current-controlled multiphase sinusoidal oscillator using translinear current conveyors. IEEE Trans. Circuits Syst. II Analog Digit. Signal Process. 1998, 45, 881–885. [Google Scholar] [CrossRef]

- Vavra, J.; Bajer, J. Current-mode multiphase sinusoidal oscillator based on current differencing units. Analog Integr. Circuits Signal. Process. 2013, 74, 121–128. [Google Scholar] [CrossRef]

- Souliotis, G.; Psychalinos, C. Electronically controlled multiphase sinusoidal oscillators using current amplifiers. Int. J. Circuit Theory Appl. 2009, 37, 43–52. [Google Scholar] [CrossRef]

- Pandey, R.; Pandey, N.; Bothra, M.; Paul, S.K. Operational transresistance amplifier-based multiphase sinusoidal oscillators. J. Electr. Comput. Eng. 2011, 2011, 1–8. [Google Scholar] [CrossRef]

- Gupta, P.; Pandey, R. Dual Output Voltage Differencing Buffered Amplifier Based Active-C Multiphase Sinusoidal Oscillator. Int. J. Eng. 2021, 34, 1438–1444. [Google Scholar]

- Gift, S.J.; Maundy, B. An improved multiphase sinusoidal oscillator using current feedback amplifiers. Int. J. Electron. Lett. 2016, 4, 177–187. [Google Scholar] [CrossRef]

- Tangsrirat, W.; Tanjaroen, W.; Pukkalanun, T. Current-mode multiphase sinusoidal oscillator using CDTA-based allpass sections. AEU Int. J. Electron. Commun. 2009, 63, 616–622. [Google Scholar] [CrossRef]

- Jaikla, W.; Siripruchyanun, M.; Biolek, D.; Biolkova, V. High-output-impedance current-mode multiphase sinusoidal oscillator employing current differencing transconductance amplifier-based allpass filters. Int. J. Electron. 2010, 97, 811–826. [Google Scholar] [CrossRef]

- Pisitchalermpong, S.; Tangsrirat, W.; Surakampontorn, W. CDBA-based multiphase sinusoidal oscillator using grounded capacitors. In Proceedings of the 2006 SICE-ICASE International Joint Conference, Busan, Korea, 18–21 October 2006; pp. 5762–5765. [Google Scholar]

- Tuntrakool, S.; Kumngern, M.; Jaikla, W. VDDDAs-based voltage-mode multiphase sinusoidal oscillator. In Proceedings of the International Conference on Industrial Application Engineering, Beppu, Japan, 26–30 March 2016; pp. 105–108. [Google Scholar]

- Jaikla, W.; Prommee, P. Electronically tunable current-mode multiphase sinusoidal oscillator employing CCCDTA-based allpass filters with only grounded passive elements. Radioengineering 2011, 20, 594–599. [Google Scholar]

- Wu, D.S.; Liu, S.I.; Hwang, Y.S.; Wu, Y.P. Multiphase sinusoidal oscillator using the CFOA pole. IEE Proc.-Circuits Devices Syst. 1995, 142, 37–40. [Google Scholar] [CrossRef]

- Kaçar, F.; Yeşil, A.; Minaei, S.; Kuntman, H. Positive/negative lossy/lossless grounded inductance simulators employing single VDCC and only two passive elements. AEU Int. J. Electron. Commun. 2014, 68, 73–78. [Google Scholar] [CrossRef]

- 3WK16341. Optocouplers with a Photoresistor. Available online: http://www.tesla-blatna.cz/_soubory/optocoupler-optron.pdf (accessed on 25 September 2022).

- Bajer, J.; Lahiri, A.; Biolek, D. Current-Mode CCII plus Based Oscillator Circuits using a Conventional and a Modified Wien-Bridge with All Capacitors Grounded. Radioengineering 2011, 20, 245–251. [Google Scholar]

- Biolkova, V.; Bajer, J.; Biolek, D. Four-Phase Oscillators Employing Two Active Elements. Radioengineering 2011, 20, 334–339. [Google Scholar]

- Wang, Z. 2-MOSFET transresistor with extremely low distortion for output reaching supply voltages. Electron. Lett. 1990, 13, 951–952. [Google Scholar] [CrossRef]

- Kaplan, B.; Kottick, D. Use of a Three-Phase Oscillator Model for the Compact Representation of Synchronous Generators. IEEE Trans. Magn. 1983, 19, 1480–1486. [Google Scholar] [CrossRef]

| Ref | Design Technique | ABBs | No. of Active Element per Phase | Additional Amplifier | Grounded C only | No. of R + C per Phase | Electronic Control of FO/ Simulated FO | FO and CO Independently Adjustable/Percent Error of Simulated FO | Mode of Output (CM/VM)/Simulated THD Output | Technology Used/Experiment |

|---|---|---|---|---|---|---|---|---|---|---|

| [20] | Lossy integrator | OPA | 1 | Yes | Yes | 3 + 1 | No/NA | Yes/NA | VM/NA | HA2544/Yes |

| [21] | All pass | OPA | 1 | Yes | Yes | 3 + 1 | No/NA | Yes/NA | VM/NA | LF351/Yes |

| [22] | Lossy integrator | CCII | 1 | No | Yes | 3 + 1 | No/NA | No/NA | VM/NA | 0.35 μm CMOS/No |

| [23] | Lossy integrator | CCII | 1 | Yes | Yes | 2 + 1 | No/NA | No/NA | VM/NA | AD844/Yes |

| [24] | Lossy integrator | CCII | 1 | No | Yes | 2 + 1 | No/NA | No/NA | VM/NA | AD844AN/Yes |

| [25] | Lossy integrator | CCCII | 1 | No | Yes | 0 + 2 | Yes/NA | Yes/NA | CM/NA | Bipolar PR200N and NR200N/No |

| [26] | All pass | CDU | 1 | Yes | Yes | 1 + 1 | No | Yes | CM | OPA860/No |

| [27] | Lossy integrator | CA | 1 | No | Yes | 0 + 1 | Yes/0.459 MHz | Yes/12.57% | CM/1.98% | AMS CMOS 0.35 μm/No |

| [28] | Lossy integrator | OTRA | 1 | Yes | No | 2 + 1 | No/2.838 MHz | No/2.93% | VM/NA | AD844AN/Yes |

| [29] | All pass | DO-VDBA | 1 | No | No | 0 + 1 | Yes/3.5 MHz | Yes/2.77% | VM/0.78% | 0.18 μm CMOS/No |

| [30] | Lossy integrator | CFA | 1 | No | * | 2 + 0 | No/NA | No/NA | VM/NA | AD844/Yes |

| [31] | All pass | CDTA | 2 | Yes | No | 0 + 1 | Yes/180 kHz | Yes/1.64% | CM/1.4% | Bipolar PR100N and NP100N/No |

| [32] | All pass | CDTA | 1 | No | No | 2 + 1 | No/375 kHz | No/6.25% | CM/1.032% | Bipolar PR200N and NR200N/No |

| [33] | Lossy integrator | CDBA | 1 | Yes | Yes | 2 + 1 | No/26.76 kHz | No/N/A | VM/N/A | AD844/No |

| [34] | Lossy integrator | VDDDA | 1 | No | Yes | 2 + 1 | Yes/2.5 MHz | Yes/NA | VM/0.87%, 0.86% 0.78% | TSMC CMOS technology (level 7)/No |

| [35] | All pass | CCCDTA | 1 | No | Yes | 1 + 1 | Yes/1.033 MHz | Yes/NA | CM/0.519% | 0.25 μm TSMC CMOS technology/No |

| [36] | Lossy integrator | CFOA | 1 | No | * | 2 + 0 | No/NA | No/NA | VM/NA | AD844/Yes |

| Proposed MSO | Lossy integrator | VDCC | 1 | No | Yes | 2 + 1 | Yes/1.43 MHz | Yes/7.74% | CM/1.22%, 1.18%, 0.57% | 0.18 µm TSMC CMOS technology and AD844, LT1228/Yes |

| Component | W/L [µm/µm] |

|---|---|

| M1–M4 | 3.6/1.8 |

| M5–M6 | 7.2/1.8 |

| M7–M8 | 2.4/1.8 |

| M9–M10 | 3.06/0.72 |

| M11–M12 | 9/0.72 |

| M13–M17 | 14.4/0.72 |

| M18–M22 | 0.72/0.72 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Pitaksuttayaprot, K.; Phanrattanachai, K.; Jaikla, W. Electronically Adjustable Multiphase Sinusoidal Oscillator with High-Output Impedance at Output Current Nodes Using VDCCs. Electronics 2022, 11, 3227. https://doi.org/10.3390/electronics11193227

Pitaksuttayaprot K, Phanrattanachai K, Jaikla W. Electronically Adjustable Multiphase Sinusoidal Oscillator with High-Output Impedance at Output Current Nodes Using VDCCs. Electronics. 2022; 11(19):3227. https://doi.org/10.3390/electronics11193227

Chicago/Turabian StylePitaksuttayaprot, Koson, Kritphon Phanrattanachai, and Winai Jaikla. 2022. "Electronically Adjustable Multiphase Sinusoidal Oscillator with High-Output Impedance at Output Current Nodes Using VDCCs" Electronics 11, no. 19: 3227. https://doi.org/10.3390/electronics11193227