AMROFloor: An Efficient Aging Mitigation and Resource Optimization Floorplanner for Virtual Coarse-Grained Runtime Reconfigurable FPGAs

Abstract

1. Introduction

- It is the first time to achieve aging mitigation and resource optimization for Virtual Coarse-Grained Runtime Reconfigurable Architecture (VCGRRA);

- A Maximize Reconfigurable Regions Algorithm (MRRA) is proposed to quickly determine the number and size of RRs that are most conducive to aging mitigation, which improves the convergence rate of the algorithm and ensures a better layout solution;

- A Resource Combination Algorithm (RCA) is proposed to further optimize the resources of the layout planning that has achieved aging mitigation;

- Experimental results show that the AMROFloor method can extend the Mean Time to Failure (MTTF) of FPGAs by 13.8% and optimize the resource overhead by 19.2% on average.

2. Related Work

3. Preliminary

3.1. VCGRRA

3.2. DAG Task Model

3.3. Task_Stress/RR_MTTF Evaluation

4. Aging Mitigation Floorplanner Based on GA

4.1. Problem Description

4.2. Objective and Constraints

4.3. Number and Size of RRs

| Algorithm 1: MRRA |

| Input: Task_R; NT: Number of Tasks; Output: RR_R; NRR: Number of RRs; NPE: Number of PEs; R: All resources on-chip (1) /* Quantify the resources in terms of the number of PEs */ (2) Quantification Task_R → NPE; R → NPE; (3) /* Initialize the number of RRs to the number of tasks */ (4) Initialization NRR → NT; (5) /* Initialize the resources of each RR_R to Task_R */ (6) Initialization RR_R → Task_R; (7) /* Determine the number of RRs and the amount of resources for each RR */ (8) If R ≥ sum (RR_R) then (9) Output RR_R; NRR; (10) breaks; (11) else (12) sorting RR_R by descending order; (13) while (NRR > 1) (14) combine the two RRs with the smallest RR_R in the sort into the larger one; (15) NRR = NRR -1; (16) If R ≥ sum (RR_R) then (17) Output RR_R; NRR; (18) breaks; (19) end (20) end (21) Output RR_R = R; NRR = 1; (22) end |

5. Resource Combination Algorithm

| Algorithm 2: RCA |

| Input: Initial Floorplanning Solution (I_FS); Output: Resource Optimization Floorplanning Solution (RO_FS); RR_MS: the RR with max stress in the IFS; NRR: Number of Initial RRs; (1) Initialization list to store the number and resource of RRs; (2) Initialization list to store the RR_Exec of each RR; (3) Initialization list to sore RR_Stress of each RR; (4) /* Step1: Merger any two RRs into the larger one */ (5) Max(, ) → ; _Exec + _Exec → _Exec; (i, j ∈ , γ) (6) /* Step2: Calculate the RR_Stress after the merger and sort them by descending */ (7) Calculate(_Stress); Sort(_Stress) →δ; (8) /* Step3: Compare stress differences and check if constraints are met after merging */ (9) r = 0; (10) while (r < .length) (11) If RR_MS - _Stress[r] > 0 then (12) check constrains (return Boolean); (13) If True then (14) update , ; (15) jump to the step1; (16) else (17) r = r + 1; (18) end (19) else (20) r = r + 1; (21) end (22) end (23) /* Step4: Determine if and have been updated */ (24) If .size == NRR then (25) Output I_FS; (26) else (27) Output RO_FS; (28) end |

6. Experiments and Results

6.1. Experiment Setup

- Hom_MS: The layout solution with homogeneous RRs aims at minimizing the makespan of the tasks;

- Het_MS: The layout solution with heterogeneous RRs aims at minimizing the makespan of the tasks;

- Hom_AM: The layout solution with homogeneous RRs aims at aging mitigation;

- Het_AM: The layout solution with heterogeneous RRs aims at aging mitigation;

- RL: Random layout solution.

6.2. Evaluation Metrics

6.3. Results and Analysis

6.3.1. MTTF

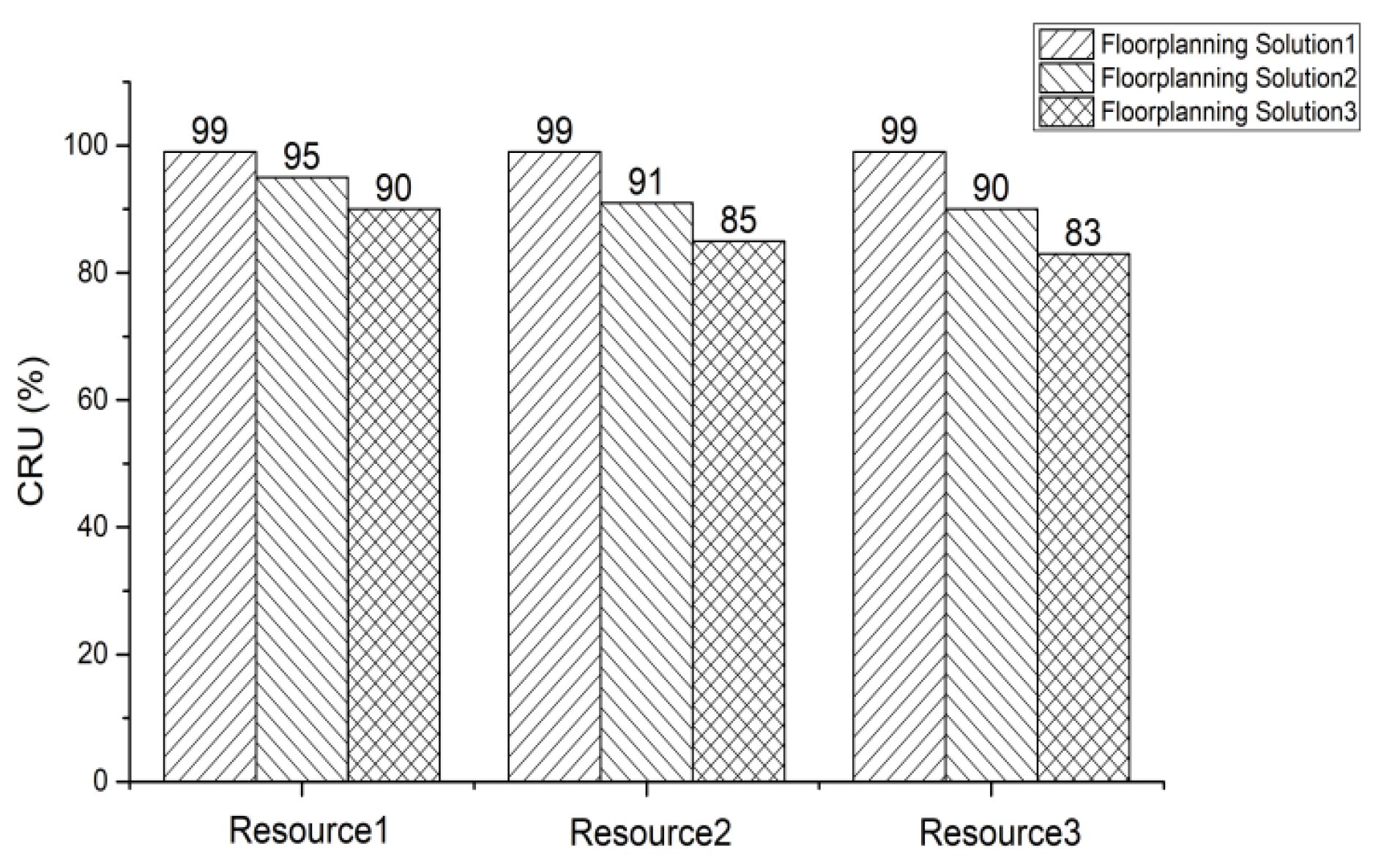

6.3.2. CRU

6.3.3. Solution Efficiency

6.4. Case Analysis

7. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Shokry, B.; Mahmoud, D.G.; Amer, H.H.; Shatta, M.; Alkady, G.I.; Daoud, R.M.; Adly, I.; Shaker, M.N.; Refaat, T. Work-in-Progress: Triple Event Upset Tolerant Area-Efficient FPGA-Based System for Space Applications and Nuclear Plants. In Proceedings of the 16th IEEE International Conference on Factory Communication Systems (WFCS), Porto, Portugal, 27–29 April 2020; pp. 1–4. [Google Scholar]

- Giordano, R.; Perrella, S.; Barbieri, D.; Izzo, V. A Radiation-Tolerant, Multigigabit Serial Link Based on FPGAs. IEEE Trans. Nucl. Sci. 2020, 67, 1852–1860. [Google Scholar] [CrossRef]

- Fang, Z.; Yang, C.; Jin, H.; Lou, L.; Tang, K.; Tang, X.; Guo, T.; Wang, W.; Zheng, Y. A Digital-Enhanced Chip-Scale Photoacoustic Sensor System for Blood Core Temperature Monitoring and In Vivo Imaging. IEEE Trans. Biomed. Circuits Syst. 2020, 13, 1405–1416. [Google Scholar] [CrossRef] [PubMed]

- Zhen, W.; Jianhui, J.; Naijin, C.; Guangming, L.; Ying, Z. Effects of three factors under BTI on the soft error rate of integrated circuits. J. Comput. Res. Dev. 2018, 55, 1108–1116. [Google Scholar]

- Zhang, H.; Kochte, M.A.; Schneider, E.; Bauer, L.; Wunderlich, H.J.; Henkel, J. STRAP: Stress-aware placement for aging mitigation in runtime reconfigurable architectures. In Proceedings of the IEEE/ACM International Conference on ComputerAided Design (ICCAD), Austin, TX, USA, 2–6 November 2015; pp. 38–45. [Google Scholar]

- Zhang, H.; Bauer, L.; Kochte, M.A.; Schneider, E.; Wunderlich, H.J.; Henkel, J. Aging resilience and fault tolerance in runtime reconfigurable architectures. IEEE Trans. Comput. 2017, 66, 957–970. [Google Scholar] [CrossRef]

- Sahoo, S.S.; Nguyen, T.D.; Veeravalli, B.; Kumar, A. Lifetime-aware design methodology for dynamic partially reconfigurable systems. In Proceedings of the 23rd Asia and South Pacific Design Automation Conference (ASP-DAC), Jeju, Korea, 22–25 January 2018; pp. 393–398. [Google Scholar]

- Sahoo, S.S.; Nguyen, T.D.; Veeravalli, B.; Kumar, A. Multi-objective design space exploration for system partitioning of FPGA-based Dynamic Partially Reconfigurable Systems. Integration 2019, 67, 95–107. [Google Scholar] [CrossRef]

- Kourfali, A.; Stroobandt, D. In-circuit fault tolerance for FPGAs using dynamic reconfiguration and virtual overlays. Microelectron. Reliab. 2019, 102, 113438–113452. [Google Scholar] [CrossRef]

- Fricke, F.; Werner, A.; Shahin, K.; Huebner, M. CGRA tool flow for fast run-time reconfiguration. In Proceedings of the ARC 2018: Applied Reconfigurable Computing, Architectures, Tools, and Applications, Santorini, Greece, 2–4 May 2018; Springer International Publishing: Cham, Switzerland, 2018; pp. 661–672. [Google Scholar]

- Coole, J.; Stitt, G. Intermediate fabrics: Virtual architectures for circuit portability and fast placement and routing. In Proceedings of the 8th IEEE/ACM/IFIP International Conference on Hardware/Software Codesign and System Synthesis (CODES+ISSS), New York, NY, USA, 24–29 October 2010; pp. 13–22. [Google Scholar]

- Stott, E.A.; Wong, J.S.; Sedcole, P.; Cheung, P.Y. Degradation in FPGAs: Measurement and modelling. In Proceedings of the 18th Annual ACM/SIGDA International Symposium on Field Programmable Gate Arrays, New York, NY, USA, 21–23 February 2010; pp. 229–238. [Google Scholar]

- Ahmed, I.; Zhao, S.; Meijers, J.; Trescases, O.; Betz, V. Automatic bram testing for robust dynamic voltage scaling for fpgas. In Proceedings of the 28th International Conference on Field Programmable Logic and Applications (FPL), Dublin, Ireland, 27–31 August 2018; pp. 681–687. [Google Scholar]

- Xilinx Inc. Vivado Design SuiteUserGuide: Partial Reconfiguration. Available online: https://china.xilinx.com/support/documentation/sw_manuals/xilinx2019/ug909vivadopartialreconfiguration.pdf (accessed on 20 May 2021).

- Khaleghi, B.; Omidi, B.; Amrouch, H.; Henkel, J.; Asadi, H. Estimating and Mitigating Aging Effects in Routing Network of FPGAs. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2019, 27, 651–664. [Google Scholar] [CrossRef]

- Zhang, H.; Bauer, L.; Kochte, M.A.; Schneider, E.; Braun, C.; Imhof, M.E.; Wunderlich, H.J.; Henkel, J. Module diversification: Fault tolerance and aging mitigation for runtime reconfigurable architectures. In Proceedings of the IEEE International Test Conference (ITC), Anaheim, CA, USA, 6–13 September 2013; pp. 1–10. [Google Scholar]

- Ghaderi, Z.; Bozorgzadeh, E. Aging-aware high-level physical planning for reconfigurable systems. In Proceedings of the 21st IEEE Asia and South Pacific Design Automation Conference (ASP-DAC), Macao, China, 25–28 January 2016; pp. 631–636. [Google Scholar]

- Srinivasan, S.; Krishnan, R.; Mangalagiri, P.; Xie, Y.; Narayanan, V.; Irwin, M.J.; Sarpatwari, K. Toward increasing FPGA lifetime. IEEE Trans. Dependable Secur. Comput. 2008, 5, 115–127. [Google Scholar] [CrossRef]

- Gu, J.; Yin, S.; Wei, S. Stress-aware loops mapping on cgras with considering nbti aging effect. In Proceedings of the 54th ACM/IEEE Design Automation Conference (DAC), Austin, TX, USA, 18–22 June 2017; pp. 1–6. [Google Scholar]

- Afzali-Kusha, H.; Akbari, O.; Kamal, M.; Pedram, M. Energy and reliability improvement of voltage-based, clustered, coarse-grain reconfigurable architectures by employing quality-aware mapping. IEEE J. Emerg. Sel. Top. Circuits Syst. 2018, 8, 480–493. [Google Scholar] [CrossRef]

- Hu, B.; Shihab, M.; Makris, Y.; Schaefer, B.C.; Sechen, C. An efficient MILP-based aging-aware floorplanner for multicontext coarse-grained runtime reconfigurable FPGAs. In Proceedings of the 2002 Design, Automation & Test in Europe Conference & Exhibition (DATE), Grenoble, France, 9–13 March 2020; pp. 1526–1531. [Google Scholar]

- Kourfali, A.; Kulkarni, A.; Stroobandt, D. SICTA: A superimposed in-circuit fault tolerant architecture for SRAM-based FPGAs. Proceedings of IEEE 23rd International Symposium on On-Line Testing and Robust System Design (IOLTS), Thessaloniki, Greece, 3–5 July 2017; pp. 5–8. [Google Scholar]

- Koch, D.; Beckhoff, C.; Lemieux, G.G.F. An efficient FPGA overlay for portable custom instruction set extensions. In Proceedings of the 23rd International Conference on Field programmable Logic and Applications (FPL), Porto, Portugal, 2–4 September 2013; pp. 1–8. [Google Scholar]

- Quraishi, M.H.; Tavakoli, E.B.; Ren, F. A Survey of System Architectures and Techniques for FPGA Virtualization. IEEE Trans. Parallel Distrib. Syst. 2021, 9, 2216–2230. [Google Scholar] [CrossRef]

- Grant, D.; Wang, C.; Lemieux, G.G. A CAD framework for Malibu: An FPGA with time multiplexed coarse-grained elements. In Proceedings of the 19th ACM/SIGDA International Symposium on Field Programmable Gate Arrays, New York, NY, USA, 27 February–1 March 2011; pp. 123–132. [Google Scholar]

- Heyse, K.; Davidson, T.; Vansteenkiste, E.; Bruneel, K.; Stroobandt, D. Efficient implementation of Virtual Coarse Grained Reconfigurable Arrays on FPGAs. In Proceedings of the 23rd International Conference on Field programmable Logic and Applications, Porto, Portugal, 2–4 September 2013; pp. 1–8. [Google Scholar]

- Xiang, Y.; Chantem, T.; Dick, R.P.; Hu, X.S.; Shang, L. System-level reliability modeling for MPSoCs. In Proceedings of the 8th IEEE/ACM/IFIP International Conference on Hardware/Software Codesign and System Synthesis (CODES+ISSS), Scottsdale, AZ, USA, 24–29 October 2010; pp. 297–306. [Google Scholar]

- Hara, Y.; Tomiyama, H.; Honda, S.; Takada, H. Proposal and Quantitative Analysis of the CHStone Benchmark Program Suite for Practical C-based High-level Synthesis. J. Inf. Process. 2009, 17, 242–254. [Google Scholar] [CrossRef][Green Version]

- OpenCores. Available online: https://www.opencores.org (accessed on 8 June 2021).

- Xilinx. Intellectual Property. Available online: https://www.xilinx.com/products/intellectualproperty.html (accessed on 23 May 2021).

- Dick, R.P.; Rhodes, D.L.; Wolf, W. TGFF: Task graphs for free. In Proceedings of the Sixth International Workshop on Hardware/Software Codesign, Seattle, WA, USA, 18 March 1998; pp. 97–101. [Google Scholar]

| Parameter | Description |

|---|---|

| Number of RRs | |

| RR_R | Resources included in the RR |

| RR_MTTF | Expected MTTF of RR |

| RR_Stress | Accumulated stress on RR |

| RR_Exec | Queue of tasks executed on RR |

| Parameter | Description |

|---|---|

| Number of tasks | |

| Task_R | Resource used for task implementation |

| Task_MTTF | Expected MTTF of task |

| Task_Stress | Expected stress of task |

| Task_S | Start time of task |

| Task_E | Execution time of task |

| Task_D | Deadline of task |

| Task | Number | PE | Task_Stress |

|---|---|---|---|

| T1 | 0 | 79 | 3 |

| T2 | 1 | 192 | 1.8 |

| T3 | 2 | 534 | 5 |

| T4 | 3 | 1011 | 1.1 |

| T5 | 4 | 87 | 1.2 |

| T6 | 5 | 3089 | 5 |

| T7 | 6 | 1526 | 0.3 |

| T8 | 7 | 787 | 2.6 |

| … | … | … | … |

| Method | Heterogeneous | Homogeneous | Aging Mitigation | Resource Optimization |

|---|---|---|---|---|

| Hom_MS | ✓ | |||

| Het_MS | ✓ | |||

| Hom_AM | ✓ | ✓ | ||

| Het_AM | ✓ | ✓ | ||

| RL | ✓ | |||

| AMROFloor | ✓ | ✓ | ✓ |

| Scenes/Methods | Hom_AM (%) | Het_AM (%) | AMROFloor (%) | |

|---|---|---|---|---|

| TaskSet 1 | Resource 1 | 99 | 99 | 99 |

| Resource 2 | 95 | 89 | 81 | |

| Resource 3 | 90 | 77 | 69 | |

| TaskSet 2 | Resource 1 | 99 | 99 | 99 |

| Resource 2 | 94 | 82 | 70 | |

| Resource 3 | 85 | 61 | 50 | |

| TaskSet 3 | Resource 1 | 99 | 98 | 94 |

| Resource 2 | 90 | 70 | 53 | |

| Resource 3 | 83 | 56 | 41 | |

| Avg. | 93 | 81 | 73 | |

| Scenes/Methods | SGA (s) | MILP_DSE (s) | AMROFloor (s) | |

|---|---|---|---|---|

| TaskSet 1 | Resource 1 | 124.3 | 1153.2 | 46.3 |

| Resource 2 | 175.4 | 1899.8 | 68.6 | |

| Resource 3 | 354.2 | 2386.1 | 116.3 | |

| TaskSet 2 | Resource 1 | 133.9 | 1156.7 | 47.1 |

| Resource 2 | 197.7 | 1801.3 | 68.2 | |

| Resource 3 | 312.1 | 2385.7 | 106.4 | |

| TaskSet 3 | Resource 1 | 116.8 | 1158.2 | 56.2 |

| Resource 2 | 203.5 | 1800.4 | 77.9 | |

| Resource 3 | 308.2 | 2382.1 | 119.3 | |

| Avg. | 214.0 | 1791.5 | 78.5 | |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Li, Z.; Huang, Z.; Wang, Q.; Wang, J. AMROFloor: An Efficient Aging Mitigation and Resource Optimization Floorplanner for Virtual Coarse-Grained Runtime Reconfigurable FPGAs. Electronics 2022, 11, 273. https://doi.org/10.3390/electronics11020273

Li Z, Huang Z, Wang Q, Wang J. AMROFloor: An Efficient Aging Mitigation and Resource Optimization Floorplanner for Virtual Coarse-Grained Runtime Reconfigurable FPGAs. Electronics. 2022; 11(2):273. https://doi.org/10.3390/electronics11020273

Chicago/Turabian StyleLi, Zeyu, Zhao Huang, Quan Wang, and Junjie Wang. 2022. "AMROFloor: An Efficient Aging Mitigation and Resource Optimization Floorplanner for Virtual Coarse-Grained Runtime Reconfigurable FPGAs" Electronics 11, no. 2: 273. https://doi.org/10.3390/electronics11020273

APA StyleLi, Z., Huang, Z., Wang, Q., & Wang, J. (2022). AMROFloor: An Efficient Aging Mitigation and Resource Optimization Floorplanner for Virtual Coarse-Grained Runtime Reconfigurable FPGAs. Electronics, 11(2), 273. https://doi.org/10.3390/electronics11020273