Timing Analysis and Optimization Method with Interdependent Flip-Flop Timing Model for Near-Threshold Design

Abstract

:1. Introduction

- In order to cope with the nonlinear relation and wide effective coverage of interdependency between the setup–hold time and clock-to-q delay for flip-flops in the NTV domain, the interdependent clock-to-q delay of the flip-flop is predicted by the ANN model, whose training data are generated by SPICE simulation in a restricted hexagonal area in the two-dimensional setup-hold time space, leading to high prediction accuracy and low simulation cost.

- By integrating the ANN-based interdependent timing model into STA flow, an iterative circuit optimization method is proposed to minimize the clock period without any timing violations by balancing the timing slacks among iteratively selected paths, where Genetic Algorithm (GA) is employed to find the optimal setup time and hold time for each flip-flop in the selected paths.

2. Background

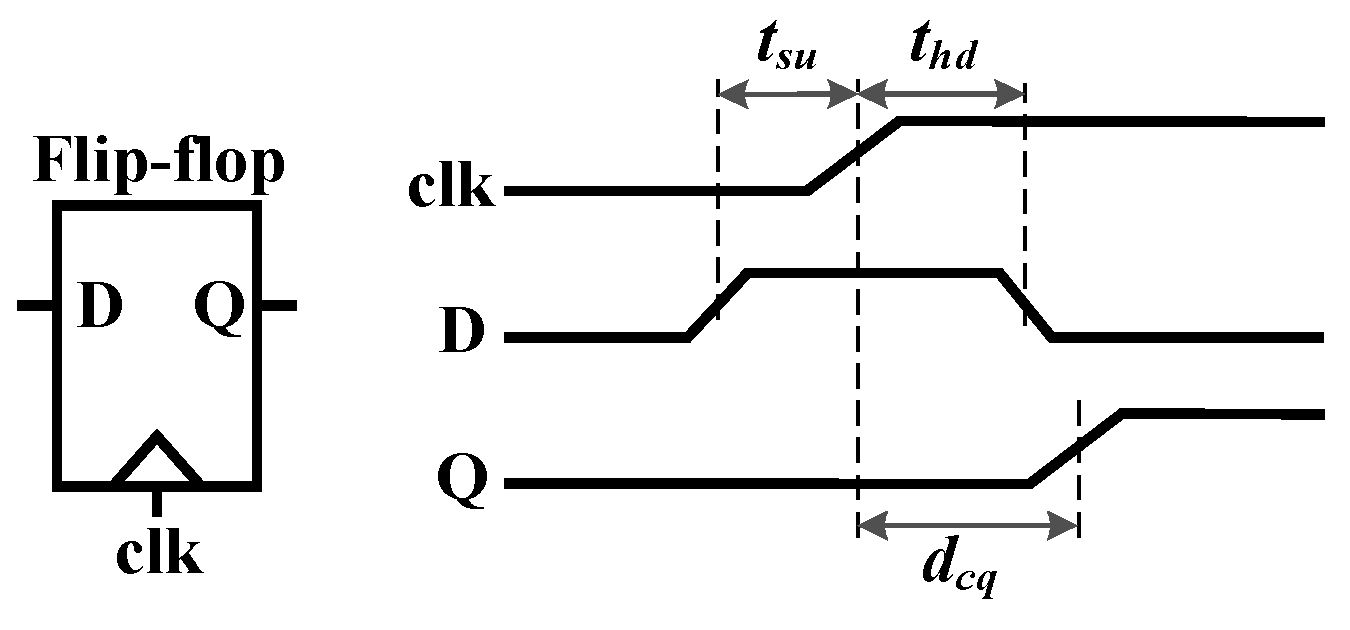

2.1. Traditional Timing Model for Flip-Flop

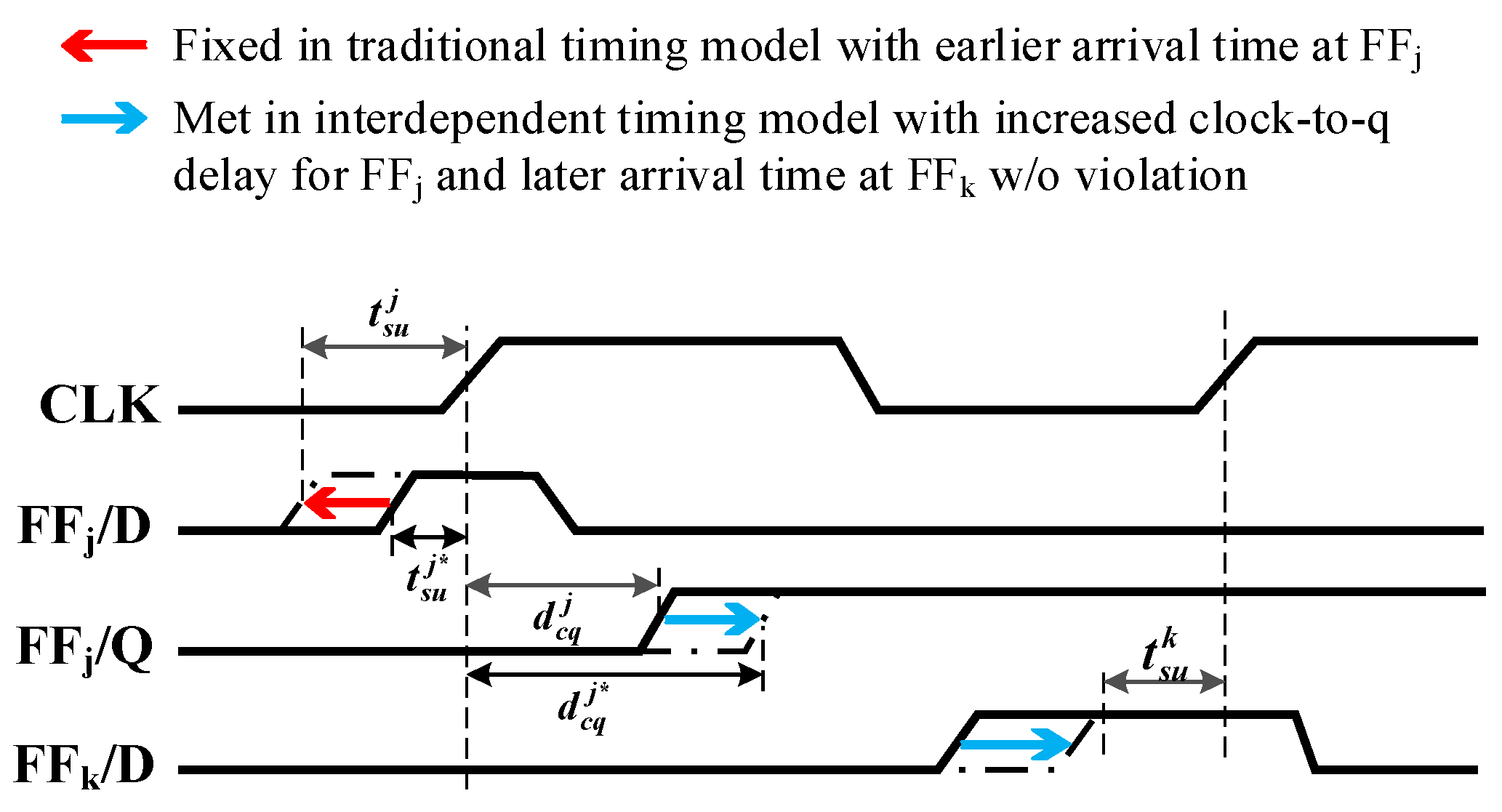

2.2. Interdependent Timing Model for Flip-Flop

3. Interdependent Timing Model Characterized by ANN

3.1. Selection of Effective Coverage

3.2. ANN-Based Prediction Model

4. Timing Optimization Method with Interdependent Timing Model

4.1. Formulation of Timing Optimization Problem

4.2. Iterative Optimization Method

| Algorithm 1. GA optimization |

|

5. Experimental Results and Discussion

5.1. Experimental Setup

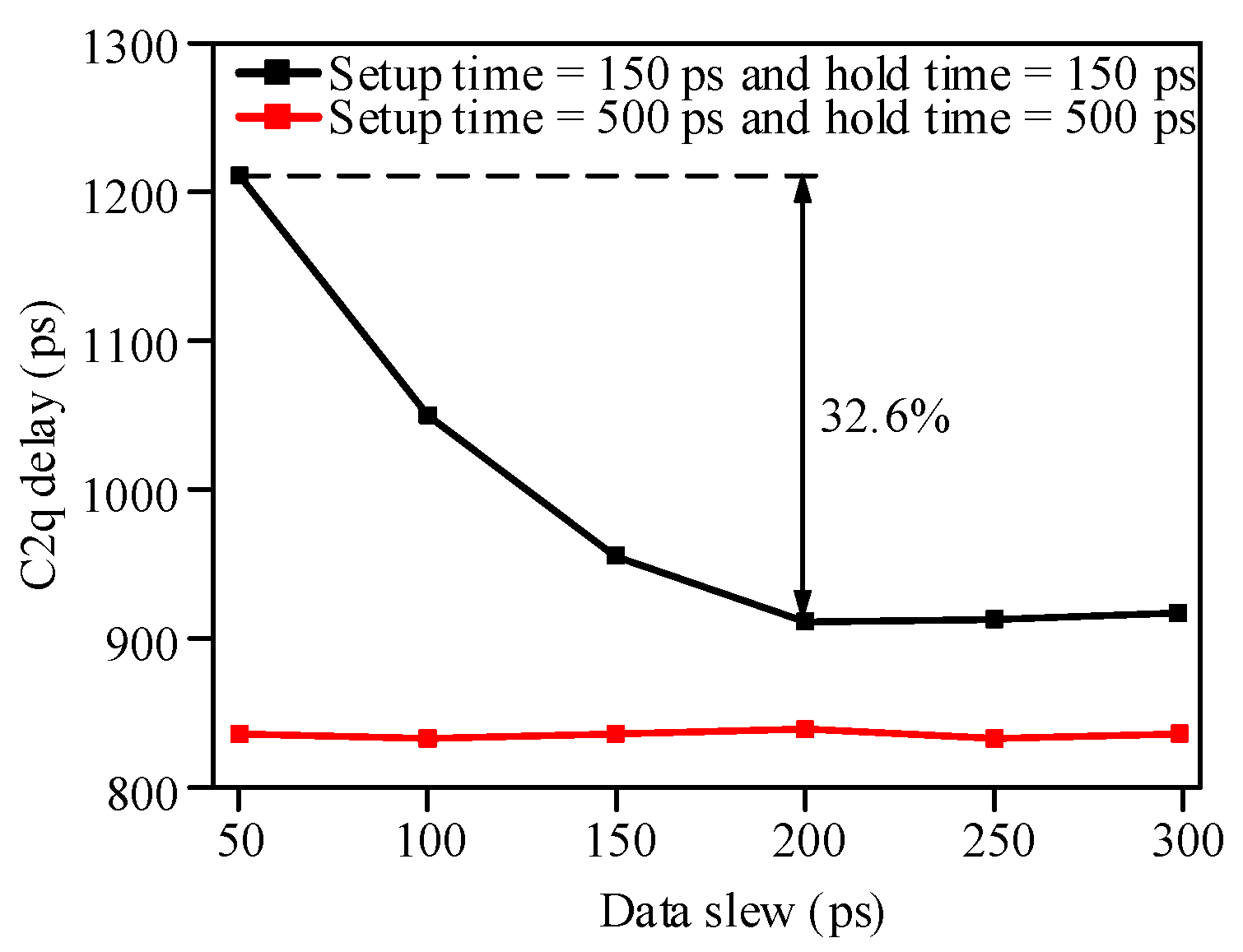

5.2. Prediction Accuracy Validation of ANN-Based Interdependent Model

5.3. Performance Improvement Validation of Iterative Timing Optimization Method

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Zhang, G.L.; Li, B.; Shi, Y.; Hu, J.; Schlichtmann, U. EffiTest2: Efficient Delay Test and Prediction for Post-Silicon Clock Skew Configuration Under Process Variations in IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems. IEEE Trans. Comput. Des. Integr. Circuits Syst. 2019, 38, 705–718. [Google Scholar] [CrossRef]

- Agni, S.K.B.; Jayagowri, R. Gate Matching Algorithm for Early False Path Detection in Statistical Static Timing Analysis. In Proceedings of the 2022 IEEE International Conference on Signal Processing, Informatics, Communication and Energy Systems (SPICES), Trivandrum, India, 10–12 March 2022; pp. 543–548. [Google Scholar] [CrossRef]

- Saurab, B.; Chavan, A.P. Design and Optimization of Timing Errors on Swapping of Threshold Voltage. In Proceedings of the 2021 IEEE Mysore Sub Section International Conference (MysuruCon), Hassan, India, 24–25 October 2021; pp. 687–691. [Google Scholar] [CrossRef]

- Kaul, H.; Anders, M.; Hsu, S.; Agarwal, A.; Krishnamurthy, R.; Borkar, S. Near-threshold voltage (NTV) design: Opportunities and challenges. In Proceedings of the 49th Annual Design Automation Conference (DAC ‘12), San Francisco, CA, USA, 3 June 2012; Association for Computing Machinery: New York, NY, USA, 2012; pp. 1153–1158. [Google Scholar] [CrossRef]

- Gautschi, M.; Schiavone, P.D.; Traber, A.; Loi, I.; Pullini, A.; Rossi, D.; Flamand, E.; Gurkaynak, F.K.; Benini, L. Near-Threshold RISC-V Core with DSP Extensions for Scalable IoT Endpoint Devices in IEEE Transactions on Very Large Scale Integration (VLSI) Systems. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2017, 25, 2700–2713. [Google Scholar] [CrossRef] [Green Version]

- Heo, J.; Jeong, K.; Choi, J.Y.; Kim, T.; Choi, K. Hardware Performance Monitoring Methodology at Near-Threshold Computing and Advanced Technology Nodes: From Design to Postsilicon in IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems. IEEE Trans. Comput. Des. Integr. Circuits Syst. 2022, 41, 1929–1942. [Google Scholar] [CrossRef]

- Keller, S.; Harris, D.M.; Martin, A.J. A Compact Transregional Model for Digital CMOS Circuits Operating Near Threshold. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2014, 22, 2041–2053. [Google Scholar] [CrossRef]

- Shiomi, J.; Ishihara, T.; Onodera, H. Microarchitectural-level statistical timing models for near-threshold circuit design. In Proceedings of the 20th Asia and South Pacific Design Automation Conference, Tokyo, Japan, 19–22 January 2015; pp. 87–93. [Google Scholar] [CrossRef]

- Golanbari, M.S.; Kiamehr, S.; Tahoori, M.B. Hold-time violation analysis and fixing in near-threshold region. In Proceedings of the 26th International Workshop on Power and Timing Modeling, Optimization and Simulation (PATMOS), Bremen, Germany, 21–23 September 2016; pp. 50–55. [Google Scholar] [CrossRef]

- Kanng, A.B.; Lee, H. Timing margin recovery with flexible flip-flop timing model. In Proceedings of the fifteenth International Symposium on Quality Electronic Design, Santa Clara, CA, USA, 3–5 March 2014; pp. 496–503. [Google Scholar] [CrossRef]

- Yang, Y.; Tam, K.H.; Jiang, I.H. Criticality-dependency-aware timing characterization and analysis. In Proceedings of the 52nd Annual Design Automation Conference (DAC ‘15), San Francisco, CA, USA, 7–11 June 2015; Association for Computing Machinery: San Francisco, CA, USA, 2015. [Google Scholar] [CrossRef]

- Saurabh, S.; Shah, H.; Singh, S. Timing Closure Problem: Review of Challenges at Advanced Process Nodes and Solutions. IETE Tech. Rev. 2019, 36, 580–593. [Google Scholar] [CrossRef]

- Balef, H.A.; Jiao, H.; de Gyvez, J.P.; Goossens, K. An analytical model for interdependent setup/hold-time characterization of flip-flops. In Proceedings of the 2017 18th International Symposium on Quality Electronic Design (ISQED), Santa Clara, CA, USA, 14–15 March 2017; pp. 209–214. [Google Scholar] [CrossRef]

- Chen, N.; Li, B.; Schlichtmann, U. Iterative timing analysis based on nonlinear and interdependent flipflop modelling. IET Circuits Devices Syst. 2012, 6, 330–337. [Google Scholar] [CrossRef]

- Heo, J.; Kim, T. Timing Analysis and Optimization Based on Flexible Flip-Flop Timing Model. In Proceedings of the 2016 IEEE Computer Society Annual Symposium on VLSI (ISVLSI), Pittsburgh, PA, USA, 11–13 July 2016; pp. 42–46. [Google Scholar] [CrossRef]

- Heo, J.; Kim, T. Circuit Timing Analysis and Optimization under Flexible Flip-flop Timing Model. J. Semicond. Technol. Sci. 2017, 17, 862–877. [Google Scholar] [CrossRef]

- Zhang, G.L.; Li, B.; Schlichtmann, U. PieceTimer: A holistic timing analysis framework considering setup/hold time interdependency using a piecewise model. In Proceedings of the 2016 IEEE/ACM International Conference on Computer-Aided Design (ICCAD), Austin, TX, USA, 7–10 November 2016; pp. 1–8. [Google Scholar] [CrossRef] [Green Version]

- Li, B.; Hashimoto, M.; Schlichtmann, U. From process variations to reliability: A survey of timing of digital circuits in the nanometer era. IPSJ Trans. Syst. LSI Des. Methodol. 2018, 11, 2–15. [Google Scholar] [CrossRef] [Green Version]

- Cao, P.; Liu, Z.; Guo, J.; Pang, H.; Wu, J.; Yang, J. Accurate and Efficient Interdependent Timing Model for Flip-Flop in Wide Voltage Region. In Proceedings of the 2019 17th IEEE International New Circuits and Systems Conference (NEWCAS), Munich, Germany, 23–26 June 2019; pp. 1–4. [Google Scholar] [CrossRef]

- Agarwal, M.; Saurabh, S. An Efficient Timing Model of Flip-Flops Based on Artificial Neural Network. In Proceedings of the 2021 ACM/IEEE 3rd Workshop on Machine Learning for CAD (MLCAD), Raleigh, NC, USA, 30 August–3 September 2021; pp. 1–6. [Google Scholar] [CrossRef]

- Geatpy-The Genetic and Evolutionary Algorithm Toolbox for Python with High Performance. Available online: www.geatpy.com (accessed on 27 January 2022).

| Architecture | Number of Edges | MARE (%) | |

|---|---|---|---|

| Rise | Fall | ||

| (5,8,8,1) | 112 | 1.72 | 2.73 |

| (5,15,10,1) | 235 | 1.08 | 1.03 |

| (5,8,8,5,1) | 149 | 2.66 | 2.59 |

| (5,20,15,5,1) | 480 | 0.68 | 0.69 |

| (5,20,20,12,1) | 752 | 0.60 | 0.60 |

| (5,28,28,20,1) | 1504 | 0.33 | 0.27 |

| Circuit | Flip-Flop Number | Cell Number | Minimum T, ns | Comparison, % | |||

|---|---|---|---|---|---|---|---|

| STA | Ref. [15] | Ours | Ref. [15] | Ours | |||

| s27 | 3 | 15 | 5.40 | 5.38 | 5.22 | 0.37 | 3.32 |

| s382 | 21 | 179 | 5.87 | 5.85 | 5.77 | 0.34 | 1.70 |

| s1196 | 18 | 463 | 6.03 | 5.68 | 5.65 | 5.80 | 6.28 |

| s5378 | 179 | 1658 | 7.48 | 7.31 | 7.23 | 2.27 | 3.36 |

| s13207 | 638 | 3448 | 11.19 | 11.04 | 10.90 | 1.34 | 2.59 |

| s35932 | 1728 | 10308 | 8.21 | 7.99 | 7.87 | 2.68 | 4.10 |

| s38417 | 1636 | 11145 | 11.77 | 11.74 | 11.59 | 0.25 | 1.53 |

| s38584 | 1426 | 12102 | 10.74 | 10.58 | 10.46 | 1.49 | 2.60 |

| Average | 1.82 | 3.19 | |||||

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Cao, P.; Qin, Y.; Jiang, H. Timing Analysis and Optimization Method with Interdependent Flip-Flop Timing Model for Near-Threshold Design. Electronics 2022, 11, 3670. https://doi.org/10.3390/electronics11223670

Cao P, Qin Y, Jiang H. Timing Analysis and Optimization Method with Interdependent Flip-Flop Timing Model for Near-Threshold Design. Electronics. 2022; 11(22):3670. https://doi.org/10.3390/electronics11223670

Chicago/Turabian StyleCao, Peng, Yuan Qin, and Haiyang Jiang. 2022. "Timing Analysis and Optimization Method with Interdependent Flip-Flop Timing Model for Near-Threshold Design" Electronics 11, no. 22: 3670. https://doi.org/10.3390/electronics11223670