Regression Model-Based AMS Circuit Optimization Technique Utilizing Parameterized Operating Condition

Abstract

:1. Introduction

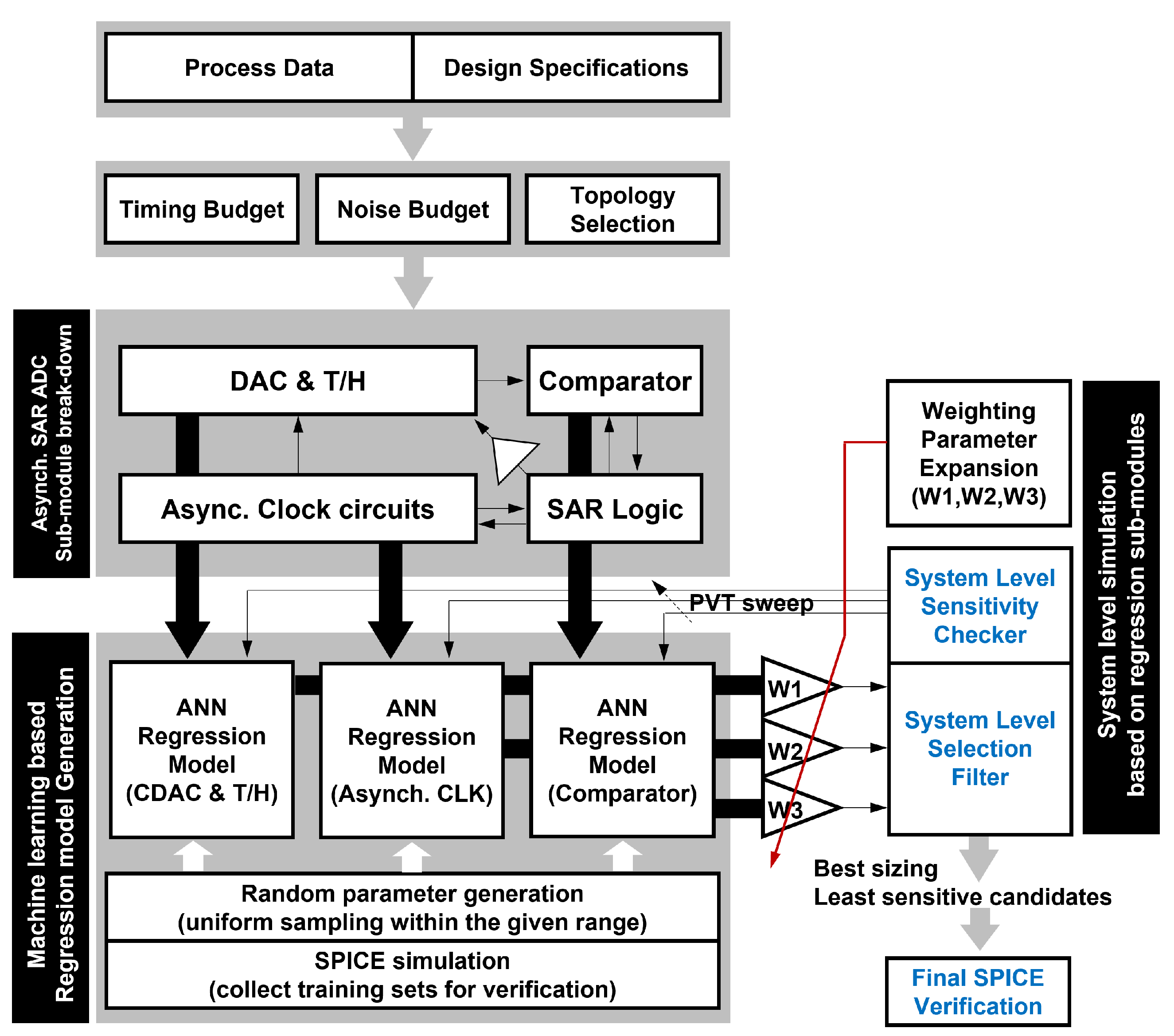

- We propose a new model-based design optimization technique that adaptively ensures the robust performance of AMS circuits and systems. Based on our prior research [22], we enhance the overall process by incorporating a sensitivity check step in order to offer customized operational environments as intended by the user.

- In practice, as there are demands to redesign circuits targeting different operating conditions with the same structure, this research contributes by greatly economizing the redesign effort while also increasing the production yield.

- We applied the overall design flow to an asynchronous SAR ADC architecture. The asynchronous SAR ADC design is suitable for verifying the performance of the AMS design algorithm because it is quite difficult to determine the optimal performance with respect to the key components of the ADC. Regarding the sensitivity performance, the design example covers the range of the supply voltage deviation of , the temperature from −40 C to 80 C, and the process with SS/TT/FF corners. Finally, the figure-of-merit, which indicates the ADC power efficiency, is compared with the results when applying the SPICE-based design method.

2. Methods

2.1. Step 1: Preparing a Library

2.2. Step 2: Creating Sub-Module with User Intent

2.3. Step 3: Evaluating Performance and Sensitivity

2.4. Step 4: Generating Final Netlist

3. Circuit Design

3.1. Topology Selection: Asynchronous SAR ADC

3.2. Step 1: Preparing a Library

3.3. Step 2: Creating Sub-Module with User Intent

3.3.1. Track-and-Hold Circuit

3.3.2. Comparator

3.3.3. SAR ADC Timing Controller

3.4. Step 3 and 4: Evaluating Performance and Sensitivity and Generating Final Netlist

4. Simulation Results

5. Discussion and Future Research Orientations

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- MacMillen, D.; Butts, M.; Camposano, R.; Hill, D.; Williams, T.W. An Industrial view of electronic design automation. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2000, 19, 1428–1448. [Google Scholar] [CrossRef] [Green Version]

- Jangkrajarng, N.; Bhattacharya, S.; Hartono, R.; Shi, C.-J. IPRAI—Intellectual property reuse-based analog IC layout automation. Integration 2003, 36, 237–262. [Google Scholar] [CrossRef]

- Jespers, P.G.A.; Murmann, B. Systematic Design of Analog CMOS Circuits; Cambridge University Press: Cambridge, UK, 2017. [Google Scholar]

- Berkcan, E.; D’Abreu, M. Physical assembly for analog compilation of high voltage ICs. In Proceedings of the IEEE 1988 Custom Integrated Circuits Conference, Rochester, NY, USA, 16–19 May 1988; pp. 14.3/1–14.3/7. [Google Scholar]

- Mendhurwar, K.; Sundani, H.; Aggarwal, P.; Raut, R.; Devabhaktuni, V. A new approach to sizing analog CMOS building blocks using pre-compiled neural network models. Analog Integr. Circuits Signal Process. 2012, 70, 265–281. [Google Scholar] [CrossRef]

- Nassif, S.R. Modeling and analysis of manufacturing variations. In Proceedings of the IEEE 2001 Custom Integrated Circuits Conference, San Diego, CA, USA, 9 May 2001. [Google Scholar]

- Felt, E.; Zanella, S.; Guardiani, C.; Sangiovanni-Vincentelli, A. Hierarchical statistical characterization of mixed-signal circuits using behavioral modeling. In Proceedings of the International Conference on Computer Aided Design, San Jose, CA, USA, 10–14 November 1996. [Google Scholar]

- Fraccaroli, E.; Lora, M.; Fummi, F. Automatic Generation of Analog/Mixed Signal Virtual Platforms for Smart Systems. IEEE Trans. Comput. 2020, 69, 1263–1278. [Google Scholar] [CrossRef]

- Duran, P.A. A Practical Guide to Analog Behavioral Modeling for IC System Design; Metzler, J.B., Ed.; Springer Science & Business Media: Berlin, Germany, 1998. [Google Scholar]

- Rocha, F.; Martins, R.; Lourenço, N.; Horta, N. Electronic Design Automation of Analog ICs Combining Gradient Models with Multi-Objective Evolutionary Algorithms; Springer Briefs in Applied Sciences and Technology; Springer International Publishing: Cham, Switzerland, 2014. [Google Scholar]

- Rutenbar, R.A.; Gielen, G.G.E.; Roychowdhury, J. Hierarchical Modeling, Optimization, and Synthesis for System-Level Analog and RF Designs. Proc. IEEE 2007, 95, 640–669. [Google Scholar] [CrossRef]

- Koh, H.Y.; Sequin, C.H.; Gray, P.R. OPASYN: A compiler for CMOS operational amplifiers. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 1990, 9, 113–125. [Google Scholar] [CrossRef]

- Harvey, J.P.; Elmasry, M.I.; Leung, B. STAIC: An interactive framework for synthesizing CMOS and BiCMOS analog circuits. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 1992, 11, 1402–1417. [Google Scholar] [CrossRef]

- Gielen, G.G.E.; Walscharts, H.C.C.; Sansen, W.M.C. Analog circuit design optimization based on symbolic simulation and simulated annealing. IEEE J. Solid-State Circuits 1990, 25, 707–713. [Google Scholar] [CrossRef]

- Swings, K.; Sansen, W. DONALD: A workbench for interactive design space exploration and sizing of analog circuits. In Proceedings of the European Conference on Design Automation, Amsterdam, The Netherlands, 25–28 February 1991; pp. 475–479. [Google Scholar]

- Kruiskamp, W.; Leenaerts, D. DARWIN: CMOS opamp synthesis by means of a genetic algorithm. In Proceedings of the Design Automation Conference, San Francisco, CA, USA, 12–16 June 1995; pp. 433–438. [Google Scholar]

- Hershenson, M.; Boyd, S.P.; Lee, T.H. GPCAD: A tool for CMOS op-amp synthesis. In Proceedings of the International Conference on Computer-Aided Design, Digest of Technical Papers of the IEEE/ACM, San Jose, CA, USA, 8–12 November 1998; pp. 296–303. [Google Scholar]

- Nye, W.; Riley, D.C.; Sangiovanni-Vincentelli, A.; Tits, T.L. DELIGHT.SPICE: An optimization based system for the design of integrated circuits. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 1988, 7, 501–519. [Google Scholar] [CrossRef]

- Phelps, R.; Krasnicki, M.; Rutenbar, R.A.; Carley, L.R.; Hellums, J.R. Anaconda: Simulation-based synthesis of analog circuits via stochastic pattern search. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2000, 19, 703–717. [Google Scholar] [CrossRef]

- Lourenço, N.; Horta, N. GENOM-POF: Multi-Objective evolutionary synthesis of analog ICs with corners validation. In Proceedings of the Fourteenth International Conference on Genetic and Evolutionary Computation Conference (GECCO’ 12), Philadelphia, PA, USA, 7–11 July 2012; pp. 1119–1126. [Google Scholar]

- Barros, M.; Guilherme, J.; Horta, N. GA-SVM optimization kernel applied to analog IC design automation. In Proceedings of the IEEE International Conference on Electronics, Nice, France, 10–13 December 2006; pp. 486–489. [Google Scholar]

- Nam, J.-W.; Lee, Y. Machine-Learning based Analog and Mixed-signal Circuit Design and Optimization. In Proceedings of the International Conference on Information Networking (ICOIN), Jeju Island, Korea, 12–15 January 2021; pp. 874–876. [Google Scholar]

- Van Engelen, J.E.; Hoos, H.H. A survey on semi-supervised learning. Mach. Learn. 2020, 109, 373–440. [Google Scholar] [CrossRef] [Green Version]

- Abiodun, O.I.; Jantan, A.; Omolara, A.E.; Dada, K.V.; Mohamed, N.A.; Arshad, H. State-of-the-art in artificial neural network applications: A survey. Heliyon 2018, 4, e00938. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Aizenberg, I.; Belardi, R.; Bindi, M.; Grasso, F.; Manetti, S.; Luchetta, A.; Piccirilli, M.C. A Neural Network Classifier with Multi-Valued Neurons for Analog Circuit Fault Diagnosis. Electronics 2021, 10, 349. [Google Scholar] [CrossRef]

- Wu, J.; Chen, X.Y.; Zhang, H.; Xiong, L.D.; Lei, H.; Deng, S.H. Hyperparameter optimization for machine learning models based on Bayesian optimization. J. Electron. Sci. Technol. 2019, 17, 26–40. [Google Scholar]

- Al-Saffar, A.A.M.; Tao, H.; Talab, M.A. Review of deep convolution neural network in image classification. In Proceedings of the International Conference on Radar, Antenna, Microwave, Electronics, and Telecommunications (ICRAMET), Jakarta, Indonesia, 23–24 October 2017; pp. 26–31. [Google Scholar]

- Bouwmans, T.; Javed, S.; Sultana, M.; Jung, S.K. Deep neural network concepts for background subtraction: A systematic review and comparative evaluation. Neural Netw. 2019, 117, 8–66. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Lau, M.M.; Lim, K.H. Review of Adaptive Activation Function in Deep Neural Network. In Proceedings of the IEEE-EMBS Conference on Biomedical Engineering and Sciences (IECBES), Sarawak, Malaysia, 3–6 December 2018; pp. 686–690. [Google Scholar]

- Zheng, J.; Lu, C.; Chen, D.; Guo, D. Improving the Generalization Ability of Deep Neural Networks for Cross-Domain Visual Recognition. IEEE Trans. Cogn. Dev. Syst. 2021, 13, 607–620. [Google Scholar] [CrossRef]

- Liu, J.; Hassanpourghadi, M.; Zhang, Q.; Su, S.; Chen, M.S.-W. Transfer Learning with Bayesian Optimization-Aided Sampling for Efficient AMS Circuit Modeling. In Proceedings of the IEEE/ACM International Conference on Computer-Aided Design (ICCAD), Virtual, 2–5 November 2020. [Google Scholar]

- Hao, C.; Chen, D. Software/Hardware Co-design for Multi-modal Multi-task Learning in Autonomous Systems. In Proceedings of the IEEE 3rd International Conference on Artificial Intelligence Circuits and Systems (AICAS), Washington, DC, USA, 6–9 June 2021; pp. 1–5. [Google Scholar]

| Input Parameter | Variable Range | Unit |

|---|---|---|

| Max[input signal frequency] | 0.75∼1.2 | GHz |

| Sampling speed | 1.5∼2.5 | GHz |

| Supply voltage | 0.75∼0.85 | V |

| Max[input signal swing] | 1.4 | Vpp |

| Sampling capacitor | 2.0∼30 | fF |

| Load capacitor | 2∼10 | fF |

| Aspect ratio[Sampling switch] | 0.25∼4.0 | V |

| Process corner | - | |

| Temperature | −40∼120 | C |

| Output Matrix | Unit |

|---|---|

| dBc | |

| ENOB | bit |

| Bandwidth | GHz |

| Number of Epoch | |Error| | Unit |

|---|---|---|

| 500 | 4.9 | % |

| 1000 | 3.1 | % |

| 1500 | 2.6 | % |

| 2000 | 1.7 | % |

| Input Parameter | Variable Range | Unit |

|---|---|---|

| Operating speed | 50∼150 | psec |

| Supply voltage | 0.75∼0.85 | V |

| Input transistor size | 1∼8 | scale |

| Regeneration strength | 1∼8 | scale |

| Reset switch size | 1∼4 | scale |

| Load capacitor size | 2∼10 | fF |

| Process corner | - | |

| Temperature | −40∼120 | C |

| Output Metrics | Unit |

|---|---|

| Noise power | |

| Poser dissipation | W |

| Speed | psec |

| Input Parameter | Variable Range | Unit |

|---|---|---|

| Supply voltage | 0.7∼0.9 | V |

| Logic gate size | 1∼25 | scale |

| Load capacitor size | 2∼10 | fF |

| Process corner | - | |

| Temperature | −40∼120 | C |

| Output Metrics | Unit |

|---|---|

| W | |

| Area | scale |

| Speed | psec |

| Spec. | Corner | SPICE Sim. | AMS Sim. | Error |

|---|---|---|---|---|

| FoM (fJ/c.s) | FoM (fJ/c.s) | % | ||

| SS | 6.8 | 5.8 | 17.2 | |

| 8-bit 1.5-GS/s | TT | 6.0 | 5.5 | 9.1 |

| FF | 5.3 | 4.7 | 12.8 | |

| SS | 12.5 | 11.9 | 5.04 | |

| 8-bit 2.0-GS/s | TT | 9.8 | 9.1 | 7.7 |

| FF | 11.8 | 9.9 | 7.7 | |

| SS | 12.2 | 11.8 | 3.4 | |

| 6-bit 2.5-GS/s | TT | 10.0 | 9.2 | 8.7 |

| FF | 8.5 | 7.7 | 10.4 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Nam, J.-W.; Cho, Y.-K.; Lee, Y.K. Regression Model-Based AMS Circuit Optimization Technique Utilizing Parameterized Operating Condition. Electronics 2022, 11, 408. https://doi.org/10.3390/electronics11030408

Nam J-W, Cho Y-K, Lee YK. Regression Model-Based AMS Circuit Optimization Technique Utilizing Parameterized Operating Condition. Electronics. 2022; 11(3):408. https://doi.org/10.3390/electronics11030408

Chicago/Turabian StyleNam, Jae-Won, Young-Kyun Cho, and Youn Kyu Lee. 2022. "Regression Model-Based AMS Circuit Optimization Technique Utilizing Parameterized Operating Condition" Electronics 11, no. 3: 408. https://doi.org/10.3390/electronics11030408

APA StyleNam, J.-W., Cho, Y.-K., & Lee, Y. K. (2022). Regression Model-Based AMS Circuit Optimization Technique Utilizing Parameterized Operating Condition. Electronics, 11(3), 408. https://doi.org/10.3390/electronics11030408