A Flash Frequency Tuning Technique for SC-Based mm Wave VCOs

Abstract

:1. Introduction

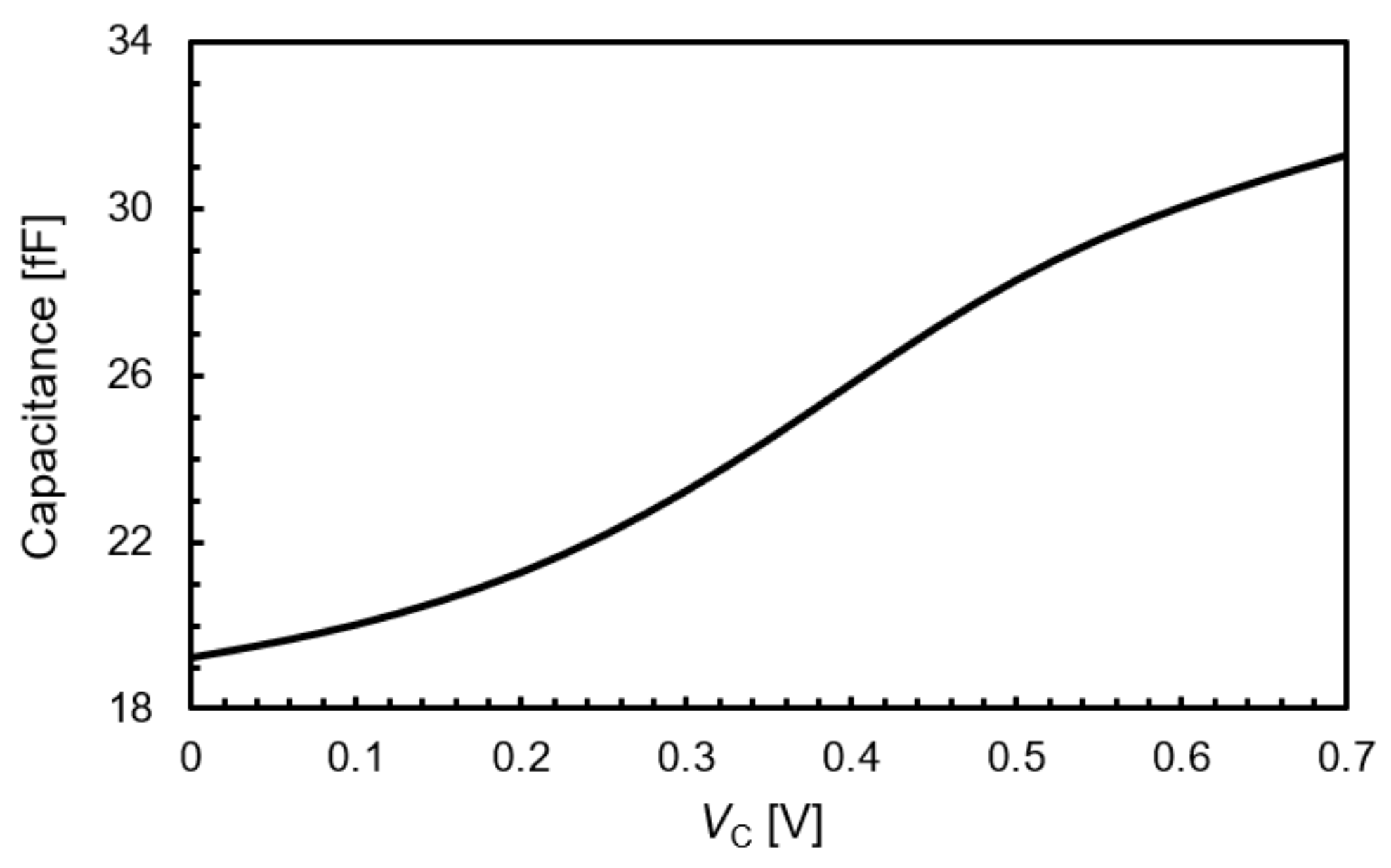

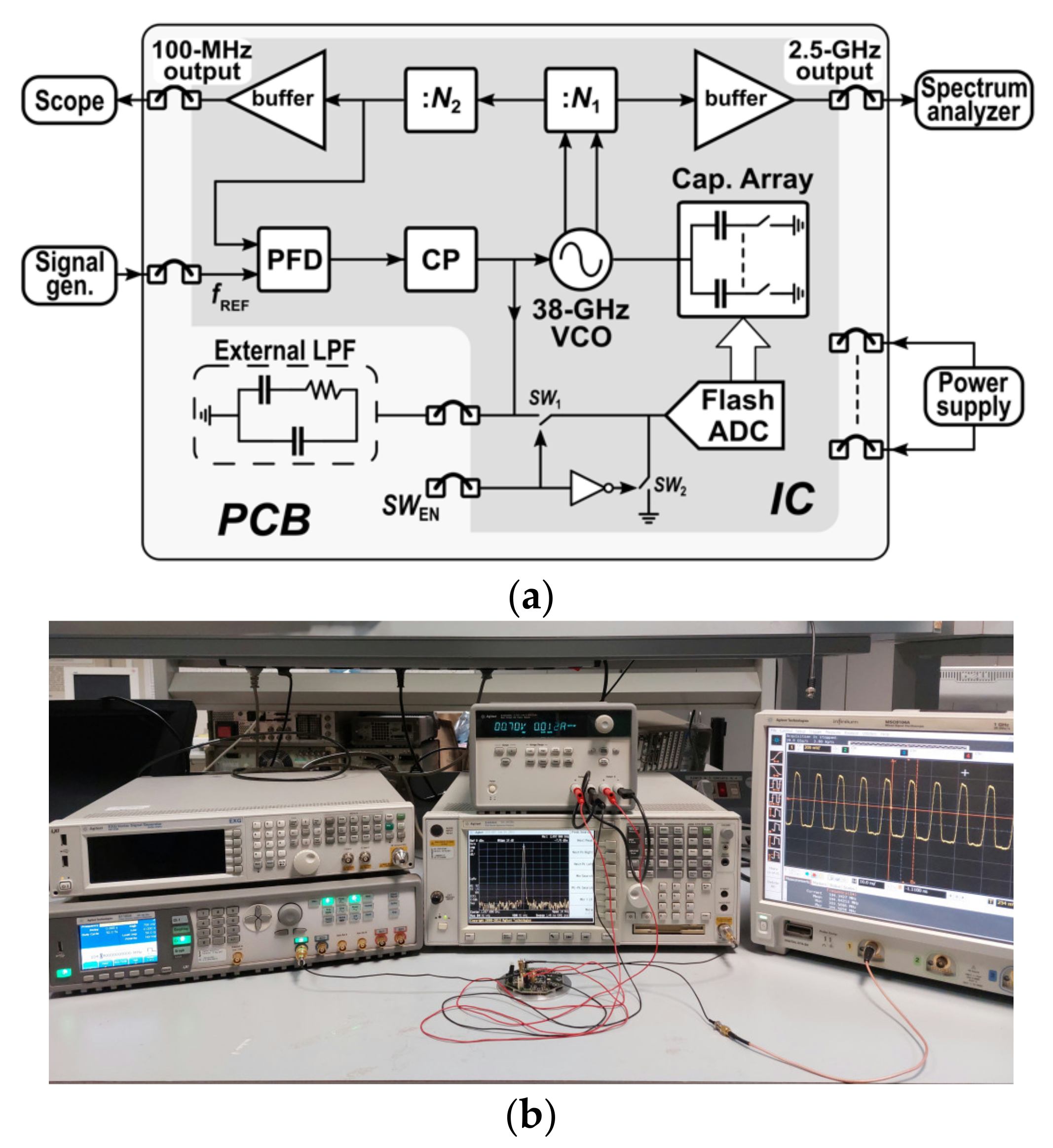

2. Circuit Description

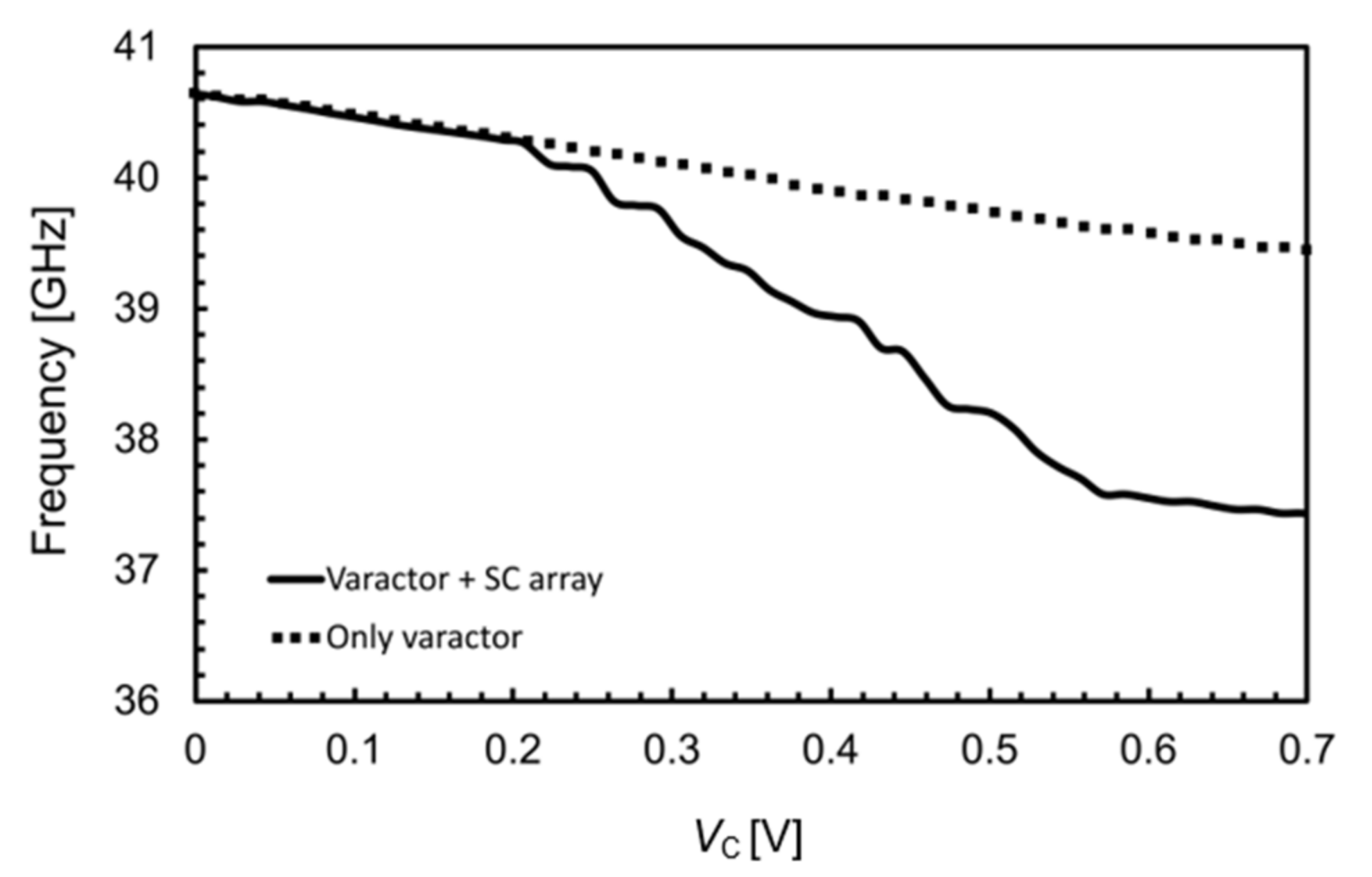

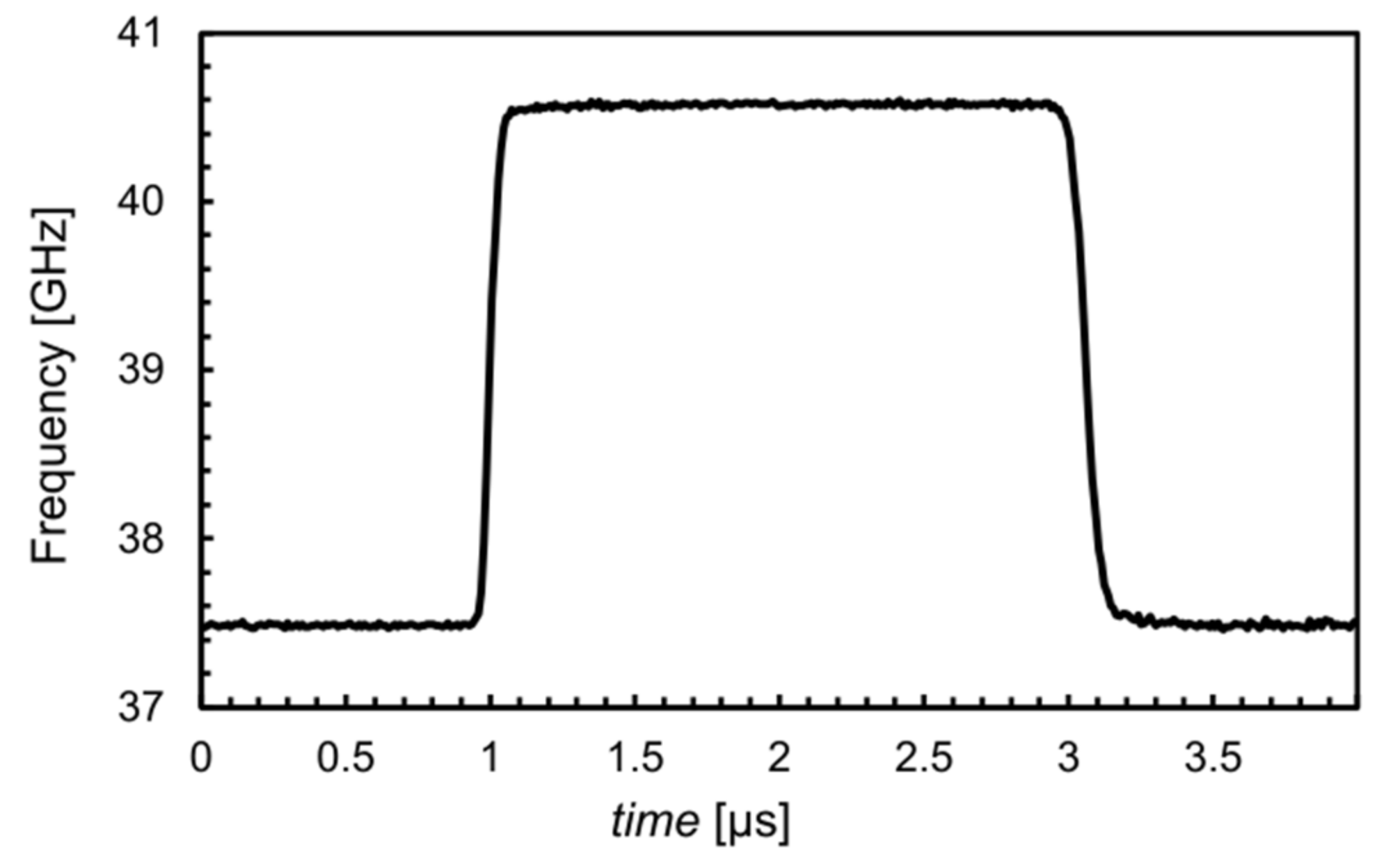

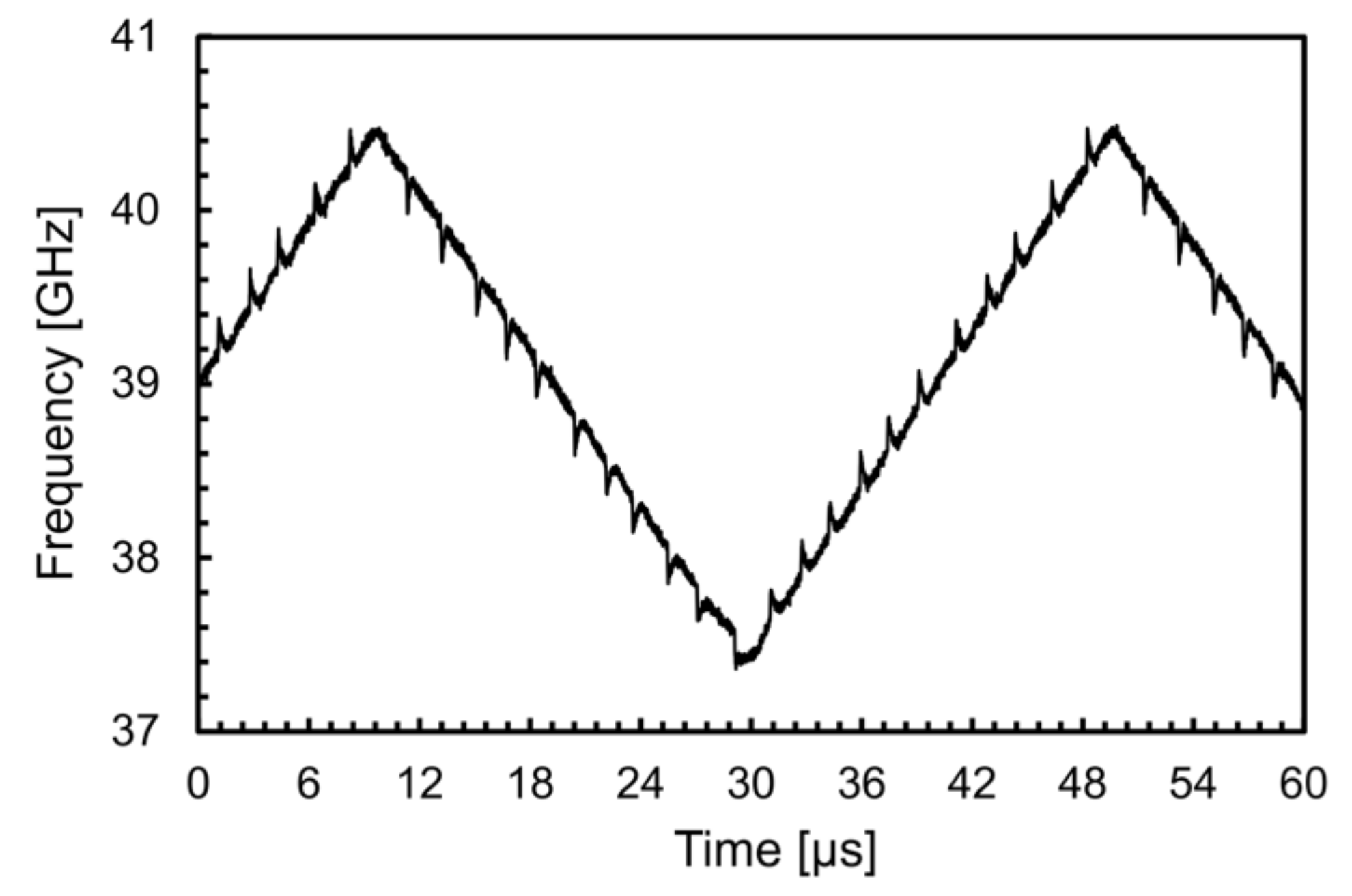

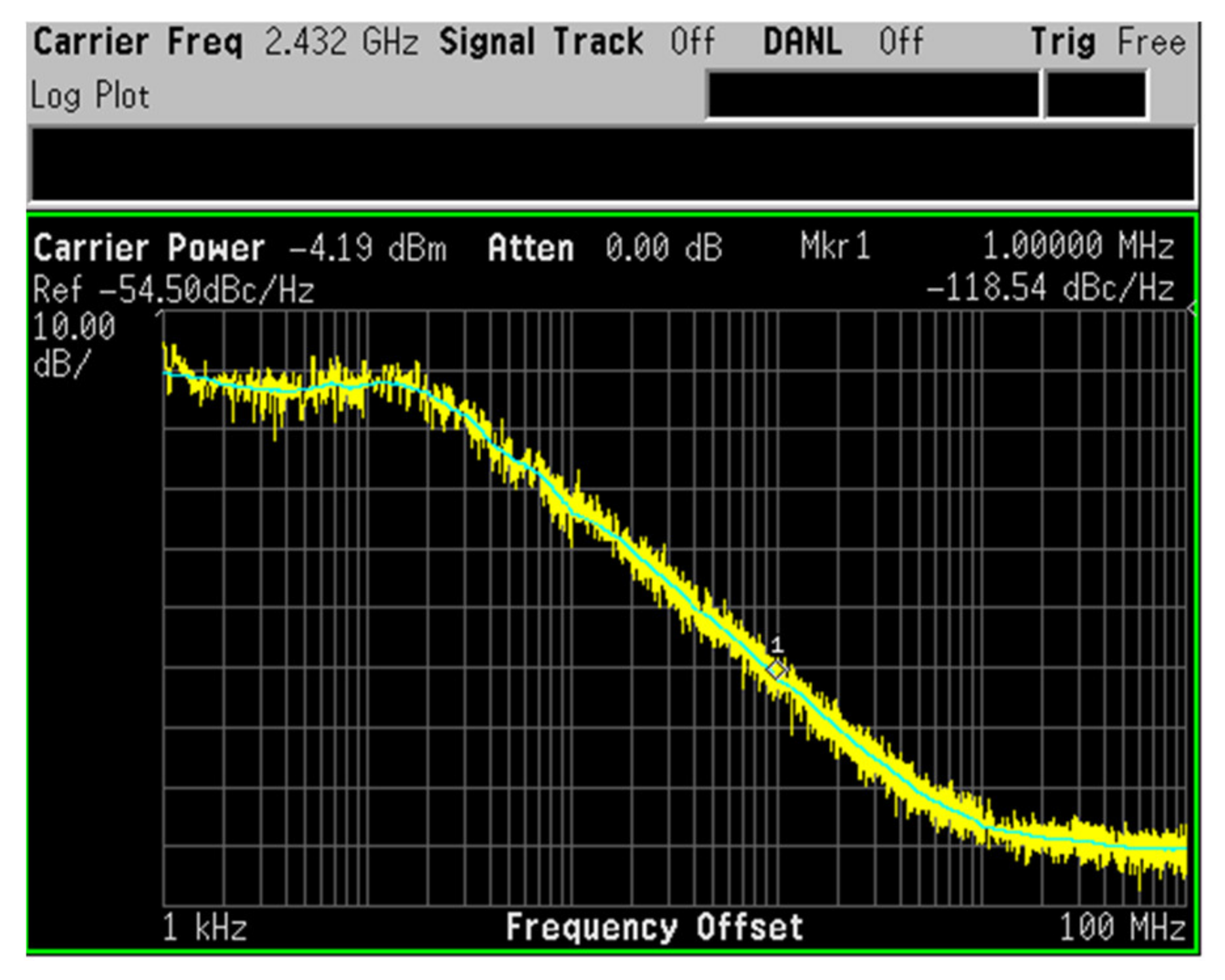

3. Experimental Results

4. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Arbabian, A.; Callender, S.; Kang, S.; Rangwala, M.; Niknejad, A.M. A 94 GHz mm-Wave-to-Baseband Pulsed-Radar Transceiver with Applications in Imaging and Gesture Recognition. IEEE J. Solid State Circuits 2013, 48, 1055–1071. [Google Scholar] [CrossRef]

- Shirazi, A.H.M.; Nikpaik, A.; Molavi, R.; Lightbody, S.; Djahanshahi, H.; Taghivand, M.; Mirabbasi, S.; Shekhar, S. On the Design of mm-Wave Self-Mixing-VCO Architecture for High Tuning-Range and Low Phase Noise. IEEE J. Solid State Circuits 2016, 51, 1210–1222. [Google Scholar] [CrossRef]

- Di Meo, S.; Svelto, F.; Summers, P.E.; Renne, G.; Preda, L.; Bellomi, M.; Espin-Lopez, P.F.; Martellosio, A.; Pasian, M.; Matrone, G.; et al. On the Feasibility of Breast Cancer Imaging Systems at Millimeter-Waves Frequencies. IEEE Trans. Microw. Theory Tech. 2017, 65, 1795–1806. [Google Scholar] [CrossRef]

- Maltsev, A.; Maslennikov, R.; Sevastyanov, A.; Khoryaev, A.; Lomayev, A. Experimental investigations of 60 GHz WLAN systems in office environment. IEEE J. Sel. Areas Commun. 2009, 27, 1488–1499. [Google Scholar] [CrossRef]

- Rajagopal, S.; Abu-Surra, S.; Ramakrishna, S.; Taori, R. MIMO designs for mmWave wireless LAN systems. In Proceedings of the 48th Asilomar Conference on Signals, Systems and Computers, Pacific Grove, CA, USA, 2–5 November 2014; pp. 1916–1920. [Google Scholar]

- Rakesh, R.T.; Sen, D.; Das, G.; Viterbo, E.; Hong, Y. On Distance Statistics of First Arriving Multi-Paths in Indoor mm-Wave Communications. IEEE Trans. Veh. Technol. 2020, 69, 16218–16223. [Google Scholar]

- Fettweis, G.; Alamouti, S.M. 5G: Personal mobile internet beyond what cellular did to telephony. IEEE Commun. Mag. 2014, 52, 140–145. [Google Scholar] [CrossRef]

- Ek, S.; Påahlsson, T.; Elgaard, C.; Carlsson, A.; Axholt, A.; Stenman, A.-K.; Sundstrom, L.; Sjoland, H. A 28-nm FD-SOI 115-fs Jitter PLL-Based LO System for 24–30-GHz Sliding-IF 5G Transceivers. IEEE J. Solid State Circuits 2018, 53, 1988–2000. [Google Scholar] [CrossRef]

- Cavarra, A.; Papotto, G.; Parisi, A.; Finocchiaro, A.; Nocera, C.; Palmisano, G. Transformer-Based VCO for W-Band Automotive Radar Applications. Electronics 2021, 10, 531. [Google Scholar] [CrossRef]

- Lee, J.; Li, Y.-A.; Hung, M.-H.; Huang, S.-J. A Fully-Integrated 77-GHz FMCW Radar Transceiver in 65-nm CMOS Technology. IEEE J. Solid State Circuits 2010, 45, 2746–2756. [Google Scholar]

- Papotto, G.; Nocera, C.; Finocchiaro, A.; Parisi, A.; Cavarra, A.; Castorina, A.; Ragonese, E.; Palmisano, G. A 27-mW W-Band Radar Receiver With Effective TX Leakage Suppression in 28-nm FD-SOI CMOS. IEEE Trans. Microw. Theory Tech. 2021, 69, 4132–4141. [Google Scholar] [CrossRef]

- Vovnoboy, J.; Levinger, R.; Mazor, N.; Elad, D. A Dual-Loop Synthesizer with Fast Frequency Modulation Ability for 77/79 GHz FMCW Automotive Radar Applications. IEEE J. Solid State Circuits 2018, 53, 1328–1337. [Google Scholar] [CrossRef]

- Ma, T.; Deng, W.; Chen, Z.; Wu, J.; Zheng, W.; Wang, S.; Qi, N.; Liu, Y.; Chi, B. A CMOS 76–81-GHz 2-TX 3-RX FMCW radar transceiver based on mixed-mode PLL chirp generator. IEEE J. Solid State Circuits 2019, 55, 233–248. [Google Scholar] [CrossRef]

- Qiao, J.; Shen, X.S.; Mark, J.W.; Lei, L. Video Quality Provisioning for Millimeter Wave 5G Cellular Networks with Link Outage. IEEE Trans. Wirel. Commun. 2015, 14, 5692–5703. [Google Scholar] [CrossRef]

- Abdulaziz, M.; Forsberg, T.; Tormanen, M.; Sjoland, H. A 10-mW mm-Wave Phase-Locked Loop with Improved Lock Time in 28-nm FD-SOI CMOS. IEEE Trans. Microw. Theory Tech. 2019, 67, 1588–1600. [Google Scholar] [CrossRef] [Green Version]

- Lin, T.-H.; Kaiser, W.J. A 900-MHz 2.5-mA CMOS frequency synthesizer with an automatic SC tuning loop. IEEE J. Solid State Circuits 2001, 36, 424–431. [Google Scholar]

- Lin, T.-H.; Lai, Y.-J. An Agile VCO Frequency Calibration Technique for a 10-GHz CMOS PLL. IEEE J. Solid State Circuits 2007, 42, 340–349. [Google Scholar] [CrossRef] [Green Version]

- Shin, J.; Shin, H. A Fast and High-Precision VCO Frequency Calibration Technique for Wideband ΔΣ Fractional-N Frequency Synthesizers. IEEE Trans. Circuits Syst. I Regul. Pap. 2009, 57, 1573–1582. [Google Scholar] [CrossRef]

- Ryu, H.; Sung, E.-T.; Park, S.; Cho, J.-K.; Baek, D. Fast Automatic Frequency Calibrator Using an Adaptive Frequency Search Algorithm. IEEE Trans. Very Large Scale Integr. Syst. 2016, 25, 1490–1496. [Google Scholar] [CrossRef]

- Ferriss, M.; Sadhu, B.; Rylyakov, A.; Ainspan, H.; Friedman, D. A 12-to-26GHz fractional-N PLL with dual continuous tuning LC-D/VCOs. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 31 January–4 February 2016; pp. 196–198. [Google Scholar]

- Shi, C.; Yang, H.; Xiao, H.; Liu, J.; Liao, H. A dual loop dual VCO CMOS PLL using a novel coarse tuning technique for DTV. In Proceedings of the 9th International Conference on Solid-State and Integrated-Circuit Technology, Beijing, China, 20–23 October 2008; pp. 1597–1600. [Google Scholar]

- Parisi, A.; Finocchiaro, A.; Cavarra, A.; Papotto, G.; Palmisano, G. An Oscillator Circuit, Corresponding Radar Sensor, Vehicle and Method of Operation. Italy Patent Application 102020000019786, 7 August 2020. [Google Scholar]

- Cathelin, A. Fully depleted silicon on insulator devices CMOS: The 28 nm node is the perfect technology for analog, RF, mmW, and mixed signal system-on-chip integration. IEEE Solid State Circuits Mag. 2017, 9, 18–26. [Google Scholar] [CrossRef]

- Deng, W.; Song, Z.; Ma, R.; Lin, J.; Li, Y.; Ye, J.; Kong, S.; Hu, S.; Jia, H.; Chi, B. An Energy-Efficient 10-Gb/s CMOS Millimeter-Wave Transceiver with Direct-Modulation Digital Transmitter and I/Q Phase-Coupled Frequency Synthesizer. IEEE J. Solid State Circuits 2020, 55, 2027–2042. [Google Scholar] [CrossRef]

| Ek JSSC’18 [8] | Ma JSSC’20 [13] | Deng JSSC’20 [24] | This Work | ||

|---|---|---|---|---|---|

| CMOS technology | 28 nm FD-SOI | 65 nm | 65 nm | 28 nm FD-SOI | |

| Power supply | (V) | 1.2 | 1 | 1 | 0.7 |

| Power consumption | (mW) | 3.3 | - | 11.6 | 8.4 |

| Tuning approach | SC + varactor | SC + varactor | SC + Varactor | SC + varactor | |

| Center frequency | (GHz) | 18 | 39.6 | 20 | 39 |

| Tuning range | (GHz) | 16.3 to 19.7 | 37.2 to 42 | 17.4 to 22.4 | 37.4 to 40.7 |

| PN(a) @ 1 MHz | (dBc/Hz) | −92.3 (b) | −93.4 | −96.9 | −94 |

| Calibration extra time | YES | YES | YES | NO | |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Parisi, A.; Cavarra, A.; Finocchiaro, A.; Papotto, G.; Palmisano, G. A Flash Frequency Tuning Technique for SC-Based mm Wave VCOs. Electronics 2022, 11, 433. https://doi.org/10.3390/electronics11030433

Parisi A, Cavarra A, Finocchiaro A, Papotto G, Palmisano G. A Flash Frequency Tuning Technique for SC-Based mm Wave VCOs. Electronics. 2022; 11(3):433. https://doi.org/10.3390/electronics11030433

Chicago/Turabian StyleParisi, Alessandro, Andrea Cavarra, Alessandro Finocchiaro, Giuseppe Papotto, and Giuseppe Palmisano. 2022. "A Flash Frequency Tuning Technique for SC-Based mm Wave VCOs" Electronics 11, no. 3: 433. https://doi.org/10.3390/electronics11030433

APA StyleParisi, A., Cavarra, A., Finocchiaro, A., Papotto, G., & Palmisano, G. (2022). A Flash Frequency Tuning Technique for SC-Based mm Wave VCOs. Electronics, 11(3), 433. https://doi.org/10.3390/electronics11030433