A Calibration-Free, 16-Channel, 50-MS/s, 14-Bit, Pipelined-SAR ADC with Reference/Op-Amp Sharing and Optimized Stage Resolution Distribution

Abstract

:1. Introduction

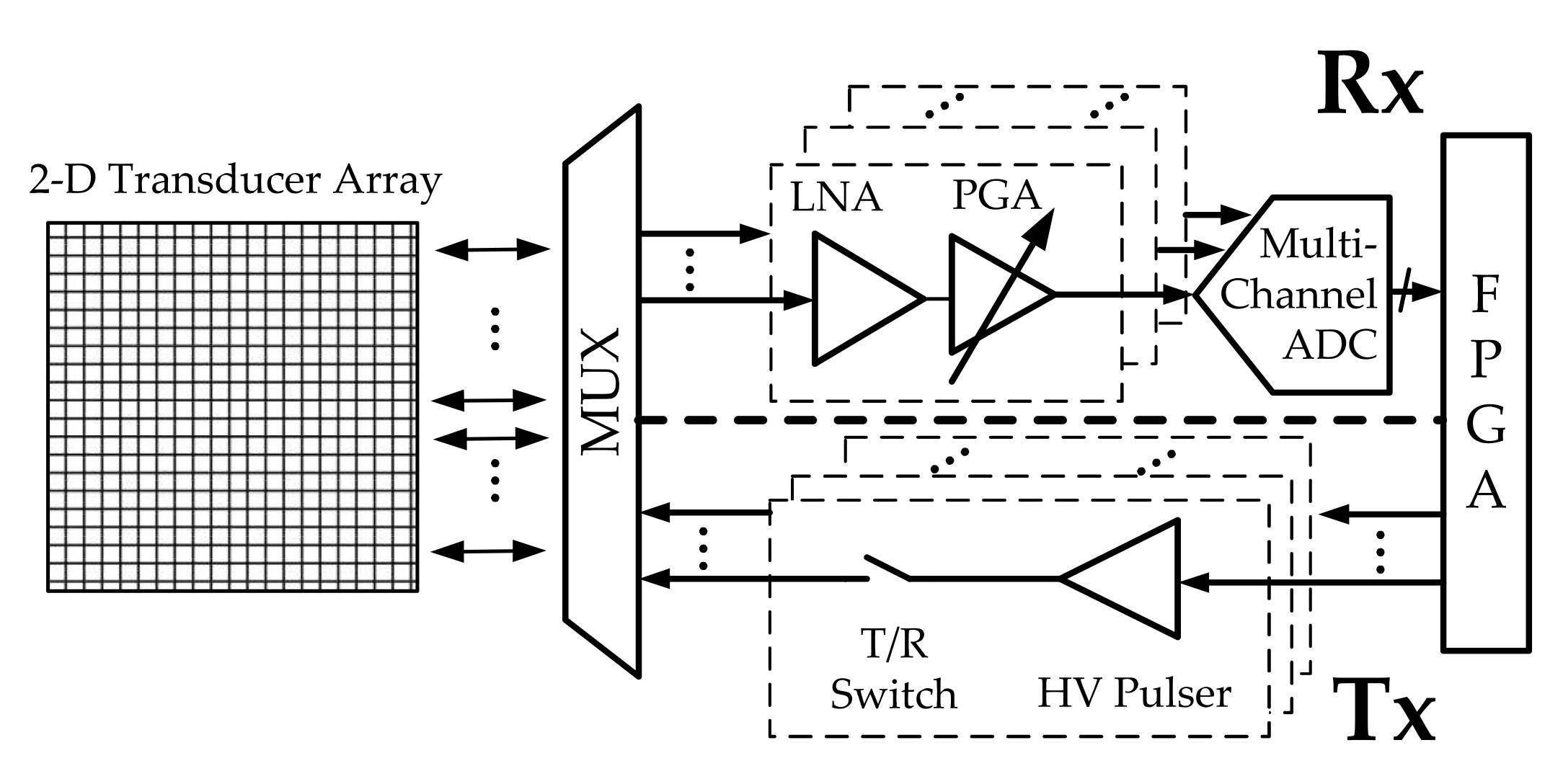

1.1. Ultrasound Imaging System

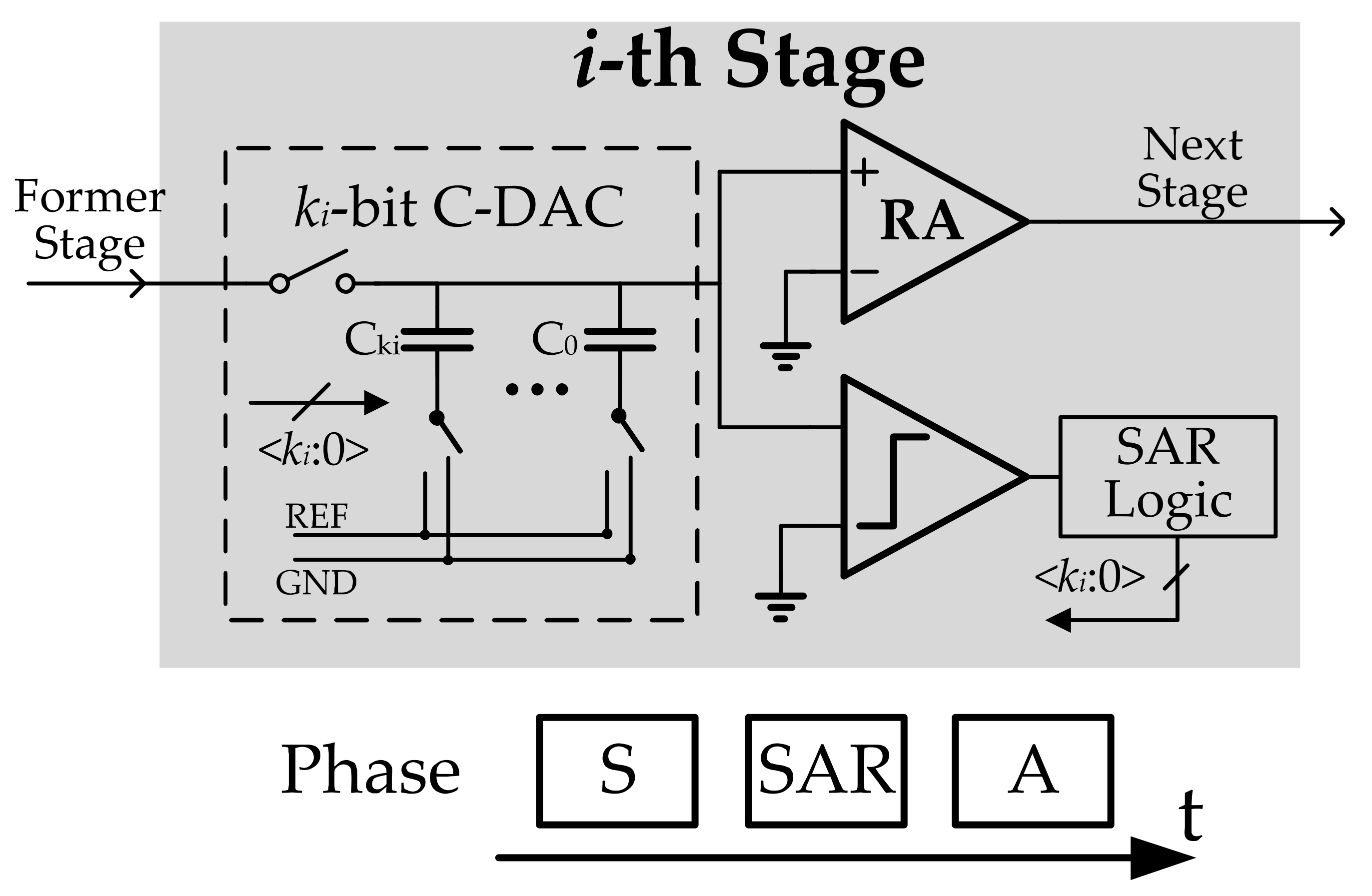

1.2. Pipelined-SAR ADC

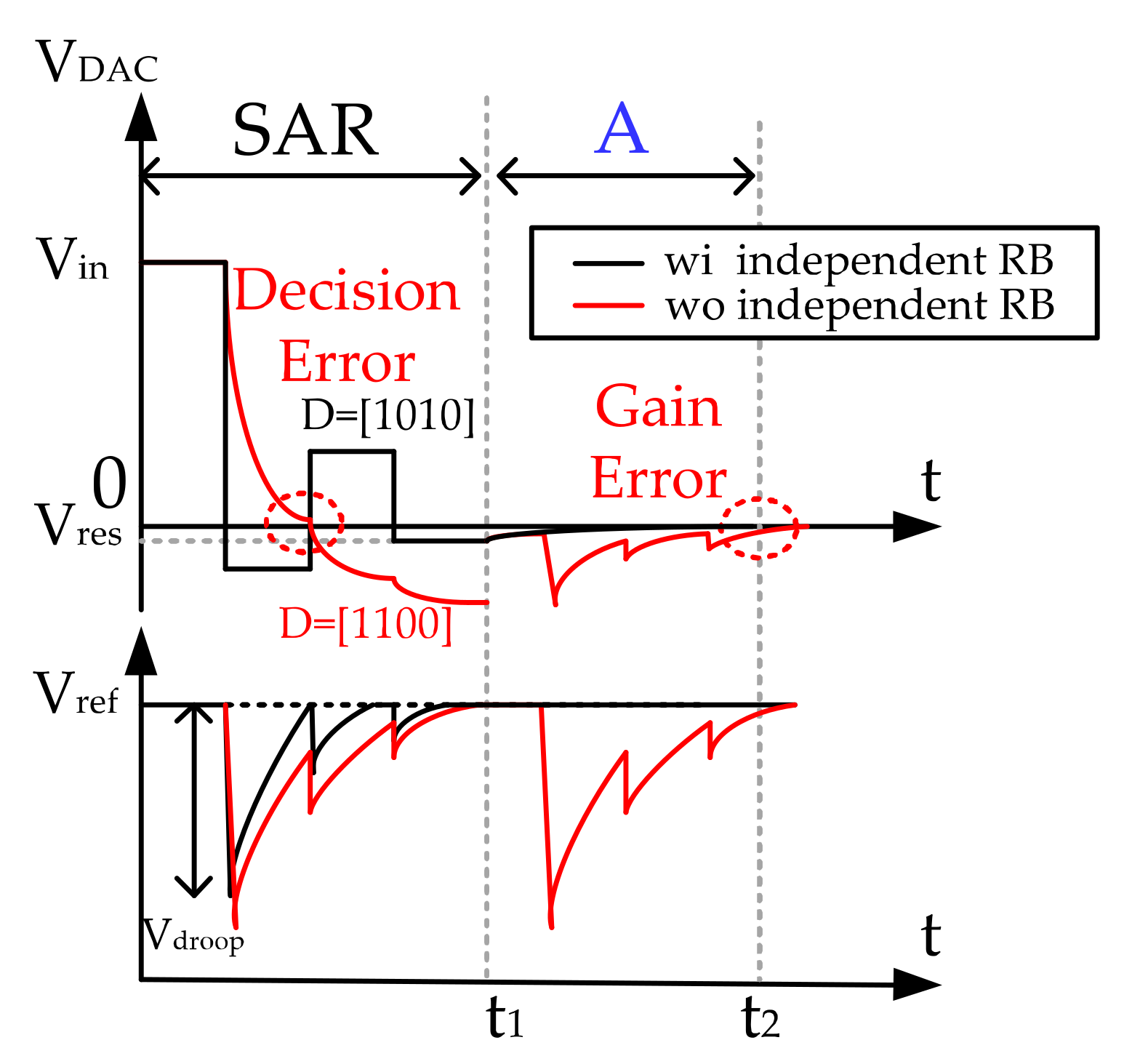

1.3. Reference Considerations in Pipelined-SAR ADCs

2. Reference and Op-Amp Sharing in Pipelined-SAR ADCs

2.1. Proposed Reference Sharing Scheme

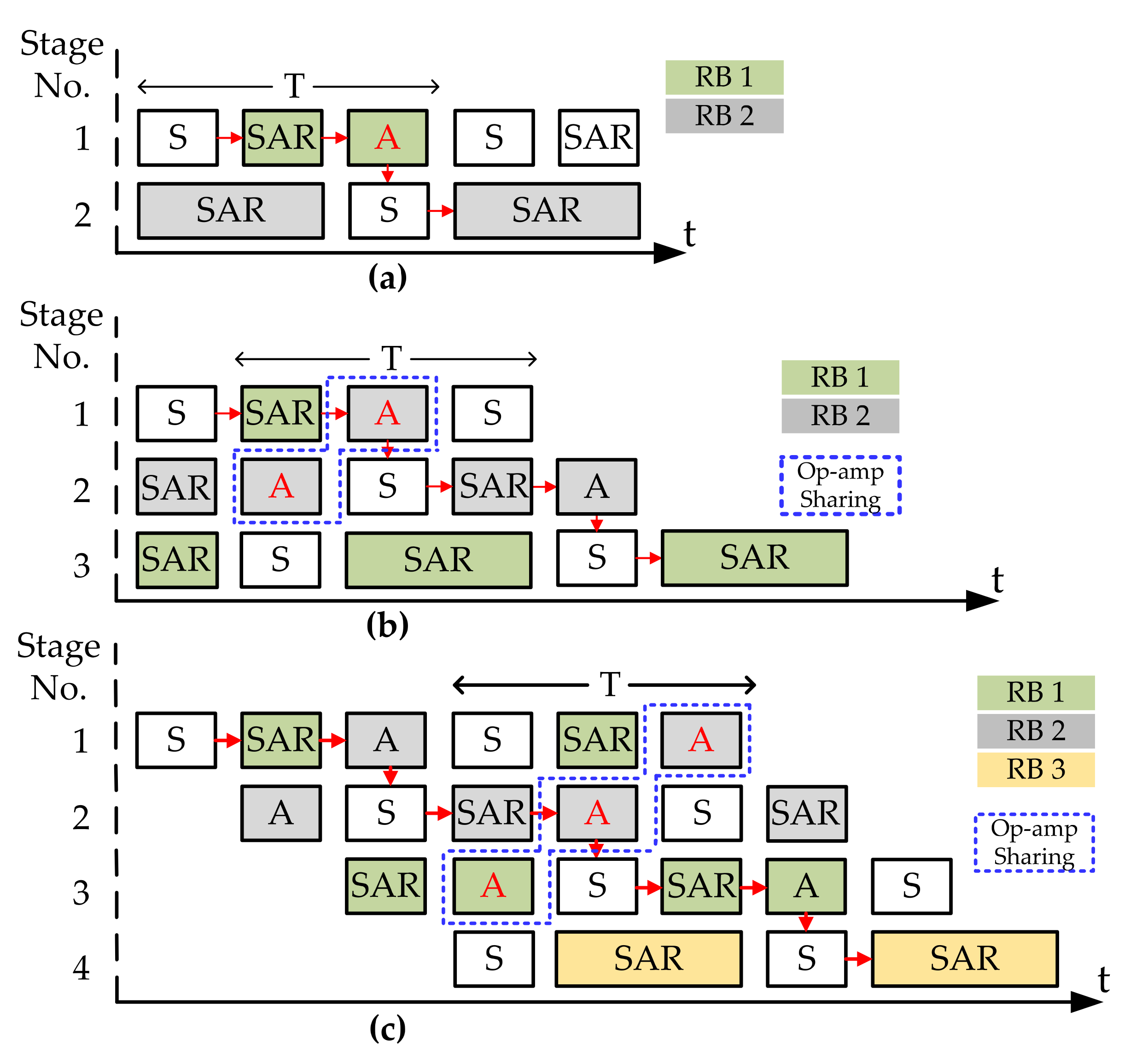

2.2. Op-Amp Sharing in the Proposed Scheme

3. Architecture Optimization Based on Reference/Op-Amp Sharing

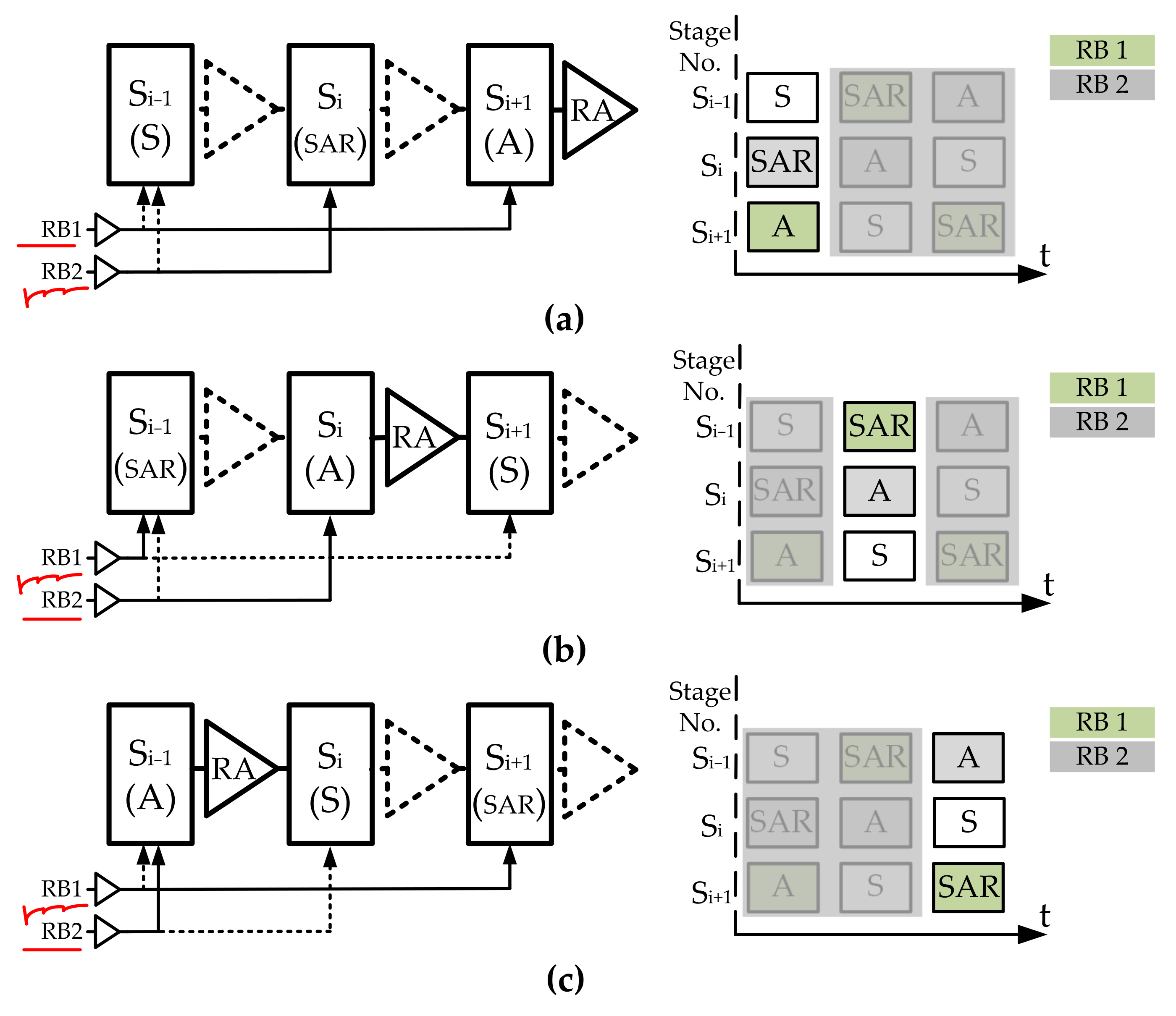

3.1. Reference and Op-Amp Sharing in Different Architectures

3.2. Principle of Area and Power Consumption Analysis

3.2.1. Area Analysis

3.2.2. Power Consumption Analysis

3.3. Proposed Area-and-Power Efficient Three-Stage Architecture for a 14-Bit ADC

3.4. Summary of This Section

4. Proposed Three-Stage Pipelined-SAR ADC

4.1. Overall Structure

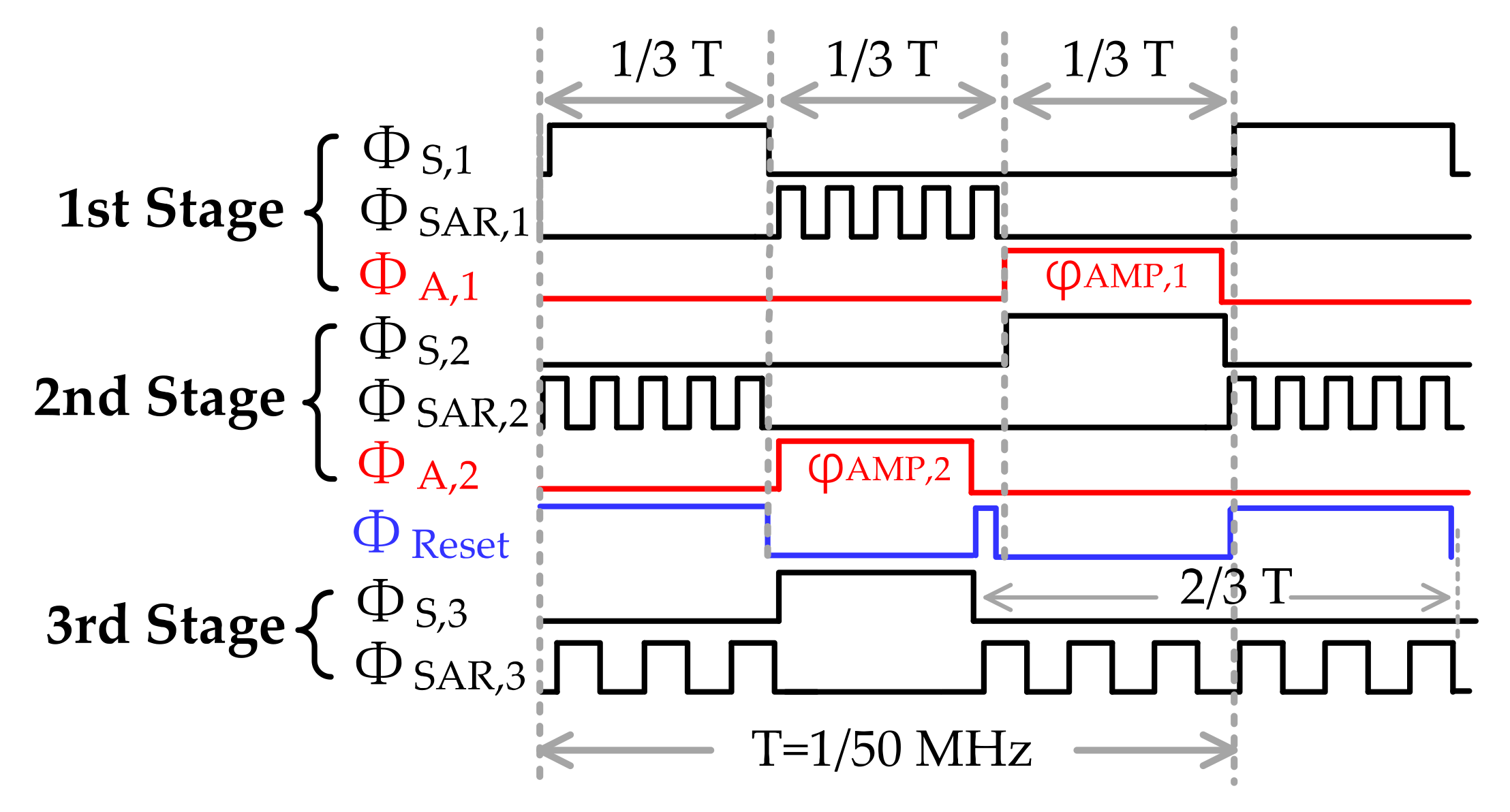

4.2. Timing Diagram

5. Circuit Implementation

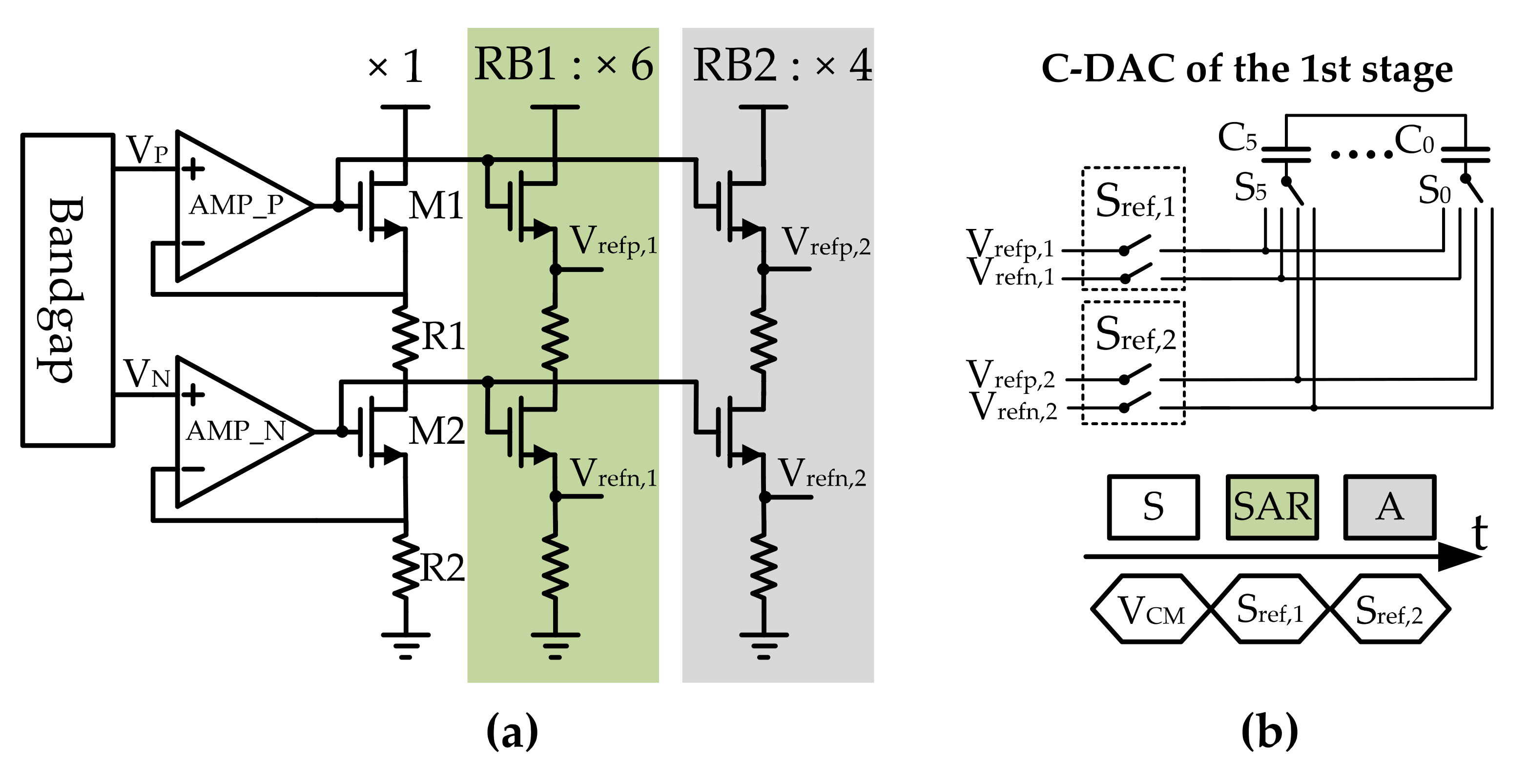

5.1. Shared Reference

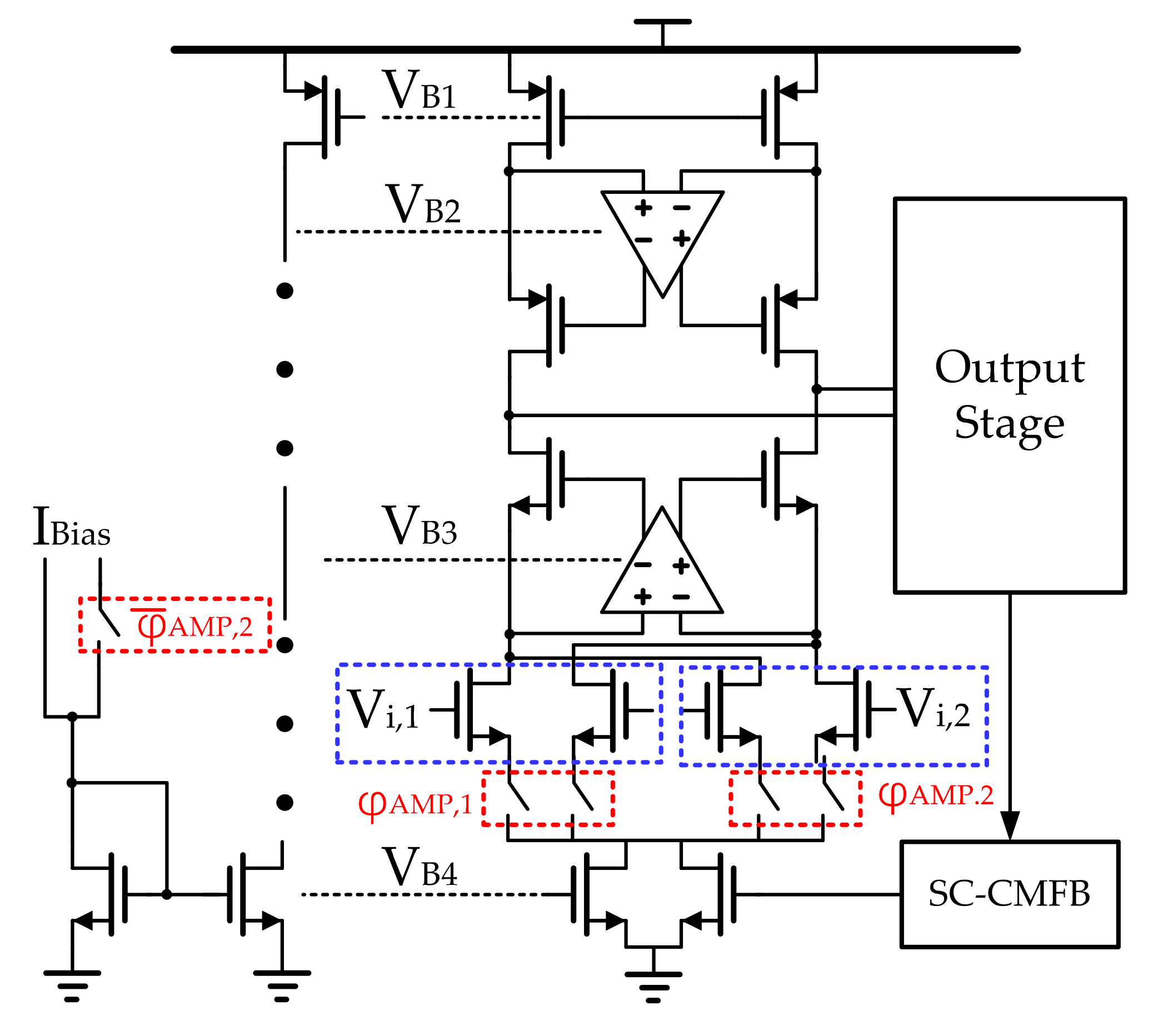

5.2. Shared Op-Amp

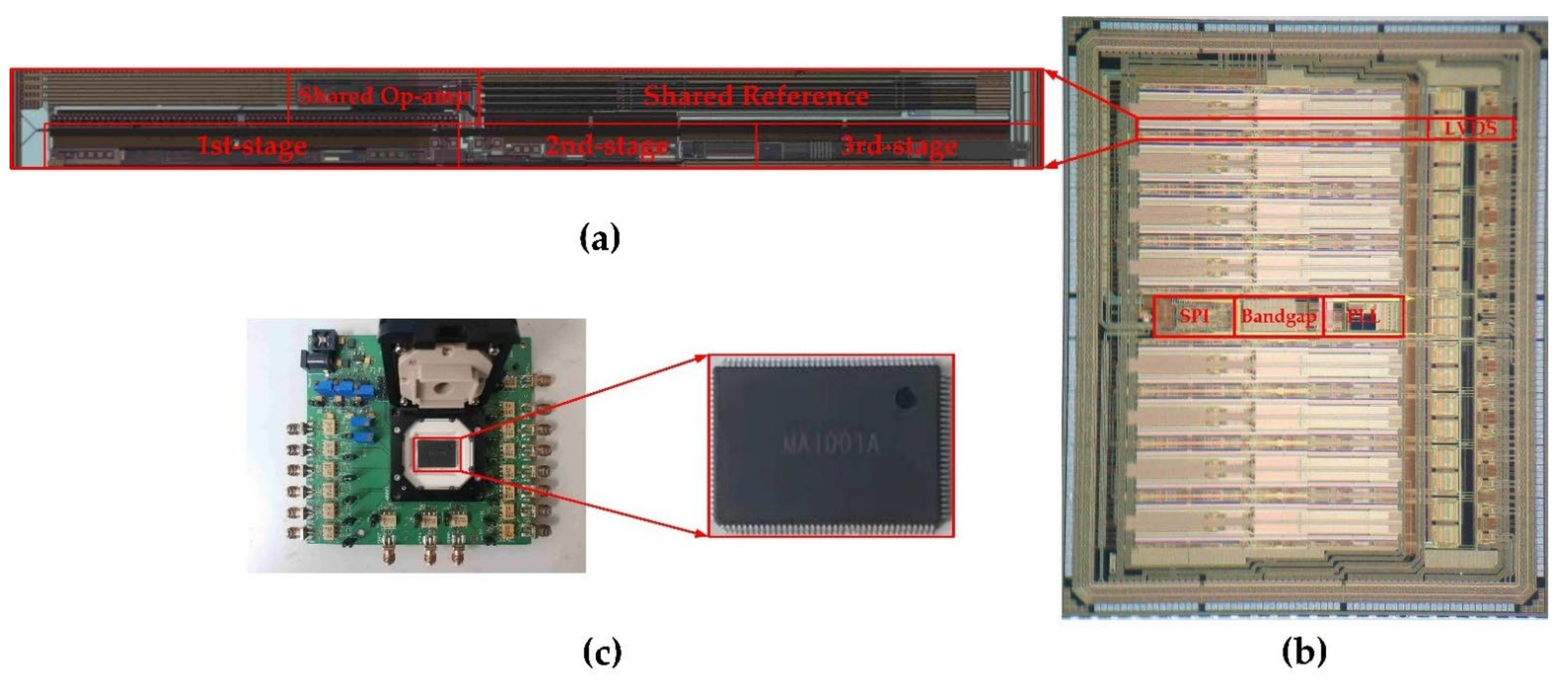

5.3. Layout Considerations

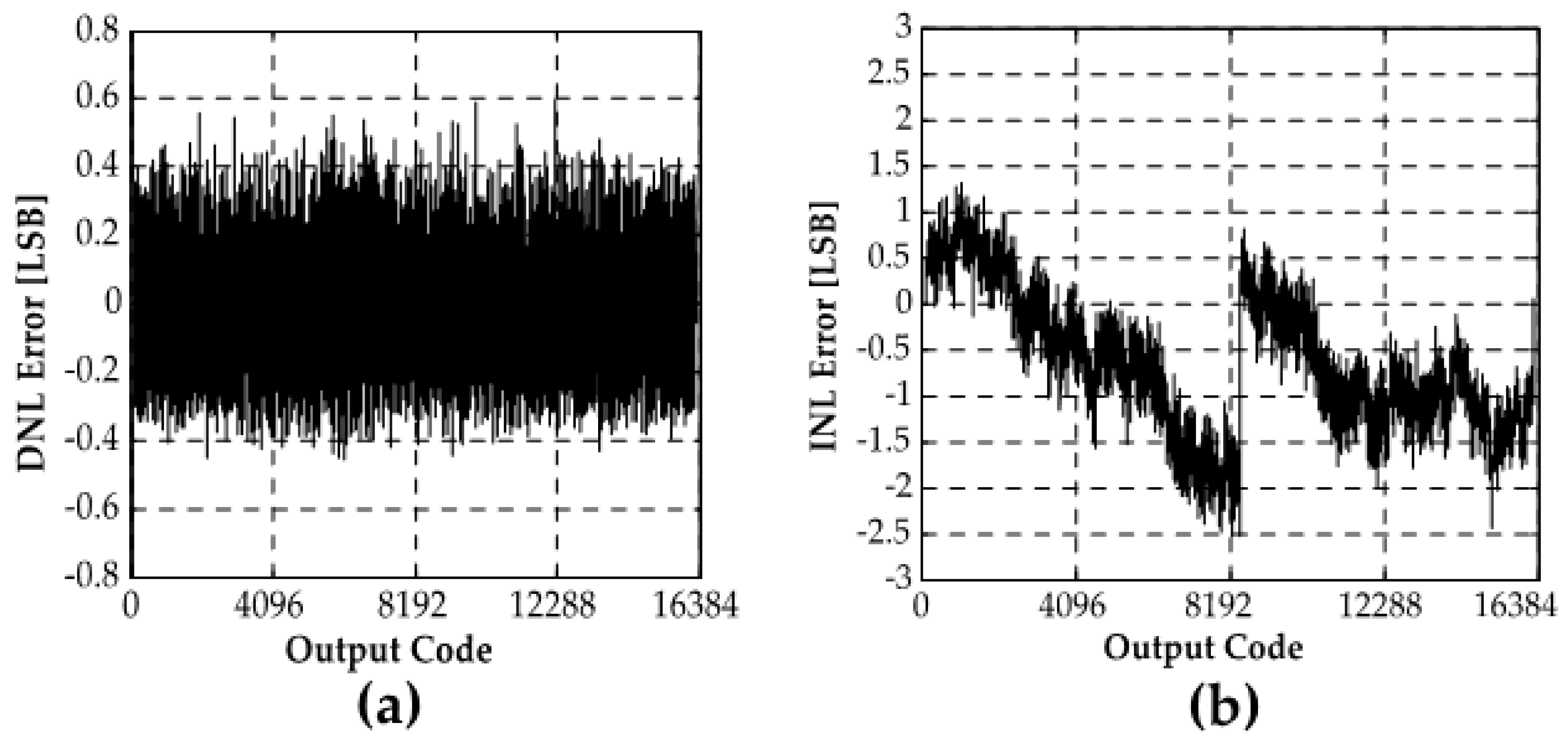

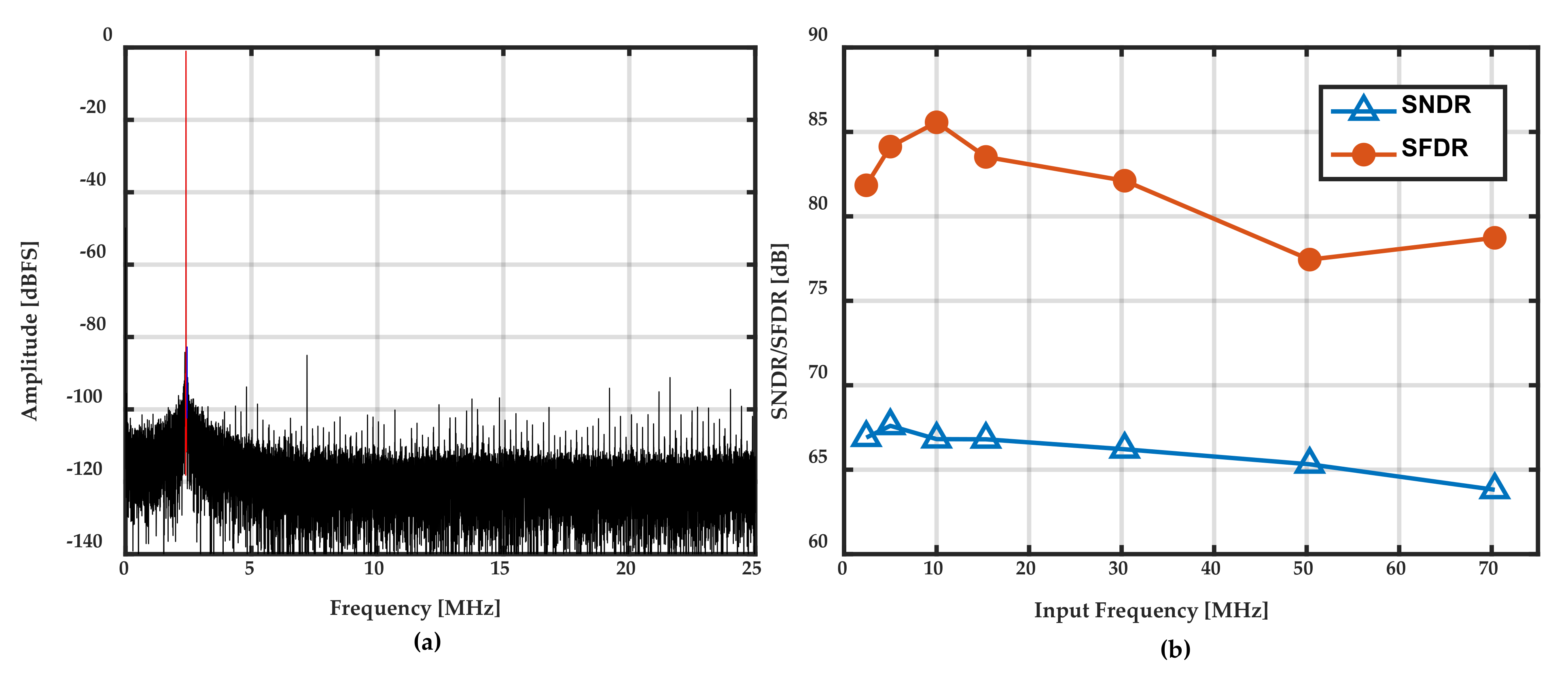

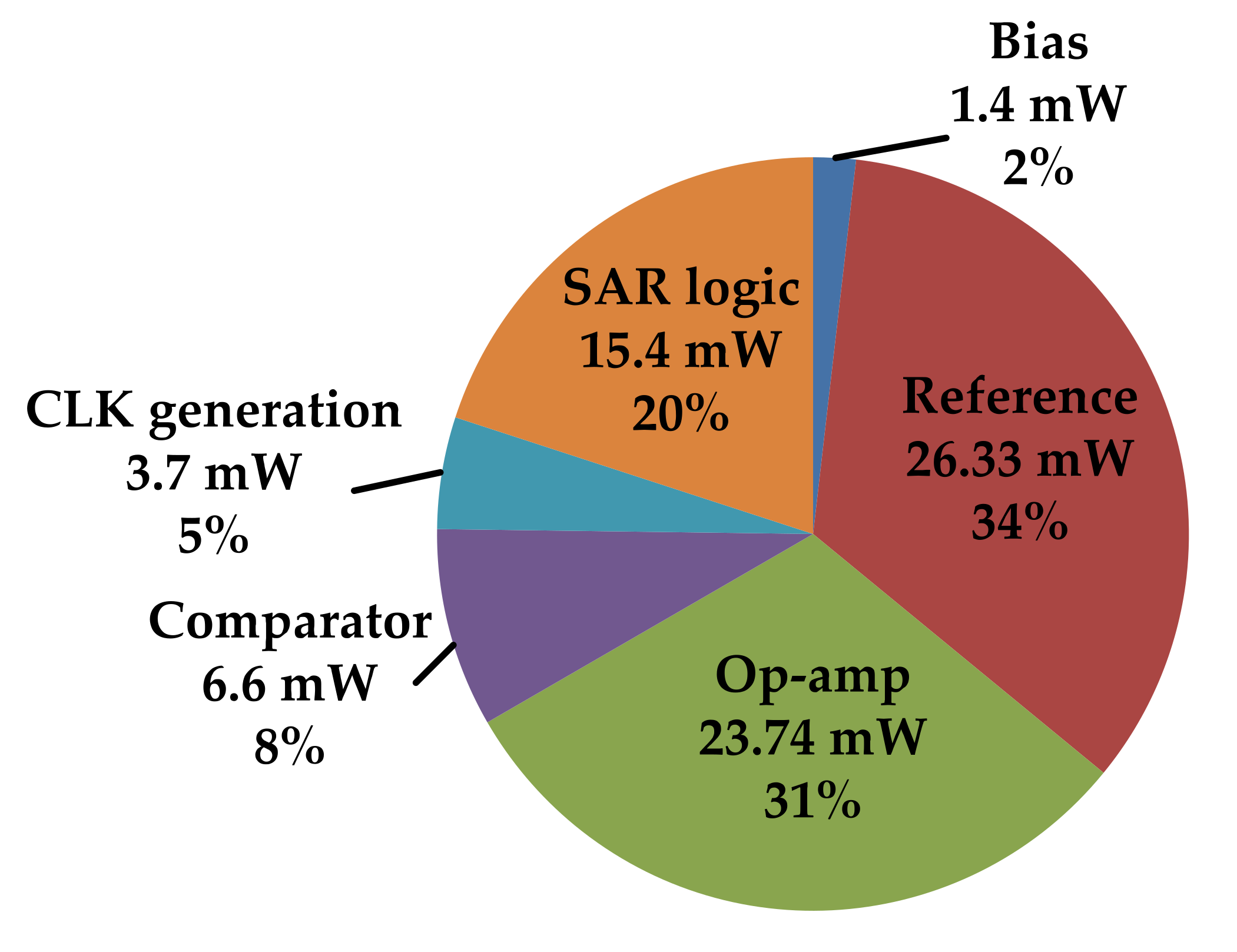

6. Measurement Results

7. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Tang, H.; Lu, Y.; Assaderaghi, F.; Daneman, M.; Jiang, X.; Lim, M.; Ng, E.; Singhal, U.; Tsai, J.M. 3D Ultrasonic Fingerprint Capacitive Fingerprint Sensor. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 31 January 2016. [Google Scholar]

- Chen, M.-C.; Perez, A.P.; Kothapalli, S.-R.; Cathelin, P.; Cathelin, A.; Gambhir, S.S.; Murmann, B. A Pixel Pitch-Matched Ultrasound Receiver for 3-D Photoacoustic Imaging With Integrated Delta-Sigma Beamformer in 28-nm UTBB FD-SOI. IEEE J. Solid-State Circuits 2017, 52, 1–14. [Google Scholar] [CrossRef] [PubMed]

- Romero-Morales, C.; Martín-Llantino, P.; Calvo-Lobo, C.; San-Antolín, M.; López-López, D.; Blanco-Morales, M.; Rodríguez-Sanz, D. Ultrasound Imaging of the Abdominal Wall and Trunk Muscles in Patients with Achilles Tendinopathy versus Healthy Participants. Diagnostics 2019, 10, 17. [Google Scholar] [CrossRef] [Green Version]

- Petrusca, L.; Varray, F.; Souchon, R.; Bernard, A.; Chapelon, J.Y.; Liebgott, H.; N’Djin, W.A.; Viallon, M. Fast Volumetric Ultrasound B-Mode and Doppler Imaging with a New High-Channels Density Platform for Advanced 4D Cardiac Imaging/Therapy. Appl. Sci. 2018, 8, 200. [Google Scholar] [CrossRef] [Green Version]

- Liu, H.-L.; Jan, C.-K.; Chu, P.-C.; Hong, J.-C.; Lee, P.-Y.; Hsu, J.-D.; Lin, C.-C.; Huang, C.-Y.; Chen, P.-Y.; Wei, K.-C. Design and Experimental Evaluation of a 256-Channel Dual-Frequency Ultrasound Phased-Array System for Transcranial Blood–Brain Barrier Opening and Brain Drug Delivery. IEEE Trans. Biomed. Eng. 2014, 61, 1350–1360. [Google Scholar] [CrossRef]

- Chen, D.; Cui, X.; Zhang, Q.; Li, D.; Cheng, W.; Fei, C.; Yang, Y. A Survey on Analog-to-Digital Converter Integrated Circuits for Miniaturized High Resolution Ultrasonic Imaging System. Micromachines 2022, 13, 114. [Google Scholar] [CrossRef] [PubMed]

- Analog Devices Inc. Octal LNA/VGA/AAF/ADC and Crosspoint Switch. AD9272 Datasheet, April 2009, revised July 2017. Available online: https://www.analog.com/media/en/technical-documentation/data-sheets/AD9272.pdf (accessed on 23 February 2022).

- Texas Instruments. 16-Channel Ultrasound AFE with 90-mW/Channel Power, 1-nV/√Hz Noise, 14-Bit, 65-MSPS or 12-Bit, 80-MSPS ADC and Passive CW Mixer; AFE5816 Datasheet, April 2015, revised September 2017. Available online: https://www.ti.com/lit/ds/symlink/afe5816.pdf (accessed on 23 February 2022).

- Analog Devices Inc. Octal Ultrasound AFE with JESD204B. AD9675 Datasheet. January 2016. Available online: https://www.analog.com/media/en/technical-documentation/data-sheets/AD9675.pdf (accessed on 24 February 2022).

- Lagos, J.; Markulic, N.; Hershberg, B.; Dermit, D.; Shrivas, M.; Martens, E.; Craninckx, J. A 10.1-ENOB, 6.2-fJ/conv.-step, 500-MS/s, Ringamp-Based Pipelined-SAR ADC With Background Calibration and Dynamic Reference Regulation in 16-nm CMOS. IEEE J. Solid-State Circuits 2022, 1. [Google Scholar] [CrossRef]

- Lan, J.; Zhai, D.; Chen, Y.; Ni, Z.; Shen, X.; Ye, F.; Ren, J. A 2.5-GS/s Four-Way-Interleaved Ringamp-Based Pipelined-SAR ADC with Digital Background Calibration in 28-nm CMOS. Electronics 2021, 10, 3173. [Google Scholar] [CrossRef]

- Malki, B.; Verbruggen, B.; Wambacq, P.; Deguchi, K.; Iriguchi, M.; Craninckx, J. A Complementary Dynamic Residue Amplifier for a 67 dB SNDR 1.36 mW 170 MS/s Pipelined SAR ADC. In Proceedings of the European Solid-State Circuits Conference, Venezia Lido, Italy, 22 September 2014. [Google Scholar]

- Kwon, Y.; Kim, T.; Sun, N.; Chae, Y. A 348-μW 68.8-dB SNDR 20-MS/s Pipelined SAR ADC With a Closed-Loop Two-Stage Dynamic Amplifier. IEEE Solid-State Circuits Lett. 2021, 4, 166–169. [Google Scholar] [CrossRef]

- Ni, M.; Wang, X.; Li, F.; Wang, Z. A 13-bit 312.5-MS/s Pipelined SAR ADC With Open-Loop Integrator-Based Residue Amplifier and Gain-Stabilized Integration Time Generation. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2021, 29, 1416–1427. [Google Scholar] [CrossRef]

- Wu, C.; Yuan, J. A 12-Bit, 300-MS/s Single-Channel Pipelined-SAR ADC with an Open-Loop MDAC. IEEE J. Solid-State Circuits 2019, 54, 1446–1454. [Google Scholar] [CrossRef]

- Lee, C.C.; Flynn, M.P. A SAR-Assisted Two-Stage Pipeline ADC. IEEE J. Solid-State Circuits 2011, 46, 859–869. [Google Scholar] [CrossRef]

- Lien, Y.-C. A 14.6 mW 12 b 800 MS/s 4×time-interleaved pipelined SAR ADC achieving 60.8 dB SNDR with Nyquist input and sampling timing skew of 60 fsrms without calibration. IEEE Symp. 2016, 1–2. [Google Scholar] [CrossRef]

- Chen, L.; Sanyal, A.; Ma, J.; Sun, N. A 24-mW 11-Bit 1-MS/s SAR ADC with a Bidirectional Single-Side Switching Technique. In Proceedings of the European Solid-State Circuits Conference, Venezia Lido, Italy, 22 September 2014. [Google Scholar]

- Ginsburg, B.P.; Chandrakasan, A.P. An Energy-Efficient Charge Recycling Approach for a SAR Converter with Capacitive DAC. In Proceedings of the IEEE International Symposium on Circuits and Systems, New York, NY, USA, 23 May 2005. [Google Scholar]

- Zhu, Y.; Chan, C.-H.; Chio, U.-F.; Sin, S.-W.; Seng-Pan, U.; Martins, R.P.; Maloberti, F. A 10-bit 100-MS/s Reference-Free SAR ADC in 90 nm CMOS. IEEE J. Solid-State Circuits 2010, 45, 1111–1121. [Google Scholar] [CrossRef]

- Liu, C.C.; Chang, S.J.; Huang, G.Y.; Lin, Y.Z.; Huang, C.M.; Huang, C.H.; Bu, L.; Tsai, C.C. A 10 b 100 MS/s 1.13 mW SAR ADC with Binary-Scaled Error Compensation. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 7 February 2010. [Google Scholar]

- Cao, Y.; Zhang, S.; Zhang, T.; Chen, Y.; Zhao, Y.; Chen, C.; Ye, F.; Ren, J. A 91.0-dB SFDR Single-Coarse Dual-Fine Pipe-lined-SAR ADC with Split-Based Background Calibration in 28-nm CMOS. IEEE Trans. Circuits Syst. I Regul. Pap. 2021, 68, 641–654. [Google Scholar] [CrossRef]

- Li, C.; Chan, C.-H.; Zhu, Y.; Martins, R.P. Analysis of Reference Error in High-Speed SAR ADCs with Capacitive DAC. IEEE Trans. Circuits Syst. I Regul. Pap. 2018, 66, 82–93. [Google Scholar] [CrossRef]

- Ju, H.; Lee, S.; Lee, M. A 12-bit 40-MS/s SAR ADC with Calibration-Less Switched Capacitive Reference Driver. Electronics 2020, 9, 1854. [Google Scholar] [CrossRef]

- Harikumar, P.; Wikner, J.J. Design of a Reference Voltage Buffer for a 10-Bit 50 MS/s SAR ADC in 65 nm CMOS. In Proceedings of the IEEE International Symposium on Circuits and Systems, Lisbon, Portugal, 24 May 2015. [Google Scholar]

- Shehzad, K.; Verma, D.; Khan, D.; Ain, Q.U.; Basim, M.; Kim, S.J.; Pu, Y.; Hwang, K.C.; Yang, Y.; Lee, K.-Y. Design of a Low Power 10-b 8-MS/s Asynchronous SAR ADC with On-Chip Reference Voltage Generator. Electronics 2020, 9, 872. [Google Scholar] [CrossRef]

- Jeon, Y.-D.; Nam, J.-W.; Kim, K.-D.; Roh, T.M.; Kwon, J.-K. A Dual-Channel Pipelined ADC with Sub-ADC Based on Flash–SAR Architecture. IEEE Trans. Circuits Syst. II Express Briefs 2012, 59, 741–745. [Google Scholar] [CrossRef]

- Lee, K.H.; Kim, K.S.; Lee, S.H. A 12 b 50 MS/s 21.6 mW 0.18 μm CMOS ADC Maximally Sharing Capacitors and Op-Amps. IEEE Trans. Circuits Syst. I Regul. Pap. 2011, 58, 2127–2136. [Google Scholar]

- Sun, L.; Ko, C.T.; Pun, K.P. Optimizing the Stage Resolution in Pipelined SAR ADCs for High-Speed High-Resolution Appli-cations. IEEE Trans. Circuits Syst. II Express Briefs 2014, 61, 476–480. [Google Scholar] [CrossRef]

- Wu, Y.; Lan, J.; Chen, M.; Ye, F.; Ren, J. A 16-channel 50MS/s 14bit Pipelined-SAR ADC for Integrated Ultrasound Imaging Systems. In Proceedings of the 2020 IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), Ha Long, Vietnam, 8–10 December 2020; pp. 3–6. [Google Scholar] [CrossRef]

- Chiu, Y.; Gray, P.; Nikolic, B. A 14-b 12-MS/s CMOS pipeline ADC with over 100-dB SFDR. IEEE J. Solid-State Circuits 2004, 39, 2139–2151. [Google Scholar] [CrossRef]

- Xu, H.; Member, S.; Huang, H.; Cai, Y.; Du, L.; Zhou, Y.; Member, S. A 78.5-dB SNDR Radiation- and Metastability- Tolerant Two-Step Split SAR ADC Operating Up to 75 MS/s with 24.9-mW Power Consumption in 65-nm CMOS. IEEE J. Solid-State Circuits 2019, 54, 441–451. [Google Scholar] [CrossRef]

- Wang, R.; Chio, U.-F.; Sin, S.-W.; Seng-Pan, U.; Wang, Z.; Martins, R.P. A 12-bit 110MS/s 4-stage single-opamp pipelined SAR ADC with ratio-based GEC technique. In Proceedings of the European Solid-State Circuits Conference, Bordeaux, France, 17 September 2012; pp. 265–268. [Google Scholar]

- Zheng, X.; Wang, Z.; Li, F.; Zhao, F.; Yue, S.; Zhang, C.; Wang, Z. A 14-bit 250 MS/s IF Sampling Pipelined ADC in 180 nm CMOS Process. IEEE Trans. Circuits Syst. I Regul. Pap. 2016, 63, 1381–1392. [Google Scholar] [CrossRef] [Green Version]

- Mao, J.; Guo, M.; Sin, S.-W.; Martins, R.P. A 14-Bit Split-Pipeline ADC with Self-Adjusted Opamp-Sharing Duty-Cycle and Bias Current. IEEE Trans. Circuits Syst. II Express Briefs 2018, 65, 1380–1384. [Google Scholar] [CrossRef]

- Miyahara, Y.; Sano, M.; Koyama, K.; Suzuki, T.; Hamashita, K.; Song, B.-S. A 14b 60 MS/s Pipelined ADC Adaptively Cancelling Opamp Gain and Nonlinearity. IEEE J. Solid-State Circuits 2013, 49, 416–425. [Google Scholar] [CrossRef]

- Kim, T.; Shin, S.; Kim, S. An 80.2 dB DR 23.25 mW/Channel 8-Channel Ultrasound Receiver with a Beamforming Embedded SAR ADC. IEEE Trans. Circuits Syst. II Express Briefs 2018, 66, 1487–1491. [Google Scholar] [CrossRef]

- Chirala, M.K.; Huynh, P.; Ryu, J.; Kim, Y.H. A 128-ch Δ-Σ ADC Based Mixed Signal IC for Full Digital Beamforming Wireless Handheld Ultrasound Imaging System. In Proceedings of the Annual International Conference of the IEEE Engineering in Medicine and Biology Society, Milan, Italy, 25 August 2015. [Google Scholar]

| Architecture | Resolution Distribution (ki) * | Case No. | Number of Op-Amp (Nop) | Number of References (Nref) | ||

|---|---|---|---|---|---|---|

| Original | With Op-amp Sharing | Original | With Reference Sharing | |||

| 2-stage PPL-SAR | 6b + 9b [32] | i | 1 | 1 | 2 | 2 |

| 7b + 8b [21] | ii | 1 | 1 | 2 | 2 | |

| 3-stage PPL-SAR | 4b + 4b + 8b | iii | 2 | 1 | 3 | 2 |

| 5b + 5b + 6b (this work) | iv | 2 | 1 | 3 | 2 | |

| 4-stage PPL-SAR | 4b × 3 + 5b [33] | v | 3 | 1 | 4 | 3 |

| Circuit Block | Range of Area (A/Aunit) | Range of Power (P/Punit) |

|---|---|---|

| Residue Amplifier * | 100–400 | 10–200 |

| Reference * | 200–400 | 100–500 |

| [32] | [35] | [36] | [37] | [38] | This Work | |

|---|---|---|---|---|---|---|

| Technology | 65 nm | 65 nm | 180 nm | 180 nm | 130 nm | 180 nm |

| Architecture | Pipelined-SAR | Split-Pipeline | Pipeline | SAR | Sigma-Delta | Pipelined-SAR |

| Number of Channels | 1 | 1 | 1 | 8 | 128 | 16 |

| Sampling Rate (MS/s) | 75 | 100 | 60 | 20 | 20 | 50 |

| Resolution (bit) | 14 | 14 | 14 | 12 | 12 | 14 |

| SNDR (dB) | 77.8 | 68.5 | 76.9 | 58.2 | 65 | 68.25 |

| SFDR (dB) | 92.1 | 84.4 | 91.2 | N/A | 58 | 82.19 |

| Power/channel a (mW) | 24.9 | 32 | 67.8 | 2.6 | 17 | 49.5 |

| Area/channel (mm2) | 0.342 b | 0.38 | 1.43 | 0.26 | N/A | 0.625 b |

| FoM c (pJ/conv-step) | 0.052 | 0.147 | 0.198 | 0.196 | 0.585 | 0.469 |

| Calibration | Background | Background | Background LMS | Beam- forming | Background | Not required |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wu, Y.; Ye, F.; Ren, J. A Calibration-Free, 16-Channel, 50-MS/s, 14-Bit, Pipelined-SAR ADC with Reference/Op-Amp Sharing and Optimized Stage Resolution Distribution. Electronics 2022, 11, 749. https://doi.org/10.3390/electronics11050749

Wu Y, Ye F, Ren J. A Calibration-Free, 16-Channel, 50-MS/s, 14-Bit, Pipelined-SAR ADC with Reference/Op-Amp Sharing and Optimized Stage Resolution Distribution. Electronics. 2022; 11(5):749. https://doi.org/10.3390/electronics11050749

Chicago/Turabian StyleWu, Yimin, Fan Ye, and Junyan Ren. 2022. "A Calibration-Free, 16-Channel, 50-MS/s, 14-Bit, Pipelined-SAR ADC with Reference/Op-Amp Sharing and Optimized Stage Resolution Distribution" Electronics 11, no. 5: 749. https://doi.org/10.3390/electronics11050749