Design of a Dual Change-Sensing 24T Flip-Flop in 65 nm CMOS Technology for Ultra Low-Power System Chips

Abstract

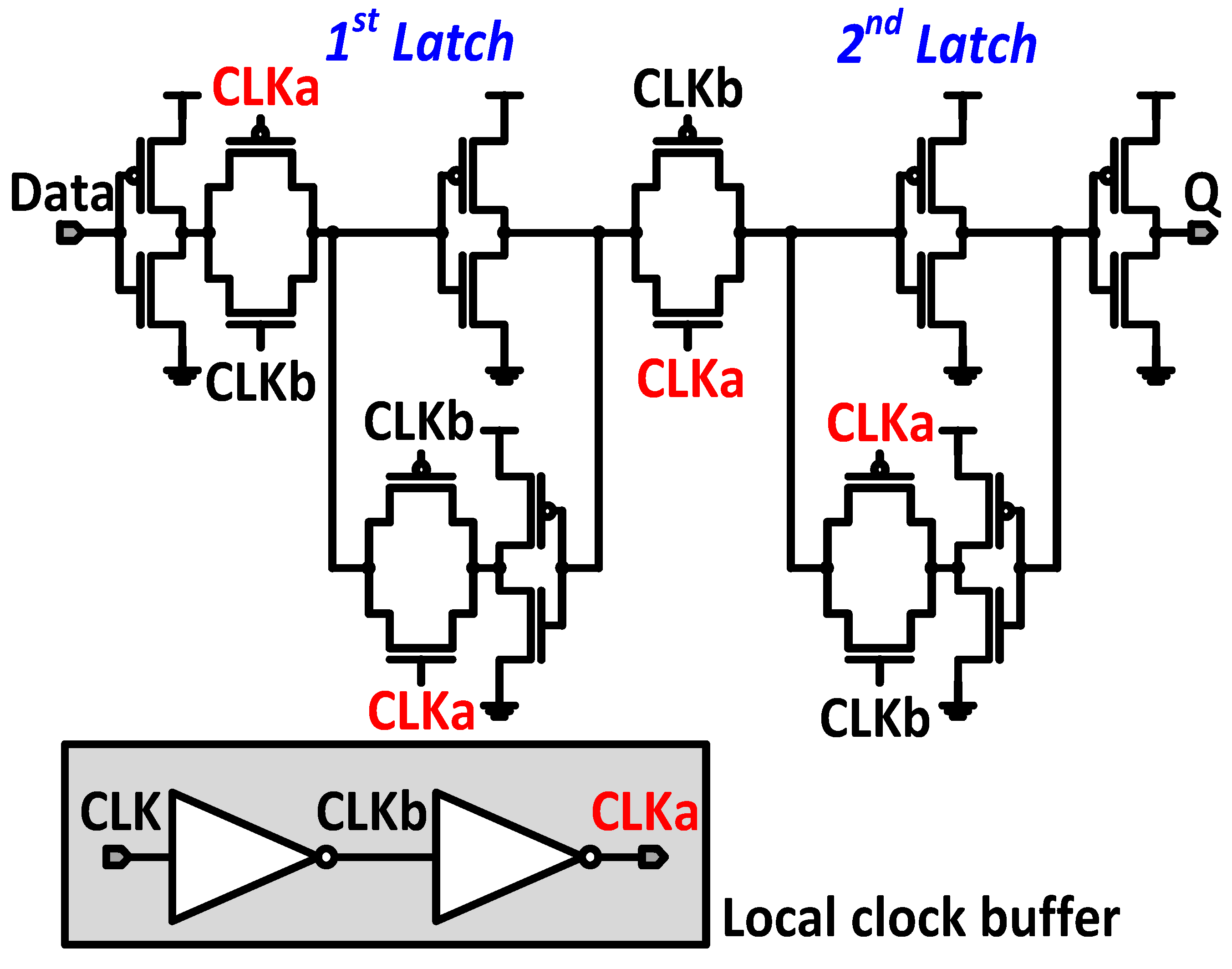

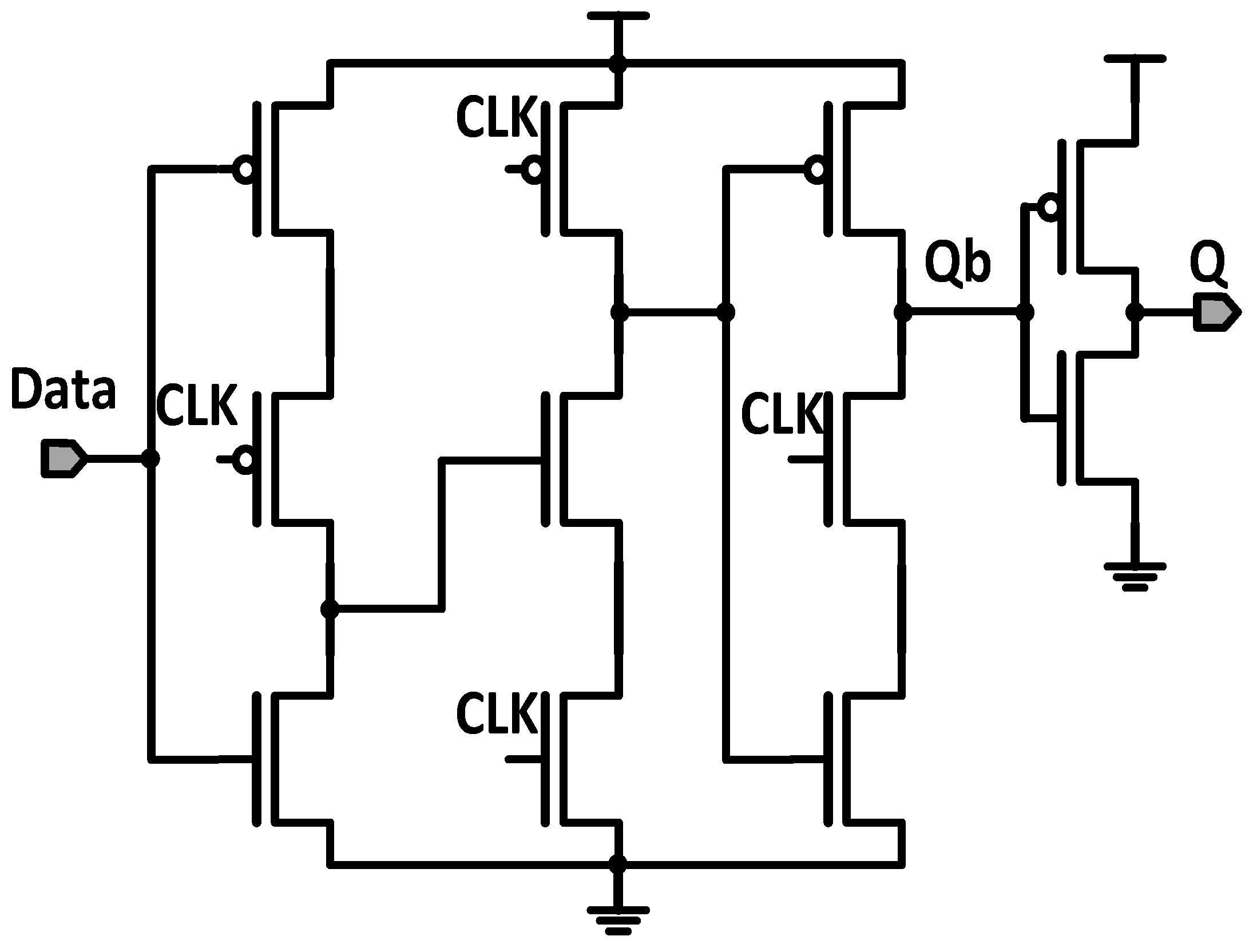

:1. Introduction

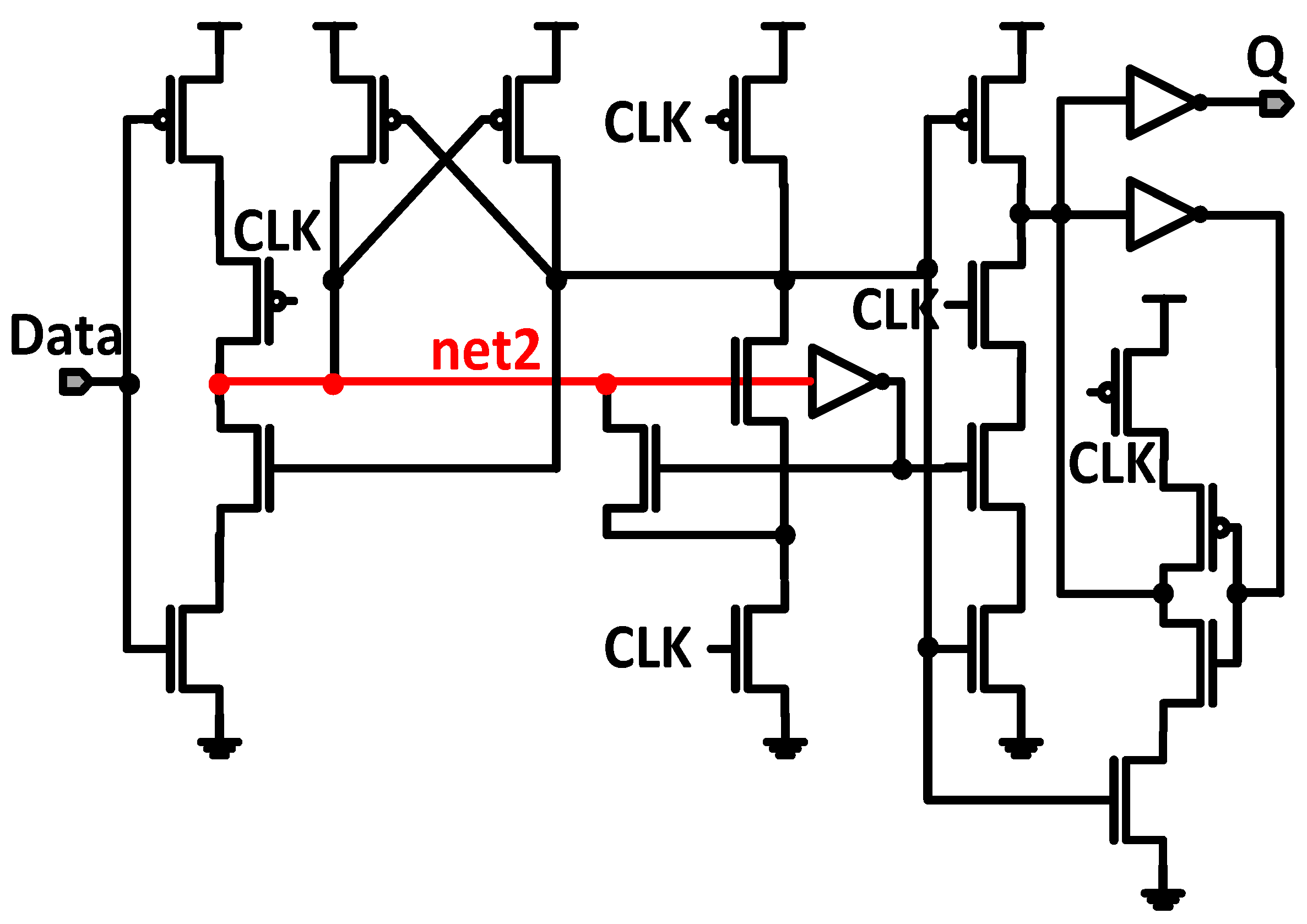

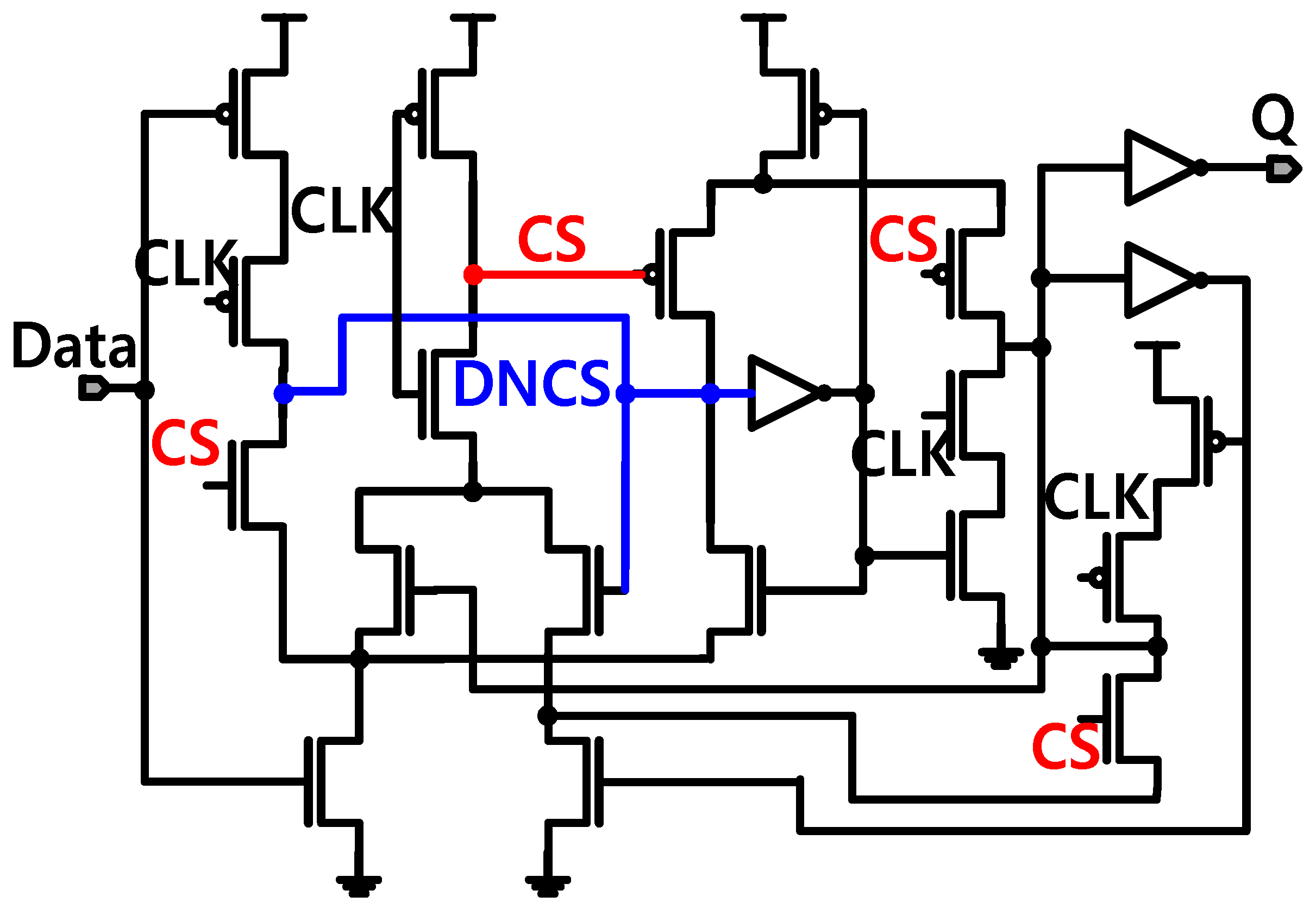

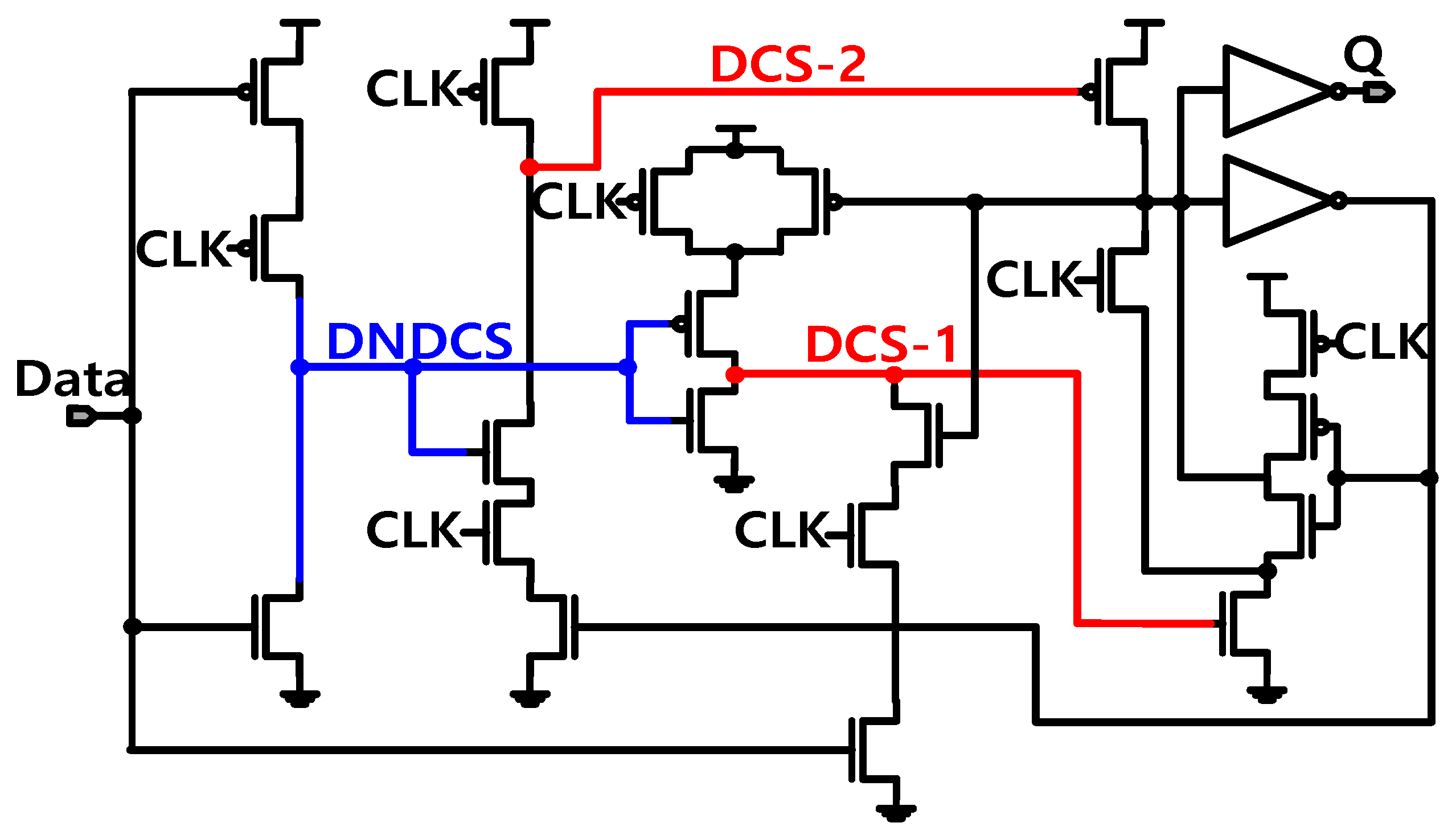

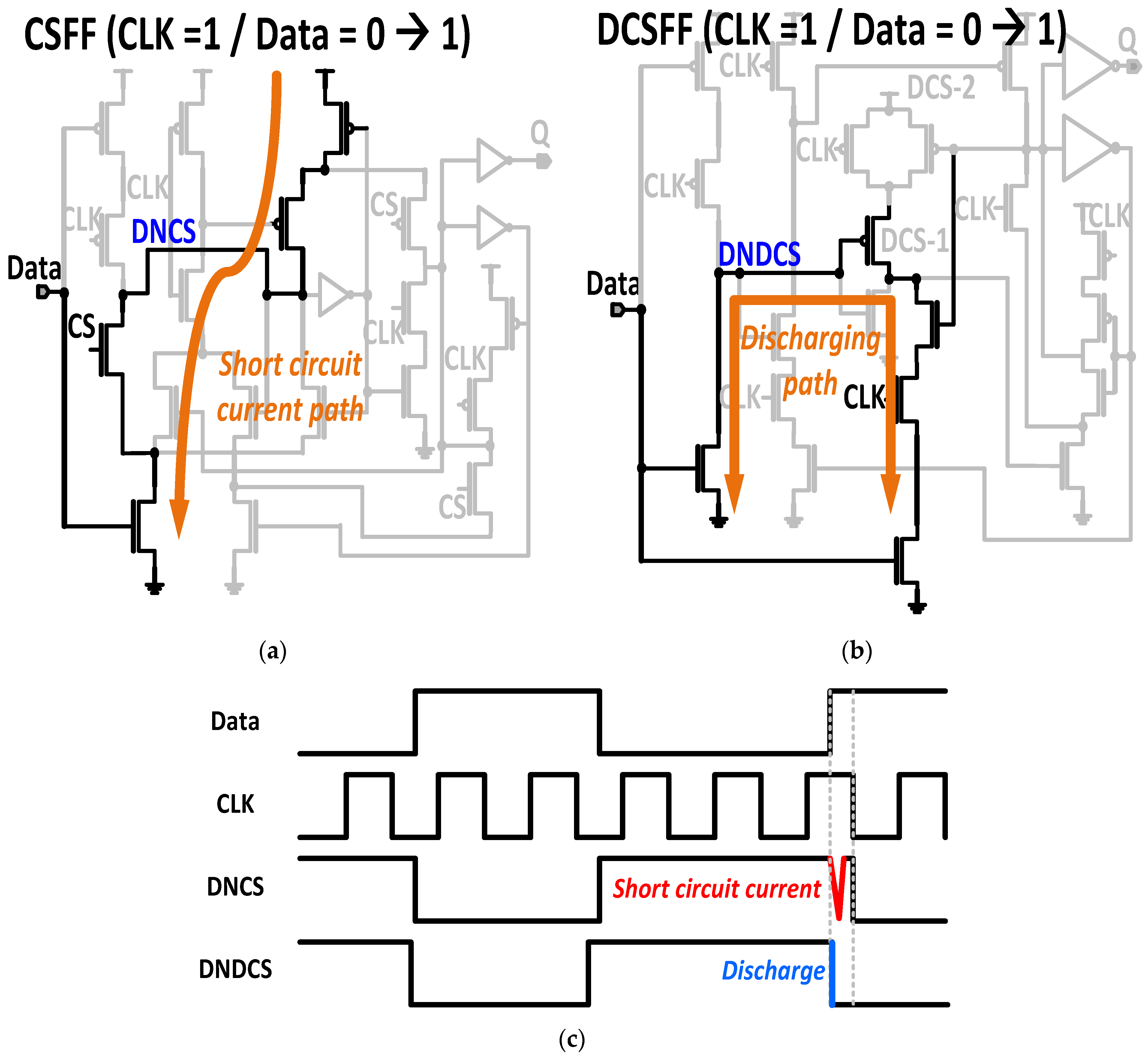

2. Proposed Dual Change-Sensing Flip-Flop (DCSFF)

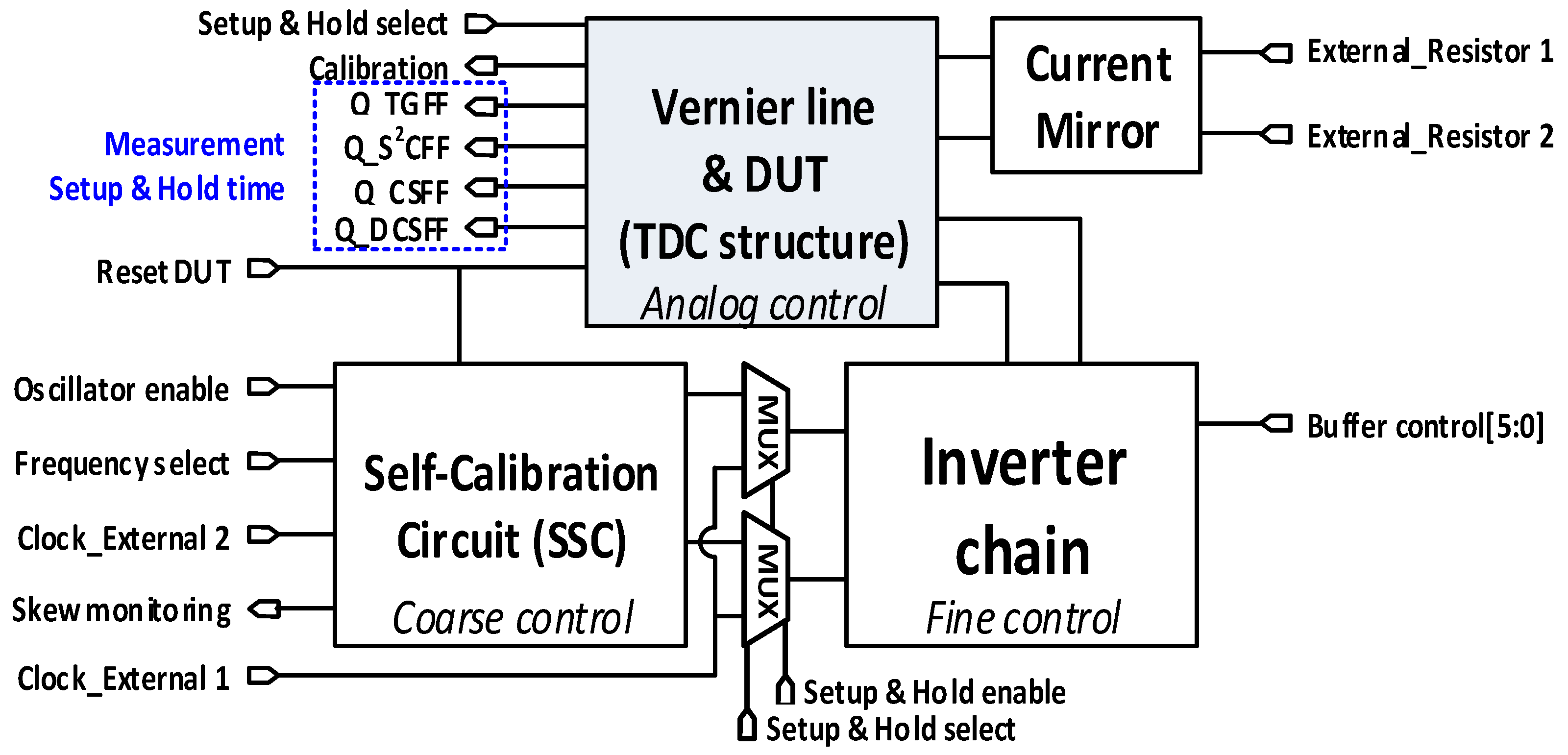

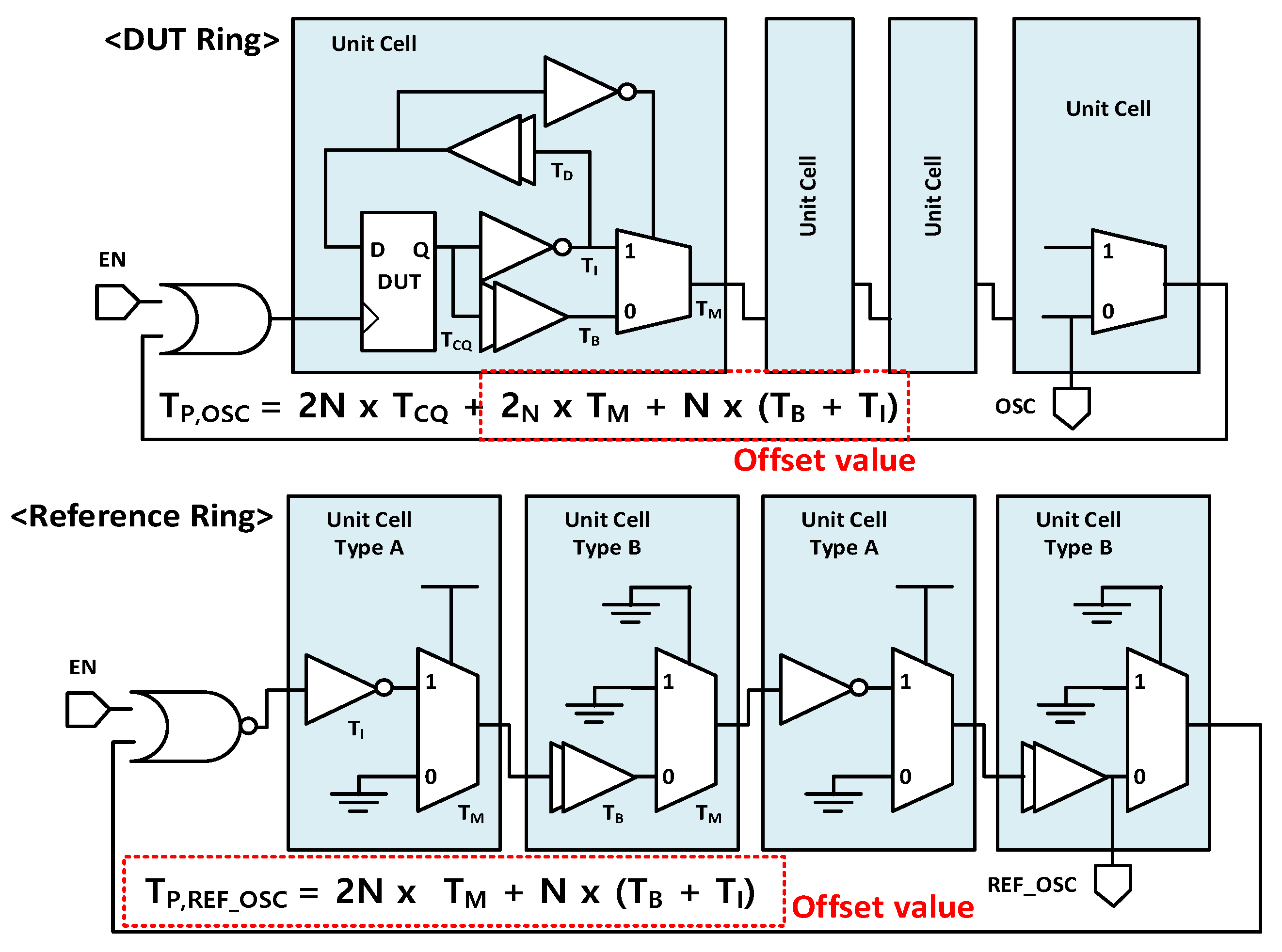

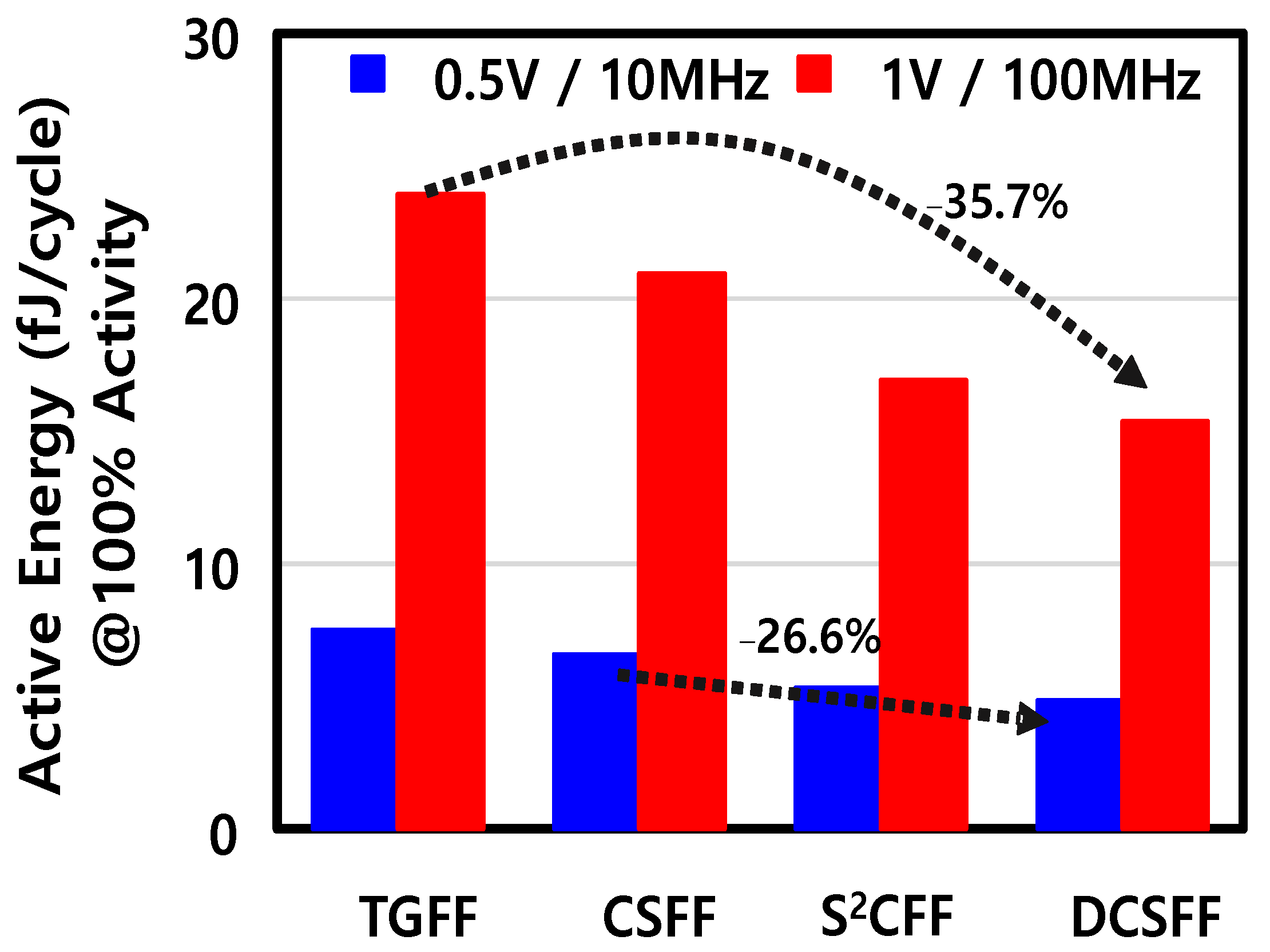

3. Measured Results

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Yuan, J.; Hwang, B. High-Speed CMOS Circuit Technique. IEEE J. Solid-State Circuits 1989, 24, 62–70. [Google Scholar] [CrossRef] [Green Version]

- Shin, J.L.; Golla, R.; Li, H.; Dash, S.; Choi, Y.; Smith, A.; Sathianathan, H.; Joshi, M.; Park, H.; Elgebaly, M.; et al. The Next Generation 64b SPARC Core in a T4 SoC Processor. IEEE J. Solid-State Circuits 2013, 48, 82–90. [Google Scholar] [CrossRef]

- Markovic, D.; Tschanz, J.W.; De, V.K. Transmission-Gate Based Flip-Flop. U.S. Patent 6,642,765, 4 November 2003. [Google Scholar]

- Teh, C.K.; Fujita, T.; Hara, H.; Hamada, M. A 77% Energy-Saving 22-Transistor Single-Phase Clocking D-Flip-Flop with Adaptive-Coupling Configuration in 40nm CMOS. In Proceedings of the 2011 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 20–24 February 2011; pp. 338–339. [Google Scholar]

- Kim, Y.; Shin, B. A static contention-free single-phase-clocked 24T flip-flop in 45nm for low-power applications. In Proceedings of the 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 9–13 February 2014; pp. 466–467. [Google Scholar]

- Le, V.L.; Li, J.; Chang, A.; Kim, T.H. A 0.4-V, 0.138-fJ/cycle single-phase-clocking redundant-transition-free 24T flip-flop with change-sensing scheme in 40-nm CMOS. IEEE J. Solid-State Circuits 2018, 53, 2806–2817. [Google Scholar] [CrossRef]

- Stojanovic, V.; Oklobdzija, V.G. Comparative analysis of masters-lave latches and flip-flops for high-performance and low-power systems. IEEE J. Solid-State Circuits 1999, 34, 536–548. [Google Scholar] [CrossRef]

- Alioto, M.; Consoli, E.; Palumbo, G. Variations in nanometer CMOS flip-flops: Part I—Impact of process variations on timing. IEEE Trans. Circuits Syst. I Regul. Pap. 2015, 62, 2035–2043. [Google Scholar] [CrossRef]

- Cai, Y.; Savanth, A.; Prabhat, P.; Myers, J.; Weddell, A.S.; Kazmierski, T.J. Ultra-low power 18-transistor fully static contention-free single-phase clocked flip-flop in 65-nm CMOS. IEEE J. Solid-State Circuits 2019, 54, 550–559. [Google Scholar] [CrossRef]

- Kawai, N.; Ishinura, M. A fully static topologically-compressed 21-transistor flip-flop with 75% power saving. IEEE J. Solid-State Circuits 2014, 49, 2526–2533. [Google Scholar] [CrossRef]

- Le, V.L.; Li, J.; Chang, A.; Kim, T.H. An 82% energy-saving change-sensing flip-flop in 40 nm CMOS for ultra-low power applications. In Proceedings of the 2017 IEEE Asian Solid-State Circuits Conference (A-SSCC), Seoul, Korea, 6–8 November 2017; pp. 197–200. [Google Scholar]

- Shin, G.; Lee, E.; Lee, J.; Lee, Y.; Lee, Y. A redundancy eliminated flip-flop in 28 nm for low-voltage low-power applications. IEEE Solid-State Circuits Lett. 2020, 3, 446–449. [Google Scholar] [CrossRef]

- Kuamar, H.; Nagarajan, R. Low Power High Speed 15-Transistor Static True Single Phase Flip Flop. In Proceedings of the 2nd International Conference on Intelligent Computing, Instrumentation and Control Technologies (ICICICT), Kannur, India, 5–6 July 2019; pp. 440–444. [Google Scholar]

- Lee, Y.; Shin, G.; Lee, Y. A Fully Static True-Single-Phase-Clocked Dual-Edge-Triggered Flip-Flop for Near-Threshold Voltage Operation in IoT Applications. IEEE Access 2020, 8, 40232–40245. [Google Scholar] [CrossRef]

- Huang, Y.; Jiao, H. An Ultra-Low-Voltage Single-Phase Adaptive Pulse Latch with Redundant Toggling Elimination. In Proceedings of the IEEE 15th International Conference on Solid-State & Integrated Circuit Technology (ICSICT), Kunming, China, 3–6 November 2020; pp. 1–3. [Google Scholar]

- Shin, G.; Lee, E.; Lee, J.; Lee, Y.; Lee, Y. An Ultra-Low-Power Fully-Static Contention-Free Flip-Flop With Complete Redundant Clock Transition and Transistor Elimination. IEEE J. Solid-State Circuits 2021, 56, 3039–3048. [Google Scholar] [CrossRef]

- Zhihong, L.; Yihao, Z.; Law, H. Self-calibrate two-step digital setup/hold time measurement. In Proceedings of the 2010 International Symposium on VLSI Design, Automation and Test, Hsin Chu, Taiwan, 26–29 April 2010; pp. 232–235. [Google Scholar]

- Giridhar, B.; Peterson, W. Pulse Amplification Based Dynamic Synchronizers with Meta-stability Measurement using Capacitance De-rating. In Proceedings of the IEEE 2013 Custom Integrated Circuits Conference, San Jose, CA, USA, 22–25 September 2013; pp. 110–113. [Google Scholar]

- Zhai, B.; Dreslinski, R.G.; Blaauw, D.; Mudge, T.; Sylvester, D. Energy efficient near-threshold chip multi-processing. In Proceedings of the 2007 International Symposium on Low Power Electronics and Design (ISLPED ’07), Portland, OR, USA, 27–29 August 2007; pp. 32–37. [Google Scholar]

- Wang, A.; Calhoun, B.; Chandrakasan, A. Sub-Threshold Design for Ultra Low-Power Systems; Springer: New York, NY, USA, 2006. [Google Scholar]

| Performance | DCSFF | TGFF [3] | SSCFF [5] | CSFF [6] |

| Contention-free | YES | YES | YES | NO |

| Number of Transistor | 24 | 24 | 24 | 24 |

| Single Phase Clock | YES | NO | YES | YES |

| Layout Size (relative size) | 1.04 | 1 | 1.05 | 1.13 |

| Measured C-Q Delay @1.2 V (ps) | 112.7 | 150.6 | 140.6 | 128.9 |

| Measured Setup Time @1.2 V (ps) | 216 | 165 | 186 | 197 |

| Measured Hold Time @1.2 V (ps) | 49 | 55 | 46 | 34 |

| Measured Power @ 1.2 V, 100 MHz, 20%/100% (μW) | 0.37/1.54 | 1.72/2.39 | 1.49/1.69 | 0.48/2.09 |

| Measured Power @ 0.5 V, 10 MHz, 20%/100% (μW) | 0.013/0.048 | 0.058/0.075 | 0.051/0.053 | 0.016/0.066 |

| Measured Leakage@1.2 V (μW) | 0.084 | 1.555 | 1.435 | 0.079 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Park, J.-Y.; Jin, M.; Kim, S.-Y.; Song, M. Design of a Dual Change-Sensing 24T Flip-Flop in 65 nm CMOS Technology for Ultra Low-Power System Chips. Electronics 2022, 11, 877. https://doi.org/10.3390/electronics11060877

Park J-Y, Jin M, Kim S-Y, Song M. Design of a Dual Change-Sensing 24T Flip-Flop in 65 nm CMOS Technology for Ultra Low-Power System Chips. Electronics. 2022; 11(6):877. https://doi.org/10.3390/electronics11060877

Chicago/Turabian StylePark, Jun-Young, Minhyun Jin, Soo-Youn Kim, and Minkyu Song. 2022. "Design of a Dual Change-Sensing 24T Flip-Flop in 65 nm CMOS Technology for Ultra Low-Power System Chips" Electronics 11, no. 6: 877. https://doi.org/10.3390/electronics11060877

APA StylePark, J.-Y., Jin, M., Kim, S.-Y., & Song, M. (2022). Design of a Dual Change-Sensing 24T Flip-Flop in 65 nm CMOS Technology for Ultra Low-Power System Chips. Electronics, 11(6), 877. https://doi.org/10.3390/electronics11060877