The Design Considerations and Challenges in MOS-Based Temperature Sensors: A Review

Abstract

:1. Introduction

2. Subtypes of MOS-Based Temperature Sensors

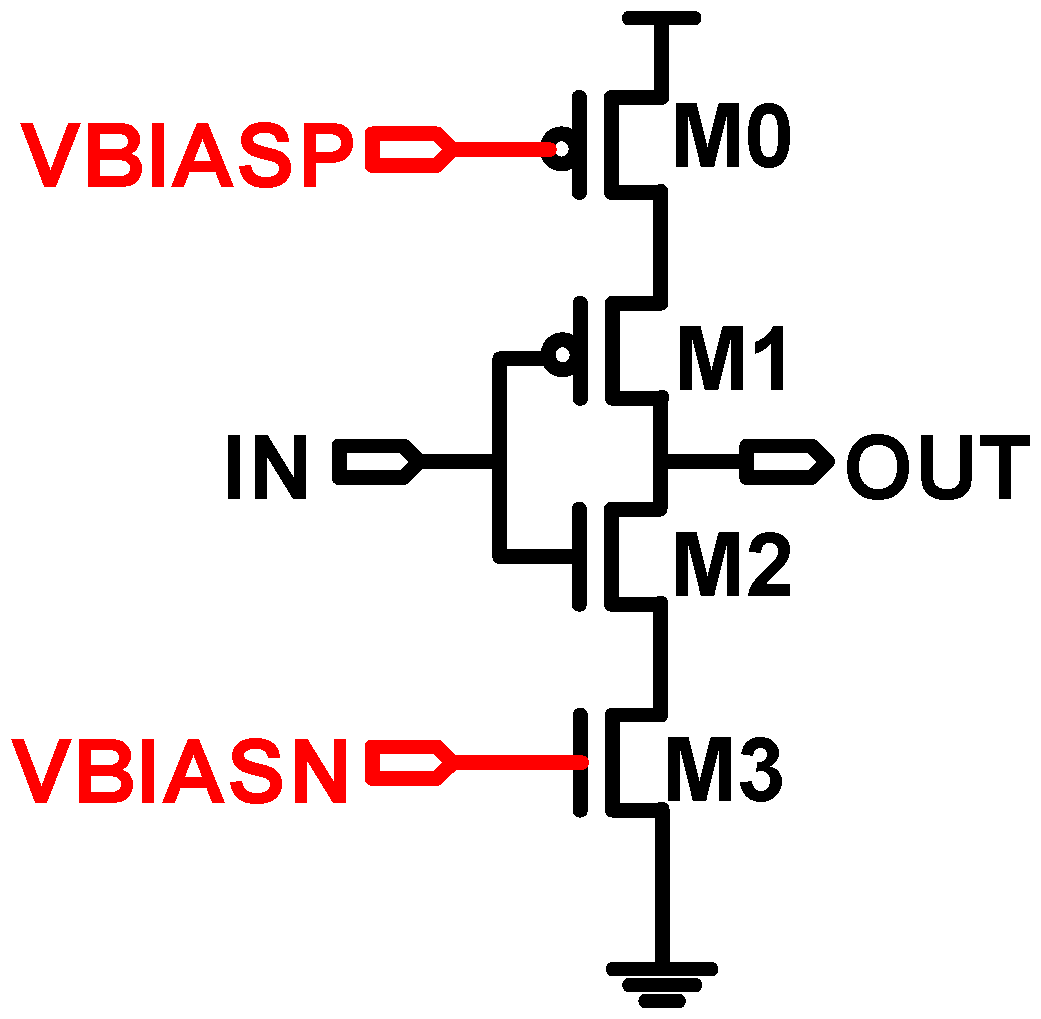

2.1. The Logic, Saturation and Linear MOS-Based Temperature Sensors (Type I)

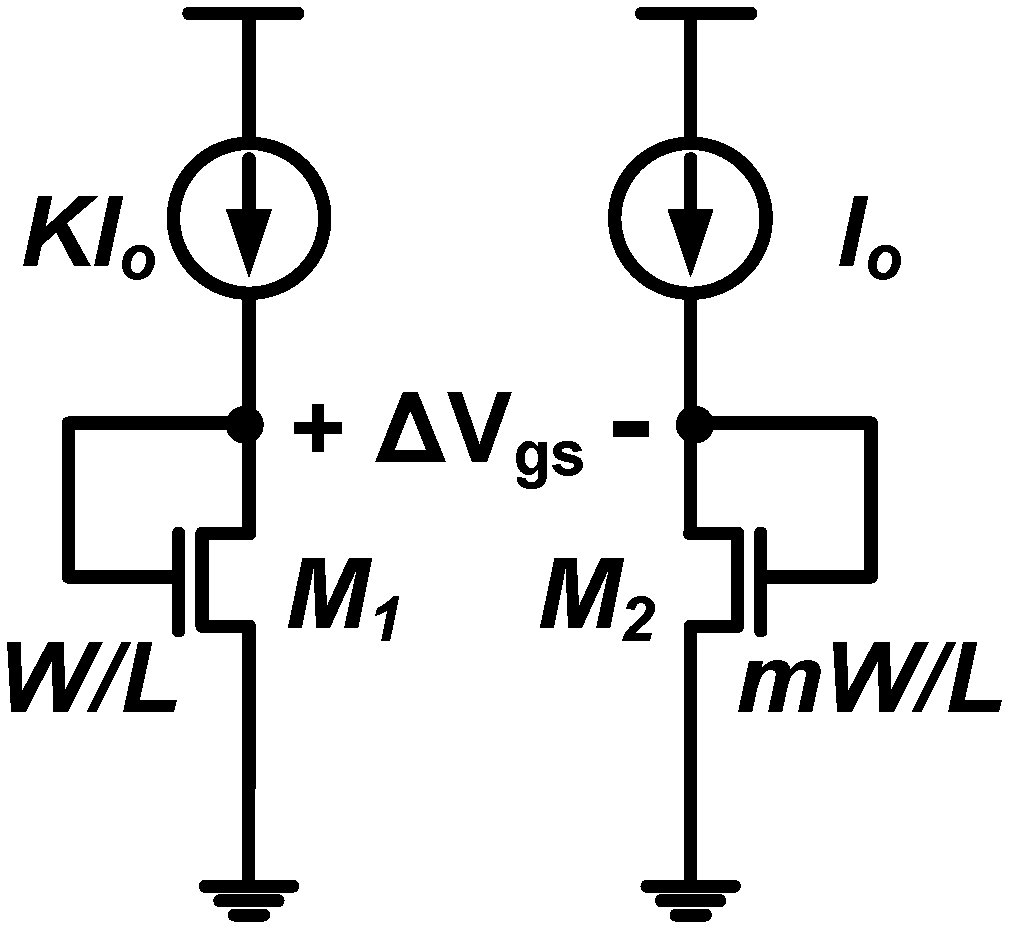

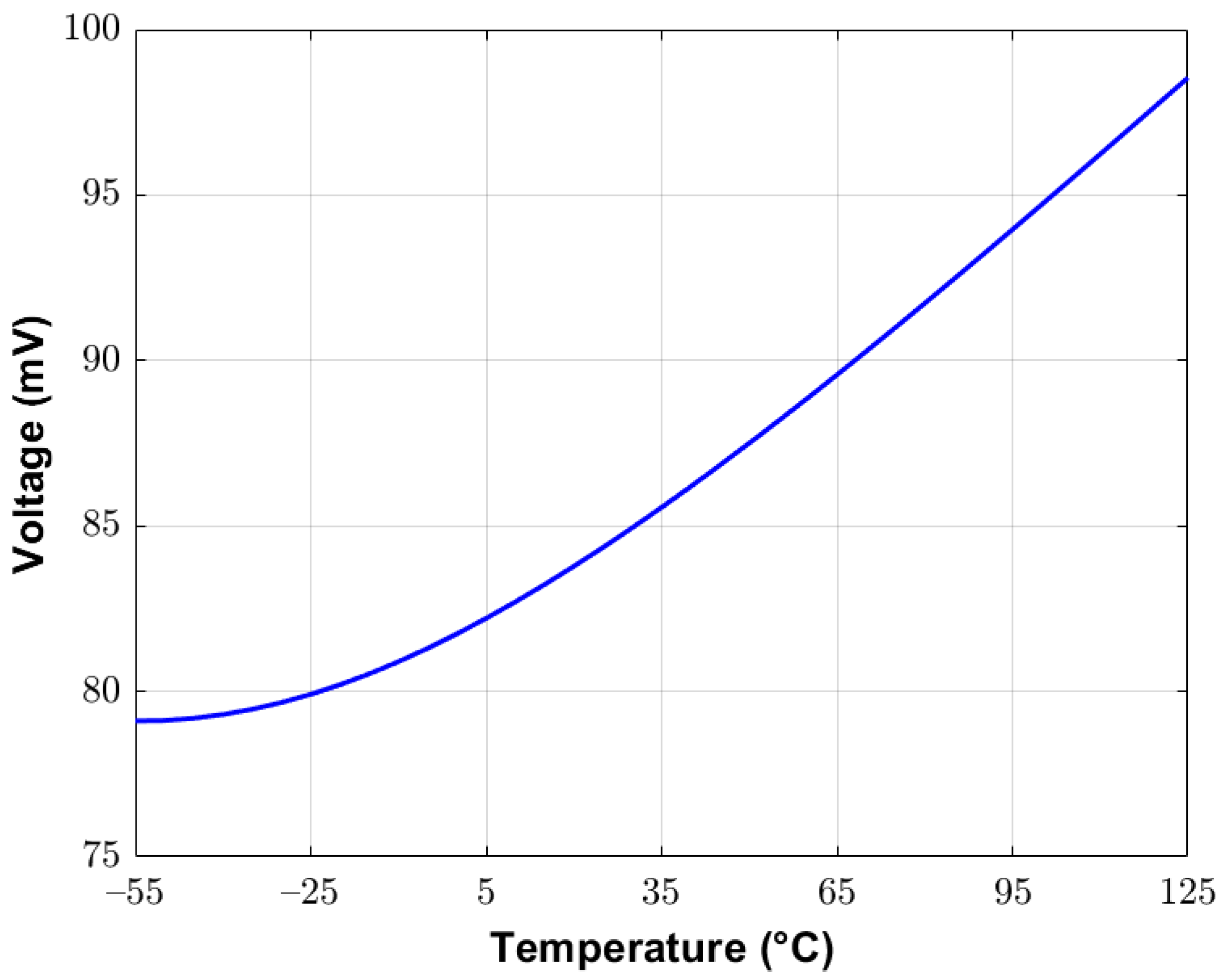

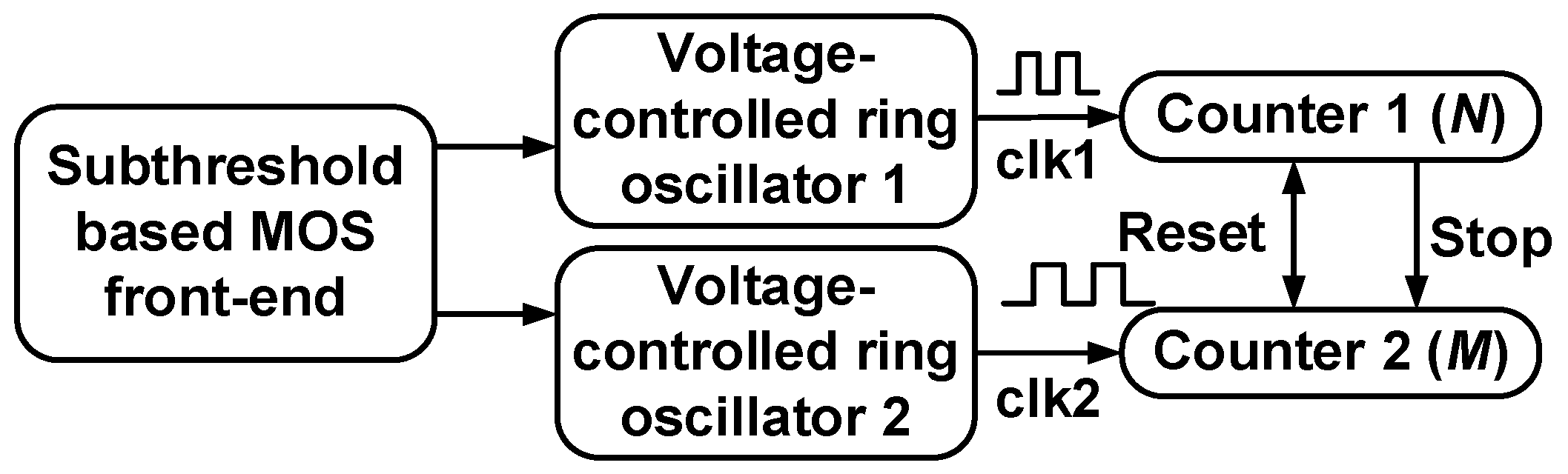

2.2. Subthreshold MOS-Based Temperature Sensor (Type II)

2.3. Gate Leakage-Based Temperature Sensors (Type III)

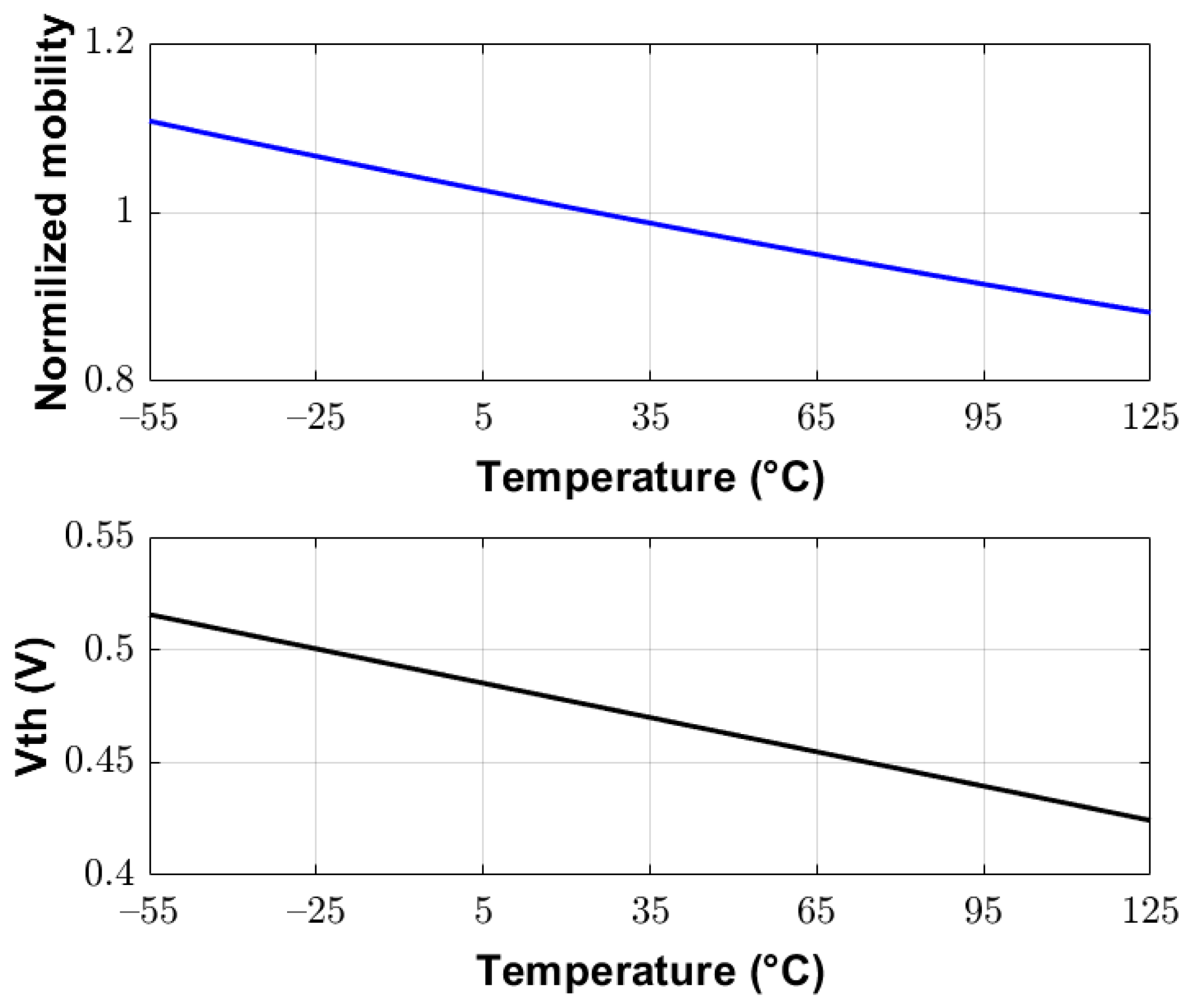

3. Design Considerations and Challenges for the MOS-Based Temperature Sensors

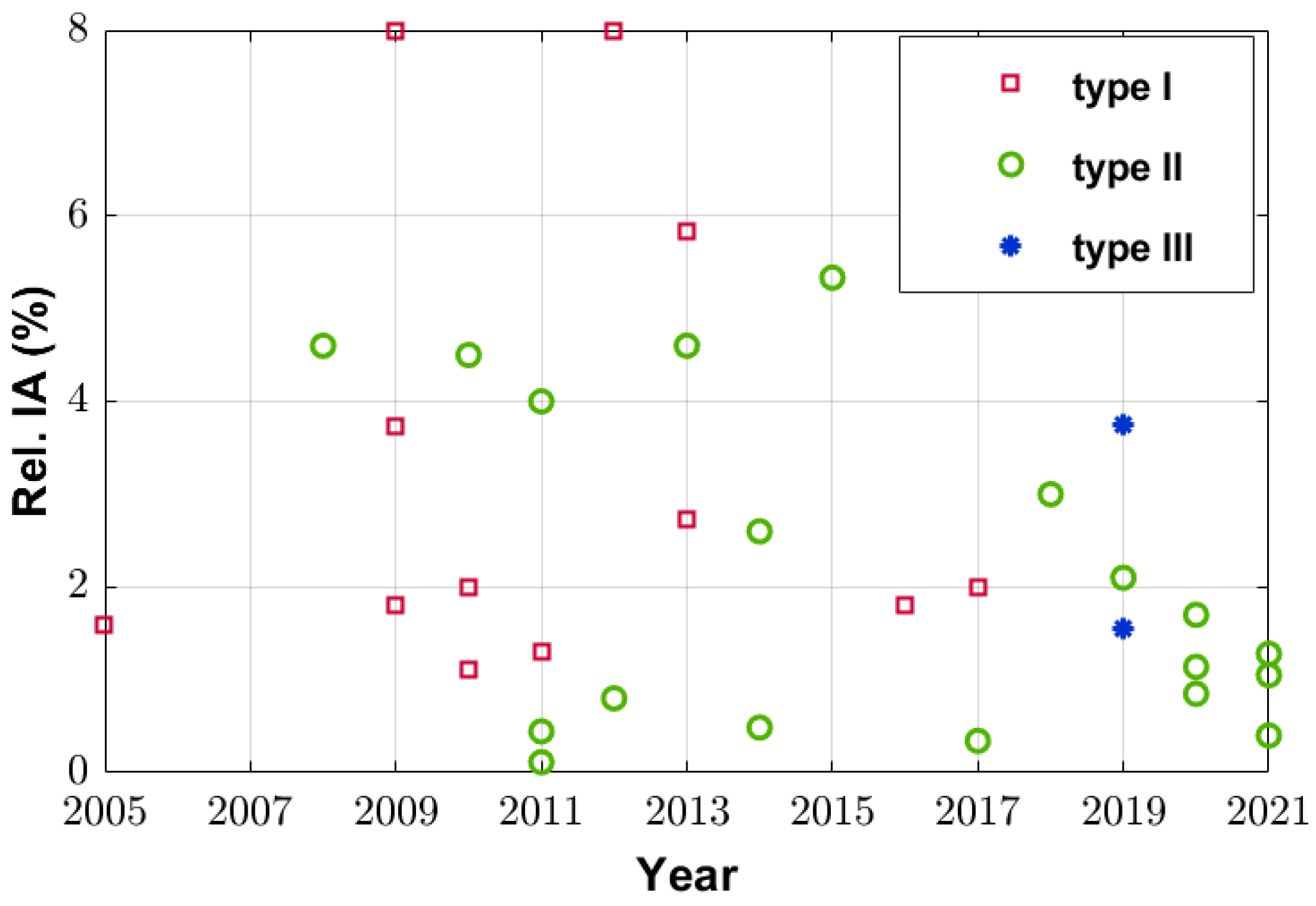

3.1. The Type of Choice Versus Year of Publication

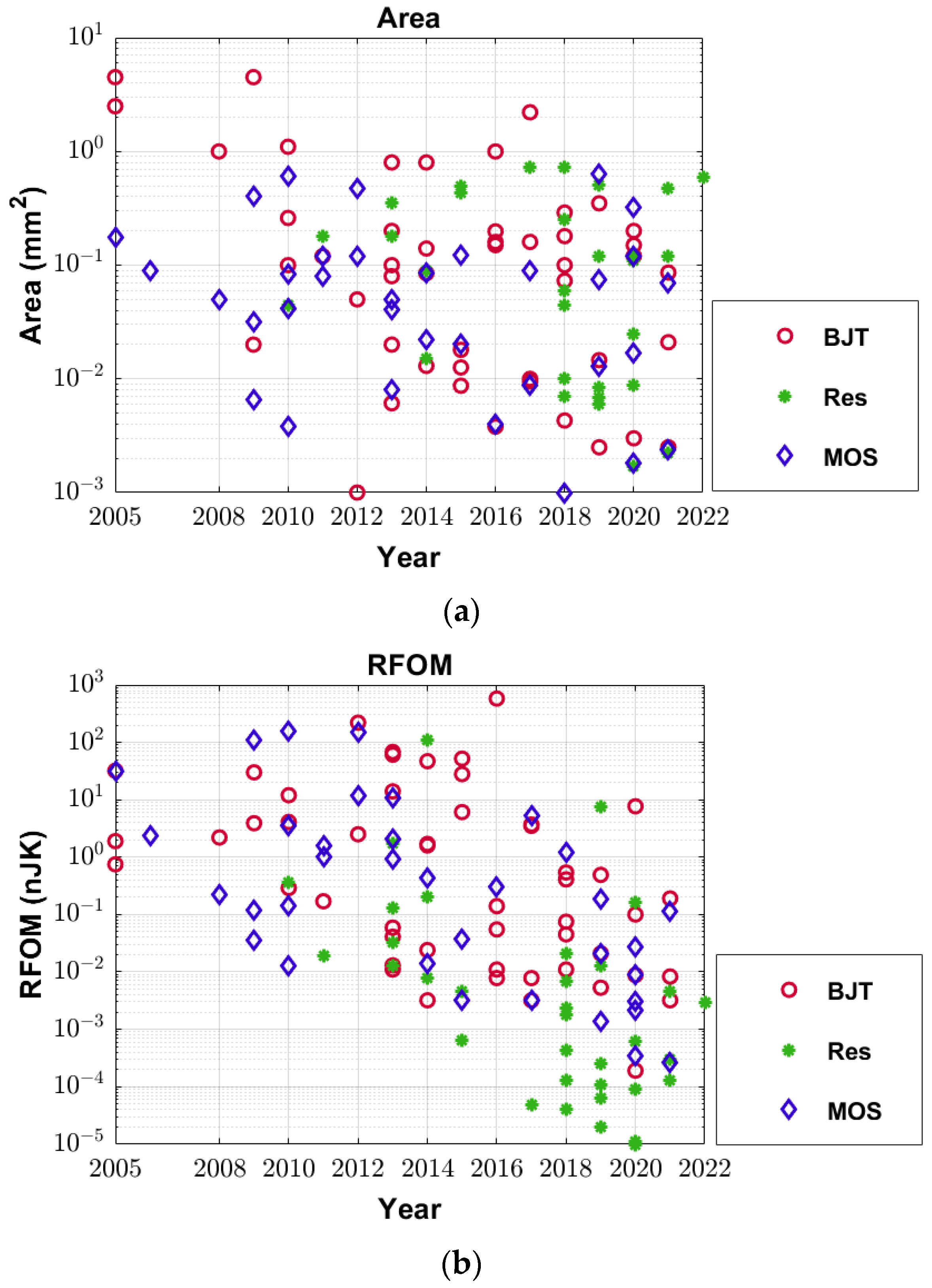

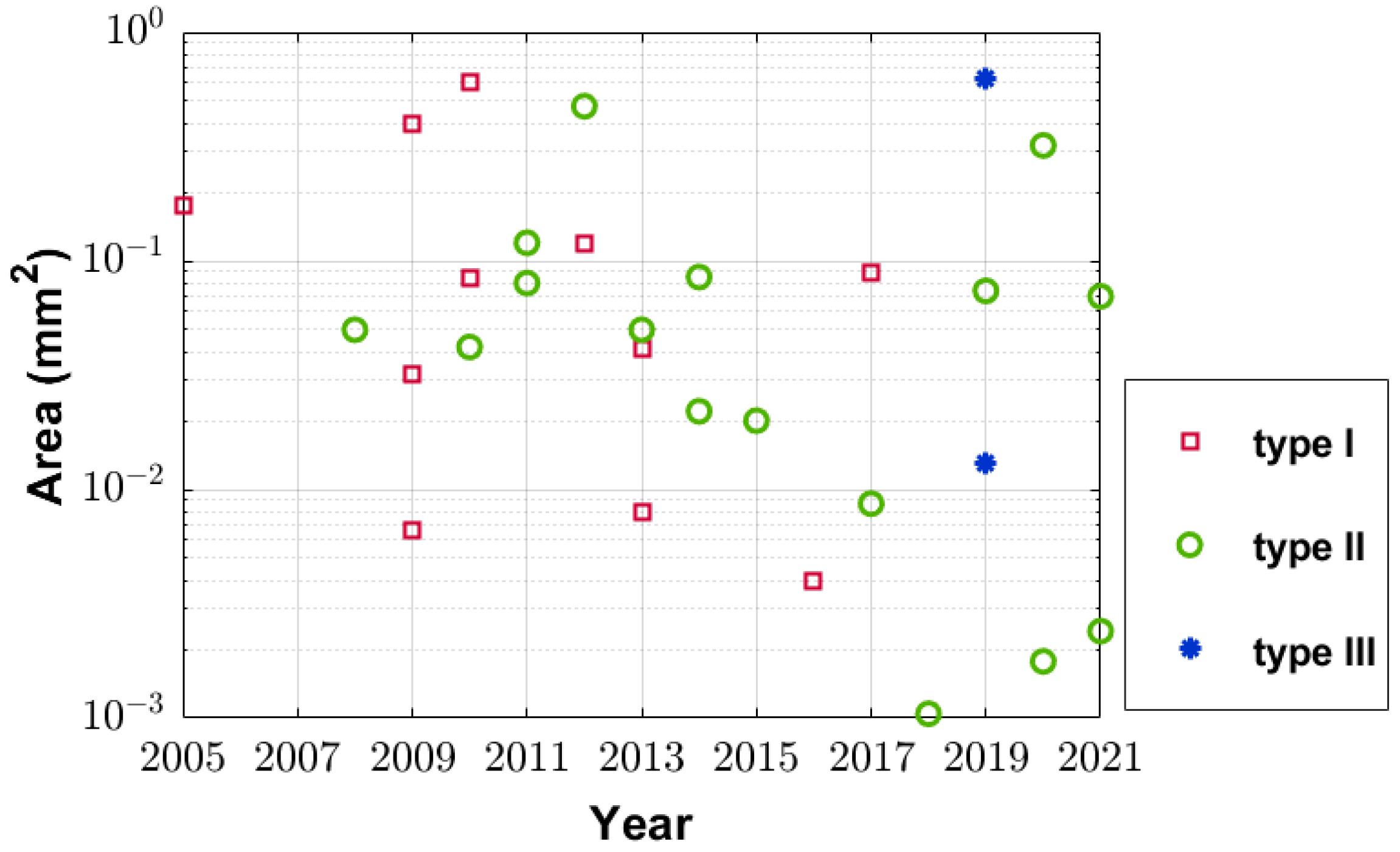

3.2. Area

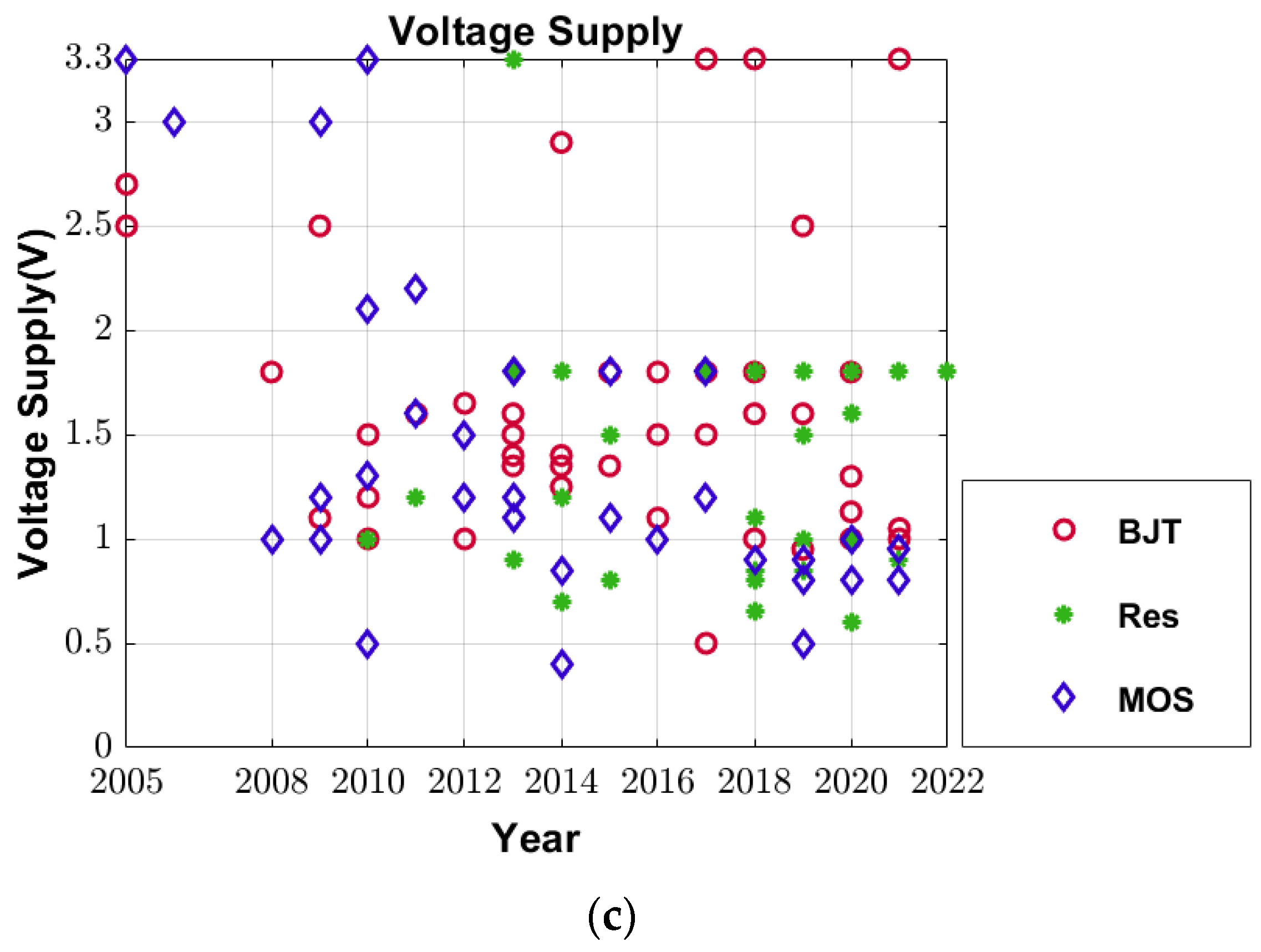

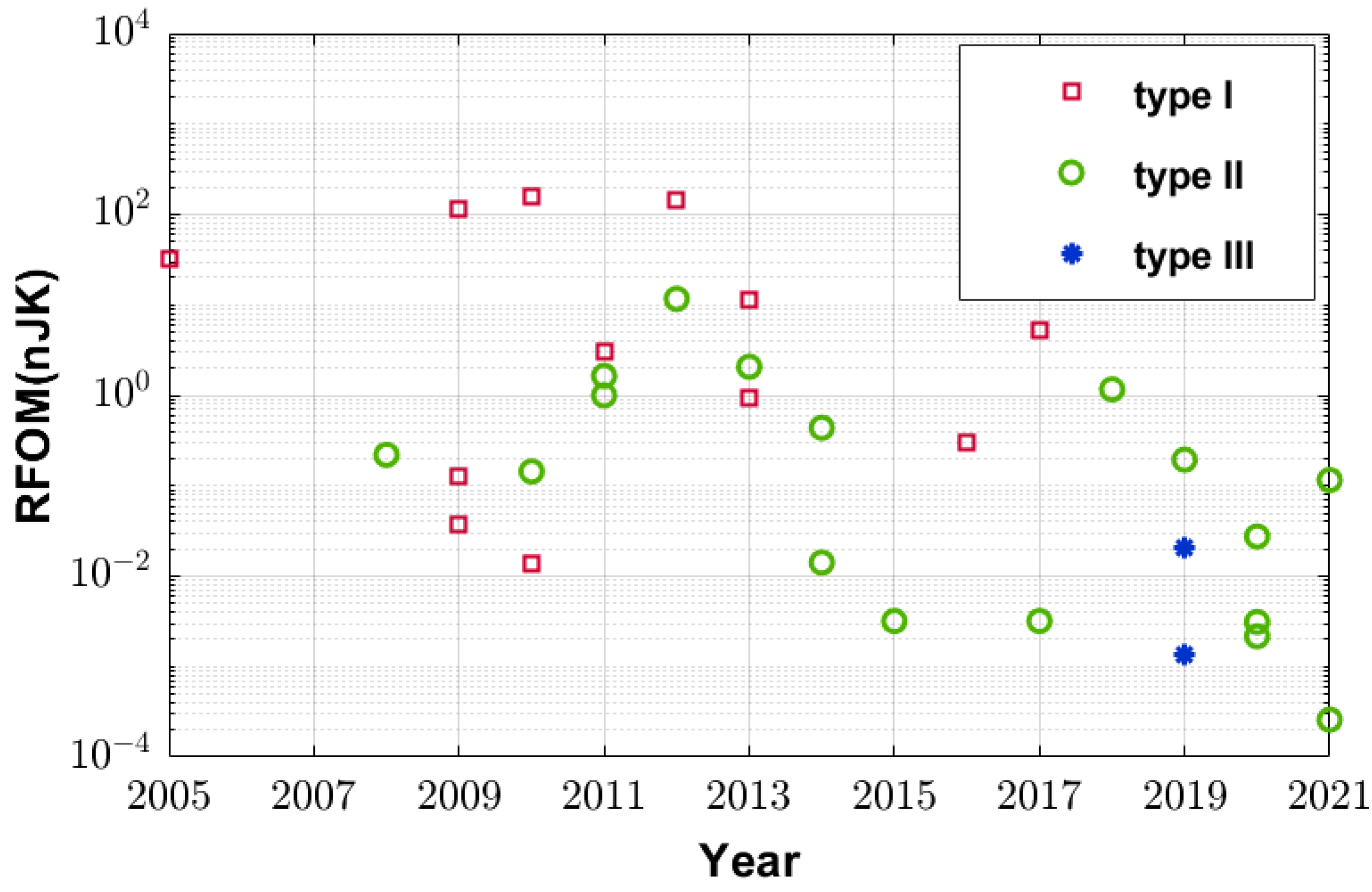

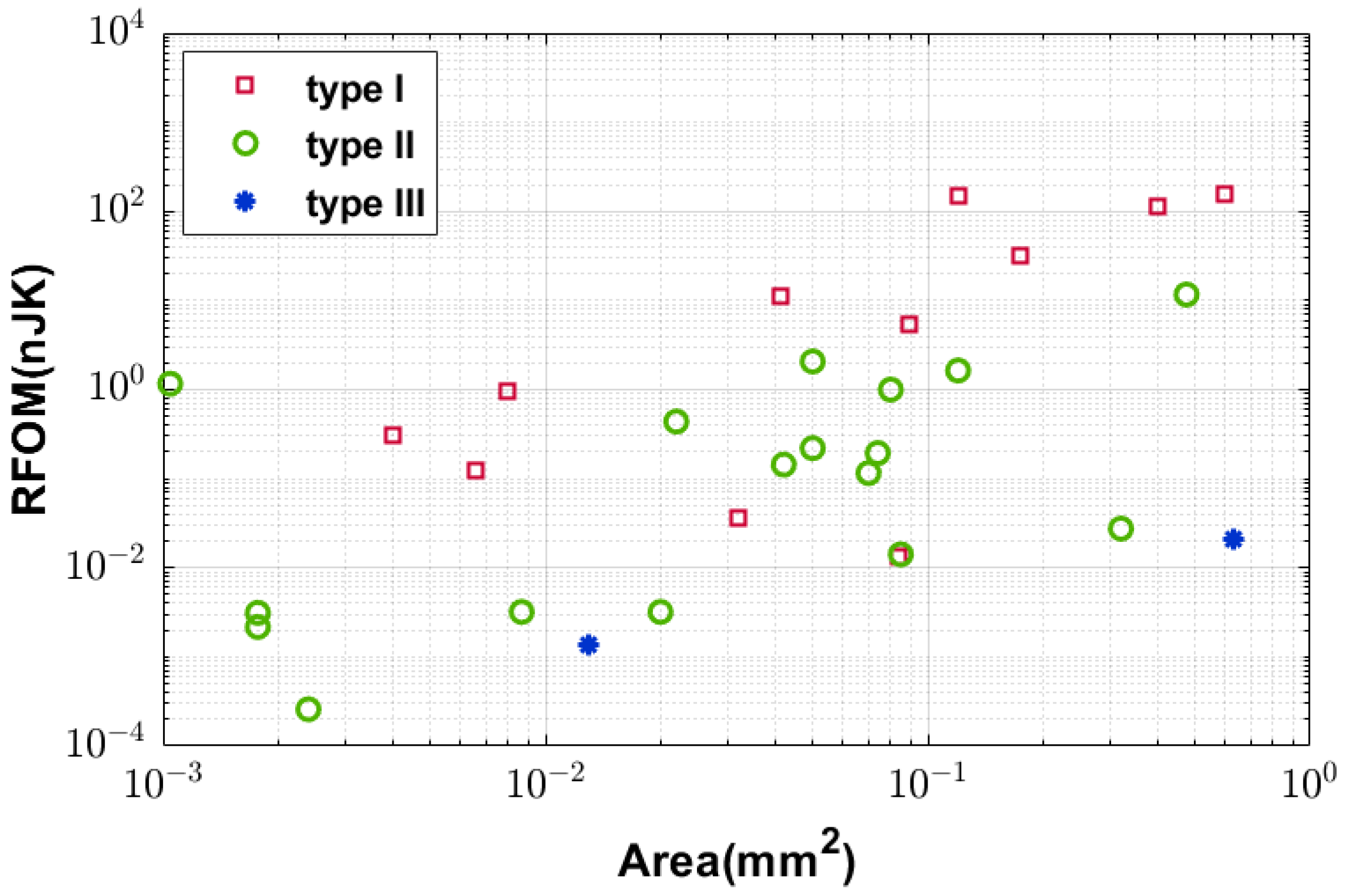

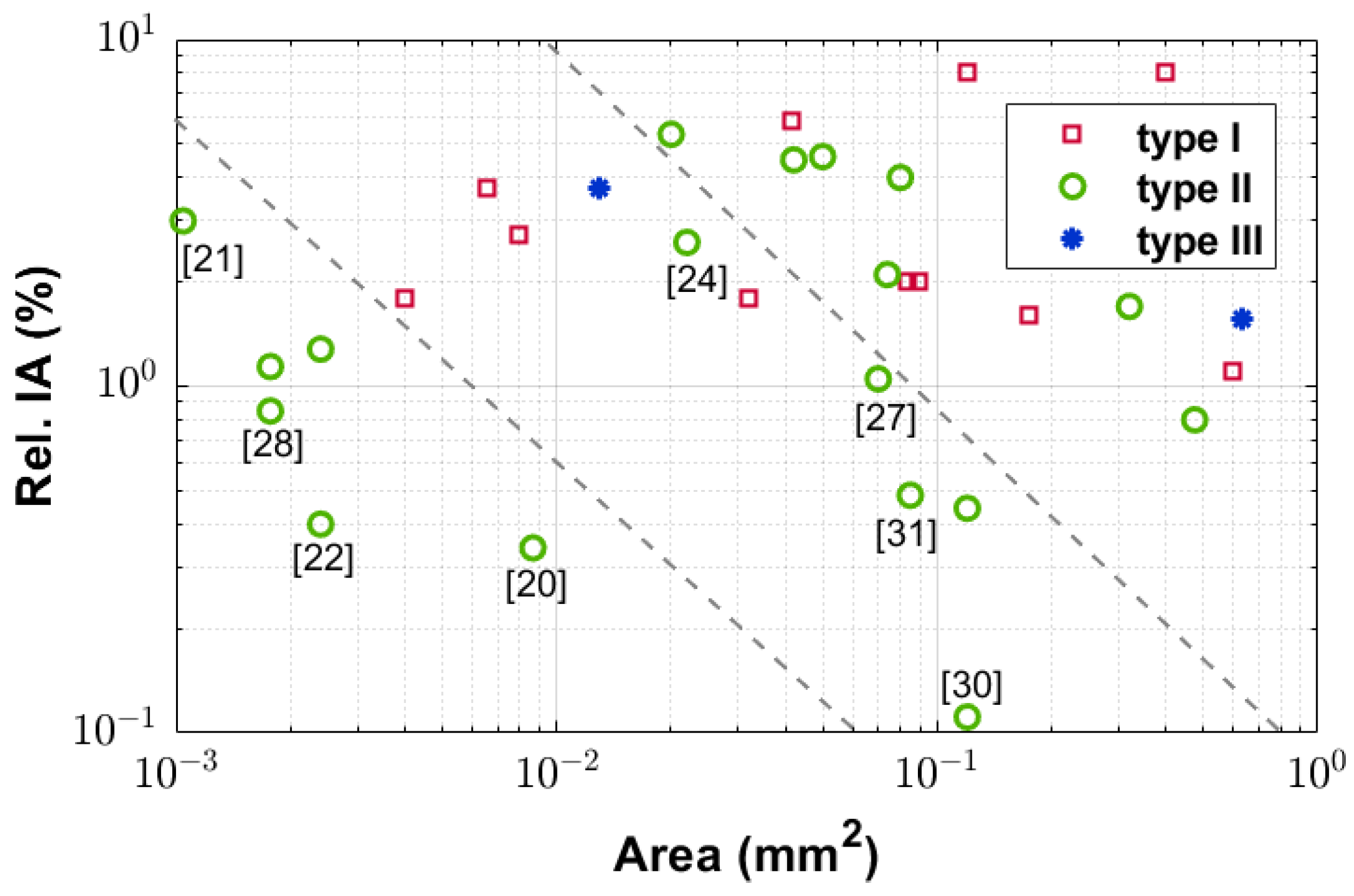

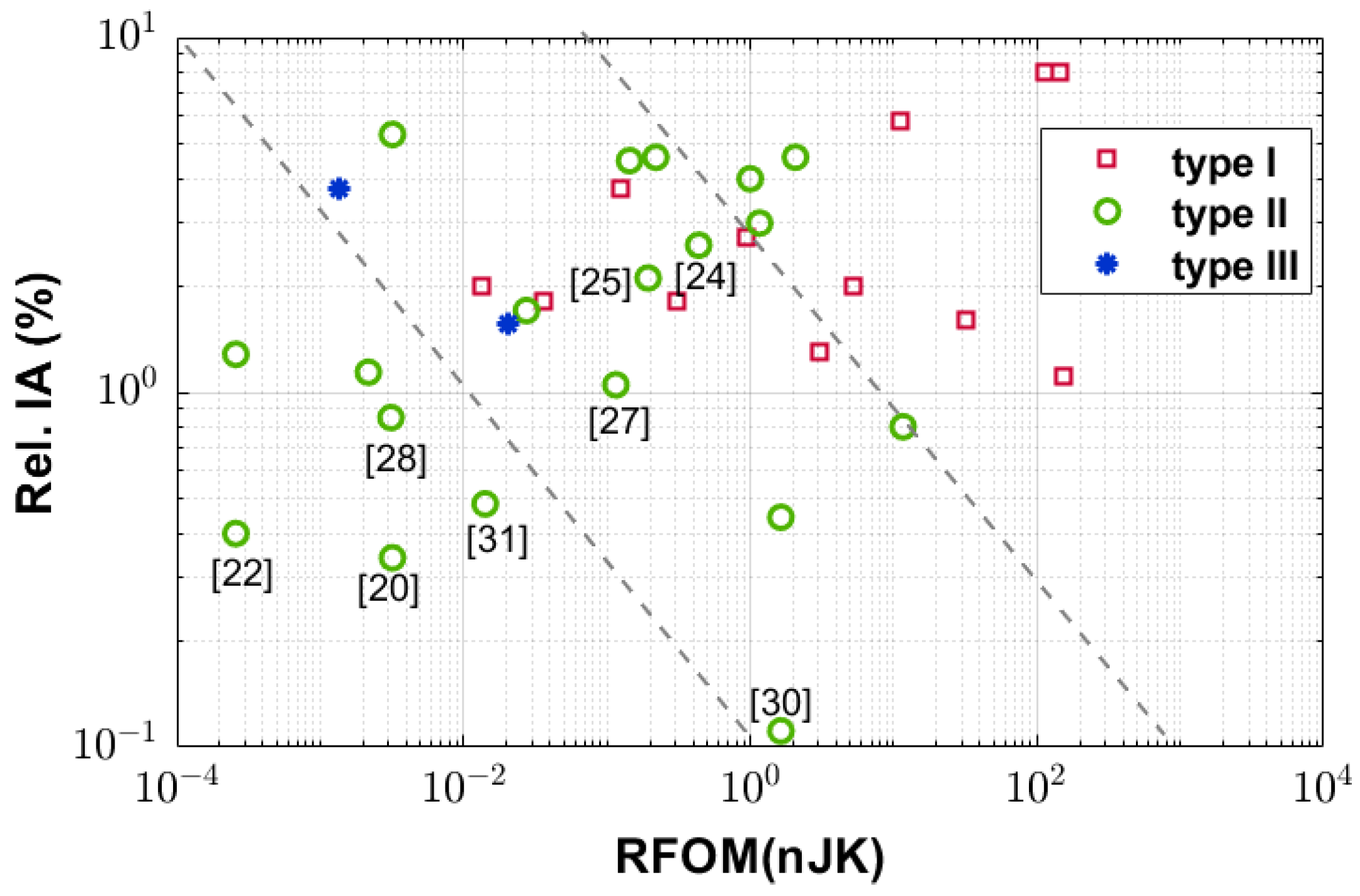

3.3. The Resolution Figure of Merit (RFOM) Versus Area

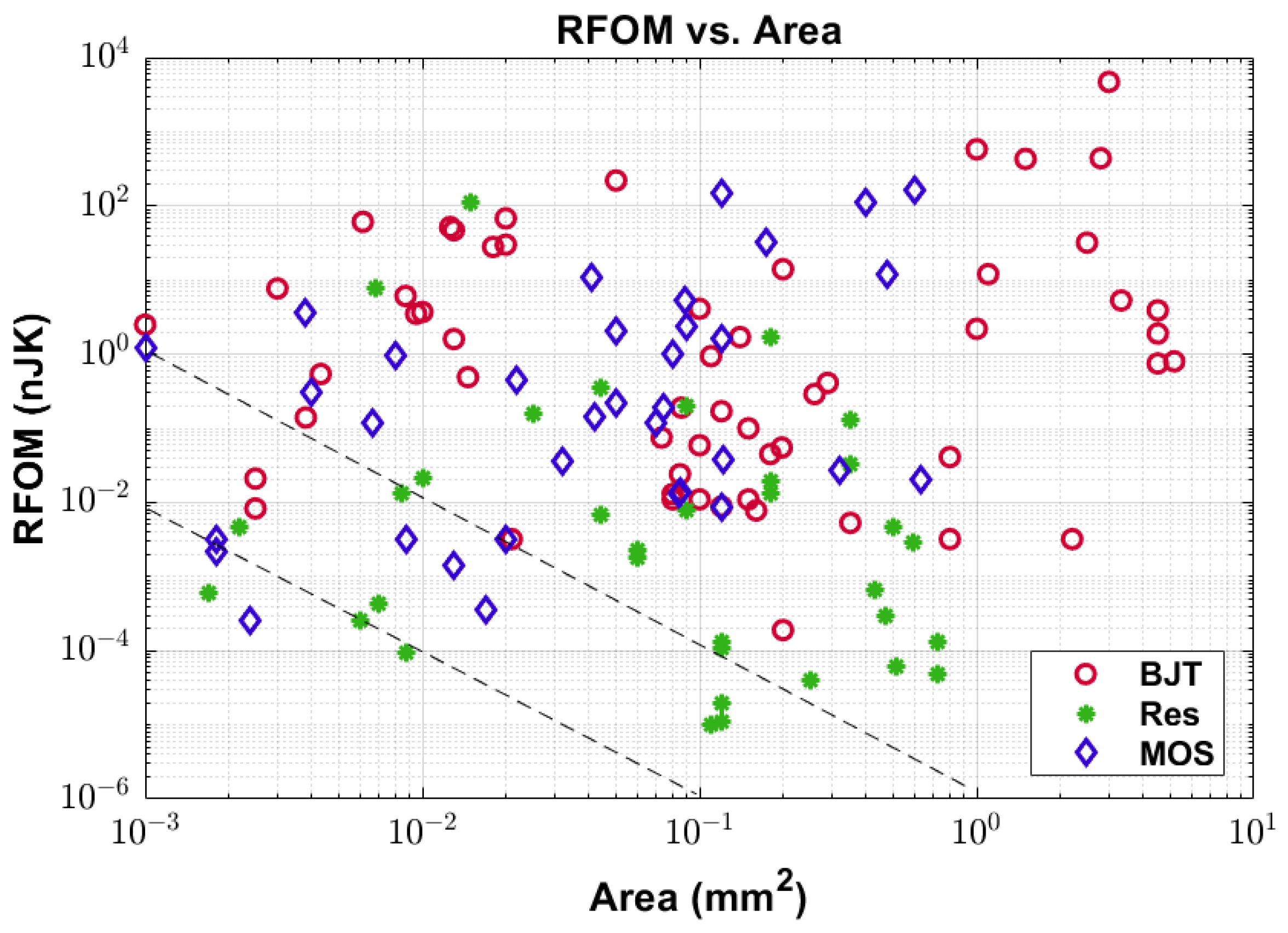

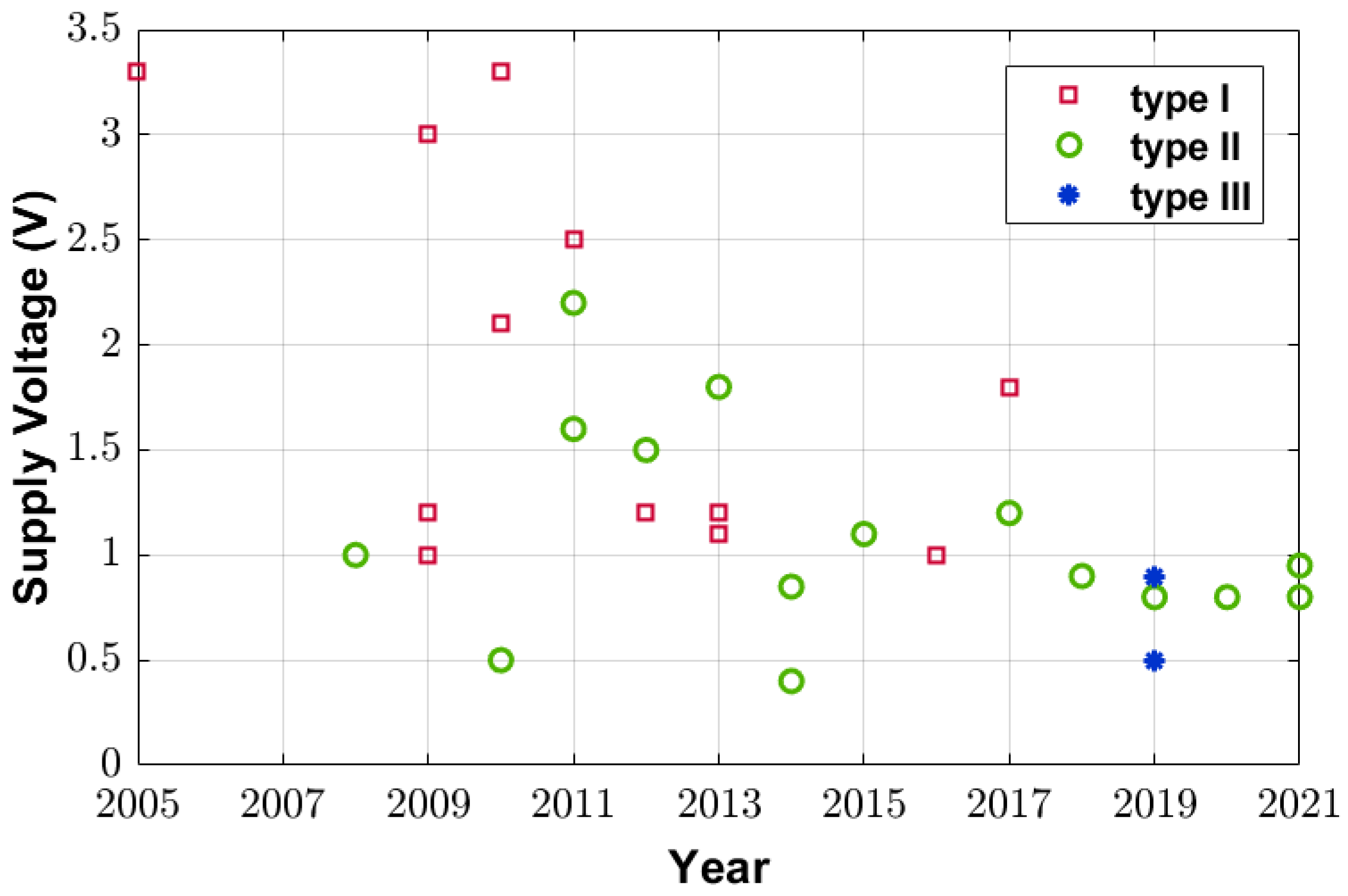

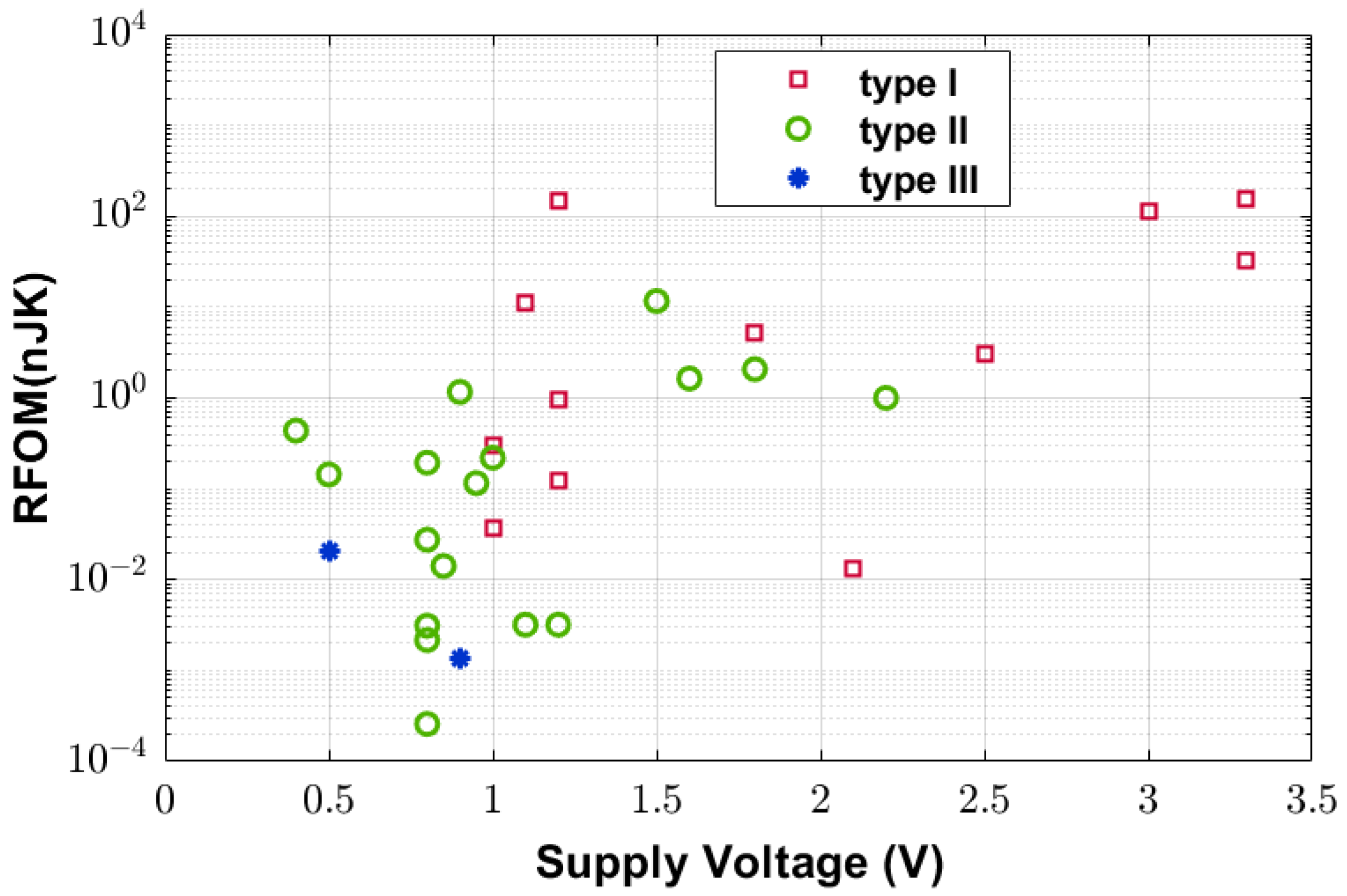

3.4. The Supply Voltage

3.5. Inaccuracy vs. Area and Energy Efficiency

3.6. Process Variations, Number of Trims and Global Curve Fitting

3.7. Noise

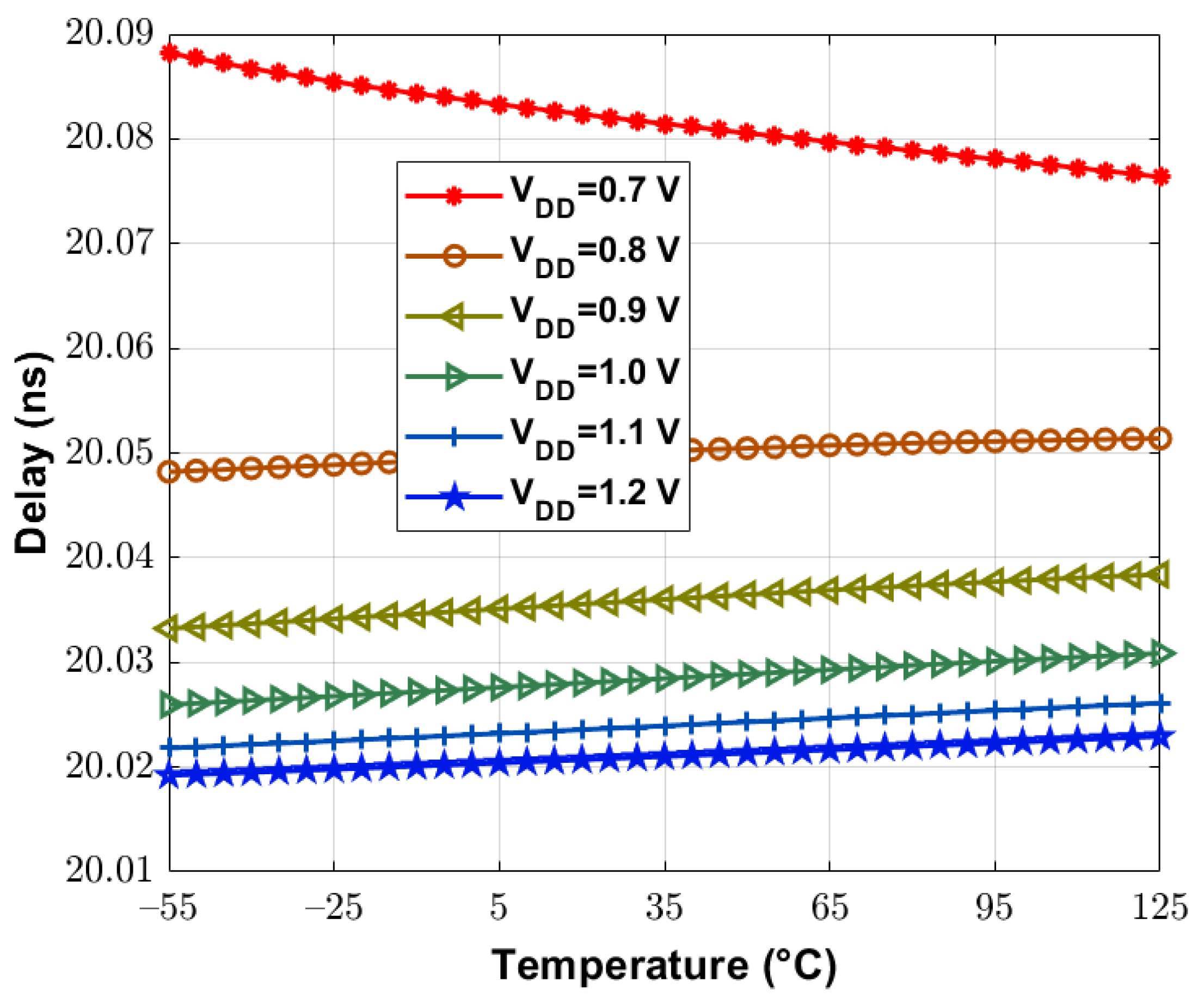

3.8. Power Supply Sensitivity

3.9. Self-Heating and Lifespan

4. Conclusions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Kazys, R.; Vaskeliene, V. High Temperature Ultrasonic Transducers: A Review. Sensors 2021, 21, 3200. [Google Scholar] [CrossRef] [PubMed]

- Sheikh, H.F.; Ahmad, I.; Wang, Z.; Ranka, S. An overview and classification of thermal-aware scheduling techniques for multi-core processing systems. Sustain. Comput. Inform. Syst. 2012, 2, 151–169. [Google Scholar] [CrossRef]

- Aiello, O.; Fiori, F. On the Susceptibility of Embedded Thermal Shutdown Circuit to Radio Frequency Interference. IEEE Trans. Electromagn. Compat. 2012, 54, 405–412. [Google Scholar] [CrossRef]

- Ha, D.; Woo, K.; Meninger, S.; Xanthopoulos, T.; Crain, E.; Ham, D. Time-Domain CMOS Temperature Sensors with Dual Delay-Locked Loops for Microprocessor Thermal Monitoring. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2012, 20, 1590–1601. [Google Scholar] [CrossRef]

- Chen, P.; Chen, S.; Shen, Y.; Peng, Y. All-Digital Time-Domain Smart Temperature Sensor with an Inter-Batch Inaccuracy of −0.7 °C–+0.6 °C After One-Point Calibration. IEEE Trans. Circuits Syst. I Regul. Pap. 2011, 58, 913–920. [Google Scholar] [CrossRef]

- Chen, P.; Chen, C.; Peng, Y.; Wang, K.; Wang, Y. A Time-Domain SAR Smart Temperature Sensor with Curvature Compensation and a 3σ Inaccuracy of −0.4 °C ∼ +0.6 °C Over a 0 °C to 90 °C Range. IEEE J. Solid-State Circuits 2010, 45, 600–609. [Google Scholar] [CrossRef]

- Chen, P.; Chen, T.-K.; Wang, Y.-S.; Chen, C.-C. A Time-Domain Sub-Micro Watt Temperature Sensor with Digital Set-Point Programming. IEEE Sens. J. 2009, 9, 1639–1646. [Google Scholar] [CrossRef]

- Chen, P.; Chen, C.; Tsai, C.; Lu, W. A time-to-digital-converter-based CMOS smart temperature sensor. IEEE J. Solid-State Circuits 2005, 40, 1642–1648. [Google Scholar] [CrossRef]

- Hwang, S.; Koo, J.; Kim, K.; Lee, H.; Kim, C. A 0.008 mm2 500/spl mu/W 469 kS/s Frequency-to-Digital Converter Based CMOS Temperature Sensor with Process Variation Compensation. IEEE Trans. Circuits Syst. I Regul. Pap. 2013, 60, 2241–2248. [Google Scholar] [CrossRef]

- Kim, K.; Lee, H.; Jung, S.; Kim, C. A 366 kS/s 400 uW 0.0013 mm2 frequency-to-digital converter based CMOS temperature sensor utilizing multiphase clock. In Proceedings of the 2009 IEEE Custom Integrated Circuits Conference, San Jose, CA, USA, 13–16 September 2009; pp. 203–206. [Google Scholar] [CrossRef]

- Vaz, A.; Ubarretxena, A.; Zalbide, I.; Pardo, D.; Solar, H.; Garcia-Alonso, A.; Berenguer, R. Full Passive UHF Tag with a Temperature Sensor Suitable for Human Body Temperature Monitoring. IEEE Trans. Circuits Syst. II Express Briefs 2010, 57, 95–99. [Google Scholar] [CrossRef]

- Anand, T.; Makinwa, K.A.A.; Hanumolu, P.K. A self-referenced VCO-based temperature sensor with 0.034 °C/mV supply sensitivity in 65 nm CMOS. In Proceedings of the 2015 Symposium on VLSI Circuits (VLSI Circuits), Kyoto, Japan, 17–19 June 2015; pp. C200–C201. [Google Scholar] [CrossRef]

- Shim, D.; Jeong, H.; Lee, H.; Rhee, C.; Jeong, D.-K.; Kim, S. A Process-Variation-Tolerant on-Chip CMOS Thermometer for Auto Temperature Compensated Self-Refresh of Low-Power Mobile DRAM. IEEE J. Solid-State Circuits 2013, 48, 2550–2557. [Google Scholar] [CrossRef]

- Song, W.; Lee, J.; Cho, N.; Burm, J. An Ultralow Power Time-Domain Temperature Sensor with Time-Domain Delta–Sigma TDC. IEEE Trans. Circuits Syst. II Express Briefs 2017, 64, 1117–1121. [Google Scholar] [CrossRef]

- Law, M.K.; Bermak, A. A 405-nW CMOS Temperature Sensor Based on Linear MOS Operation. IEEE Trans. Circuits Syst. II Express Briefs 2009, 56, 891–895. [Google Scholar] [CrossRef] [Green Version]

- Law, M.K.; Bermak, A.; Luong, H.C. A Sub-µ W Embedded CMOS Temperature Sensor for RFID Food Monitoring Application. IEEE J. Solid-State Circuits 2010, 45, 1246–1255. [Google Scholar] [CrossRef]

- Lin, Y.; Sylvester, D.; Blaauw, D. An ultra low power 1 V, 220 nW temperature sensor for passive wireless applications. In Proceedings of the 2008 IEEE Custom Integrated Circuits Conference, San Jose, CA, USA, 21–24 September 2008; pp. 507–510. [Google Scholar] [CrossRef]

- Ueno, K.; Asai, T.; Amemiya, Y. Low-power temperature-to-frequency converter consisting of subthreshold CMOS circuits for integrated smart temperature sensors. Sens. Actuators A Phys. 2011, 165, 132–137. [Google Scholar] [CrossRef]

- Kim, Y.; Choi, W.; Kim, J.; Lee, S.; Lee, S.; Kim, H.; Makinwa, K.A.A.; Chae, Y.; Kim, T.W. A 0.02 mm2 embedded temperature sensor with ±2 °C inaccuracy for self-refresh control in 25 nm mobile DRAM. In Proceedings of the ESSCIRC Conference 2015—41st European Solid-State Circuits Conference (ESSCIRC), Graz, Austria, 14–18 September 2015; pp. 267–270. [Google Scholar] [CrossRef]

- Yang, K.; Dong, Q.; Jung, W.; Zhang, Y.; Choi, M.; Blaauw, D.; Sylvester, D. 9.2 A 0.6 nJ −0.22/+0.19 °C inaccuracy temperature sensor using exponential subthreshold oscillation dependence. In Proceedings of the 2017 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 5–9 February 2017; pp. 160–161. [Google Scholar] [CrossRef]

- Cochet, M.; Keller, B.; Clerc, S.; Abouzeid, F.; Cathelin, A.; Autran, J.; Roche, P.; Nikolić, B. A 225 μm2 Probe Single-Point Calibration Digital Temperature Sensor Using Body-Bias Adjustment in 28 nm FD-SOI CMOS. IEEE Solid-State Circuits Lett. 2018, 1, 14–17. [Google Scholar] [CrossRef]

- Tang, Z.; Huang, Z.; Yu, X.-P.; Shi, Z.; Tan, N.N. A 0.26-pJ·K2 2400-μm2 Digital Temperature Sensor in 55-nm CMOS. IEEE Solid-State Circuits Lett. 2021, 4, 96–99. [Google Scholar] [CrossRef]

- Fojtik, M.; Kim, D.; Chen, G.; Lin, Y.; Fick, D.; Park, J.; Seok, M.; Chen, M.; Foo, Z.; Blaauw, D.; et al. A Millimeter-Scale Energy-Autonomous Sensor System with Stacked Battery and Solar Cells. IEEE J. Solid-State Circuits 2013, 48, 801–813. [Google Scholar] [CrossRef]

- Zhao, W.; Pan, R.; Ha, Y.; Yang, Z. A 0.4 V 280-nW frequency reference-less nearly all-digital hybrid domain temperature sensor. In Proceedings of the 2014 IEEE Asian Solid-State Circuits Conference (A-SSCC), KaoHsiung, Taiwan, 10–12 November 2014; pp. 301–304. [Google Scholar] [CrossRef]

- Someya, T.; Islam, A.K.M.M.; Sakurai, T.; Takamiya, M. An 11-nW CMOS Temperature-to-Digital Converter Utilizing Subthreshold Current at Sub-Thermal Drain Voltage. IEEE J. Solid-State Circuits 2019, 54, 613–622. [Google Scholar] [CrossRef]

- Someya, T.; Islam, A.K.M.M.; Okada, K. A 6.4 nW 1.7% Relative Inaccuracy CMOS Temperature Sensor Utilizing Sub-Thermal Drain Voltage Stabilization and Frequency-Locked Loop. IEEE Solid-State Circuits Lett. 2020, 3, 458–461. [Google Scholar] [CrossRef]

- Li, J.; Lin, Y.; Ning, N.; Yu, Q. A +0.44 °C/−0.4 °C Inaccuracy Temperature Sensor with Multi-Threshold MOSFET-Based Sensing Element and CMOS Thyristor-Based VCO. IEEE Trans. Circuits Syst. I Regul. Pap. 2021, 68, 1102–1113. [Google Scholar] [CrossRef]

- Tang, Z.; Fang, Y.; Shi, Z.; Yu, X.-P.; Tan, N.N.; Pan, W. A 1770-µm2 Leakage-Based Digital Temperature Sensor with Supply Sensitivity Suppression in 55-nm CMOS. IEEE J. Solid-State Circuits 2020, 55, 781–793. [Google Scholar] [CrossRef]

- Lee, S.-C.; Chiueh, H. A 69 μW CMOS smart temperature sensor with an inaccuracy of ±0.8 °C (3σ) from −50 °C to 150 °C. SENSORS 2012, 2012, 6411595. [Google Scholar] [CrossRef]

- Souri, K.; Chae, Y.; Ponomarev, Y.; Makinwa, K.A.A. A precision DTMOST-based temperature sensor. In Proceedings of the ESSCIRC (ESSCIRC), Helsinki, Finland, 12–16 September 2011; pp. 279–282. [Google Scholar] [CrossRef]

- Souri, K.; Chae, Y.; Thus, F.; Makinwa, K. 12.7 A 0.85 V 600 nW all-CMOS temperature sensor with an inaccuracy of ±0.4 °C (3σ) from −40 to 125 °C. In Proceedings of the 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 9–13 February 2014; pp. 222–223. [Google Scholar] [CrossRef]

- Truesdell, D.S.; Calhoun, B.H. A 640 pW 22 pJ/sample Gate Leakage-Based Digital CMOS Temperature Sensor with 0.25 °C Resolution. In Proceedings of the 2019 IEEE Custom Integrated Circuits Conference (CICC), Austin, TX, USA, 14–17 April 2019; pp. 1–4. [Google Scholar] [CrossRef]

- Wang, H.; Mercier, P.P. A 763 pW 230 pJ/Conversion Fully Integrated CMOS Temperature-to-Digital Converter with +0.81 °C/−0.75 °C Inaccuracy. IEEE J. Solid-State Circuits 2019, 54, 2281–2290. [Google Scholar] [CrossRef]

- Jeong, S.; Foo, Z.; Lee, Y.; Sim, J.; Blaauw, D.; Sylvester, D. A Fully-Integrated 71 nW CMOS Temperature Sensor for Low Power Wireless Sensor Nodes. IEEE J. Solid-State Circuits 2014, 49, 1682–1693. [Google Scholar] [CrossRef]

- Pertijs, M.A.P.; Niederkorn, A.; Ma, X.; McKillop, B.; Bakker, A.; Huijsing, J.H. A CMOS smart temperature sensor with a 3/spl sigma/ inaccuracy of /spl plusmn/0.5/spl deg/C from −50/spl deg/C to 120/spl deg/C. IEEE J. Solid-State Circuits 2005, 40, 454–461. [Google Scholar] [CrossRef]

- Pertijs, M.; Makinwa, K.; Huijsing, J. A CMOS temperature sensor with a 3/spl sigma/ inaccuracy of /spl plusmn/0.1/spl deg/C from −55/spl deg/C to 125/spl deg/C. In Proceedings of the ISSCC—2005 IEEE International Digest of Technical Papers. Solid-State Circuits Conference, San Francisco, CA, USA, 10 February 2005; Volume 1, pp. 238–596. [Google Scholar] [CrossRef]

- Aita, A.L.; Pertijs, M.A.P.; Makinwa, K.A.A.; Huijsing, J.H. A CMOS smart temperature sensor with a batch-calibrated inaccuracy of ±0.25 °C (3σ) from −70 °C to 130 °C. In Proceedings of the 2009 IEEE International Solid-State Circuits Conference—Digest of Technical Papers, San Francisco, CA, USA, 8–12 February 2009; pp. 342–343. [Google Scholar] [CrossRef]

- Li, Y.W.; Lakdawala, H.; Raychowdhury, A.; Taylor, G.; Soumyanath, K. A 1.05 V 1.6 mW 0.45 °C 3σ-resolution ΔΣ-based temperature sensor with parasitic-resistance compensation in 32 nm CMOS. In Proceedings of the 2009 IEEE International Solid-State Circuits Conference—Digest of Technical Papers, San Francisco, CA, USA, 8–12 February 2009; pp. 340–341. [Google Scholar] [CrossRef]

- Duarte, D.; Zepeda, P.; Hsu, S.; Maheshwari, A.; Taylor, G. HVM performance validation and DFM techniques used in a 32 nm CMOS thermal sensor system. In Proceedings of the IEEE Custom Integrated Circuits Conference 2010, San Jose, CA, USA, 19–22 September 2010; pp. 1–4. [Google Scholar] [CrossRef]

- Souri, K.; Kashmiri, M.; Makinwa, K. A CMOS temperature sensor with an energy-efficient zoom ADC and an Inaccuracy of ±0.25 °C (3 s) from −40 °C to 125 °C. In Proceedings of the 2010 IEEE International Solid-State Circuits Conference—(ISSCC), San Francisco, CA, USA, 7–11 February 2010; pp. 310–311. [Google Scholar] [CrossRef]

- Yin, J.; Yi, J.; Law, M.K.; Ling, Y.; Lee, M.C.; Ng, K.P.; Gao, B.; Luong, H.C.; Bermak, A.; Chan, M.; et al. A system-on-chip EPC Gen-2 passive UHF RFID tag with embedded temperature sensor. In Proceedings of the 2010 IEEE International Solid-State Circuits Conference—(ISSCC), San Francisco, CA, USA, 7–11 February 2010; pp. 308–309. [Google Scholar] [CrossRef]

- Zjajo, A.; Barragan, M.J.; de Gyvez, J.P. Low-Power Die-Level Process Variation and Temperature Monitors for Yield Analysis and Optimization in Deep-Submicron CMOS. IEEE Trans. Instrum. Meas. 2012, 61, 2212–2221. [Google Scholar] [CrossRef] [Green Version]

- Chowdhury, G.; Hassibi, A. An On-Chip Temperature Sensor with a Self-Discharging Diode in 32-nm SOI CMOS. IEEE Trans. Circuits Syst. II Express Briefs 2012, 59, 568–572. [Google Scholar] [CrossRef]

- Souri, K.; Chae, Y.; Makinwa, K. A CMOS temperature sensor with a voltage-calibrated inaccuracy of ±0.15 °C (3σ) from −55 to 125 °C. In Proceedings of the 2012 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 19–23 February 2012; pp. 208–210. [Google Scholar] [CrossRef]

- Shalmany, S.H.; Draxelmayr, D.; Makinwa, K.A.A. A micropower battery current sensor with ±0.03% (3σ) inaccuracy from −40 to +85 °C. In Proceedings of the 2013 IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 17–21 February 2013; pp. 386–387. [Google Scholar] [CrossRef]

- Pu, X.; Ash, M.; Nagaraj, K.; Park, J.; Vu, S.; Kimelman, P.; de la Haye, S. A +0.4 °C accurate high-speed remote junction temperature sensor with digital Beta correction and series-resistance cancellation in 65 nm CMOS. In Proceedings of the 2013 Symposium on VLSI Circuits, Kyoto, Japan, 12–14 June 2013; pp. C214–C215. [Google Scholar]

- Shor, J.; Luria, K.; Zilberman, D. Ratiometric BJT-based thermal sensor in 32 nm and 22 nm technologies. In Proceedings of the 2012 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 19–23 February 2012; pp. 210–212. [Google Scholar] [CrossRef]

- Wang, B.; Law, M.; Bermak, A.; Luong, H.C. A Passive RFID Tag Embedded Temperature Sensor with Improved Process Spreads Immunity for a −30 °C to 60 °C Sensing Range. IEEE Trans. Circuits Syst. I Regul. Pap. 2014, 61, 337–346. [Google Scholar] [CrossRef]

- Heidary, A.; Wang, G.; Makinwa, K.; Meijer, G. 12.8 A BJT-based CMOS temperature sensor with a 3.6 pJ·K2-resolution FoM. In Proceedings of the 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 9–13 February 2014; pp. 224–225. [Google Scholar] [CrossRef]

- Ro’ee, E.; Ariel, C. Untrimmed Low-Power Thermal Sensor for SoC in 22 nm Digital Fabrication Technology. J. Low Power Electron. Appl. 2014, 4, 304–316. [Google Scholar] [CrossRef] [Green Version]

- Oshita, T.; Shor, J.; Duarte, D.E.; Kornfeld, A.; Zilberman, D. Compact BJT-Based Thermal Sensor for Processor Applications in a 14 nm tri-Gate CMOS Process. IEEE J. Solid-State Circuits 2015, 50, 799–807. [Google Scholar] [CrossRef]

- Chuang, M.-C.; Tai, C.-L.; Hsu, Y.-C.; Roth, A.; Soenen, E. A temperature sensor with a 3 sigma inaccuracy of ±2 °C without trimming from −50 °C to 150 °C in a 16 nm FinFET process. In Proceedings of the ESSCIRC Conference 2015—41st European Solid-State Circuits Conference (ESSCIRC), Graz, Austria, 14–18 September 2015; pp. 271–274. [Google Scholar] [CrossRef]

- Deng, C.; Sheng, Y.; Wang, S.; Hu, W.; Diao, S.; Qian, D. A CMOS Smart Temperature Sensor with Single-Point Calibration Method for Clinical Use. IEEE Trans. Circuits Syst. II Express Briefs 2016, 63, 136–140. [Google Scholar] [CrossRef]

- Eberlein, M.; Yahav, I. A 28 nm CMOS ultra-compact thermal sensor in current-mode technique. In Proceedings of the 2016 IEEE Symposium on VLSI Circuits (VLSI-Circuits), Honolulu, HI, USA, 15–17 June 2016; pp. 1–2. [Google Scholar] [CrossRef]

- Yousefzadeh, B.; Shalmany, S.H.; Makinwa, K. A BJT-based temperature-to-digital converter with ±60 mK (3σ) inaccuracy from −70 °C to 125 °C in 160 nm CMOS. In Proceedings of the 2016 IEEE Symposium on VLSI Circuits (VLSI-Circuits), Honolulu, HI, USA, 15–17 June 2016; pp. 1–2. [Google Scholar] [CrossRef]

- Shalmany, S.H.; Draxelmayr, D.; Makinwa, K. A ±36A integrated current-sensing system with 0.3% gain error and 400 µA offset from −55 °C to +85 °C. In Proceedings of the 2016 IEEE Symposium on VLSI Circuits (VLSI-Circuits), Honolulu, HI, USA, 15–17 June 2016; pp. 1–2. [Google Scholar] [CrossRef]

- Law, M.; Lu, S.; Wu, T.; Bermak, A.; Mak, P.; Martins, R.P. A 1.1 µW CMOS Smart Temperature Sensor with an Inaccuracy of ±0.2 °C (3σ) for Clinical Temperature Monitoring. IEEE Sens. J. 2016, 16, 2272–2281. [Google Scholar] [CrossRef]

- Wang, G.; Heidari, A.; Makinwa, K.A.A.; Meijer, G.C.M. An Accurate BJT-Based CMOS Temperature Sensor with Duty-Cycle-Modulated Output. IEEE Trans. Ind. Electron. 2017, 64, 1572–1580. [Google Scholar] [CrossRef] [Green Version]

- Hsu, Y.-C.; Tai, C.-L.; Chuang, M.-C.; Roth, A.; Soenen, E. 5.9 An 18.75 µW dynamic-distributing-bias temperature sensor with 0.87 °C (3σ) untrimmed inaccuracy and 0.00946mm2 area. In Proceedings of the 2017 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 5–9 February 2017; pp. 102–103. [Google Scholar] [CrossRef]

- Yousefzadeh, B.; Makinwa, K.A.A. 9.3 A BJT-based temperature sensor with a packaging-robust inaccuracy of ±0.3 °C (3σ) from −55 °C to +125 °C after heater-assisted voltage calibration. In Proceedings of the 2017 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 5–9 February 2017; pp. 162–163. [Google Scholar] [CrossRef]

- Lin, D.S.; Hong, H.P. A 0.5V BJT-based CMOS thermal sensor in 10-nm FinFET technology. In Proceedings of the 2017 IEEE Asian Solid-State Circuits Conference (A-SSCC), Seoul, Korea, 6–8 November 2017; pp. 41–44. [Google Scholar] [CrossRef]

- Lu, C.-Y.; Ravikumar, S.; Sali, A.D.; Eberlein, M.; Lee, H.-J. An 8b subthreshold hybrid thermal sensor with ±1.07 °C inaccuracy and single-element remote-sensing technique in 22 nm FinFET. In Proceedings of the 2018 IEEE International Solid-State Circuits Conference—(ISSCC), San Francisco, CA, USA, 11–15 February 2018; pp. 318–320. [Google Scholar] [CrossRef]

- Zhang, T.; Law, M.; Mak, P.; Vai, M.; Martins, R.P. Nano-Watt Class Energy-Efficient Capacitive Sensor Interface with on-Chip Temperature Drift Compensation. IEEE Sens. J. 2018, 18, 2870–2882. [Google Scholar] [CrossRef]

- Zhong, T.; Yun, F.; Xiao-Peng, Y.; Zheng, S.; Nianxiong, T. Capacitor-Reused CMOS Temperature Sensor with Duty-Cycle-Modulated Output and 0.38 °C (3σ) Inaccuracy. Electron. Lett. 2018, 54, 568–570. [Google Scholar] [CrossRef]

- Wang, B.; Law, M.-K.; Tsui, C.-Y.; Bermak, A. A 10.6 pJ·K2 Resolution FoM Temperature Sensor Using Astable Multivibrator. IEEE Trans. Circuits Syst. II Express Briefs 2018, 65, 869–873. [Google Scholar] [CrossRef]

- Bass, O.; Shor, J. A Miniaturized 0.003 mm2 PNP-Based Thermal Sensor for Dense CPU Thermal Monitoring. IEEE Trans. Circuits Syst. I Regul. Pap. 2020, 67, 2984–2992. [Google Scholar] [CrossRef]

- Tang, Z.; Fang, Y.; Yu, X.-P.; Shi, Z.; Tan, N. A CMOS Temperature Sensor with Versatile Readout Scheme and High Accuracy for Multi-Sensor Systems. IEEE Trans. Circuits Syst. I Regul. Pap. 2018, 65, 3821–3829. [Google Scholar] [CrossRef]

- Tang, Z.; Fang, Y.; Huang, Z.; Yu, X.-P.; Shi, Z.; Tan, N.N. An Untrimmed BJT-Based Temperature Sensor with Dynamic Current-Gain Compensation in 55-nm CMOS Process. IEEE Trans. Circuits Syst. II Express Briefs 2019, 66, 1613–1617. [Google Scholar] [CrossRef]

- Kumar, R.K.; Jiang, H.; Makinwa, K.A.A. An Energy-Efficient BJT-Based Temperature-to-Digital Converter with ±0.13 °C (3σ) Inaccuracy from −40 to 125 °C. In Proceedings of the 2019 IEEE Asian Solid-State Circuits Conference (A-SSCC), Macao, China, 4–6 November 2019; pp. 107–108. [Google Scholar] [CrossRef]

- Park, B.; Ji, Y.; Sim, J.-Y. A 490-pW SAR Temperature Sensor with a Leakage-Based Bandgap-Vth Reference. IEEE Trans. Circuits Syst. II Express Briefs 2020, 67, 1549–1553. [Google Scholar] [CrossRef]

- Yousefzadeh, B.; Makinwa, K.A.A. A BJT-Based Temperature-to-Digital Converter with a ±0.25 °C (3σ)-Inaccuracy From −40 °C to +180 °C Using Heater-Assisted Voltage Calibration. IEEE J. Solid-State Circuits 2020, 55, 369–377. [Google Scholar] [CrossRef]

- Shalmany, S.H.; Souri, K.; Sonmez, U.; Souri, K.; D’Urbino, M.; Hussaini, S.; Tauro, D.; Tabatabaei, S. 3.7 A 620µW BJT-Based Temperature-to-Digital Converter with 0.65 mK Resolution and FoM of 190 fJ·K2. In Proceedings of the 2020 IEEE International Solid-State Circuits Conference—(ISSCC), San Francisco, CA, USA, 16–20 February 2020; pp. 70–72. [Google Scholar] [CrossRef]

- Tang, Z.; Fang, Y.; Yu, X.-P.; Tan, N.N.; Zheng, S.; Harpe, P. A 1-V Diode-Based Temperature Sensor with a Resolution FoM of 3.1 pJ K2 in 55 nm CMOS. In Proceedings of the 2021 IEEE Custom Integrated Circuits Conference (CICC), Austin, TX, USA, 25–30 April 2021; pp. 1–2. [Google Scholar] [CrossRef]

- Eberlein, M.; Pretl, H. A Current-Mode Temperature Sensor with a ±1.56 °C Raw Error and Duty-Cycle Output in 16 nm FinFET. In Proceedings of the 2021 IEEE International Symposium on Circuits and Systems (ISCAS), Daegu, Korea, 22–28 May 2021; pp. 1–5. [Google Scholar] [CrossRef]

- Huang, Z.; Tang, Z.; Yu, X.-P.; Shi, Z.; Lin, L.; Tan, N.N. A BJT-Based CMOS Temperature Sensor with Duty-Cycle-Modulated Output and ±0.5 °C (3σ) Inaccuracy From −40 °C to 125 °C. IEEE Trans. Circuits Syst. II Express Briefs 2021, 68, 2780–2784. [Google Scholar] [CrossRef]

- David, R.; Francois, K.; AurÉlie, P.; Guido, S.D. Silicon Resonator Based 3.2 W Real Time Clock with 10 ppm Frequency Accuracy. IEEE J. Solid-State Circuits 2010, 45, 224–234. [Google Scholar] [CrossRef]

- Wu, C.; Chan, W.; Lin, T. A 80 kS/s 36 µW resistor-based temperature sensor using BGR-free SAR ADC with a unevenly-weighted resistor string in 0.18µm CMOS. In Proceedings of the 2011 Symposium on VLSI Circuits—Digest of Technical Papers, Kyoto, Japan, 15–17 June 2011; pp. 222–223. [Google Scholar]

- Perrott, M.; Salvia, J.; Lee, F.; Partridge, A.; Mukherjee, S.; Arft, C.; Kim, J.; Arumugam, N.; Gupta, P.; Tabatabaei, S.; et al. A temperature-to-digital converter for a MEMS-based programmable oscillator with better than ±0.5 ppm frequency stability. In Proceedings of the 2012 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 19–23 February 2012; pp. 206–208. [Google Scholar] [CrossRef]

- Shahmohammadi, M.; Souri, K.; Makinwa, K.A.A. A resistor-based temperature sensor for MEMS frequency references. In Proceedings of the 2013 ESSCIRC (ESSCIRC), Bucharest, Romania, 16–20 September 2013; pp. 225–228. [Google Scholar] [CrossRef]

- Tang, X.; Pun, K.-p.; Ng, W.-T. A 0.9V 5 kS/s resistor-based time-domain temperature sensor in 90 nm CMOS with calibrated inaccuracy of −0.6 °C/0.8 °C from −40 °C to 125 °C. In Proceedings of the 2013 IEEE Asian Solid-State Circuits Conference (A-SSCC), Singapore, 11–13 November 2013; pp. 169–172. [Google Scholar] [CrossRef]

- Park, P.; Makinwa, K.A.A.; Ruffieux, D. A resistor-based temperature sensor for a real time clock with ±2 ppm frequency stability. In Proceedings of the ESSCIRC 2014—40th European Solid State Circuits Conference (ESSCIRC), Venice Lido, Italy, 22–26 September 2014; pp. 391–394. [Google Scholar] [CrossRef]

- Weng, C.-H.; Wu, C.-K.; Lin, T.-H. A CMOS Thermistor-Embedded Continuous-Time Delta-Sigma Temperature Sensor with a Resolution FoM of 0.65 pJ °C2. IEEE J. Solid-State Circuits 2015, 50, 2491–2500. [Google Scholar] [CrossRef]

- Horng, J.; Liu, S.; Kundu, A.; Chang, C.; Chen, C.; Chiang, H.; Peng, Y. A 0.7 V resistive sensor with temperature/voltage detection function in 16nm FinFET technologies. In Proceedings of the 2014 Symposium on VLSI Circuits Digest of Technical Papers, Honolulu, HI, USA, 10–13 June 2014; pp. 1–2. [Google Scholar] [CrossRef]

- Sankaragomathi, K.A.; Koo, J.; Ruby, R.; Otis, B.P. 25.9 A ±3 ppm 1.1 mW FBAR frequency reference with 750 MHz output and 750 mV supply. In Proceedings of the 2015 IEEE International Solid-State Circuits Conference—(ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 22–26 February 2015; pp. 1–3. [Google Scholar] [CrossRef]

- Pan, S.; Jiang, H.; Makinwa, K.A.A. A CMOS temperature sensor with a 49 fJK2 resolution FoM. In Proceedings of the 2017 Symposium on VLSI Circuits, Kyoto, Japan, 5–8 June 2017; pp. C82–C83. [Google Scholar] [CrossRef]

- Pan, S.; Luo, Y.; Shalmany, S.H.; Makinwa, K.A.A. 9.1 A resistor-based temperature sensor with a 0.13 pJ·K2 resolution FOM. In Proceedings of the 2017 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 5–9 February 2017; pp. 158–159. [Google Scholar] [CrossRef] [Green Version]

- Choi, W.; Lee, Y.; Kim, S.; Lee, S.; Jang, J.; Chun, J.; Makinwa, K.A.A.; Chae, Y. A Compact Resistor-Based CMOS Temperature Sensor with an Inaccuracy of 0.12 °C (3σ) and a Resolution FoM of 0.43 pJ K2 in 65-nm CMOS. IEEE J. Solid-State Circuits 2018, 53, 3356–3367. [Google Scholar] [CrossRef]

- Pan, S.; Makinwa, K.A.A. A 0.25 mm2 resistor-based temperature sensor with an inaccuracy of 0.12 °C (3σ) from −55 °C to 125 °C and a resolution FOM of 32 fJK2. In Proceedings of the 2018 IEEE International Solid-State Circuits Conference—(ISSCC), San Francisco, CA, USA, 11–15 February 2018; pp. 320–322. [Google Scholar] [CrossRef]

- Park, H.; Kim, J. A 0.8-V Resistor-Based Temperature Sensor in 65-nm CMOS with Supply Sensitivity of 0.28 °C/V. IEEE J. Solid-State Circuits 2018, 53, 906–912. [Google Scholar] [CrossRef]

- Xin, H.; Andraud, M.; Baltus, P.; Cantatore, E.; Harpe, P. A 174 pW–488.3 nW 1 S/s–100 kS/s All-Dynamic Resistive Temperature Sensor with Speed/Resolution/Resistance Adaptability. IEEE Solid-State Circuits Lett. 2018, 1, 70–73. [Google Scholar] [CrossRef]

- Mordakhay, A.; Shor, J. Miniaturized, 0.01 mm2, Resistor-Based Thermal Sensor with an Energy Consumption of 0.9 nJ and a Conversion Time of 80 µs for Processor Applications. IEEE J. Solid-State Circuits 2018, 53, 2958–2969. [Google Scholar] [CrossRef]

- Pan, S.; Makinwa, K.A.A. 10.4 A Wheatstone Bridge Temperature Sensor with a Resolution FoM of 20fJ.K2. In Proceedings of the 2019 IEEE International Solid-State Circuits Conference—(ISSCC), San Francisco, CA, USA, 17–21 February 2019; pp. 186–188. [Google Scholar] [CrossRef]

- Pan, S.; Gürleyük, Ç.; Pimenta, M.F.; Makinwa, K.A.A. 10.3 A 0.12 mm2 Wien-Bridge Temperature Sensor with 0.1 °C (3σ) Inaccuracy from −40 °C to 180 °C. In Proceedings of the 2019 IEEE International Solid-State Circuits Conference—(ISSCC), San Francisco, CA, USA, 17–21 February 2019; pp. 184–186. [Google Scholar] [CrossRef]

- Jiang, H.; Huang, C.-C.; Chan, M.; Hall, D.A. A 2-in-1 Temperature and Humidity Sensor Achieving 62 fJ·K2 and 0.83 pJ·(%RH)2. In Proceedings of the 2019 IEEE Custom Integrated Circuits Conference (CICC), Austin, TX, USA, 14–17 April 2019; pp. 1–4. [Google Scholar] [CrossRef]

- Angevare, J.A.; Makinwa, K.A.A. A 6800-µm2 Resistor-Based Temperature Sensor with ±0.35 °C (3σ) Inaccuracy in 180-nm CMOS. IEEE J. Solid-State Circuits 2019, 54, 2649–2657. [Google Scholar] [CrossRef] [Green Version]

- Wang, A.; Chen, C.; Liu, C.; Shi, C.-J.R. A 9-Bit Resistor-Based Highly Digital Temperature Sensor with a SAR-Quantization Embedded Differential Low-Pass Filter in 65-nm CMOS with a 2.5-µs Conversion Time. IEEE Sens. J. 2019, 19, 7215–7225. [Google Scholar] [CrossRef]

- Lee, Y.; Choi, W.; Kim, T.; Song, S.; Makinwa, K.A.A.; Chae, Y. A 5800-μm2 Resistor-Based Temperature Sensor with a One-Point Trimmed Inaccuracy of ±1.2 °C (3σ) from −50 °C to 105 °C in 65-nm CMOS. In Proceedings of the ESSCIRC 2019—IEEE 45th European Solid State Circuits Conference (ESSCIRC), Cracow, Poland, 23–26 September 2019; pp. 68–71. [Google Scholar] [CrossRef] [Green Version]

- Khashaba, A.; Zhu, J.; Elmallah, A.; Ahmed, M.; Hanumolu, P.K. 3.2 A 0.0088 mm2 Resistor-Based Temperature Sensor Achieving 92 fJ·K2 FoM in 65 nm CMOS. In Proceedings of the 2020 IEEE International Solid-State Circuits Conference—(ISSCC), San Francisco, CA, USA, 16–20 February 2020; pp. 60–62. [Google Scholar] [CrossRef]

- Pan, S.; Makinwa, K.A.A. A 6.6-μW Wheatstone-Bridge Temperature Sensor for Biomedical Applications. IEEE Solid-State Circuits Lett. 2020, 3, 334–337. [Google Scholar] [CrossRef]

- Tang, Z.; Fang, Y.; Yu, X.-P.; Shi, Z.; Lin, L.; Tan, N.N. A Dynamic-Biased Resistor-Based CMOS Temperature Sensor with a Duty-Cycle-Modulated Output. IEEE Trans. Circuits Syst. II Express Briefs 2020, 67, 1504–1508. [Google Scholar] [CrossRef]

- Pan, S.; Makinwa, K.A.A. 3.6 A CMOS Resistor-Based Temperature Sensor with a 10fJ·K2 Resolution FoM and 0.4 °C (30) Inaccuracy From −55 °C to 125 °C After a 1-point Trim. In Proceedings of the 2020 IEEE International Solid- State Circuits Conference—(ISSCC), San Francisco, CA, USA, 16–20 February 2020; pp. 68–70. [Google Scholar] [CrossRef]

- Pan, S.; Angevare, J.A.; Makinwa, K.A.A. 5.4 A Hybrid Thermal-Diffusivity/Resistor-Based Temperature Sensor with a Self-Calibrated Inaccuracy of ±0.25 °C (3 Σ) from −55 °C to 125 °C. In Proceedings of the 2021 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 13–22 February 2021; pp. 78–80. [Google Scholar] [CrossRef]

- Jan, A.; Youngcheol, C.; Kofi, M. 5.3 A Highly Digital 2210 μm 2 Resistor-Based Temperature Sensor with a 1-Point Trimmed Inaccuracy of ± 1.3 °C (3 σ) from −55 °C to 125 °C in 65 nm CMOS. In Proceedings of the 2021 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 13–22 February 2021; pp. 76–78. [Google Scholar] [CrossRef]

- Jain, A.; Jiang, H.; Pochet, C.; Hall, D.A. A 310 nW Temperature Sensor Achieving 9.8 mK Resolution using a DFLL-based Readout Circuit. IEEE Trans. Circuits Syst. II Express Briefs 2021, 69, 704–708. [Google Scholar] [CrossRef]

- Ku, H.-S.; Choi, S.; Sim, J.-Y. A 12μs-Conversion, 20 mK-Resolution Temperature Sensor Based on SAR ADC. IEEE Trans. Circuits Syst. II Express Briefs 2021, 69, 789–793. [Google Scholar] [CrossRef]

- Makinwa, K. Smart Temperature Sensor Survey. Available online: https://ei.tudelft.nl/smart_temperature/ (accessed on 26 November 2021).

- Byun, S. Categorization and Characterization of Time Domain CMOS Temperature Sensors. Sensors 2020, 20, 6700. [Google Scholar] [CrossRef] [PubMed]

- Elmasry, M.I. Digital MOS Integrated Circuits; Wiley: New York, NY, USA, 1981; pp. 11–12. [Google Scholar]

- Xie, S.; Ng, W.T. An all-digital self-calibrated delay-line based temperature sensor for VLSI thermal sensing and management. Integr. VLSI J. 2015, 51, 107–117. [Google Scholar] [CrossRef]

| Reference. | Year | Technology (nm) | Area (mm2) | PP IA (°C) 1 | Min (°C) | Max (°C) | Rel. IA (%) 1 | Supply (V) | Conversion Time (ms) | µW | nJ | Resolution (°C) | RFOM 2 | Power Supply Sensitivity (°C/V) | Type |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| [22] | 2021 | 55 | 0.0024 | 0.5 | −40 | 85 | 0.4 | 0.8 | 1.04 | 0.86 | 0.8944 | 0.017 | 0.000258 | 5.8 | type II |

| [27] | 2021 | 130 | 0.07 | 0.84 | 0 | 80 | 1.05 | 0.95 | 59 | 0.196 | 11.564 | 0.1 | 0.11564 | 13.7 | type II |

| [28] | 2020 | 55 | 0.00177 | 1.4 | −40 | 125 | 0.85 | 0.8 | 1.31 | 9.8 | 12.838 | 0.013 | 0.00217 | 5.76 | type II |

| [26] | 2020 | 65 | 0.32 | 1.7 | −30 | 70 | 1.7 | 0.8 | 765 | 0.0064 | 4.896 | 0.075 | 0.02754 | 2.8 | type II |

| [33] | 2019 | 65 | 0.63 | 1.56 | 0 | 100 | 1.56 | 0.5 | 300 | 0.000763 | 0.2289 | 0.3 | 0.020601 | 8.4 | type III |

| [11] | 2019 | 180 | 0.074 | 2.1 | −20 | 80 | 2.1 | 0.8 | 839 | 0.011 | 9.2 | 0.145 | 0.194 | 3.8 | type I |

| [32] | 2019 | 65 | 0.013 | 4.5 | −20 | 100 | 3.8 | 0.9 | 34 | 0.0006 | 0.022 | 0.25 | 0.00137 | N/A | type III |

| [31] | 2014 | 160 | 0.085 | 0.8 | −40 | 125 | 0.5 | 0.85 | 6 | 0.6 | 3.6 | 0.063 | 0.01417 | N/A | type II |

| [24] | 2014 | 65 | 0.022 | 2.6 | 0 | 100 | 2.6 | 0.4 | 25 | 0.28 | 7 | 0.25 | 0.4375 | N/A | type II |

| [12] | 2016 | 65 | 0.004 | 1.8 | 0 | 100 | 1.8 | 1 | 0.022 | 154 | 3.4 | 0.3 | 0.30492 | N/A | type I |

| [19] | 2015 | 25 | 0.02 | 4 | 20 | 95 | 5.3 | 1.1 | 0.142 | 9 | 1.3 | 0.05 | 0.0032 | N/A | type II |

| [20] | 2017 | 180 | 0.0087 | 0.41 | −20 | 100 | 0.34 | 1.2 | 8 | 0.1 | 0.6 | 0.073 | 0.0032 | N/A | type II |

| [14] | 2017 | 180 | 0.089 | 2 | −20 | 80 | 2 | 1.8 | 800 | 0.8 | 660 | 0.09 | 5.3136 | N/A | type I |

| [21] | 2018 | 28 | 0.001 | 2.7 | −5 | 85 | 3 | 0.9 | 0.036 | 56 | 2 | 0.76 | 1.16444 | N/A | type II |

| [30] | 2011 | 160 | 0.12 | 0.8 | −55 | 125 | 0.4 | 1.6 | 200 | 7.5 | 1500 | 0.033 | 1.63786 | N/A | type II |

| [30] | 2011 | 160 | 0.12 | 0.2 | −55 | 125 | 0.1 | 1.6 | 200 | 7.5 | 1500 | 0.033 | 1.63786 | N/A | type II |

| [4] | 2012 | 130 | 0.12 | 8 | 0 | 100 | 8 | 1.2 | 0.2 | 1200 | 240 | 0.78 | 146.016 | N/A | type I |

| [29] | 2012 | 180 | 0.475 | 1.6 | −50 | 150 | 0.8 | 1.5 | 10 | 69 | 690 | 0.13 | 11.661 | N/A | type II |

| [23] | 2013 | 180 | 0.05 | 4.6 | 0 | 100 | 4.6 | 1.8 | 100 | 0.2 | 23 | 0.3 | 2.07 | N/A | type II |

| [13] | 2013 | 44 | 0.041 | 4.1 | 35 | 105 | 5.8 | 1.1 | 0.128 | 23.1 | 3 | 1.94 | 11.1 | N/A | type I |

| [9] | 2013 | 65 | 0.008 | 3 | 0 | 110 | 2.7 | 1.2 | 0.002 | 500 | 1.1 | 0.94 | 0.94103 | N/A | type I |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Xie, S. The Design Considerations and Challenges in MOS-Based Temperature Sensors: A Review. Electronics 2022, 11, 1019. https://doi.org/10.3390/electronics11071019

Xie S. The Design Considerations and Challenges in MOS-Based Temperature Sensors: A Review. Electronics. 2022; 11(7):1019. https://doi.org/10.3390/electronics11071019

Chicago/Turabian StyleXie, Shuang. 2022. "The Design Considerations and Challenges in MOS-Based Temperature Sensors: A Review" Electronics 11, no. 7: 1019. https://doi.org/10.3390/electronics11071019

APA StyleXie, S. (2022). The Design Considerations and Challenges in MOS-Based Temperature Sensors: A Review. Electronics, 11(7), 1019. https://doi.org/10.3390/electronics11071019