Fault Tolerance Analysis of Five-Level Neutral-Point-Clamped Inverters under Clamping Diode Open-Circuit Failure

Abstract

:1. Introduction

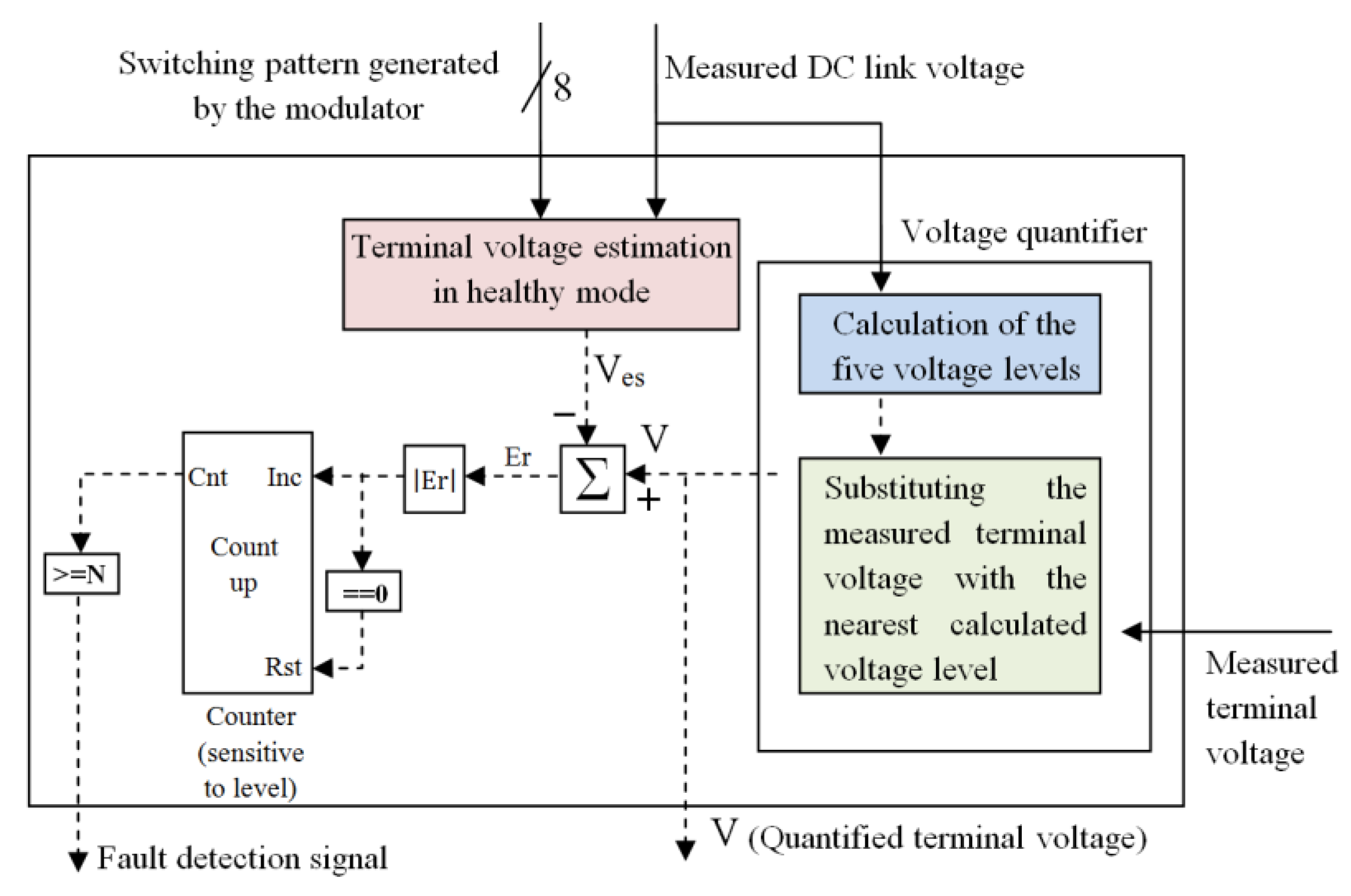

2. Principle of the Clamping Diode Fault Diagnosis Approach

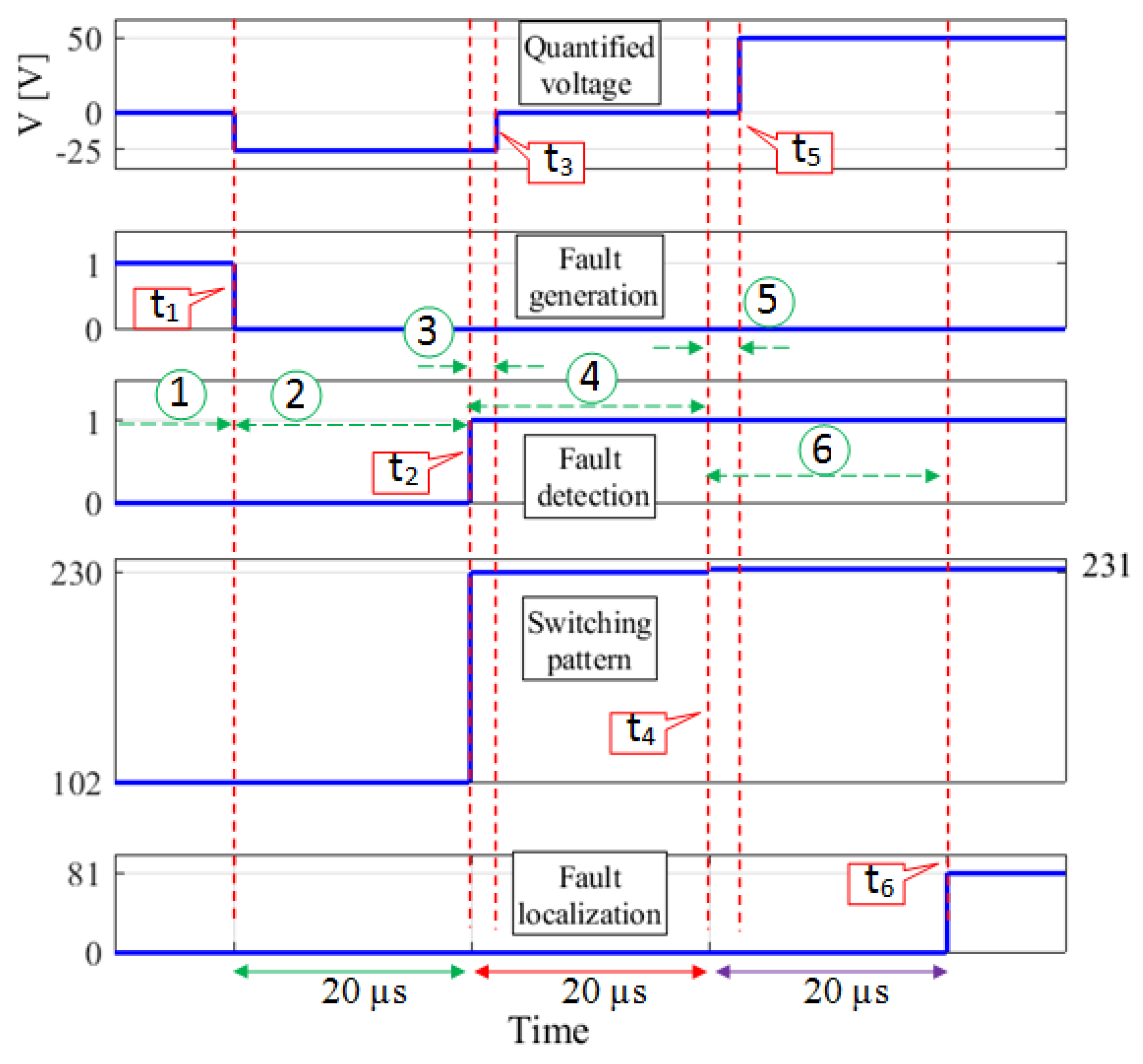

2.1. Fault Detection Strategy

2.2. Fault Localization Strategy

3. Principle of the Proposed Fault-Tolerant Strategy

3.1. Open-Circuit Fault in DC1 or DC2

3.2. Open-Circuit Fault in DC3 or DC4

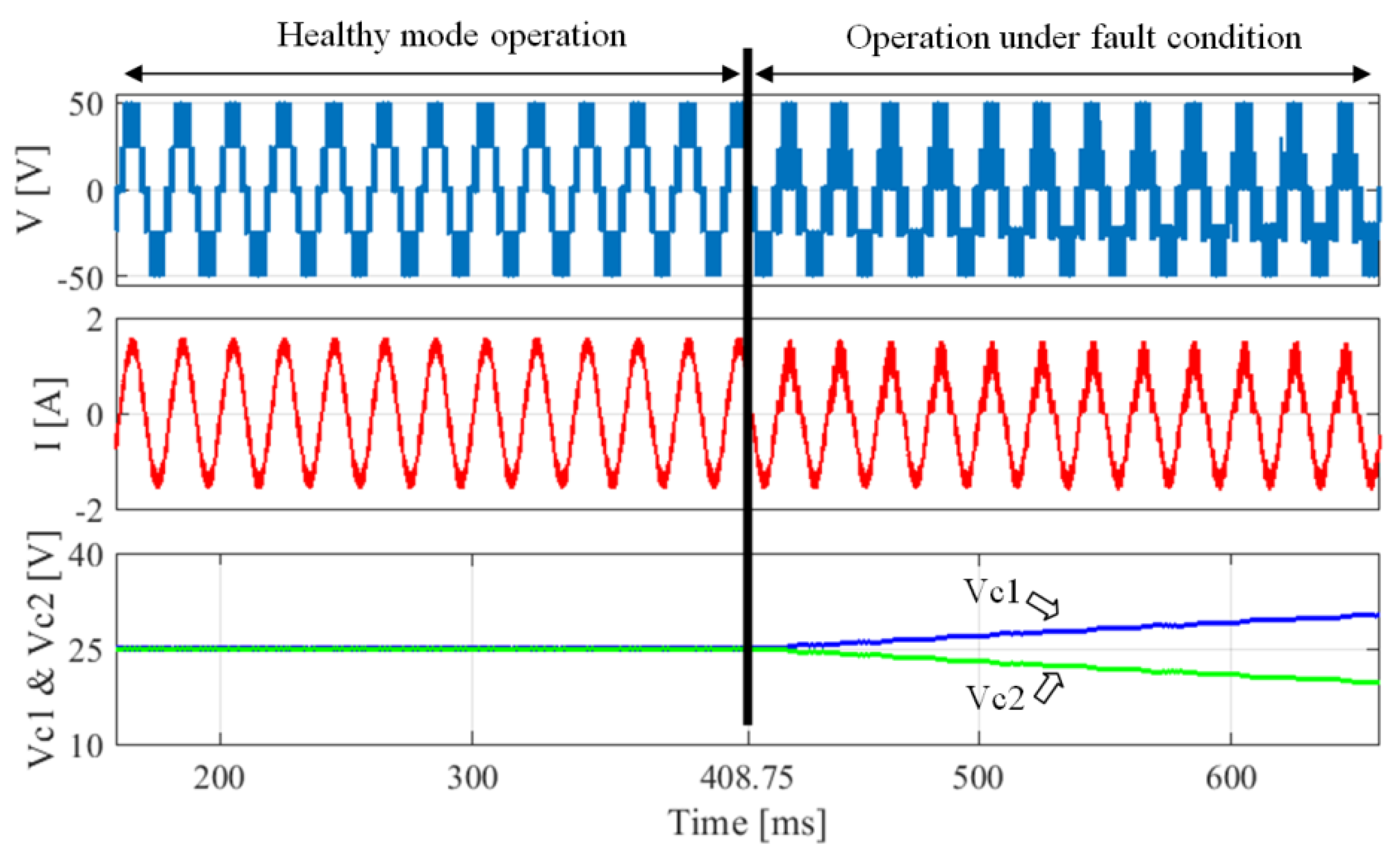

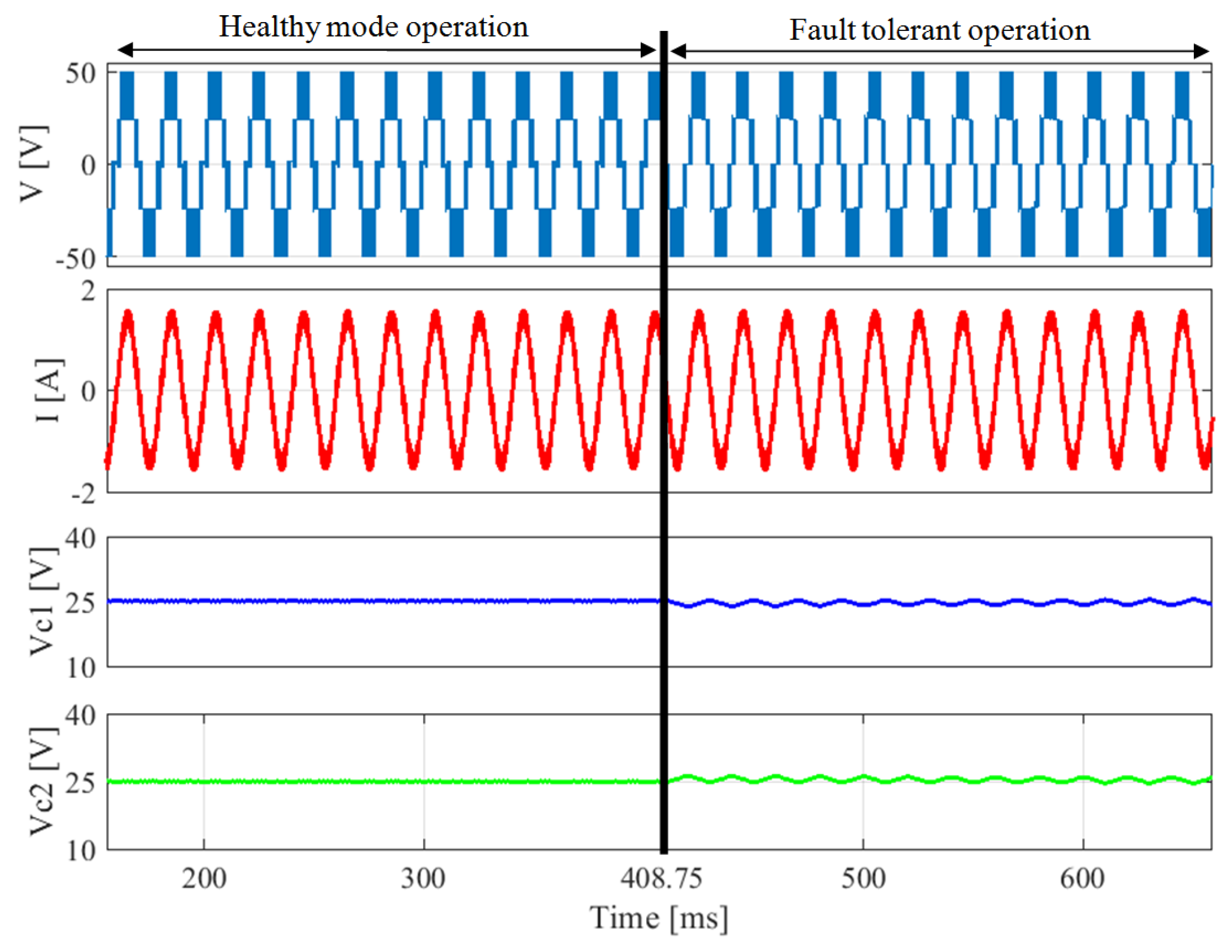

4. Simulation Results

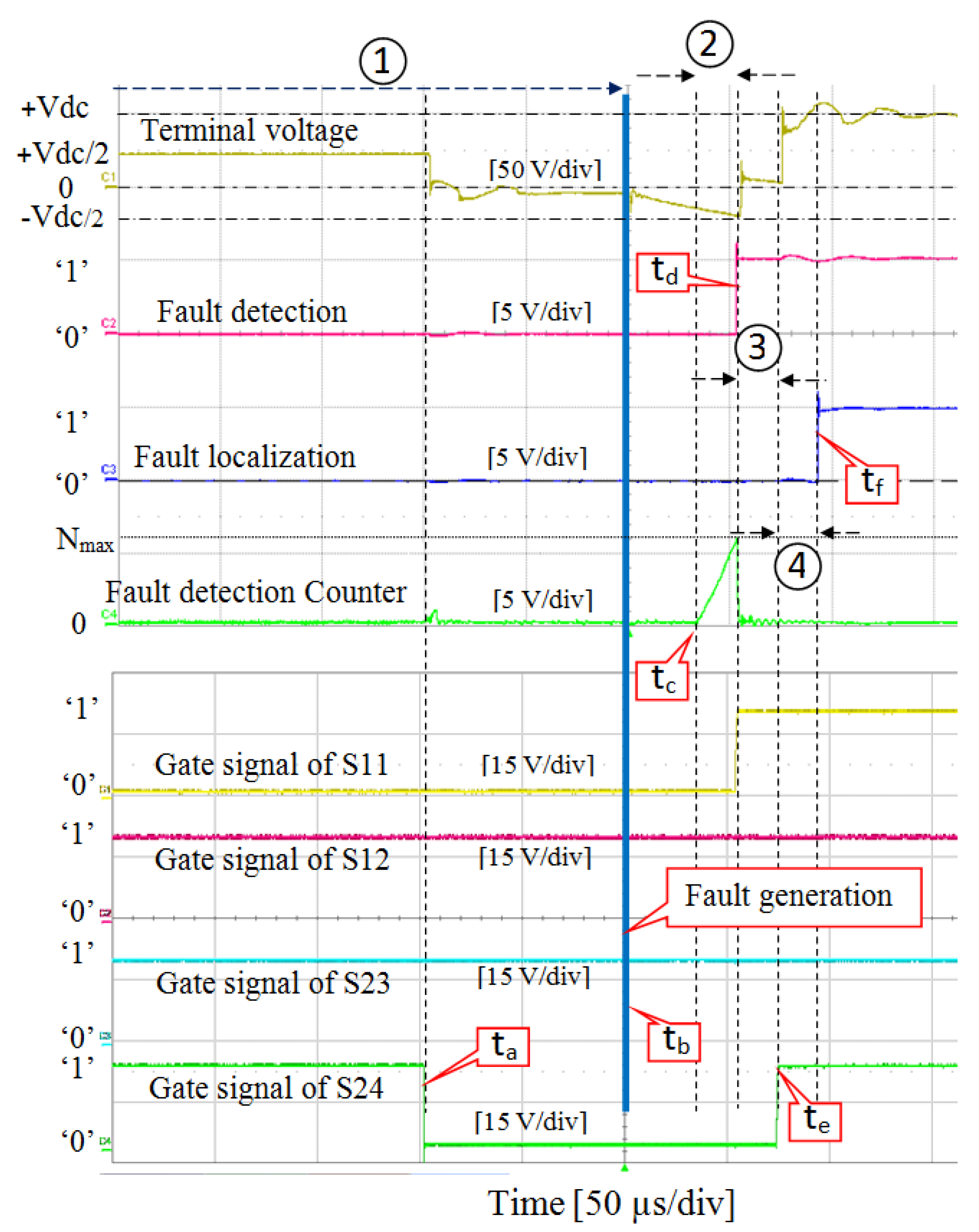

4.1. Fault Diagnosis Strategy

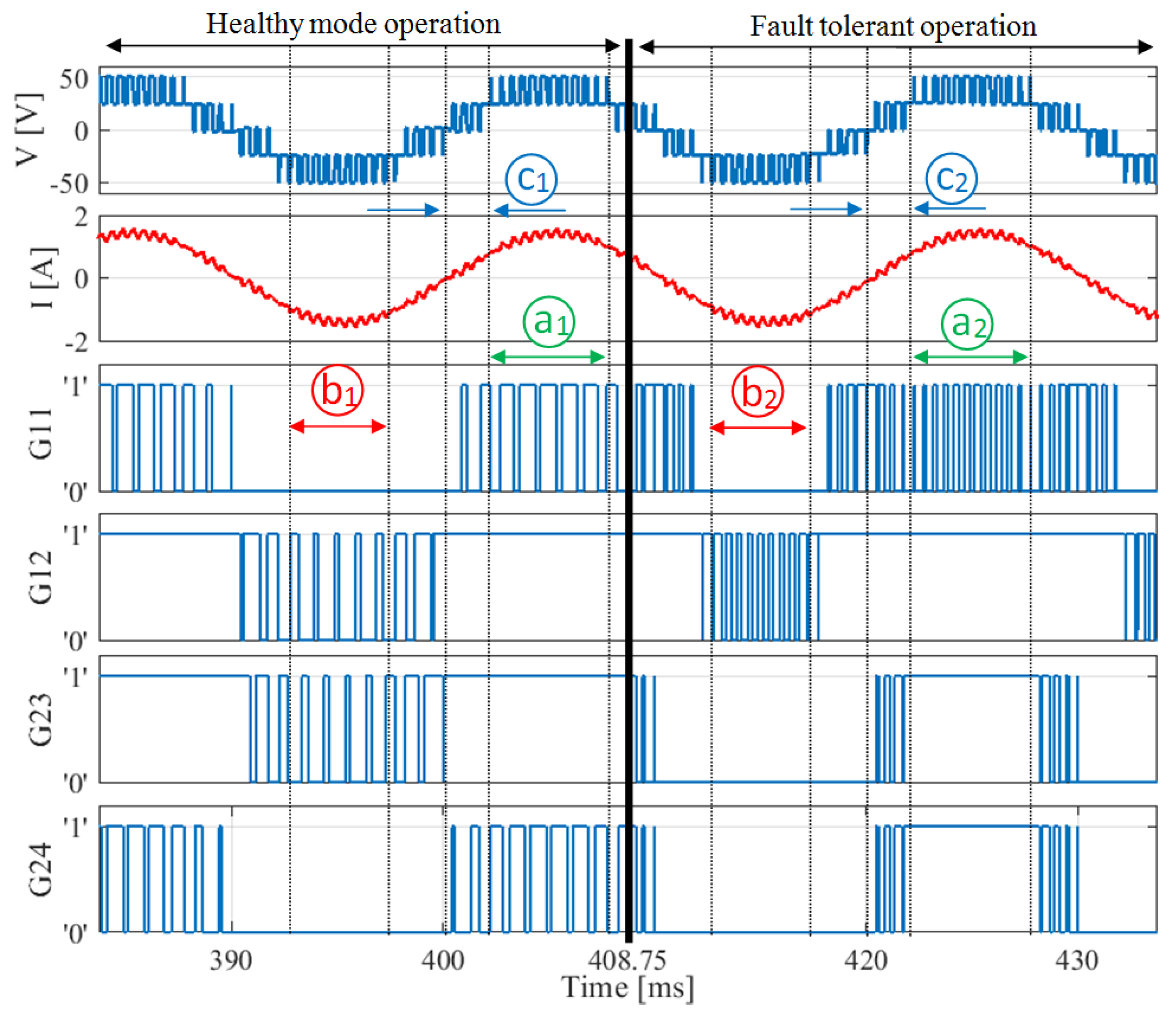

4.2. Fault-Tolerant Strategy

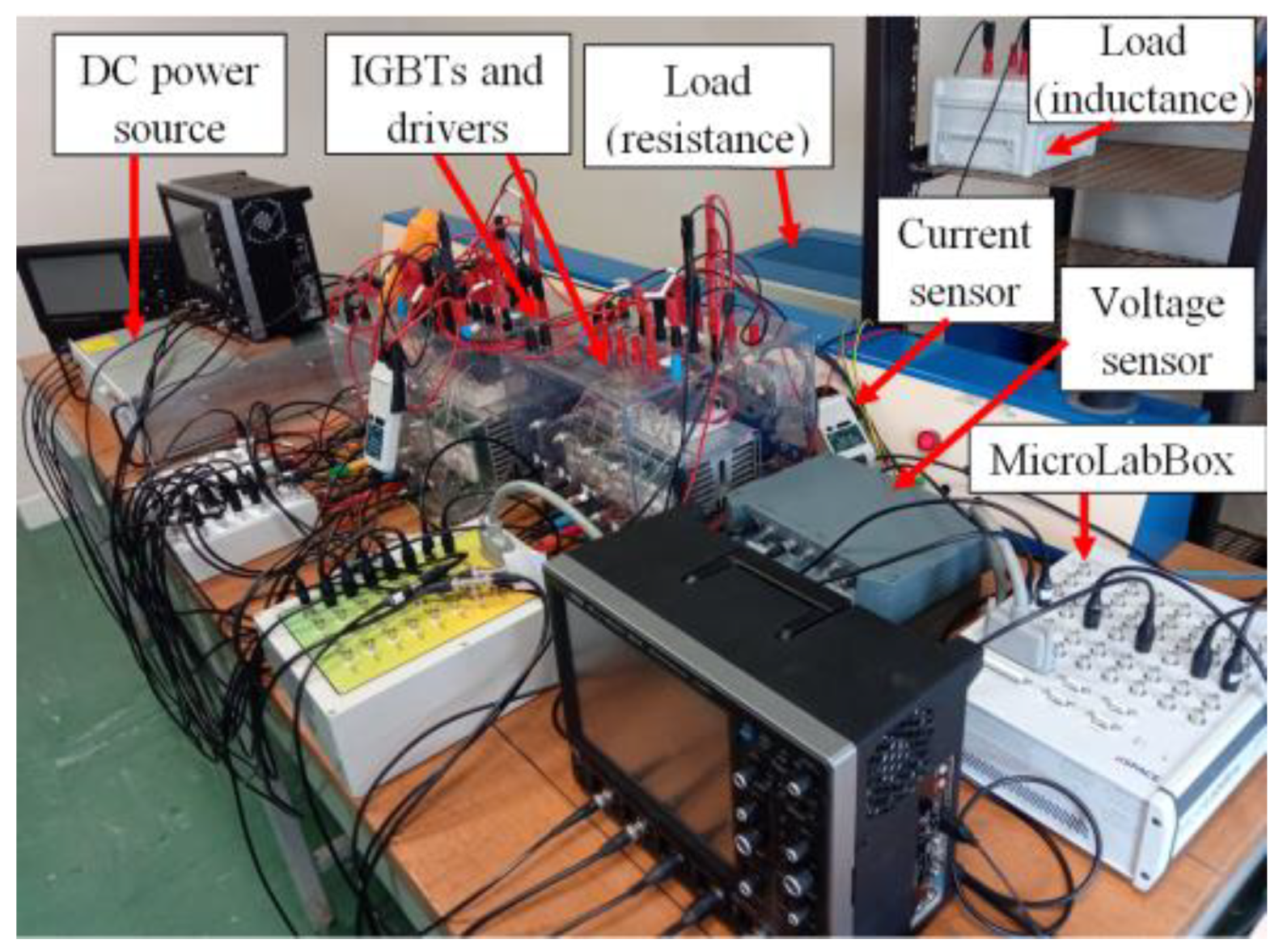

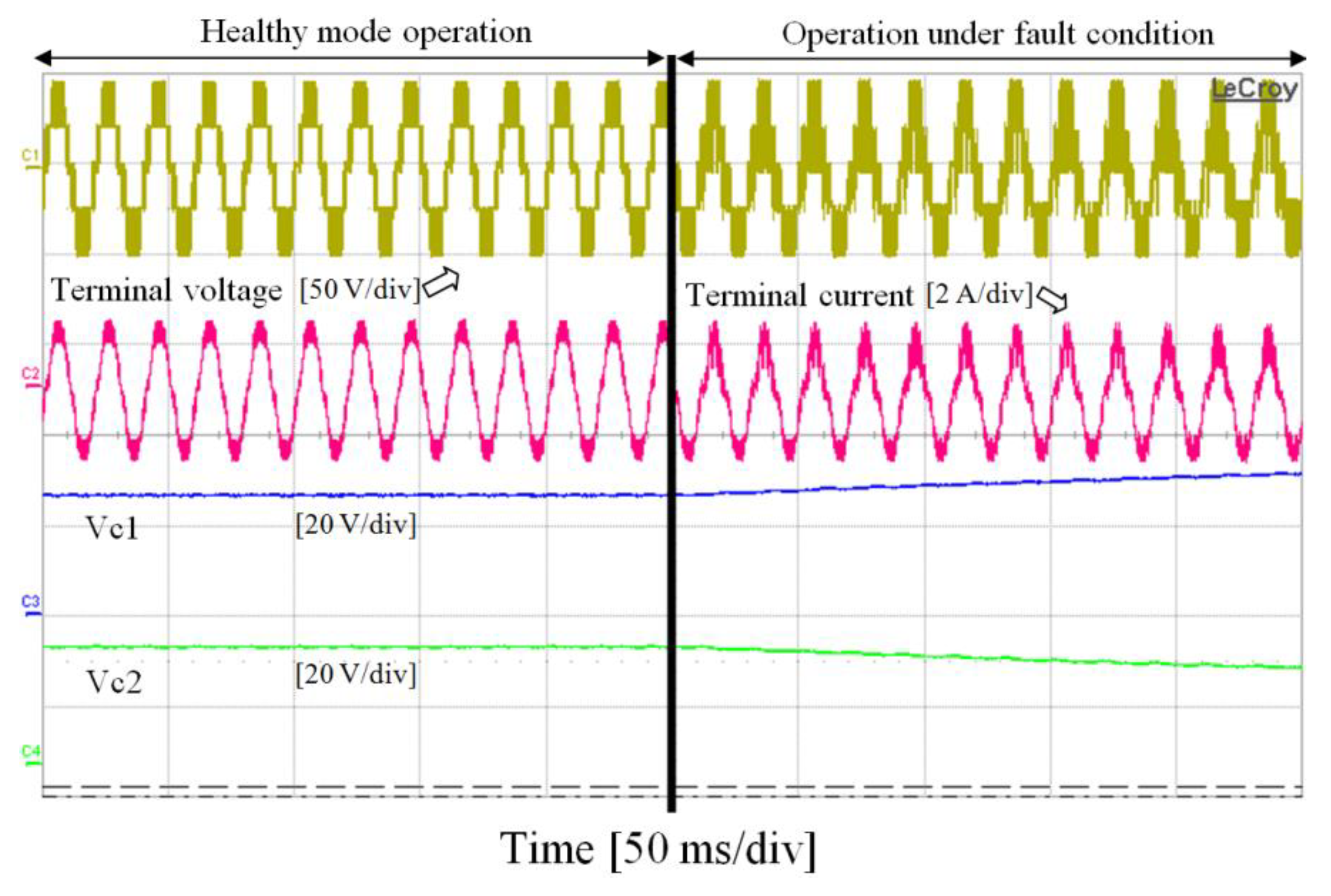

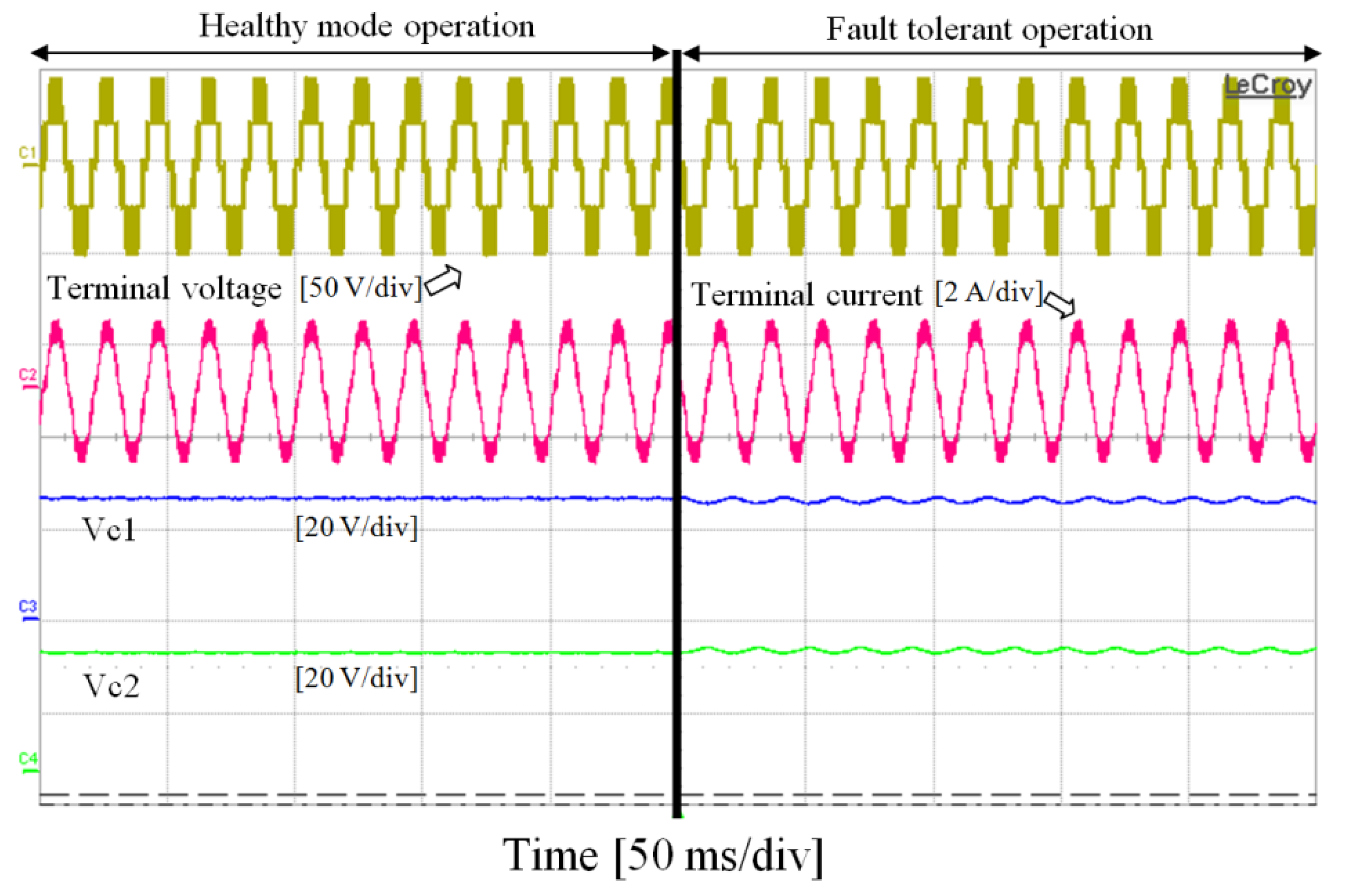

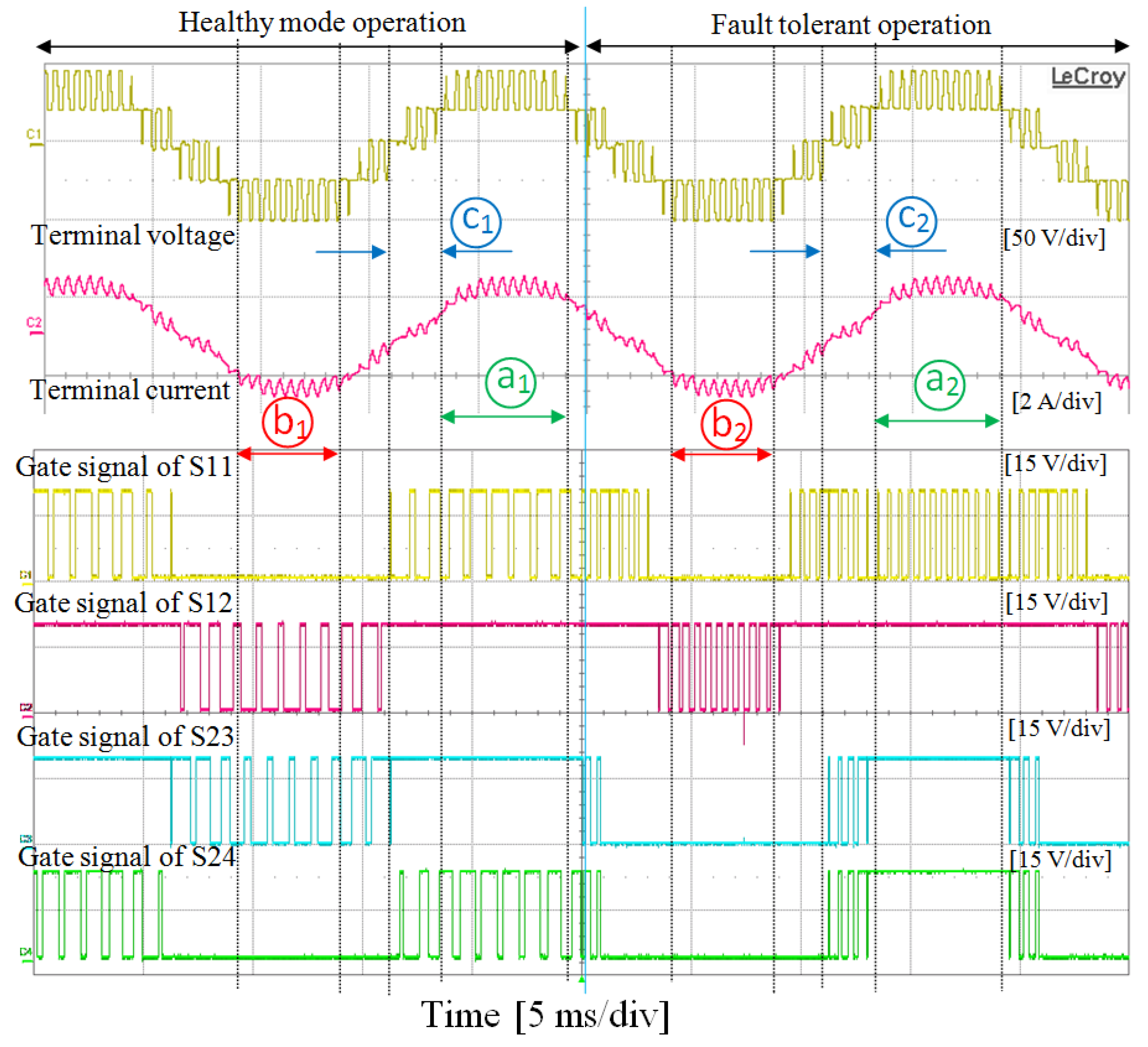

5. Experimental Results

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Gautam, S.P.; Kumar, L.; Gupta, S.; Agrawal, N. A single-phase five-level inverter topology with switch fault-tolerance capabilities. IEEE Trans. Ind. Electron. 2017, 64, 2004–2014. [Google Scholar] [CrossRef]

- Rodriguez, J.; Lai, J.S.; Peng, F.Z. Multilevel inverters: A survey of topologies, controls, and applications. IEEE Trans. Ind. Electron. 2002, 49, 724–738. [Google Scholar] [CrossRef] [Green Version]

- Wu, B. High-Power Converters AC Drives; Wiley: Hoboken, NJ, USA, 2006. [Google Scholar]

- Lee, J.; Lee, K. Open-switch fault tolerance control for three-level NPC/T-Type rectifier in wind turbine systems. IEEE Trans. Ind. Electron. 2015, 62, 1012–1021. [Google Scholar] [CrossRef]

- Lee, J.; Lee, K. Open-circuit fault-tolerant control for outer switches of three-level rectifier in wind turbine systems. IEEE Trans. Power Electron. 2016, 31, 3806–3815. [Google Scholar] [CrossRef]

- Ceballos, S.; Pou, J.; Zaragoza, J.; Robles, E.; Villate, J.L.; Martin, J.L. Fault-tolerant neutral-point-clamped converter solutions based on including a fourth resonant leg. IEEE Trans. Ind. Electron. 2011, 58, 2293–2303. [Google Scholar] [CrossRef]

- Ceballos, S.; Pou, J.; Robles, E.; Gabiola, I.; Zaragoza, J.; Villate, J.L.; Boroyevich, D. Three-level converter topologies with switch breakdown fault-tolerance capability. IEEE Trans. Ind. Electron. 2008, 55, 982–995. [Google Scholar] [CrossRef]

- Rao, M.; Sivakumar, K. A fault-tolerant single phase five-level inverter for grid independent PV systems. IEEE Trans. Ind. Electron. 2015, 62, 7569–7577. [Google Scholar]

- Choi, U.; Lee, J.; Blaabjerge, F.; Lee, K. Open-circuit fault diagnosis and fault-tolerant control for a grid-connected npc inverter. IEEE Trans. Power Electron. 2016, 31, 7234–7247. [Google Scholar] [CrossRef]

- Li, S.; Xu, L. Strategies of fault tolerant operation for three-level PWM inverters. IEEE Trans. Power Electron. 2006, 21, 933–940. [Google Scholar] [CrossRef]

- Ceballos, S.; Pou, J.; Robles, E.; Zaragoza, J.; Martin, J.L. Performance evaluation of fault-tolerant neutral-point-clamped converters. IEEE Trans. Ind. Electron. 2010, 57, 2709–2718. [Google Scholar] [CrossRef]

- Abadi, M.B.; Mendes, A.M.S.; Cruz, S.M.A. Three-level NPC inverter fault diagnosis by the average current Park’s vector approach. In Proceedings of the 20th ICEM, Marseille, France, 2–5 September 2012; pp. 1893–1898. [Google Scholar]

- Mendes, A.M.S.; Abadi, M.B.; Cruz, S.M.A. Fault diagnosis algorithm for three-level neutral point clamped AC motor drives based on average current Park’s vector. IET Power Electron. 2014, 7, 1127–1137. [Google Scholar] [CrossRef]

- Lee, J.S.; Lee, K.B.; Blaabjerg, F. Open-switch fault detection method of a back-to-back converter using NPC topology for wind turbine systems. IEEE Trans. Ind. Appl. 2015, 50, 325–335. [Google Scholar] [CrossRef]

- Kim, T.J.; Lee, W.C.; Hyun, D.S. Detection method for open circuit fault in neutral-point-clamped inverter systems. IEEE Trans. Ind. Electron. 2009, 56, 2754–2763. [Google Scholar]

- Caseiro, L.M.A.; Mendes, A.M.S. Real-time IGBT open-circuit fault diagnosis in three-level neutral-point-clamped voltage-source rectifiers based on instant voltage error. IEEE Trans. Ind. Electron. 2015, 62, 1669–1678. [Google Scholar] [CrossRef]

- Choi, U.M.; Jeong, H.G.; Lee, K.B.; Blaabjerg, F. Method for detecting an open-switch fault in a grid-connected NPC inverter system. IEEE Trans. Power Electron. 2012, 27, 2726–2739. [Google Scholar] [CrossRef]

- Fazio, P.; Maragliano, G.; Marchesoni, M.; Parodi, G. A new fault detection method for NPC converters. In Proceedings of the 14th European Conference on Power Electronics and Applications, Birmingham, UK, 30 August–1 September 2011; pp. 1–10. [Google Scholar]

- Mendes, A.M.S.; Abadi, M.B.; Cruz, S.M.A. Method to diagnose open-circuit faults in active power switches and clamp-diodes of three-level neutral-point clamped inverters. IET Elect. Power Appl. 2016, 10, 623–632. [Google Scholar]

- Ge, X.; Pu, J.; Geo, B.; Liu, Y. An open-circuit fault diagnosis approach for single-phase three-level neutral-point-clamped converters. IEEE Trans. Power Electron. 2018, 33, 2559–2570. [Google Scholar] [CrossRef]

- Abari, I.; Lahouar, A.; Hamouda, M.; Slama, J.B.H.; Al-Haddad, K. Fault detection methods for three-Level NPC inverter based on DC-bus electromagnetic signatures. IEEE Trans. Ind. Electron. 2018, 65, 5224–5236. [Google Scholar] [CrossRef]

- Shahbazi, M.; Poure, P.; Saadate, S.; Zolghadri, M.R. Fault-tolerant five-level converter topology with FPGA-based reconfigurable control. IEEE Trans. Ind. Electron. 2013, 60, 2284–2294. [Google Scholar] [CrossRef] [Green Version]

| Switching State | Terminal Voltage | Conducting Components (I > 0) | Conducting Components (I < 0) |

|---|---|---|---|

| 1 | +Vdc | S11, S12, S23, S24 | D11, D12, D23, D24 |

| 2 | +Vdc/2 | S11, S12, S23, DC4 | D11, D12, S22, DC3 |

| 3 | +Vdc/2 | DC1, S12, S23, S24 | DC2, S13, D23, D24 |

| 4 | 0 | S11, S12, D22, D21 | D11, D12, S21, S22 |

| 5 | 0 | DC1, S12, S23, DC4 | DC2, S13, S22, DC3 |

| 6 | 0 | D14, D13, S23, S24 | S13, S14, D24, D23 |

| 7 | −Vdc/2 | DC1, S12, D22, D21 | DC2, S13, S22, S21 |

| 8 | −Vdc/2 | D14, D13, S23, DC4 | S13, S14, DC3, S22 |

| 9 | −Vdc | D14, D13, D22, D21 | S13, S14, S22, S21 |

| Switching State | Terminal Voltage | S11 | S12 | S13 | S14 | S21 | S22 | S23 | S24 | Attributed Decimal Number |

|---|---|---|---|---|---|---|---|---|---|---|

| 1 | +Vdc | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 195 |

| 2 | +Vdc/2 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 198 |

| 3 | +Vdc/2 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 99 |

| 4 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 204 |

| 5 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 102 |

| 6 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 51 |

| 7 | −Vdc/2 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 108 |

| 8 | −Vdc/2 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 54 |

| 9 | −Vdc | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 60 |

| State | Faulty Switch or Diode | Conducting Components (Terminal Voltage) | Second Step | Conducting Components (Terminal Voltage) |

|---|---|---|---|---|

| 1 | S11 | DC1, S12, S23, S24 (Vdc/2) | S24 is switched off | DC1, S12, S23, DC4 (0) |

| 1 | S24 | S11, S12, S23, DC4 (Vdc/2) | S11, S12, S23, DC4 (Vdc/2) | |

| 1 | S12 | D14, D13, S23, S24 (0) | S23 is switched off | D14, D13, D22, D21 (−Vdc) |

| 1 | S23 | S11, S12, D22, D21 (0) | S11, S12, D22, D21 (0) | |

| 2 | S12 | D14, D13, S23, DC4 (−Vdc/2) | S12 is identified in the first step. | |

| 2 | S11 | DC1, S12, S23, DC4 (0) | S24 is switched on | DC1, S12, S23, S24 (Vdc/2) |

| 2 | S23 | S11, S12, D22, D21 (0) | S11, S12, D22, D21 (0) | |

| 2 | DC4 | S11, S12, D22, D21 (0) | S11, S12, S23, S24 (Vdc) | |

| 3 | S23 | DC1, S12, D22, D21 (−Vdc/2) | S23 is identified in the first step. | |

| 3 | S12 | D14, D13, S23, S24 (0) | S11 is switched on | D14, D13, S23, S24 (0) |

| 3 | DC1 | D14, D13, S23, S24 (0) | S11, S12, S23, S24 (Vdc) | |

| 3 | S24 | DC1, S12, S23, DC4 (0) | S11, S12, S23, DC4 (Vdc/2) | |

| 5 | S12 | D14, D13, S23, DC4 (−Vdc/2) | S11 is switched on | D14, D13, S23, DC4 (−Vdc/2) |

| 5 | DC1 | D14, D13, S23, DC4 (−Vdc/2) | S11, S12, S23, DC4 (Vdc/2) | |

| 5 | S23 | DC1, S12, D22, D21 (−Vdc/2) | S11, S12, D22, D21 (0) (see Table 5 for third step) | |

| 5 | DC4 | DC1, S12, D22, D21 (−Vdc/2) | S11, S12, D22, D21 (0) (see Table 5 for third step) | |

| 7 | S12 | D14, D13, D22, D21 (−Vdc) | S11 is switched on | D14, D13, D22, D21 (−Vdc) |

| 7 | DC1 | D14, D13, D22, D21 (−Vdc) | S11, S12, D22, D21 (0) | |

| 8 | S23 | D14, D13, D22, D21 (−Vdc) | S24 is switched on | D14, D13, D22, D21 (−Vdc) |

| 8 | DC4 | D14, D13, D22, D21 (−Vdc) | D14, D13, S23, S24 (0) | |

| State | Faulty Switch or Diode | Third Step | Conducting Components (Terminal Voltage) |

|---|---|---|---|

| 5, (I > 0) | S23 | S24 is switched on | S11, S12, D22, D21 (0) |

| 5, (I > 0) | DC4 | S11, S12, S23, S24 (Vdc) | |

| 5, (I < 0) | S22 | S21 is switched on | S13, S14, D23, D24 (0) |

| 5, (I < 0) | DC3 | S13, S14, S21, S22 (−Vdc) |

| Faulty Clamping Diode | Infeasible Switching State | Substituted Switching State |

|---|---|---|

| DC1 | 3 | 2 |

| 5 | 4 or 6 | |

| 7 | 8 | |

| DC2 | 3 | 2 |

| 5 | 4 or 6 | |

| 7 | 8 | |

| DC3 | 2 | 3 |

| 5 | 4 or 6 | |

| 8 | 7 | |

| DC4 | 2 | 3 |

| 5 | 4 or 6 | |

| 8 | 7 |

| Parameters | Values |

|---|---|

| Load resistance | 27.7 Ω |

| Load inductance | 9 mH |

| DC link voltage | 50 V |

| DC link capacitor | 2.2 mF |

| Switching frequency | 1 kHz |

| Modulation index | 0.8 |

| References | Drawback |

|---|---|

| [1,4,5,6,7,8] | Are not able to ensure fault-tolerant operation in case of fault event in a clamping diode |

| [9,11] | Output voltage THD increases during post-fault operation |

| [10] | The rated voltage is not restored during post-fault operation |

| [12,18] | Are not able to locate a defective clamping diode |

| [19] | Extra sensors are required for fault diagnosis |

| [20] | Knowing the grid parameters is required for fault diagnosis |

| [21] | External antennas and filters are required for fault diagnosis |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ahmadi, S.; Poure, P.; Saadate, S.; Khaburi, D.A. Fault Tolerance Analysis of Five-Level Neutral-Point-Clamped Inverters under Clamping Diode Open-Circuit Failure. Electronics 2022, 11, 1461. https://doi.org/10.3390/electronics11091461

Ahmadi S, Poure P, Saadate S, Khaburi DA. Fault Tolerance Analysis of Five-Level Neutral-Point-Clamped Inverters under Clamping Diode Open-Circuit Failure. Electronics. 2022; 11(9):1461. https://doi.org/10.3390/electronics11091461

Chicago/Turabian StyleAhmadi, Sajjad, Philippe Poure, Shahrokh Saadate, and Davood Arab Khaburi. 2022. "Fault Tolerance Analysis of Five-Level Neutral-Point-Clamped Inverters under Clamping Diode Open-Circuit Failure" Electronics 11, no. 9: 1461. https://doi.org/10.3390/electronics11091461