3D Heterogenous Integrated Wideband Switchable Bandpass Filter Bank for Millimeter Wave Applications

Abstract

:1. Introduction

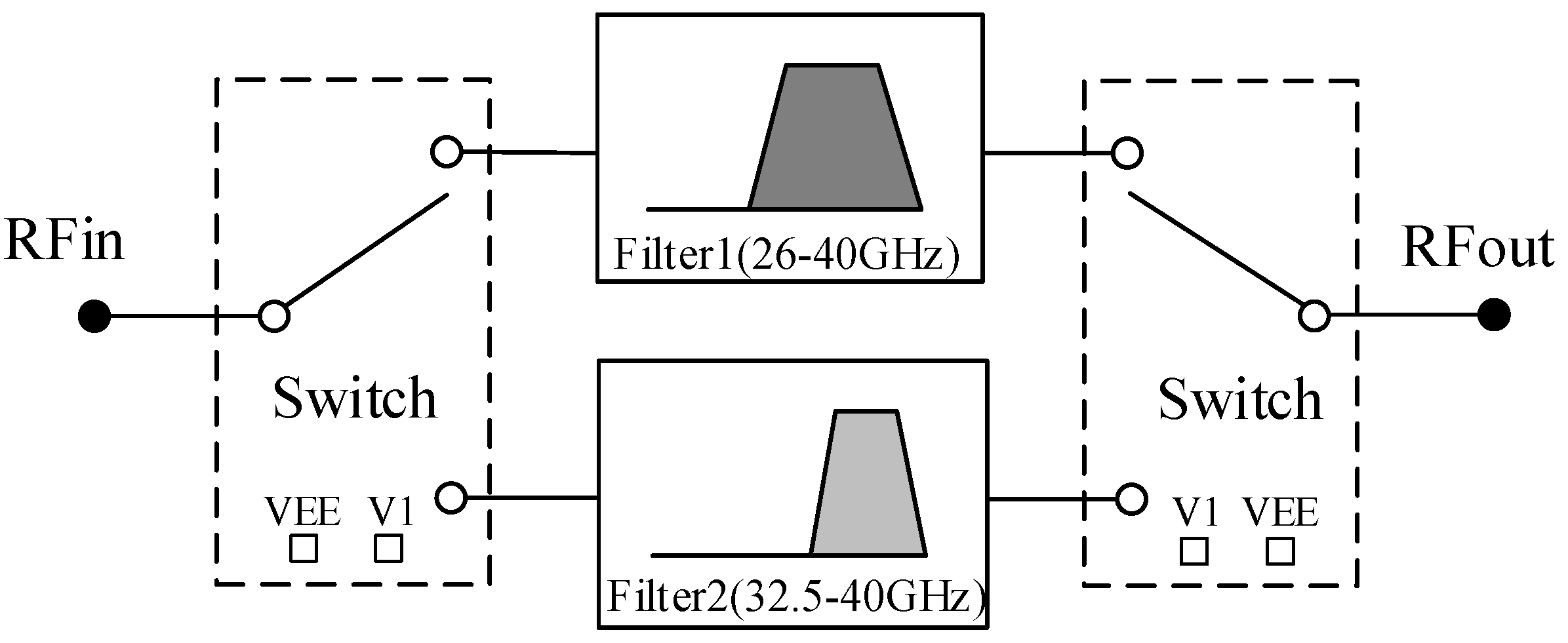

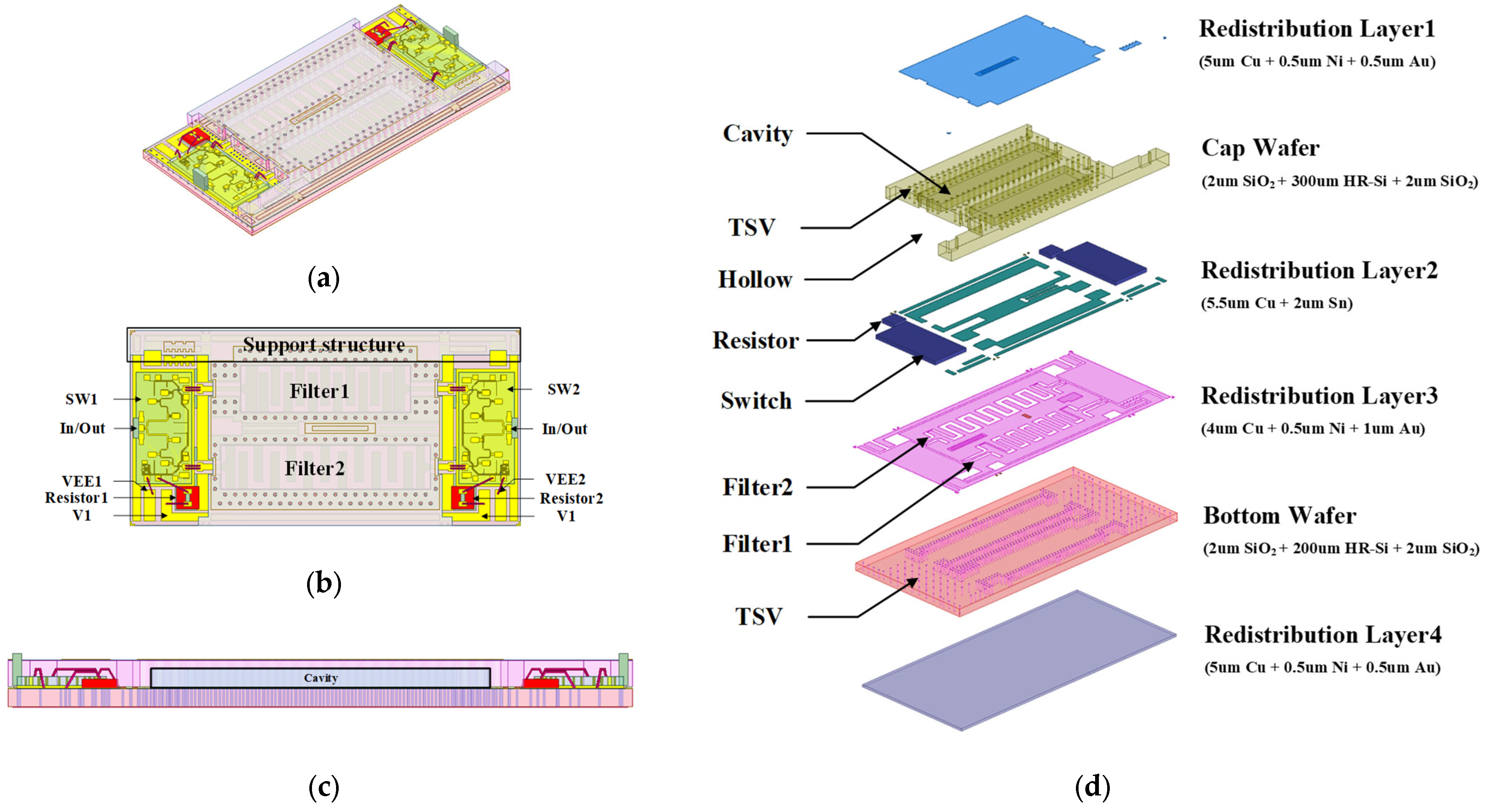

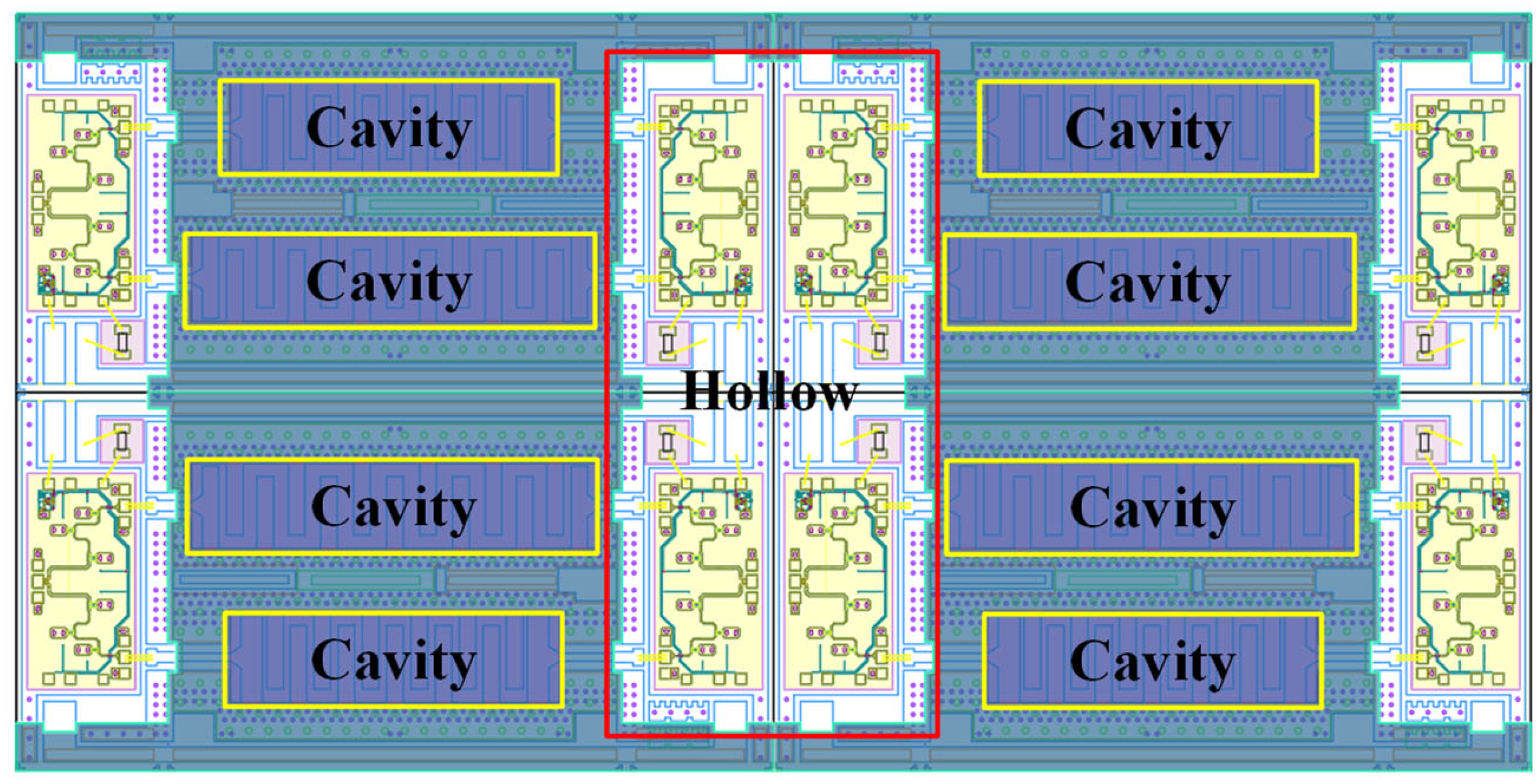

2. Design of Switchable Filter Bank

2.1. System Architecture

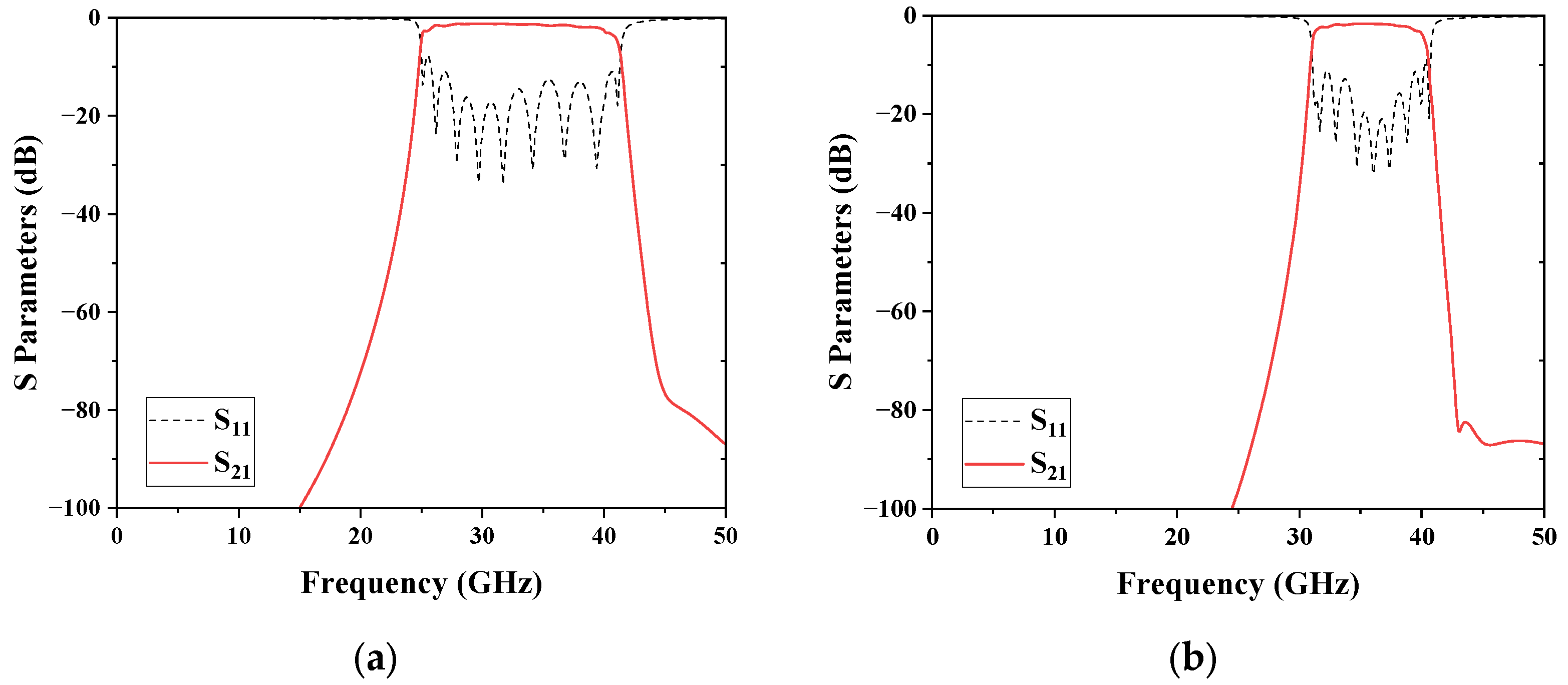

2.2. Bandpass Filter Design

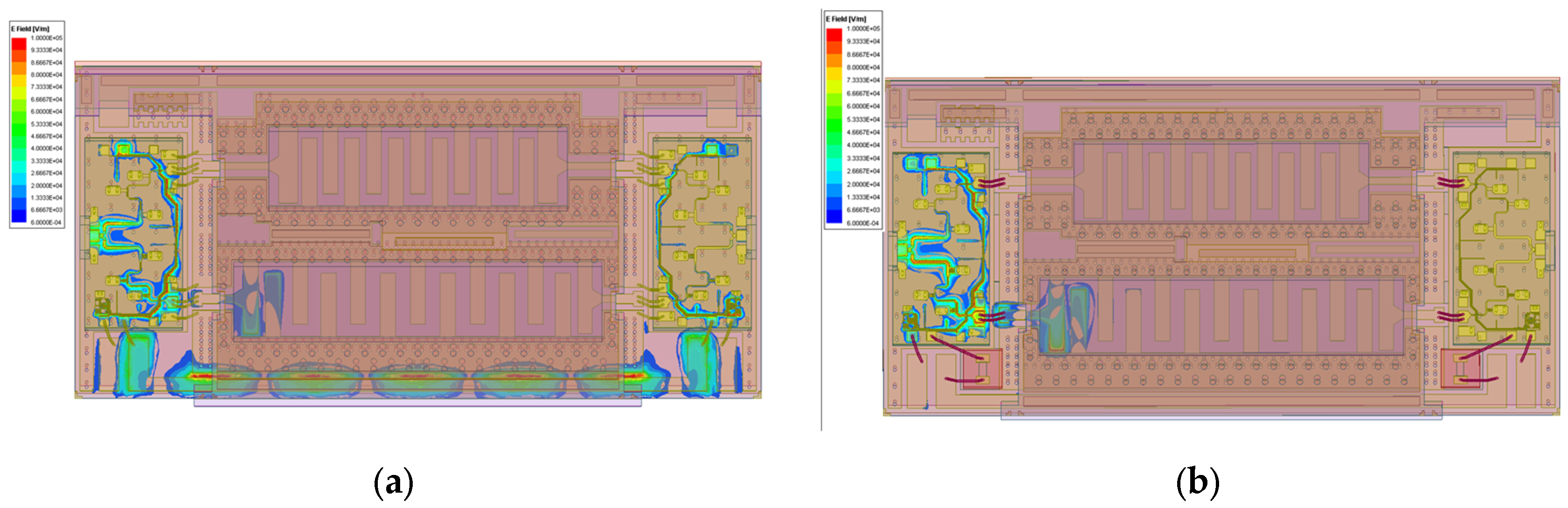

2.3. Codesign of Filter and Switch

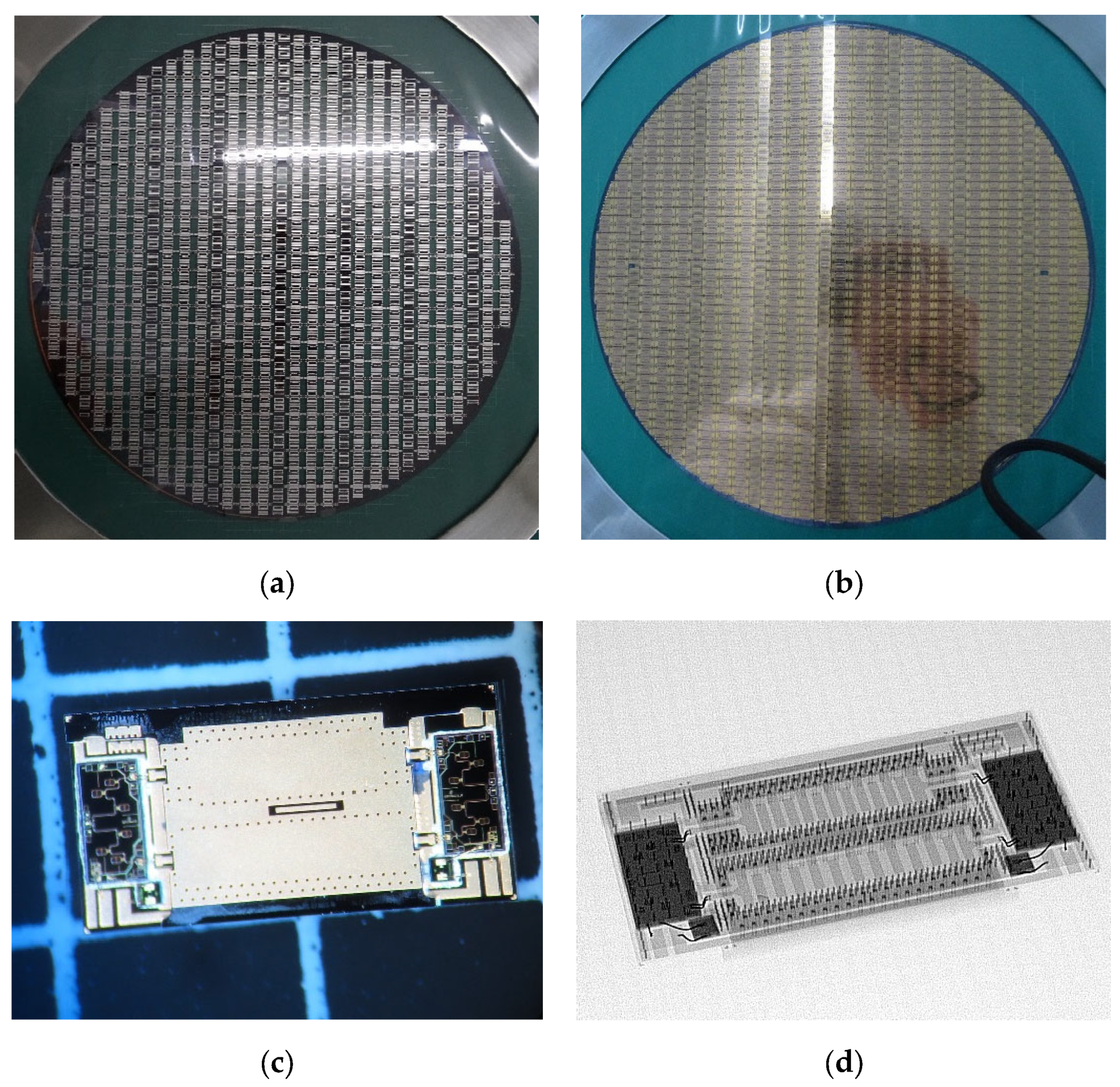

3. Fabrication Using Wafer-Level 3DHI

3.1. Cap Interposer Wafer

3.2. Bottom Interposer Wafer

3.3. Interposer Wafer Stacking

4. Measured Results and Discussion

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Chan, K.Y.; Ramer, R.; Mansour, R.R. A Switchable Iris Bandpass Filter Using RF MEMS Switchable Planar Resonators. IEEE Microw. Wirel. Compon. Lett. 2017, 27, 34–36. [Google Scholar] [CrossRef]

- Shojaei-Asanjan, D.; Mansour, R.R. The Sky’s the Limit: A Switchable RF-MEMS Filter Design for Wireless Avionics Intracommunication. IEEE Microw. Mag. 2017, 18, 100–106. [Google Scholar] [CrossRef]

- Ma, K.; Wang, Y.; Li, W.; Chen, Y. A Novel Compact Self-Packaged SPDT Switchable BPFs Based on SISL Platform. IEEE Trans. Ind. Electron. 2019, 66, 7239–7249. [Google Scholar] [CrossRef]

- Bohorquez, J.; Potelon, B.; Quendo, C.; Cariou, M.; Manchec, A.; Segalen, R.; Karpus, F.; Cadiou, S. Design of a Compact, Highly-Integrated, Eight-Filter Module Using Multilayered-PCB. In Proceedings of the 2021 IEEE MTT-S International Microwave Filter Workshop (IMFW), Perugia, Italy, 17–19 November 2021; pp. 192–194. [Google Scholar]

- Ma, K.; Jayasuriya, R.M.; Lim Chin Siong, D.R. Fully Integrated High-Isolation Low-Loss Digitally Controlled MEMS Filters. IEEE Trans. Ind. Electron. 2011, 58, 2690–2696. [Google Scholar] [CrossRef]

- Yang, X.; Xing, M.; Wang, E.; Zhang, L.; Li, N.; Qian, Z. A Design of S-Band Monolithic Integrated Switched Filter Bank. In Proceedings of the 2017 18th International Conference on Electronic Packaging Technology (ICEPT), Harbin, China, 16–19 August 2017; pp. 177–181. [Google Scholar]

- Yu, H.; Wang, X.; Zhang, L.; Niu, X.; Yi, L.; Deng, L.; Jiang, C. A LTCC-Based Wideband TR Module with Sub-Band BPFs for Active Phased Array System. In Proceedings of the 2019 IEEE MTT-S International Wireless Symposium (IWS), Guangzhou, China, 19–22 May 2019; pp. 1–3. [Google Scholar]

- Hou, F.; Sun, C.; Luan, H.; Huang, M.; Zhu, J.; Hu, S. Heterogeneously Integrated Compact Switchable Filters in 3D-MEMS Silicon Process for Millimeter Wave Application. Res. Prog. SSE 2021, 41, 330–336. [Google Scholar]

- Hou, F.; Shen, Y.; Luan, H.; Sun, C.; Huang, M.; Zhu, J.; Hu, S. Micropackaged Compact Switchable Filters With High Isolation in 3-D TSV-MEMS Process. IEEE Trans. Compon. Packag. Manuf. Technol. 2021, 11, 647–654. [Google Scholar] [CrossRef]

- Huang, M.; Wang, T.; Hou, F.; Su, P.; Sun, C.; Luan, H. A 3D TSV-MEMS Based Heterogeneous Integration Technology for RF Application. In Proceedings of the 2021 22nd International Conference on Electronic Packaging Technology (ICEPT), Xiamen, China, 11–14 August 2021; pp. 1–4. [Google Scholar]

- Hou, F.; Li, L.; Shen, Y.; Sun, C.; Luan, H.; Hu, S. Wideband Switchable Sharp-Rejection Filter in Compact 3-D Heterogeneous Integration. IEEE Trans. Compon. Packag. Manuf. Technol. 2022, 12, 1583–1590. [Google Scholar] [CrossRef]

- Chan, K.Y.E.; Ramer, R.; Guo, Y.J. RF MEMS Millimeter-Wave Switchable Bandpass Filter. In Proceedings of the 2013 IEEE International Wireless Symposium (IWS), Beijing, China, 14–18 April 2013; pp. 1–4. [Google Scholar]

- Pachler, N.; del Portillo, I.; Crawley, E.F.; Cameron, B.G. An Updated Comparison of Four Low Earth Orbit Satellite Constellation Systems to Provide Global Broadband. In Proceedings of the 2021 IEEE international conference on communications workshops (ICC workshops), Montreal, QC, Canada, 14–23 June 2021; IEEE: Piscataway, NJ, USA, 2021; pp. 1–7. [Google Scholar]

- Li, F.; Yu, H.; Ding, R.; Wang, N.; Wang, Y.; Zhou, Z. Development Strategy of Space Internet Constellation System in China. Chin. J. Eng. Sci. 2021, 23, 137. [Google Scholar] [CrossRef]

- Zhu, Y.; Zheng, Y.; Fang, S.; Zou, Y.; Pearson, S. Analysis of the Brightness Temperature Features of the Lunar Surface Using 37 GHz Channel Data from the Chang’E-2 Microwave Radiometer. Adv. Space Res. 2019, 63, 750–765. [Google Scholar] [CrossRef]

- Görsdorf, U.; Lehmann, V.; Bauer-Pfundstein, M.; Peters, G.; Vavriv, D.; Vinogradov, V.; Volkov, V. A 35-GHz Polarimetric Doppler Radar for Long-Term Observations of Cloud Parameters—Description of System and Data Processing. J. Atmos. Ocean. Technol. 2015, 32, 675–690. [Google Scholar] [CrossRef]

- Ludwig, M.; Daganzo-Eusebio, E.; Davidson, M. Ka-Band Radar Missions for Earth Observation. In Proceedings of the 2013 IEEE International Geoscience and Remote Sensing Symposium—IGARSS, Melbourne, Australia, 21–26 July 2013; IEEE: Piscataway, NJ, USA, 2013; pp. 2289–2292. [Google Scholar]

- Swanson, D.G. Narrow-Band Microwave Filter Design. IEEE Microw. Mag. 2007, 8, 105–114. [Google Scholar] [CrossRef]

- Hong, J.S.; Lancaster, M.J. Microstrip Filters for RF/Microwave Applications; Wiley: Hoboken, NJ, USA, 2004; pp. 178–189. [Google Scholar]

- Guo, X.; Zhu, L.; Wu, W. Design Method for Multiband Filters with Compact Configuration in Substrate Integrated Waveguide. IEEE Trans. Microw. Theory Tech. 2018, 66, 3011–3018. [Google Scholar] [CrossRef]

- Ranganathan, N.; Lee, D.Y.; Youhe, L.; Lo, G.-Q.; Prasad, K.; Pey, K.L. Influence of Bosch Etch Process on Electrical Isolation of TSV Structures. IEEE Trans. Compon. Packag. Manuf. Technol. 2011, 1, 1497–1507. [Google Scholar] [CrossRef]

- Yu, F.; Zhou, Q.; Wang, Z.; Mo, J.; Chen, H. Design and Implementation of RF Front-End Module Based on 3D Heterogenous-Integrated Wafer-Level Packaging. Electronics 2021, 10, 1893. [Google Scholar] [CrossRef]

| Ref. | Passband (GHz) | Insertion Loss (dB) | Return Loss (dB) | Isolation (dB) | Relative BW3dB | Shape Factor (BW30dB/BW3dB) | Process | Size |

|---|---|---|---|---|---|---|---|---|

| [8] | 18–20 | 9 | 10 | 40 | 13% | 1.6 | HR-Si based 3DHI | |

| 20–24 | 7 | 11 | 21% | 1.3 | ||||

| 24–28 | 7 | 11 | 18% | 1.3 | ||||

| 28–32 | 8 | 10 | 17% | 1.3 | ||||

| 32–36 | 9 | 11 | 13% | 1.3 | ||||

| 36–40 | 9 | 10 | 12% | 1.3 | ||||

| [10] | 6–8 | 6 | 12 | 40 | 31% | 1.3 | HR-Si based 3DHI | |

| 8–10 | 6 | 13 | 29% | 1.3 | ||||

| 10–12 | 6 | 15 | 25% | 1.3 | ||||

| 12–14 | 6 | 14 | 21% | 1.3 | ||||

| 14–16 | 7 | 10 | 17% | 1.4 | ||||

| 16–18 | 10 | 10 | 15% | 1.4 | ||||

| [12] | 57–66 | 9 | 12 | / | 16% | / | Quartz with gold layer | / |

| 71–86 | 5 | 8 | 14% | |||||

| [5] | 11–13.5 | 4.3 | 13 | / | 23% | 1.3 | PCBs with metal package | |

| 12.8–15.7 | 4.4 | 10 | 22% | 1.4 | ||||

| 14.5–17.5 | 4.6 | 12 | 21% | 1.5 | ||||

| 16.3–20 | 4.7 | 11 | 23% | 1.5 | ||||

| This work | 26–40 | 6.9 | 10 | 50 | 45% | 1.3 | HR-Si based 3DHI | |

| 32.5–40 | 8.1 | 10 | 23% | 1.3 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, Z.; Shu, Y.; Ma, S.; Guo, X.; Yang, W.; Ding, X.; Lyu, X.; Yu, F. 3D Heterogenous Integrated Wideband Switchable Bandpass Filter Bank for Millimeter Wave Applications. Electronics 2023, 12, 194. https://doi.org/10.3390/electronics12010194

Wang Z, Shu Y, Ma S, Guo X, Yang W, Ding X, Lyu X, Yu F. 3D Heterogenous Integrated Wideband Switchable Bandpass Filter Bank for Millimeter Wave Applications. Electronics. 2023; 12(1):194. https://doi.org/10.3390/electronics12010194

Chicago/Turabian StyleWang, Zhiyu, Yujian Shu, Siyuan Ma, Xi Guo, Wei Yang, Xu Ding, Xiaofeng Lyu, and Faxin Yu. 2023. "3D Heterogenous Integrated Wideband Switchable Bandpass Filter Bank for Millimeter Wave Applications" Electronics 12, no. 1: 194. https://doi.org/10.3390/electronics12010194

APA StyleWang, Z., Shu, Y., Ma, S., Guo, X., Yang, W., Ding, X., Lyu, X., & Yu, F. (2023). 3D Heterogenous Integrated Wideband Switchable Bandpass Filter Bank for Millimeter Wave Applications. Electronics, 12(1), 194. https://doi.org/10.3390/electronics12010194