A CMOS Double-Demodulation Lock-In Amplifier for Stimulated Raman Scattering Signal Detection

Abstract

:1. Introduction

2. Method of SRS Signal Detections with an In-Pixel Double Demodulation Lock-In Amplifier

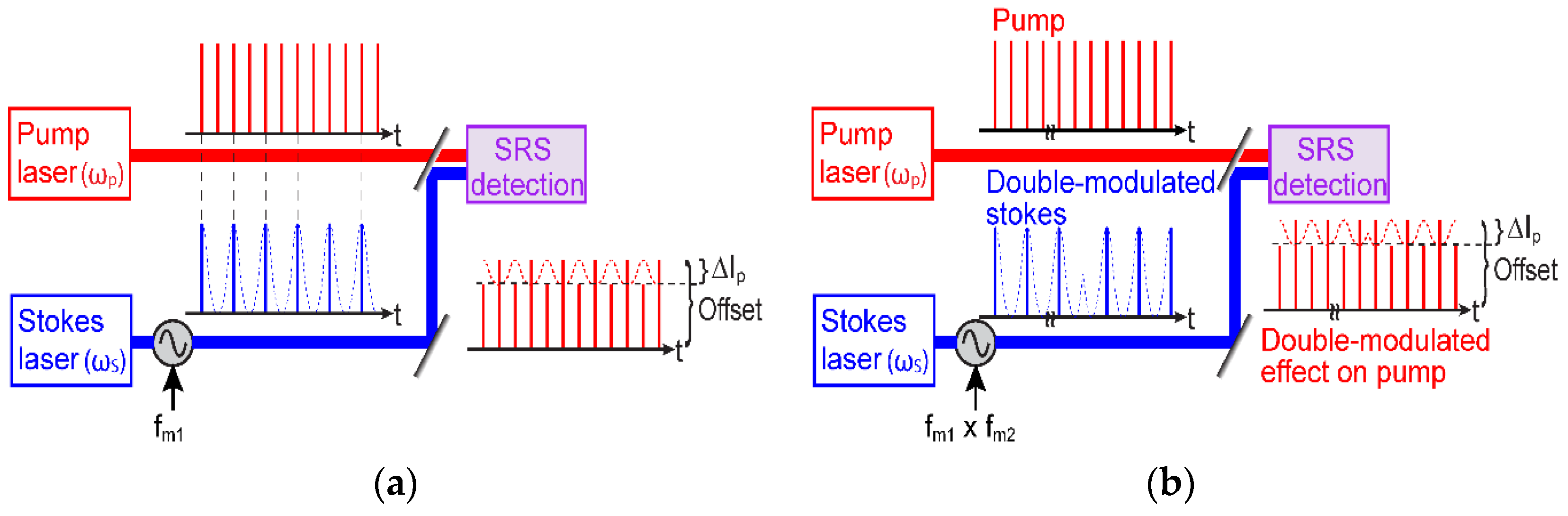

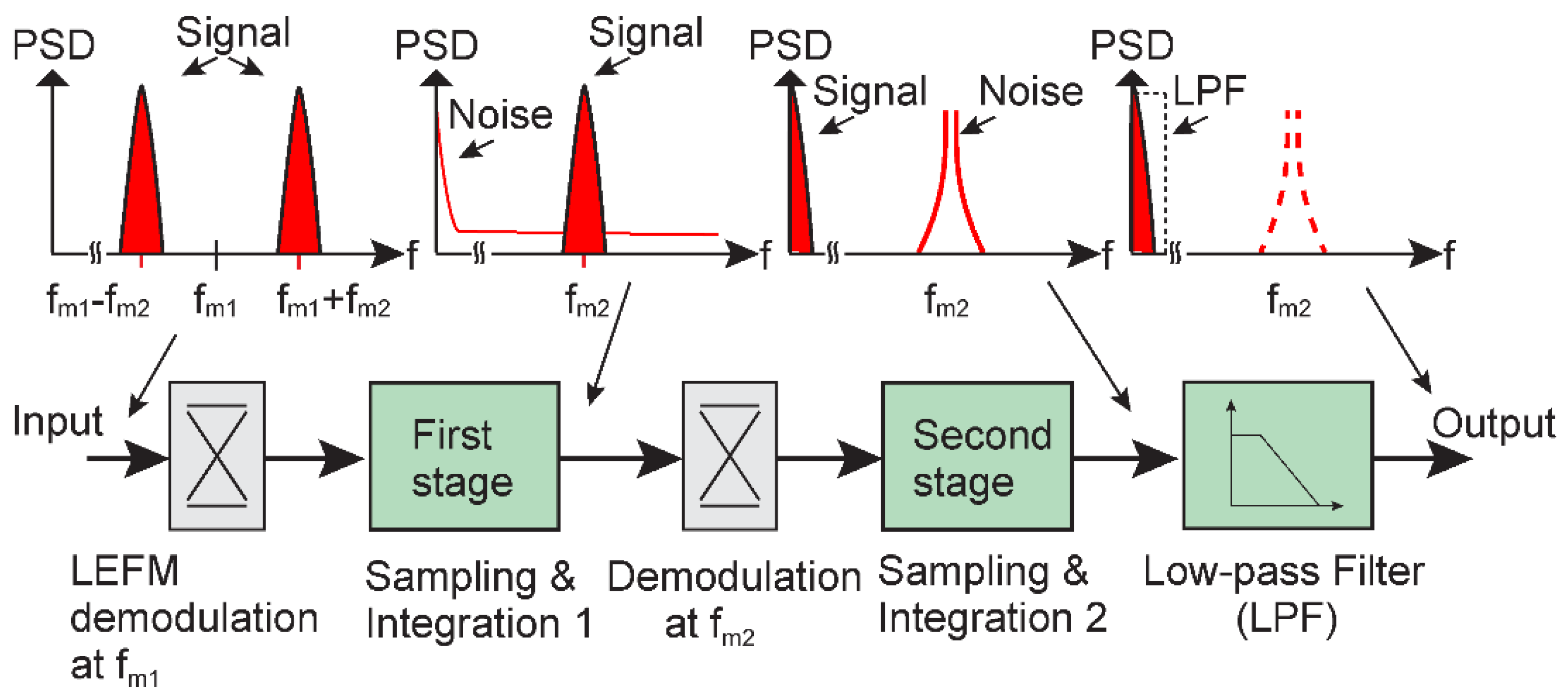

2.1. SRS Principle and the Noise Reduction Mechanism with the In-Pixel Double-Demodulation

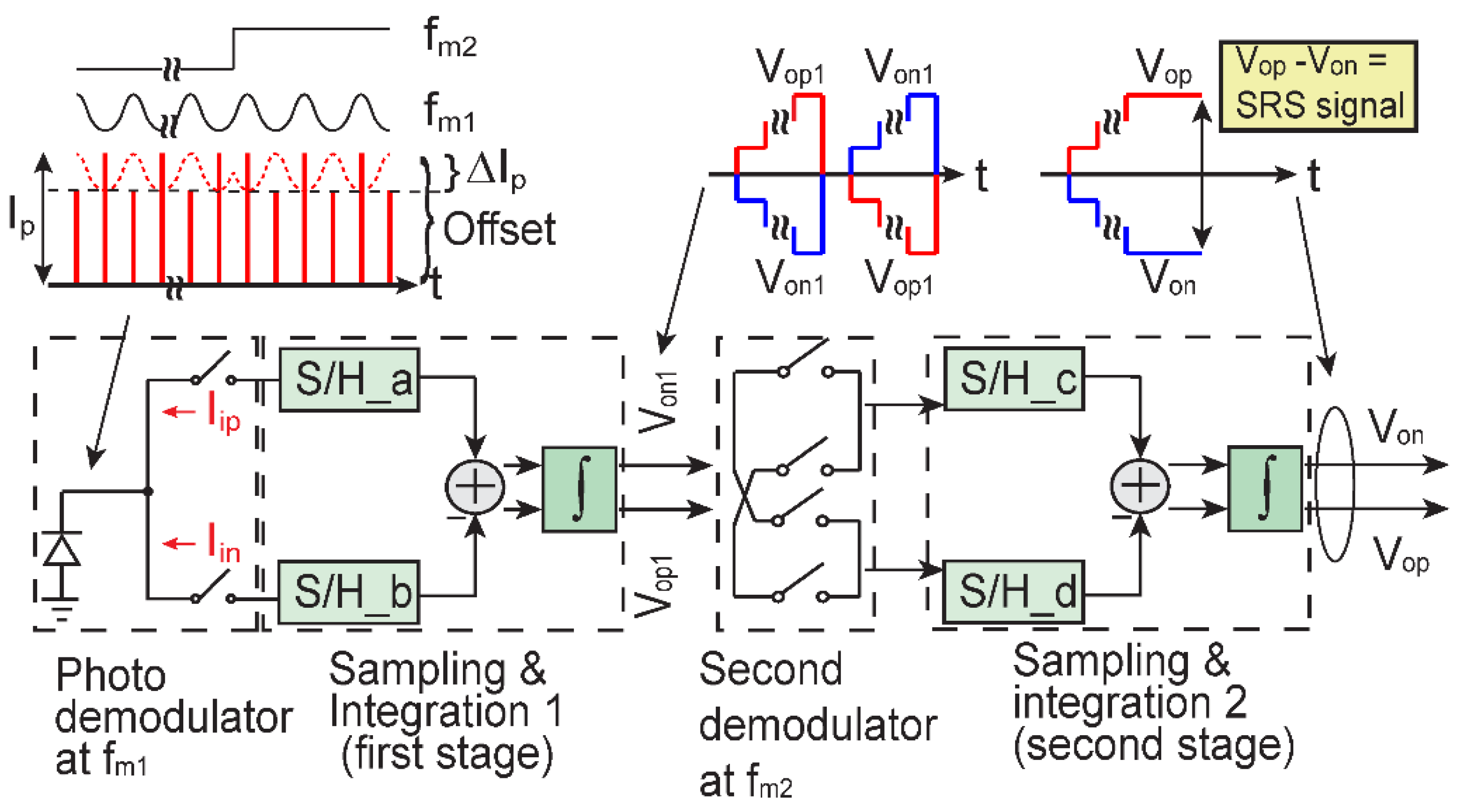

2.2. Operation of LEFM Photo-Demodulator to Extract the SRS Signal

3. Design of Double-Demodulation Lock-In Amplifier

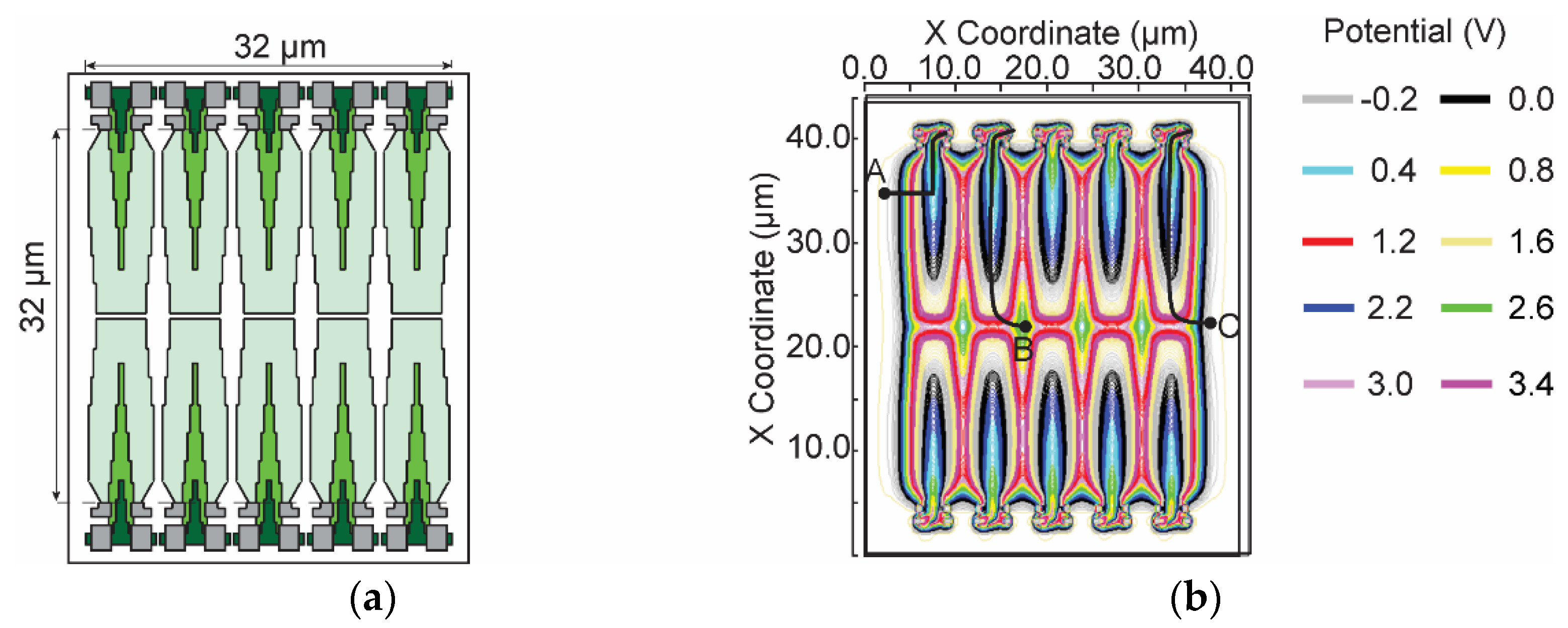

3.1. Large Area Photo-Detector and LEFM Photo-Demodulator Design

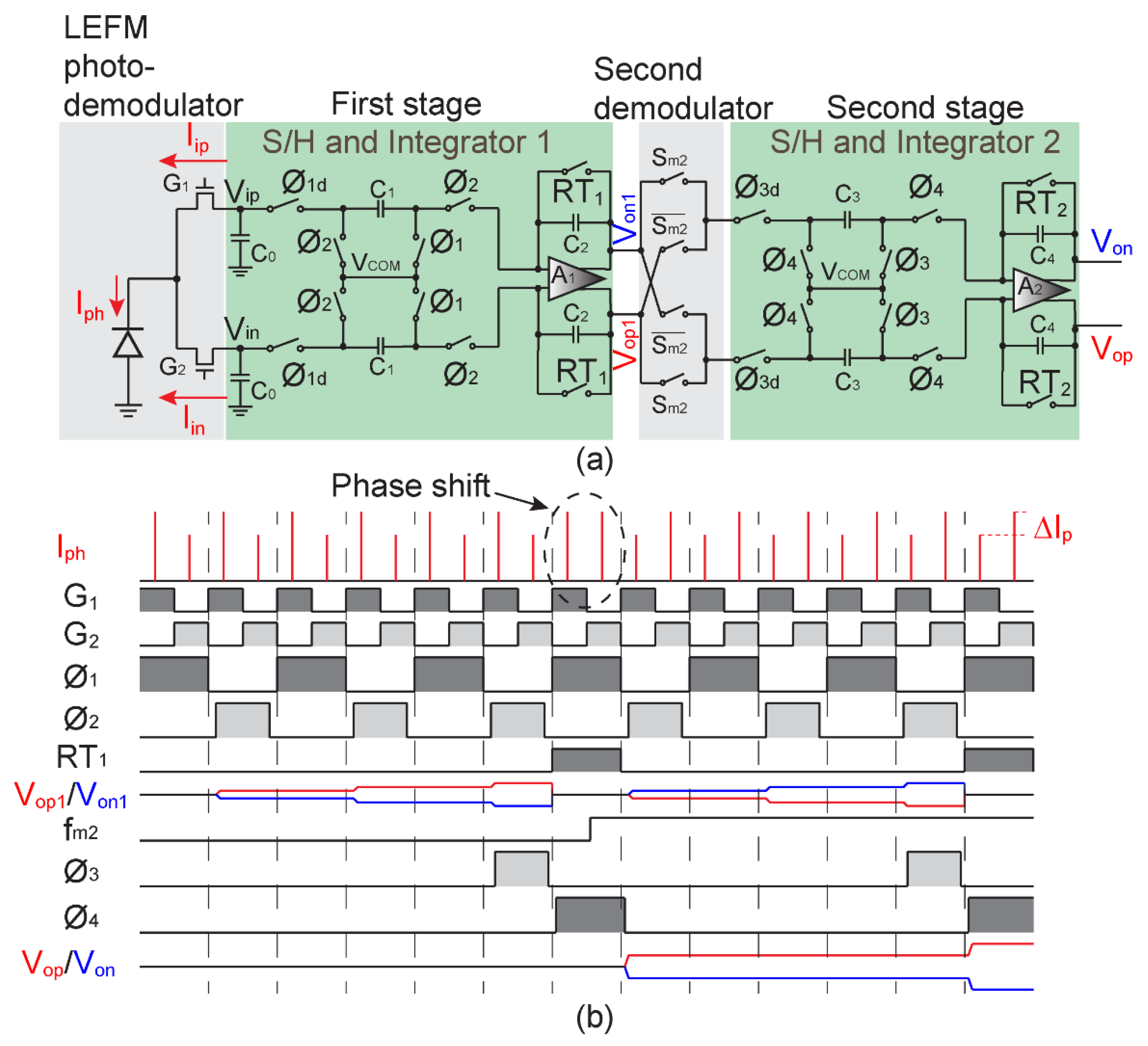

3.2. Circuit Implementation of the SRS Signal Lock-In Amplifier

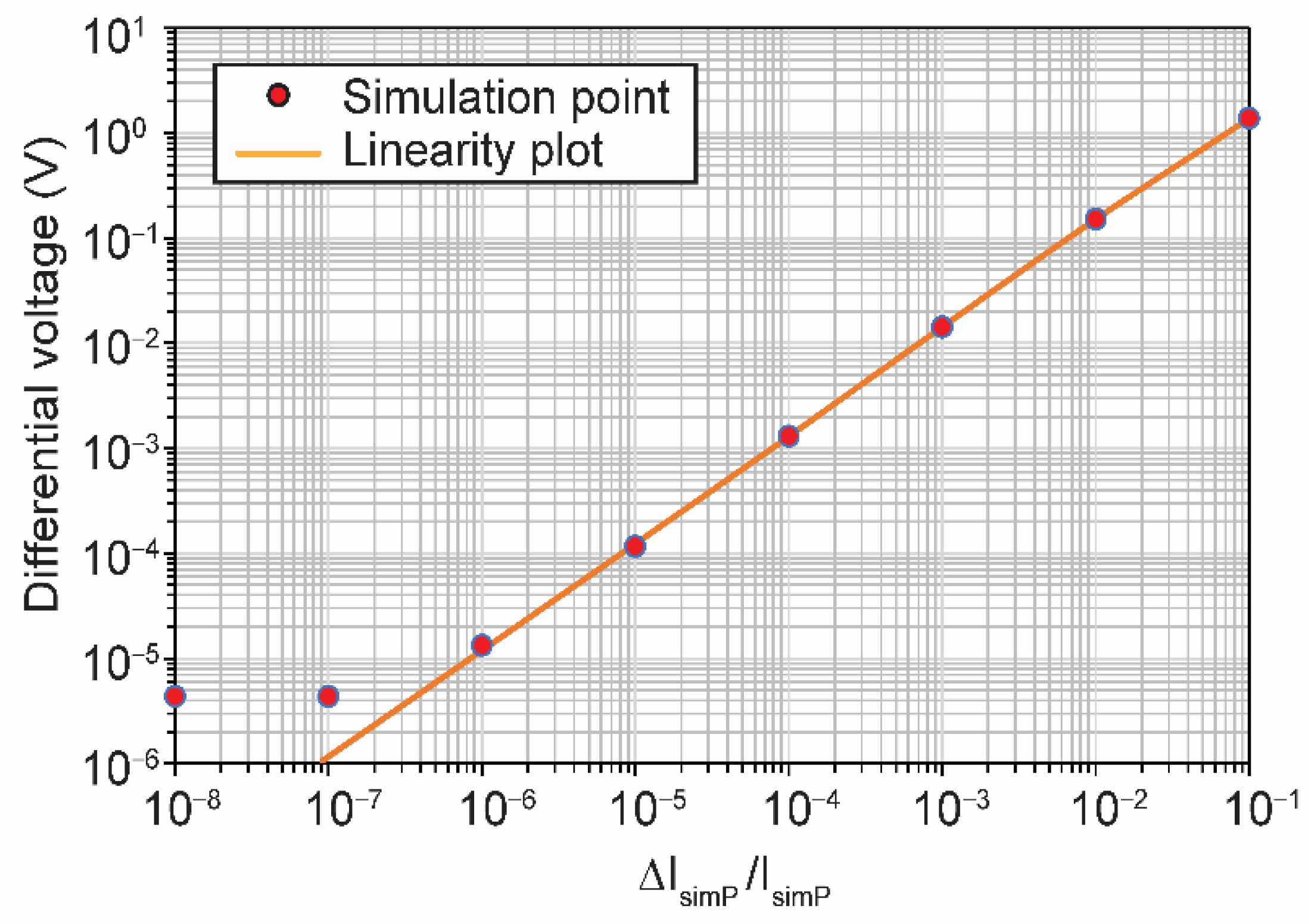

3.3. Circuit Simulation Results

4. Measurement Results and Discussion

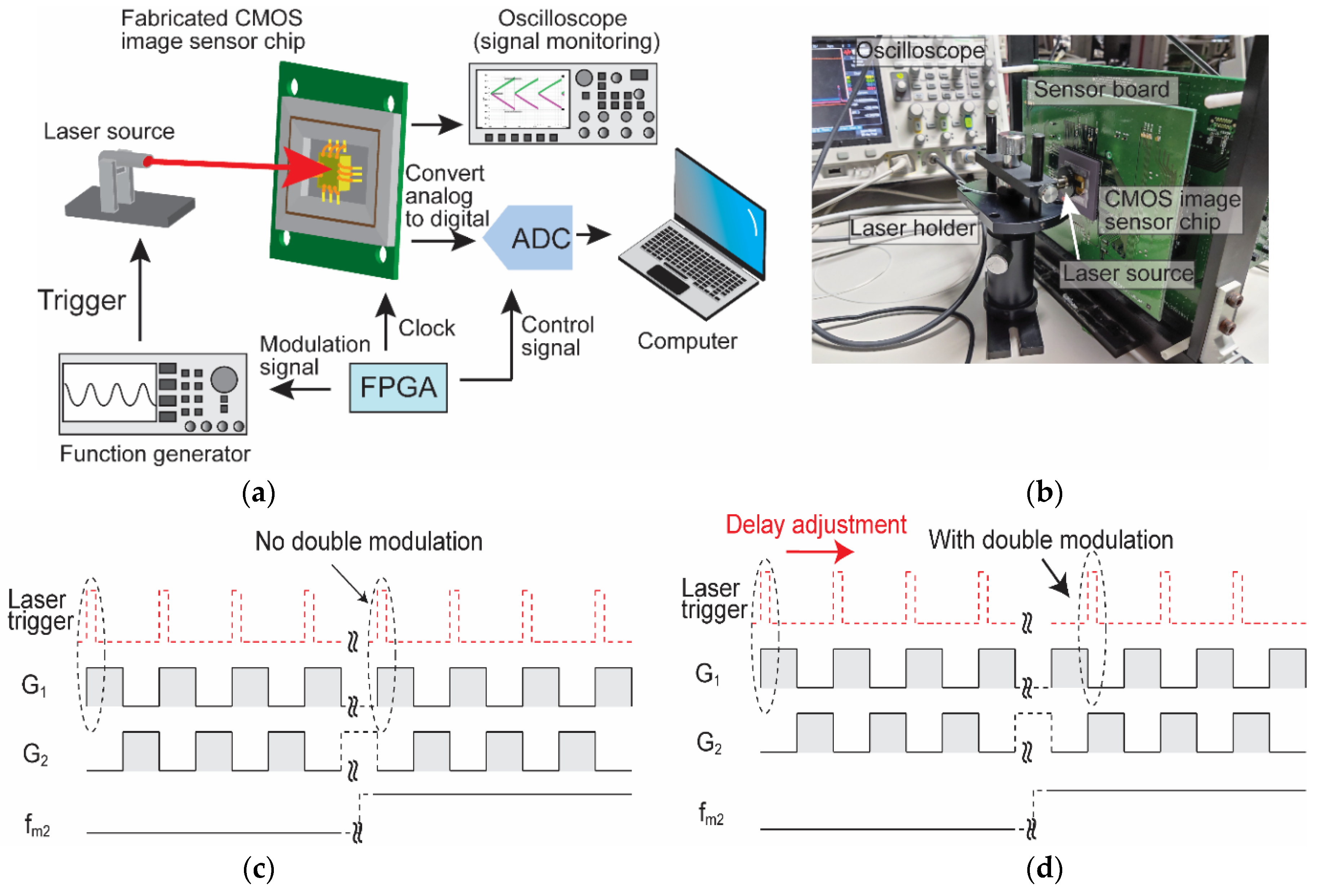

4.1. Implemented Lock-In Amplifier Chip and Measurement Setup

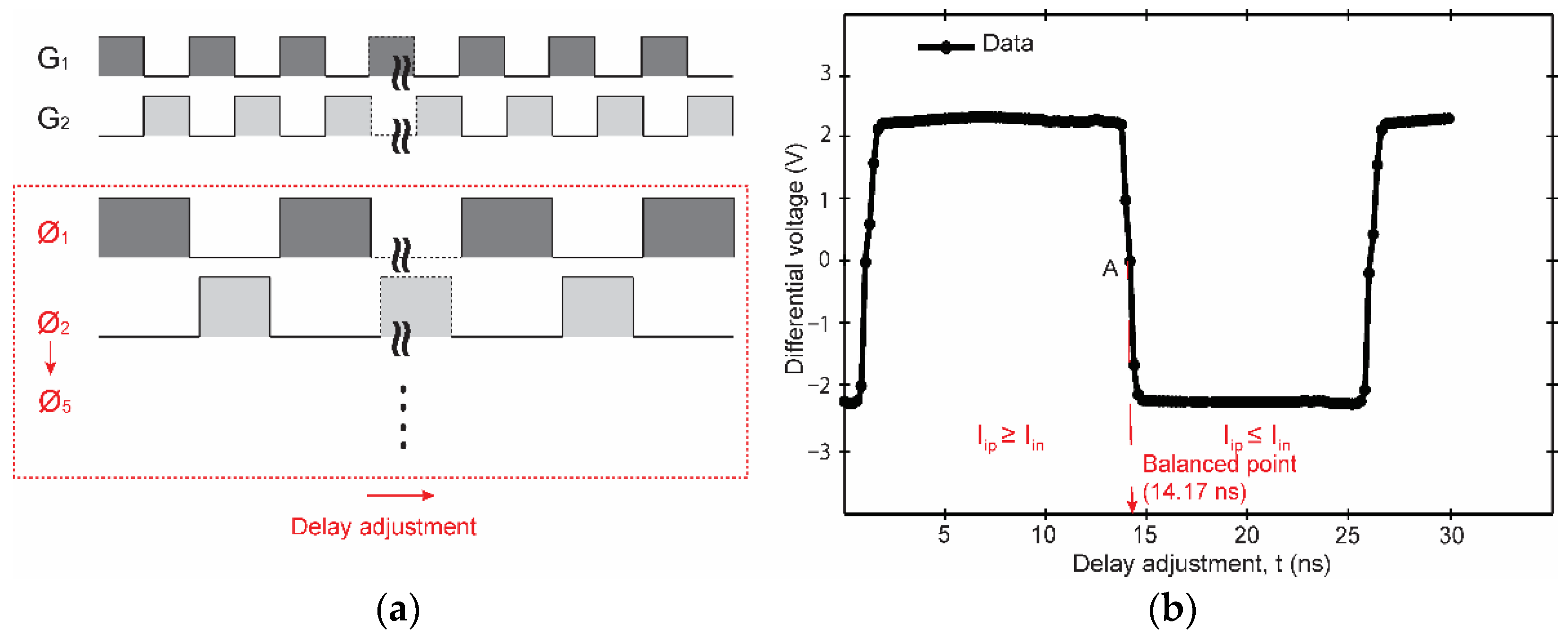

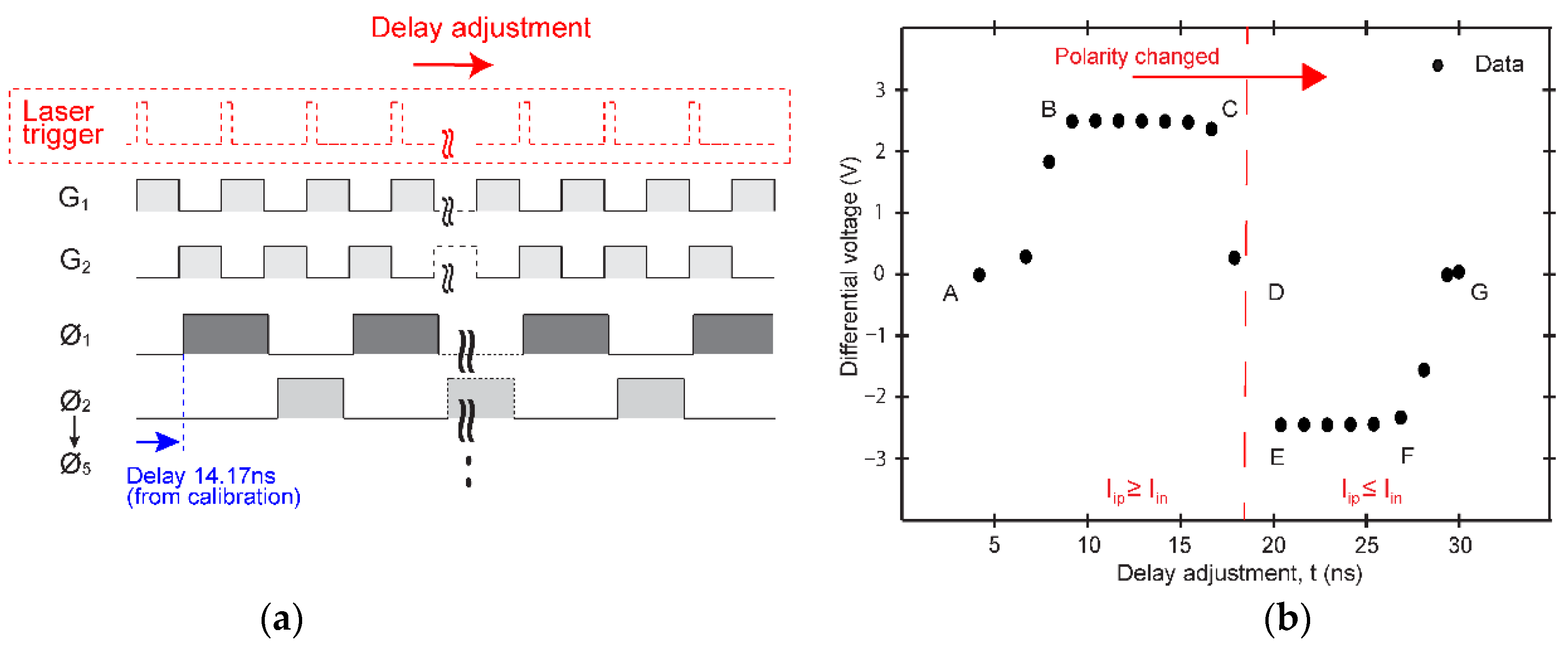

4.2. Characterization

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Riek, C.; Kocher, C.; Zirak, P.; Kölbl, C.; Fimpel, P.; Leitenstorfer, A.; Zumbusch, A.; Brida, D. Stimulated Raman Scattering Microscopy by Nyquist Modulation of a Two-Branch Ultrafast Fiber Source. Opt. Lett. 2016, 41, 3731. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Yamato, N.; Niioka, H.; Miyake, J.; Hashimoto, M. Improvement of Nerve Imaging Speed with Coherent Anti-Stokes Raman Scattering Rigid Endoscope Using Deep-Learning Noise Reduction. Sci. Rep. 2020, 10, 15212. [Google Scholar] [CrossRef] [PubMed]

- Zada, L.; Fokker, B.; Leslie, H.A.; Vethaak, A.D.; de Boer, J.F.; Ariese, F. Stimulated Raman Scattering Simulation for Imaging Optimization. J. Eur. Opt. Soc. Rapid Publ. 2021, 17, 10. [Google Scholar] [CrossRef]

- Ogawa, H.; Hashimoto, M. Avoidance of Four-Wave Mixing in Optical Fiber Bundle for Coherent Anti-Stokes Raman Scattering Endomicroscopy. Opt. Lett. 2021, 46, 3356. [Google Scholar] [CrossRef] [PubMed]

- Ozeki, Y.; Dake, F.; Kajiyama, S.; Fukui, K.; Itoh, K. Analysis and Experimental Assessment of the Sensitivity of Stimulated Raman Scattering Microscopy. Opt. Express 2009, 17, 3651. [Google Scholar] [CrossRef]

- Freudiger, C.W.; Min, W.; Saar, B.G.; Lu, S.; Holtom, G.R.; He, C.; Tsai, J.C.; Kang, J.X.; Xie, X.S. Label-Free Biomedical Imaging with High Sensitivity by Stimulated Raman Scattering Microscopy. Science 2008, 322, 1857–1861. [Google Scholar] [CrossRef] [Green Version]

- Nandakumar, P.; Kovalev, A.; Volkmer, A. Vibrational Imaging Based on Stimulated Raman Scattering Microscopy. New J. Phys. 2009, 11, 033026. [Google Scholar] [CrossRef]

- Valensise, C.M.; Giuseppi, A.; Vernuccio, F.; de La Cadena, A.; Cerullo, G.; Polli, D. Removing Non-Resonant Background from CARS Spectra via Deep Learning. APL Photonics 2020, 5, 061305. [Google Scholar] [CrossRef]

- Ozeki, Y.; Asai, T.; Shou, J.; Yoshimi, H. Multicolor Stimulated Raman Scattering Microscopy with Fast Wavelength-Tunable Yb Fiber Laser. IEEE J. Sel. Top. Quantum Electron. 2019, 25, 7100211. [Google Scholar] [CrossRef]

- Réhault, J.; Crisafi, F.; Kumar, V.; Ciardi, G.; Marangoni, M.; Cerullo, G.; Polli, D. Broadband Stimulated Raman Scattering with Fourier-Transform Detection. Opt. Express 2015, 23, 25235. [Google Scholar] [CrossRef]

- Ragni, A.; Sciortino, G.; Sampietro, M.; Ferrari, G.; Polli, D. Multi-Channel Lock-in Based Differential Front-End for Broadband Raman Spectroscopy. Integration 2019, 67, 44–49. [Google Scholar] [CrossRef] [Green Version]

- Sciortino, G.; Ragni, A.; de La Cadena, A.; Sampietro, M.; Cerullo, G.; Polli, D.; Ferrari, G. Four-Channel Differential Lock-in Amplifiers with Autobalancing Network for Stimulated Raman Spectroscopy. IEEE J. Solid-State Circuits 2021, 56, 1859–1870. [Google Scholar] [CrossRef]

- Wang, Z.; Zheng, W.; Huang, Z. Lock-in-Detection-Free Line-Scan Stimulated Raman Scattering Microscopy for near Video-Rate Raman Imaging. Opt. Lett. 2016, 41, 3960. [Google Scholar] [CrossRef] [PubMed]

- Mars, K.; Lioe, D.X.; Kawahito, S.; Yasutomi, K.; Kagawa, K.; Yamada, T.; Hashimoto, M. Label-Free Biomedical Imaging Using High-Speed Lock-in Pixel Sensor for Stimulated Raman Scattering. Sensors 2017, 17, 2581. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Gambetta, A.; Kumar, V.; Grancini, G.; Polli, D.; Ramponi, R.; Cerullo, G.; Marangoni, M. Fiber-Format Stimulated-Raman-Scattering Microscopy from a Single Laser Oscillator. Opt. Lett. 2010, 35, 226. [Google Scholar] [CrossRef]

- Lioe, D.X.; Mars, K.; Takasawa, T.; Yasutomi, K.; Kagawa, K.; Hashimoto, M.; Kawahito, S. A CMOS Image Sensor Using High-Speed Lock-in Pixels for Stimulated Raman Scattering. In Proceedings of the SPIE 9720, High-Speed Biomedical Imaging and Spectroscopy: Toward Big Data Instrumentation and Management, San Francisco, CA, USA, 7 March 2016; Tsia, K.K., Goda, K., Eds.; Volume 9720, p. 97200J. [Google Scholar]

- Lioe, D.X.; Mars, K.; Kawahito, S.; Yasutomi, K.; Kagawa, K.; Yamada, T.; Hashimoto, M. A Stimulated Raman Scattering CMOS Pixel Using a High-Speed Charge Modulator and Lock-in Amplifier. Sensors 2016, 16, 532. [Google Scholar] [CrossRef] [Green Version]

- Witte, J.F.; Makinwa, K.A.A.; Huijsing, J.H. A CMOS Chopper Offset-Stabilized Opamp. IEEE J. Solid-State Circuits 2007, 42, 1529–1535. [Google Scholar] [CrossRef]

- Seto, K.; Okuda, Y.; Tokunaga, E.; Kobayashi, T. Development of a Multiplex Stimulated Raman Microscope for Spectral Imaging through Multi-Channel Lock-in Detection. Rev. Sci. Instrum. 2013, 84, 083705. [Google Scholar] [CrossRef] [Green Version]

- Li, Y.; Shen, B.; Li, S.; Zhao, Y.; Qu, J.; Liu, L. Review of Stimulated Raman Scattering Microscopy Techniques and Applications in the Biosciences. Adv. Biol. 2021, 5, 2000184. [Google Scholar] [CrossRef]

- Bae, K.; Zheng, W.; Huang, Z. Spatial Light-Modulated Stimulated Raman Scattering (SLM-SRS) Microscopy for Rapid Multiplexed Vibrational Imaging. Theranostics 2020, 10, 312–322. [Google Scholar] [CrossRef]

- Jainwal, K.; Anand, C.; Sarkar, M. 1/f Noise Reduction Using In-Pixel Chopping in CMOS Image Sensors. IEEE Solid State Circuits Lett. 2018, 1, 146–149. [Google Scholar] [CrossRef]

- Pham, X.T.; Vu, T.K.; Nguyen, T.D.; Pham-Nguyen, L. A 1.2-ΜW 41-DB Ripple Attenuation Chopper Amplifier Using Auto-Zero Offset Cancelation Loop for Area-Efficient Biopotential Sensing. Electronics 2022, 11, 1149. [Google Scholar] [CrossRef]

- Kawahito, S.; Baek, G.; Li, Z.; Han, S.M.; Seo, M.W. CMOS Lock-in Pixel Image Sensors with Lateral Electric Field Control for Time-Resolved Imaging. Int. Image Sens. Workshop 2013, 2, 3–5. [Google Scholar]

- Ozeki, Y.; Kitagawa, Y.; Sumimura, K.; Nishizawa, N.; Umemura, W.; Kajiyama, S.; Fukui, K.; Itoh, K. Stimulated Raman Scattering Microscope with Shot Noise Limited Sensitivity Using Subharmonically Synchronized Laser Pulses. Opt. Express 2010, 18, 13708. [Google Scholar] [CrossRef] [PubMed]

- Hu, F.; Shi, L.; Min, W. Biological Imaging of Chemical Bonds by Stimulated Raman Scattering Microscopy. Nat. Methods 2019, 16, 830–842. [Google Scholar] [CrossRef] [PubMed]

- Razavi, B. Design of Analog CMOS Integrated Circuits, 1st ed.; McGraw-Hill, Inc.: New York, NY, USA, 2001; ISBN 0072380322. [Google Scholar]

- Quinn, P.J.; Van Roermund, A.H. Switched-Capacitor Techniques for High-Accuracy Filter and ADC Design; Springer: Dordrecht, The Netherlands, 2007; ISBN 978-1-4020-6257-5. [Google Scholar]

- Choksi, O.; Carley, L.R. Analysis of Switched-Capacitor Common-Mode Feedback Circuit. IEEE Trans. Circuits Syst. II Analog. Digit. Signal Process. 2003, 50, 906–917. [Google Scholar] [CrossRef]

| Initial Location | Transfer Time (ns) |

|---|---|

| A | 0.92 |

| B | 2.03 |

| C | 2.97 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Korakkottil Kunhi Mohd, S.B.; Lioe, D.X.; Yasutomi, K.; Kagawa, K.; Hashimoto, M.; Kawahito, S. A CMOS Double-Demodulation Lock-In Amplifier for Stimulated Raman Scattering Signal Detection. Electronics 2023, 12, 4. https://doi.org/10.3390/electronics12010004

Korakkottil Kunhi Mohd SB, Lioe DX, Yasutomi K, Kagawa K, Hashimoto M, Kawahito S. A CMOS Double-Demodulation Lock-In Amplifier for Stimulated Raman Scattering Signal Detection. Electronics. 2023; 12(1):4. https://doi.org/10.3390/electronics12010004

Chicago/Turabian StyleKorakkottil Kunhi Mohd, Shukri Bin, De Xing Lioe, Keita Yasutomi, Keiichiro Kagawa, Mamoru Hashimoto, and Shoji Kawahito. 2023. "A CMOS Double-Demodulation Lock-In Amplifier for Stimulated Raman Scattering Signal Detection" Electronics 12, no. 1: 4. https://doi.org/10.3390/electronics12010004

APA StyleKorakkottil Kunhi Mohd, S. B., Lioe, D. X., Yasutomi, K., Kagawa, K., Hashimoto, M., & Kawahito, S. (2023). A CMOS Double-Demodulation Lock-In Amplifier for Stimulated Raman Scattering Signal Detection. Electronics, 12(1), 4. https://doi.org/10.3390/electronics12010004