Recent Research for HZO-Based Ferroelectric Memory towards In-Memory Computing Applications

Abstract

:1. Introduction

2. Ferroelectric Memory Operation Category

2.1. Ferroelectric Tunneling Junction (FTJ)

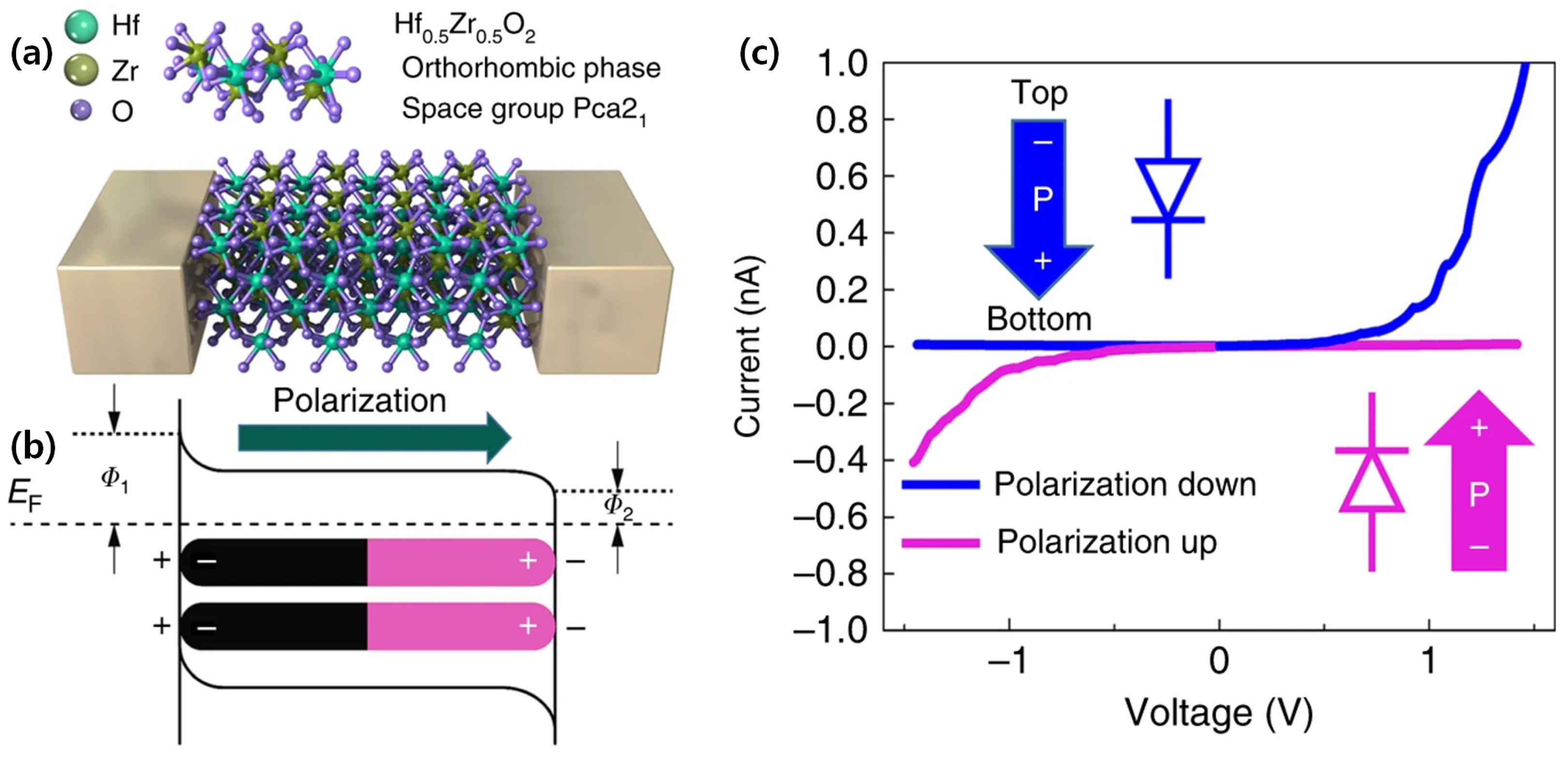

2.2. Ferroelectric Diode (Fe-Diode)

2.3. Ferroelectric Field Effect Transistor (FeFET)

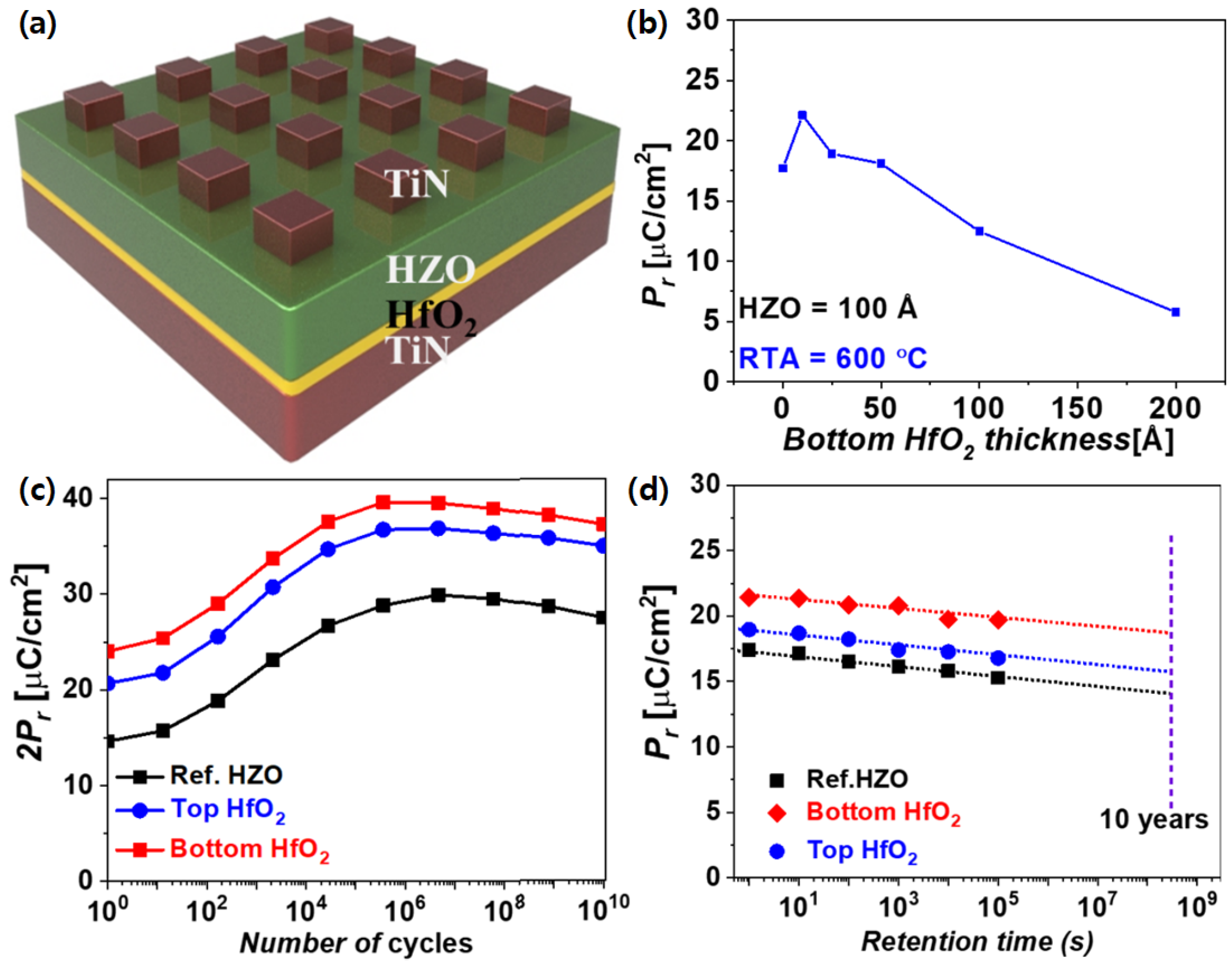

2.4. Ferroelectric RAM (FeRAM)

3. Ferroelectric Device Application

3.1. Two-Terminal Devices

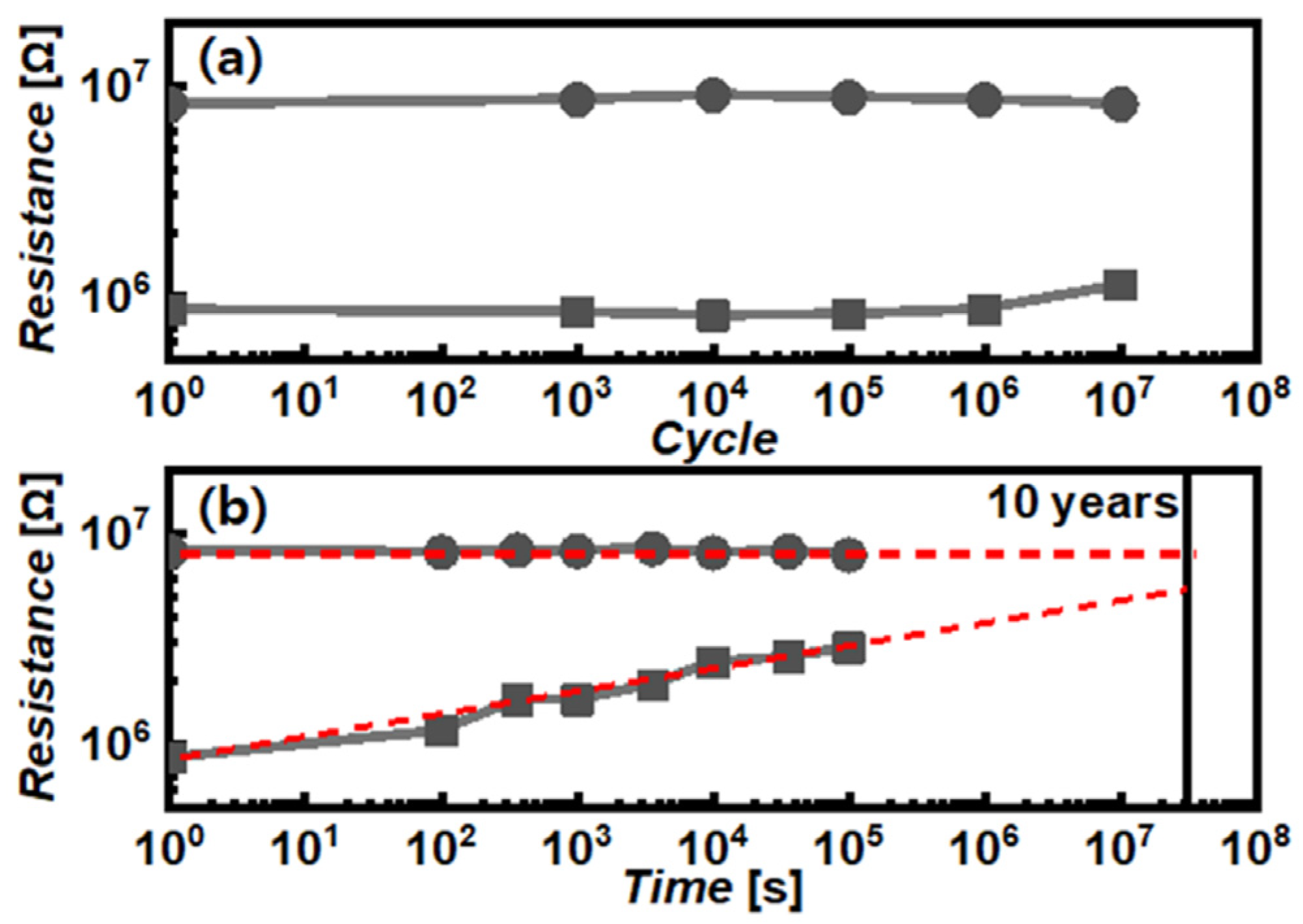

3.1.1. FTJ

3.1.2. Fe-Diode

3.2. Three-Terminal Devices

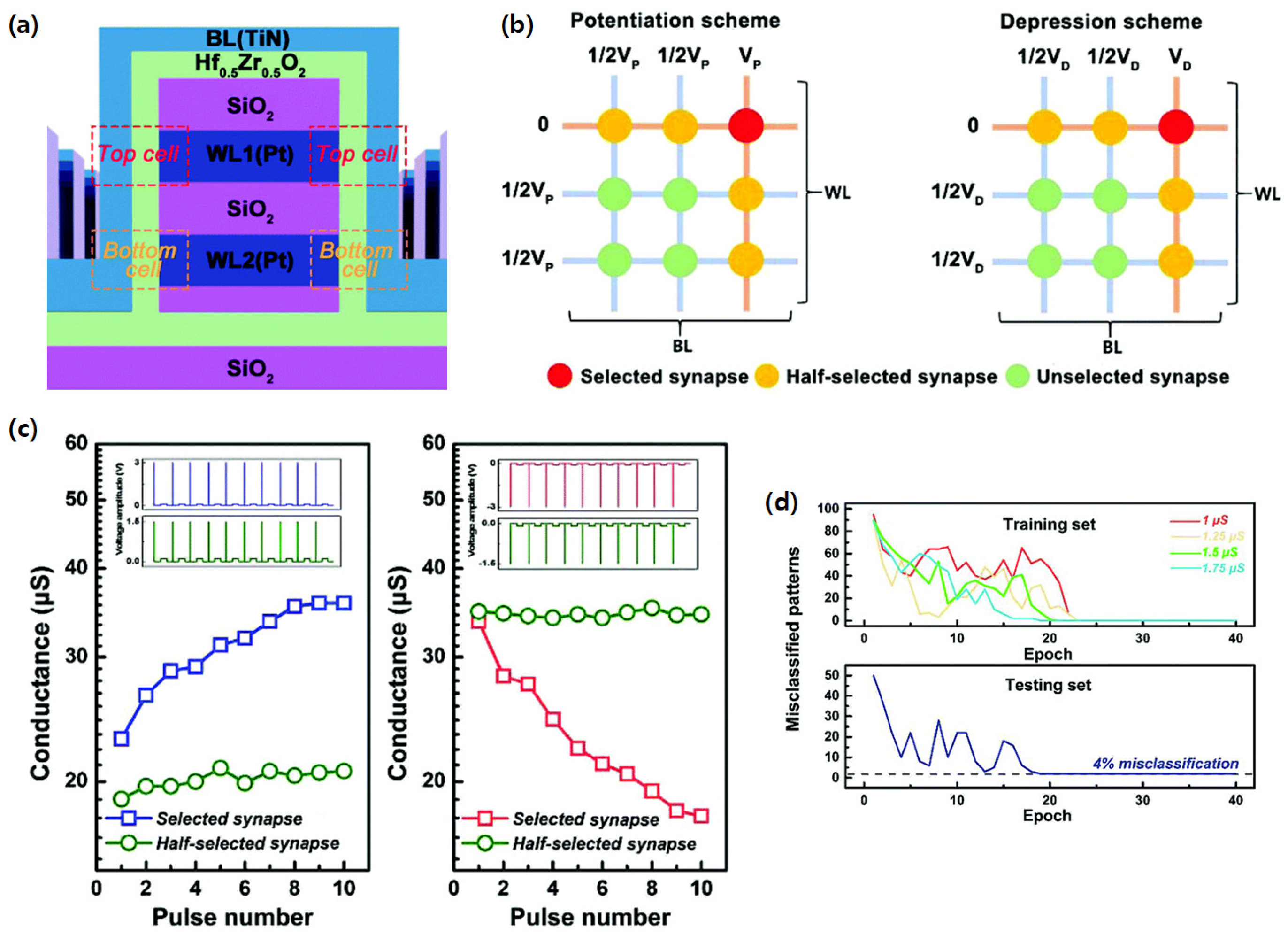

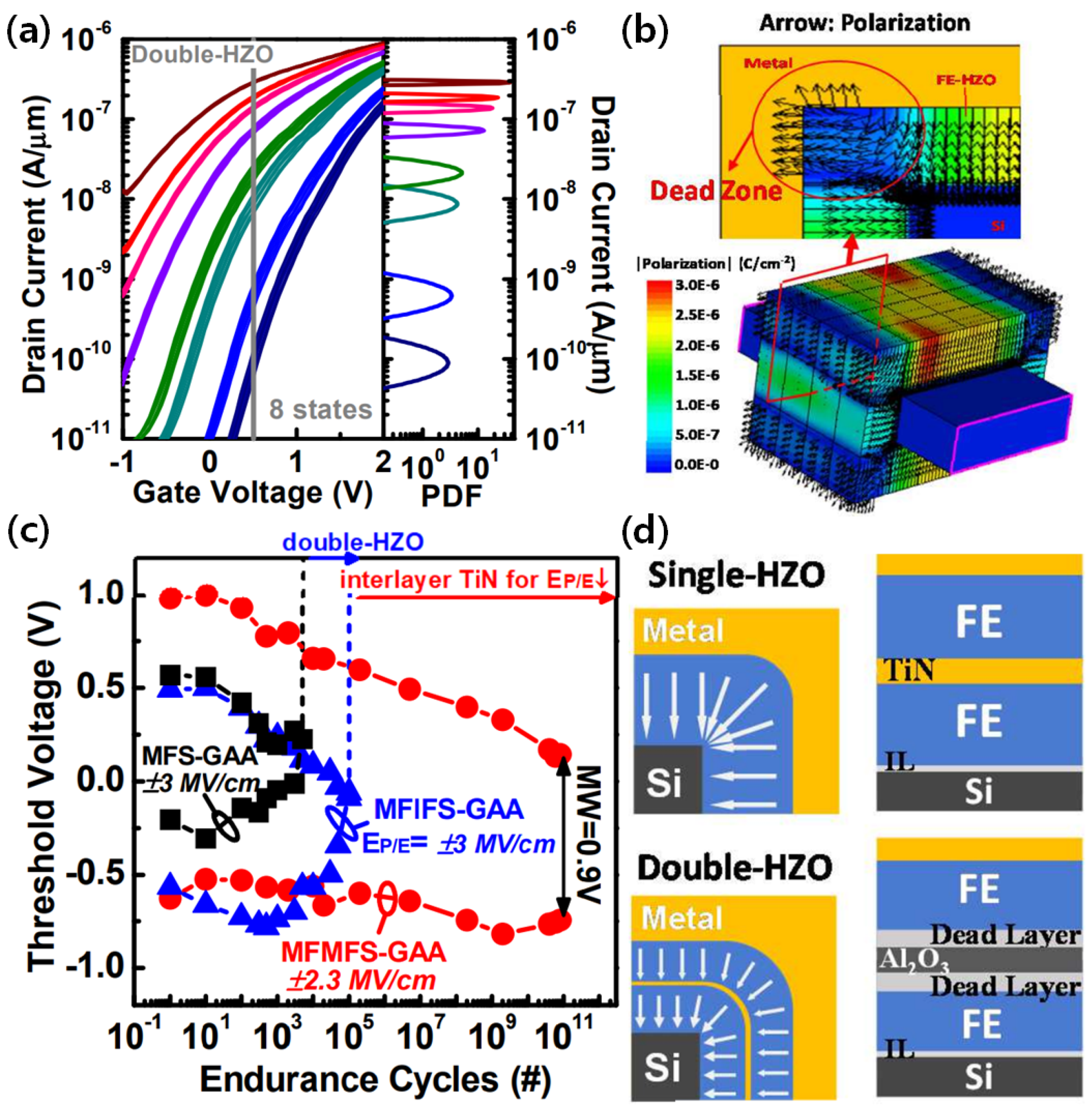

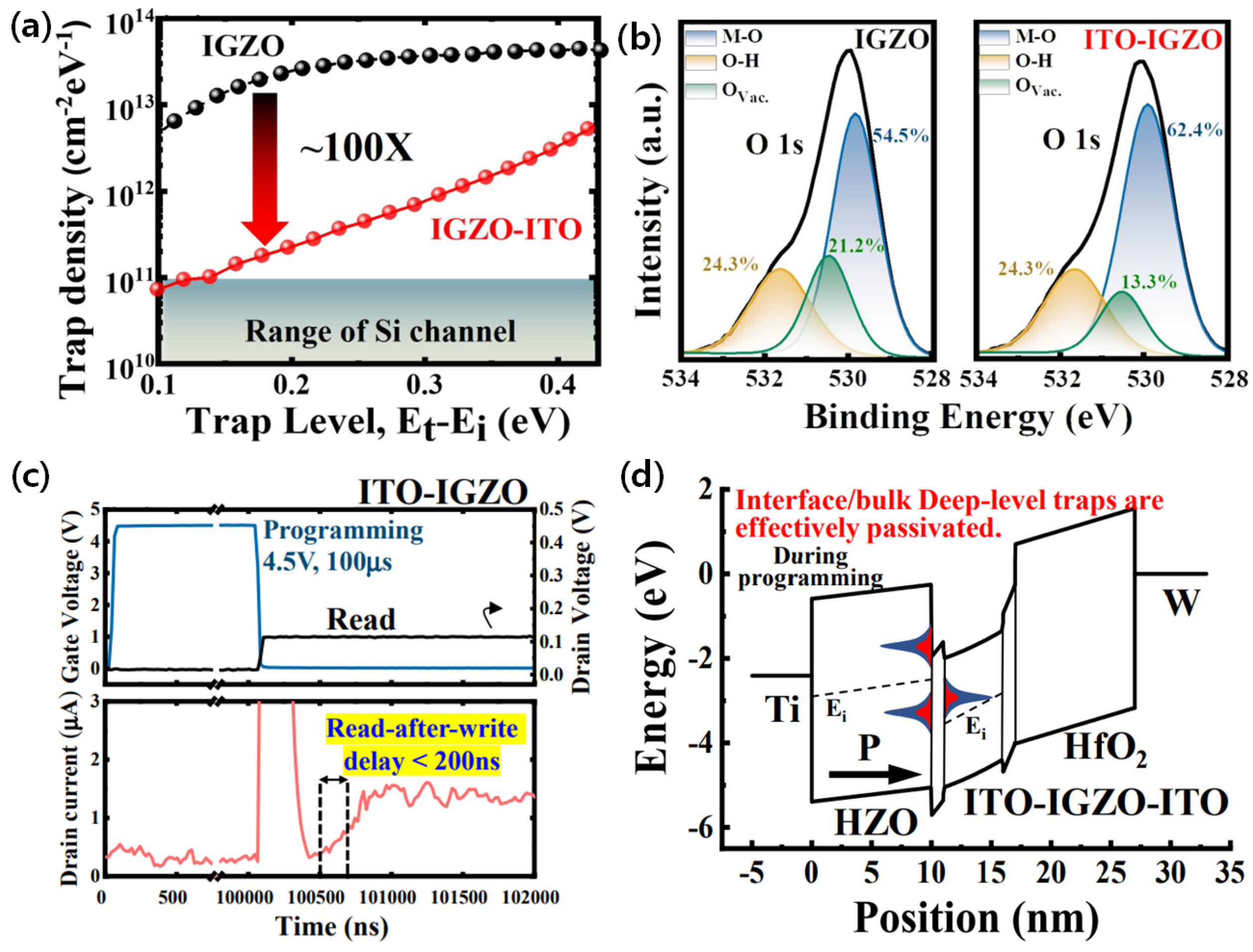

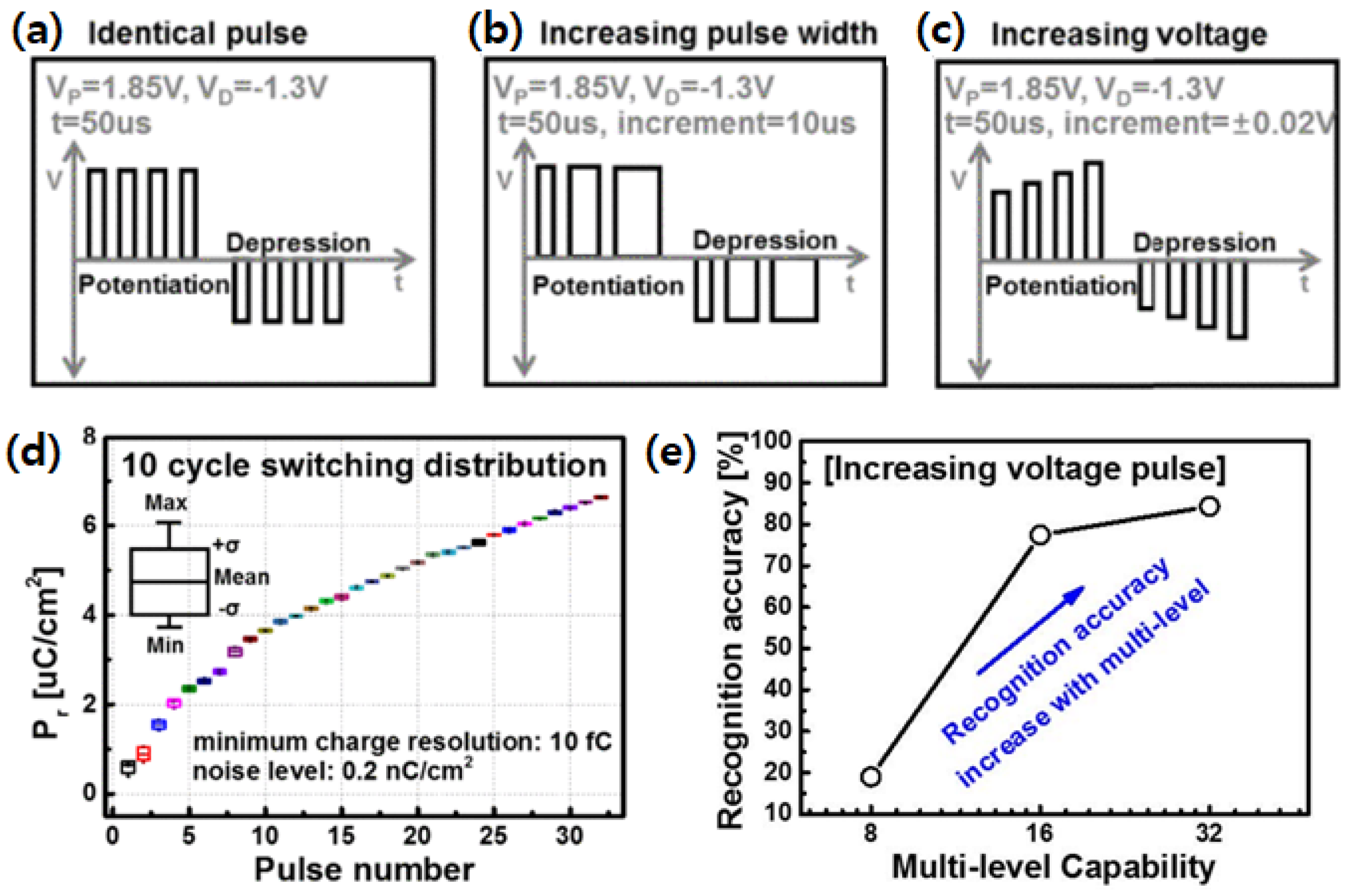

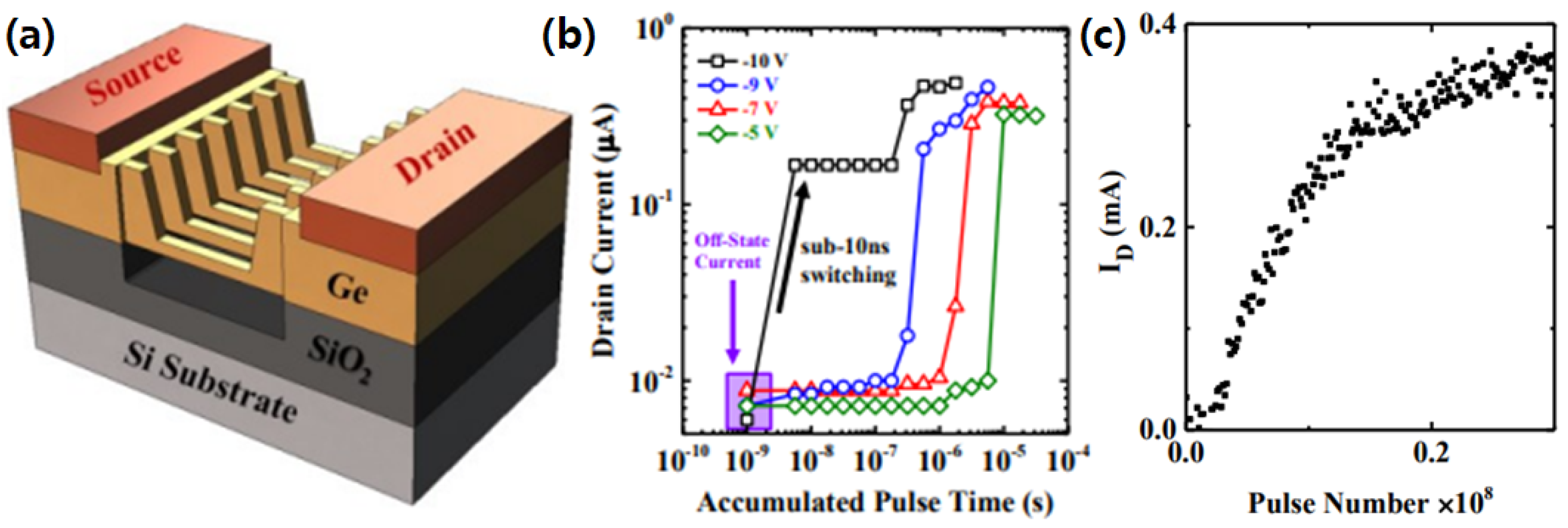

3.2.1. FeFET

3.2.2. FeRAM

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Song, C.-M.; Kwon, H.-J. Ferroelectrics Based on HfO2 Film. Electronics 2021, 10, 2759. [Google Scholar] [CrossRef]

- Cappy, A. Neuro-Inspired Information Processing; John Wiley & Sons: Hoboken, NJ, USA, 2020. [Google Scholar]

- Keshavarzi, A.; Ni, K.; Van Den Hoek, W.; Datta, S.; Raychowdhury, A. FerroElectronics for Edge Intelligence. IEEE Micro 2020, 40, 33–48. [Google Scholar] [CrossRef]

- Wang, Z.; Wu, H.; Burr, G.W.; Hwang, C.S.; Wang, K.L.; Xia, Q.; Yang, J.J. Resistive switching materials for information processing. Nat. Rev. Mater. 2020, 5, 173–195. [Google Scholar] [CrossRef]

- Dai, S.; Zhao, Y.; Wang, Y.; Zhang, J.; Fang, L.; Jin, S.; Shao, Y.; Huang, J. Recent Advances in Transistor-Based Artificial Synapses. Adv. Funct. Mater. 2019, 29, 1903700. [Google Scholar] [CrossRef]

- Sun, B.; Guo, T.; Zhou, G.; Ranjan, S.; Jiao, Y.; Wei, L.; Zhou, Y.N.; Wu, Y.A. Synaptic devices based neuromorphic computing applications in artificial intelligence. Mater. Today Phys. 2021, 18, 100393. [Google Scholar] [CrossRef]

- Han, J.-K.; Yun, S.-Y.; Lee, S.-W.; Yu, J.-M.; Choi, Y.-K. A Review of Artificial Spiking Neuron Devices for Neural Processing and Sensing. Adv. Funct. Mater. 2022, 32, 2204102. [Google Scholar] [CrossRef]

- Banerjee, W. Challenges and Applications of Emerging Nonvolatile Memory Devices. Electronics 2020, 9, 1029. [Google Scholar] [CrossRef]

- Sebastian, A.; Le Gallo, M.; Khaddam-Aljameh, R.; Eleftheriou, E. Memory devices and applications for in-memory computing. Nat. Nanotechnol. 2020, 15, 529–544. [Google Scholar] [CrossRef]

- Jouppi, N.P.; Young, C.; Patil, N.; Patterson, D.; Agrawal, G.; Bajwa, R.; Bates, S.; Bhatia, S.; Boden, N.; Borchers, A.; et al. In-Datacenter Performance Analysis of a Tensor Processing Unit. In Proceedings of the 44th Annual International Symposium on Computer Architecture, New York, NY, USA, 24–28 June 2017. [Google Scholar]

- Sze, V.; Chen, Y.-H.; Yang, T.-J.; Emer, J.S. Efficient Processing of Deep Neural Networks: A Tutorial and Survey. Proc. IEEE 2017, 105, 2295–2329. [Google Scholar] [CrossRef]

- Yu, J.-M.; Lee, C.; Kim, D.-J.; Park, H.; Han, J.-K.; Hur, J.; Kim, J.-K.; Kim, M.-S.; Seo, M.; Im, S.G.; et al. All-Solid-State Ion Synaptic Transistor for Wafer-Scale Integration with Electrolyte of a Nanoscale Thickness. Adv. Funct. Mater. 2021, 31, 2010971. [Google Scholar] [CrossRef]

- Wang, W.; Gao, S.; Li, Y.; Yue, W.; Kan, H.; Zhang, C.; Lou, Z.; Wang, L.; Shen, G. Artificial Optoelectronic Synapses Based on TiNxO2–x/MoS2 Heterojunction for Neuromorphic Computing and Visual System. Adv. Funct. Mater. 2021, 31, 2101201. [Google Scholar] [CrossRef]

- Ielmini, D.; Wong, H.-S.P. In-memory computing with resistive switching devices. Nat. Electron. 2018, 1, 333–343. [Google Scholar] [CrossRef]

- Raoux, S.; Wełnic, W.; Ielmini, D. Phase Change Materials and Their Application to Nonvolatile Memories. Chem. Rev. 2010, 110, 240–267. [Google Scholar] [CrossRef] [PubMed]

- Kent, A.D.; Worledge, D.C. A new spin on magnetic memories. Nat. Nanotechnol. 2015, 10, 187–191. [Google Scholar] [CrossRef] [PubMed]

- Jan, A.; Rembert, T.; Taper, S.; Symonowicz, J.; Strkalj, N.; Moon, T.; Lee, Y.S.; Bae, H.; Lee, H.J.; Choe, D.-H.; et al. In Operando Optical Tracking of Oxygen Vacancy Migration and Phase Change in few Nanometers Ferroelectric HZO Memories. Adv. Funct. Mater. 2023, 2214970. [Google Scholar] [CrossRef]

- Noh, J.; Bae, H.; Li, J.; Luo, Y.; Qu, Y.; Park, T.J.; Si, M.; Chen, X.; Charnas, A.R.; Chung, W.; et al. First Experimental Demonstration of Robust HZO/β-Ga2O3 Ferroelectric Field-Effect Transistors as Synaptic Devices for Artificial Intelligence Applications in a High-Temperature Environment. IEEE Trans. Electron Devices 2021, 68, 2515–2521. [Google Scholar] [CrossRef]

- Choe, D.-H.; Kim, S.; Moon, T.; Jo, S.; Bae, H.; Nam, S.-G.; Lee, Y.S.; Heo, J. Unexpectedly low barrier of ferroelectric switching in HfO2 via topological domain walls. Mater. Today 2021, 50, 8–15. [Google Scholar] [CrossRef]

- Si, M.; Luo, Y.; Chung, W.; Bae, H.; Zheng, D.; Li, J.; Qin, J.; Qiu, G.; Yu, S.; Ye, P. A novel scalable energy-efficient synaptic device: Crossbar ferroelectric semiconductor junction. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019. [Google Scholar]

- Kang, S.; Jang, W.-S.; Morozovska, A.N.; Kwon, O.; Jin, Y.; Kim, Y.-H.; Bae, H.; Wang, C.; Yang, S.-H.; Belianinov, A. Highly enhanced ferroelectricity in HfO2-based ferroelectric thin film by light ion bombardment. Science 2022, 376, 731–738. [Google Scholar] [CrossRef]

- Seo, M.; Kang, M.-H.; Jeon, S.-B.; Bae, H.; Hur, J.; Jang, B.C.; Yun, S.; Cho, S.; Kim, W.-K.; Kim, M.-S.; et al. First Demonstration of a Logic-Process Compatible Junctionless Ferroelectric FinFET Synapse for Neuromorphic Applications. IEEE Electron Device Lett. 2018, 39, 1445–1448. [Google Scholar] [CrossRef]

- Martin, L.W.; Rappe, A.M. Thin-film ferroelectric materials and their applications. Nat. Rev. Mater. 2016, 2, 16087. [Google Scholar] [CrossRef]

- Schroeder, U.; Park, M.H.; Mikolajick, T.; Hwang, C.S. The fundamentals and applications of ferroelectric HfO2. Nat. Rev. Mater. 2022, 7, 653–669. [Google Scholar] [CrossRef]

- Mulaosmanovic, H.; Breyer, E.T.; Dünkel, S.; Beyer, S.; Mikolajick, T.; Slesazeck, S. Ferroelectric field-effect transistors based on HfO2: A review. Nanotechnology 2021, 32, 502002. [Google Scholar] [CrossRef]

- Qi, L.; Ruan, S.; Zeng, Y.-J. Review on Recent Developments in 2D Ferroelectrics: Theories and Applications. Adv. Mater. 2021, 33, e2005098. [Google Scholar] [CrossRef]

- Kim, S.J.; Mohan, J.; Summerfelt, S.R.; Kim, J. Ferroelectric Hf0.5Zr0.5O2 Thin Films: A Review of Recent Advances. JOM 2018, 71, 246–255. [Google Scholar] [CrossRef]

- Kim, J.Y.; Choi, M.-J.; Jang, H.W. Ferroelectric field effect transistors: Progress and perspective. APL Mater. 2021, 9, 021102. [Google Scholar] [CrossRef]

- Park, H.W.; Lee, J.-G.; Hwang, C.S. Review of ferroelectric field-effect transistors for three-dimensional storage applications. Nano Sel. 2021, 2, 1187–1207. [Google Scholar] [CrossRef]

- Park, M.H.; Lee, Y.H.; Mikolajick, T.; Schroeder, U.; Hwang, C.S. Review and perspective on ferroelectric HfO2-based thin films for memory applications. Mrs Commun. 2018, 8, 795–808. [Google Scholar] [CrossRef]

- Böscke, T.S.; Müller, J.; Bräuhaus, D.; Schröder, U.; Böttger, U. Ferroelectricity in hafnium oxide thin films. Appl. Phys. Lett. 2011, 99, 102903. [Google Scholar] [CrossRef]

- Park, M.H.; Lee, Y.H.; Kim, H.J.; Kim, Y.J.; Moon, T.; Kim, K.D.; Muller, J.; Kersch, A.; Schroeder, U.; Mikolajick, T.; et al. Ferroelectricity and Antiferroelectricity of Doped Thin HfO2-Based Films. Adv. Mater. 2015, 27, 1811–1831. [Google Scholar] [CrossRef]

- Schroeder, U.; Yurchuk, E.; Müller, J.; Martin, D.; Schenk, T.; Polakowski, P.; Adelmann, C.; Popovici, M.I.; Kalinin, S.V.; Mikolajick, T. Impact of different dopants on the switching properties of ferroelectric hafniumoxide. Jpn. J. Appl. Phys. 2014, 53, 08LE02. [Google Scholar] [CrossRef]

- Zhou, D.; Müller, J.; Xu, J.; Knebel, S.; Bräuhaus, D.; Schröder, U. Insights into electrical characteristics of silicon doped hafnium oxide ferroelectric thin films. Appl. Phys. Lett. 2012, 100, 082905. [Google Scholar] [CrossRef]

- Park, M.H.; Kim, H.J.; Kim, Y.J.; Lee, W.; Moon, T.; Kim, K.D.; Hwang, C.S. Study on the degradation mechanism of the ferroelectric properties of thin Hf0.5Zr0.5O2 films on TiN and Ir electrodes. Appl. Phys. Lett. 2014, 105, 072902. [Google Scholar] [CrossRef]

- Kim, H.J.; Park, M.H.; Kim, Y.J.; Lee, Y.H.; Jeon, W.; Gwon, T.; Moon, T.; Kim, K.D.; Hwang, C.S. Grain size engineering for ferroelectric Hf0.5Zr0.5O2 films by an insertion of Al2O3 interlayer. Appl. Phys. Lett. 2014, 105, 192903. [Google Scholar] [CrossRef]

- Müller, J.; Schröder, U.; Böscke, T.S.; Müller, I.; Böttger, U.; Wilde, L.; Sundqvist, J.; Lemberger, M.; Kücher, P.; Mikolajick, T.; et al. Ferroelectricity in yttrium-doped hafnium oxide. J. Appl. Phys. 2011, 110, 114113. [Google Scholar] [CrossRef]

- Polakowski, P.; Riedel, S.; Weinreich, W.; Rudolf, M.; Sundqvist, J.; Seidel, K.; Muller, J. Ferroelectric deep trench capacitors based on Al:HfO2 for 3D nonvolatile memory applications. In Proceedings of the 2014 IEEE 6th International Memory Workshop (IMW), Taipei, Taiwan, 18–21 May 2014. [Google Scholar]

- Mueller, S.; Adelmann, C.; Singh, A.; Van Elshocht, S.; Schroeder, U.; Mikolajick, T. Ferroelectricity in Gd-Doped HfO2 Thin Films. ECS J. Solid State Sci. Technol. 2012, 1, N123–N126. [Google Scholar] [CrossRef]

- Schenk, T.; Schroeder, U.; Pesic, M.; Popovici, M.; Pershin, Y.V.; Mikolajick, T. Electric Field Cycling Behavior of Ferroelectric Hafnium Oxide. ACS Appl. Mater. Interfaces 2014, 6, 19744–19751. [Google Scholar] [CrossRef]

- Müller, J.; Böscke, T.; Müller, S.; Yurchuk, E.; Polakowski, P.; Paul, J.; Martin, D.; Schenk, T.; Khullar, K.; Kersch, A.; et al. Ferroelectric Hafnium Oxide: A CMOS-compatible and highly scalable approach to future ferroelectric memories. In Proceedings of the 2013 IEEE International Electron Devices Meeting, Washington, DC, USA, 9–11 December 2013. [Google Scholar]

- Muller, J.; Boscke, T.S.; Schroder, U.; Mueller, S.; Brauhaus, D.; Bottger, U.; Frey, L.; Mikolajick, T. Ferroelectricity in Simple Binary ZrO2 and HfO2. Nano Lett. 2012, 12, 4318–4323. [Google Scholar] [CrossRef]

- Jo, S.; Lee, H.; Choe, D.-H.; Kim, J.-H.; Lee, Y.S.; Kwon, O.; Nam, S.; Park, Y.; Kim, K.; Chae, B.G.; et al. Negative differential capacitance in ultrathin ferroelectric hafnia. Nat. Electron. 2023. [Google Scholar] [CrossRef]

- Park, J.Y.; Choe, D.-H.; Lee, D.H.; Yu, G.T.; Yang, K.; Kim, S.H.; Park, G.H.; Nam, S.-G.; Lee, H.J.; Jo, S.; et al. Revival of Ferroelectric Memories Based on Emerging Fluorite-Structured Ferroelectrics. Adv. Mater. 2022, e2204904. [Google Scholar] [CrossRef]

- Mikolajick, T.; Slesazeck, S.; Mulaosmanovic, H.; Park, M.H.; Fichtner, S.; Lomenzo, P.D.; Hoffmann, M.; Schroeder, U. Next generation ferroelectric materials for semiconductor process integration and their applications. J. Appl. Phys. 2021, 129, 100901. [Google Scholar] [CrossRef]

- Max, B.; Hoffmann, M.; Slesazeck, S.; Mikolajick, T. Ferroelectric Tunnel Junctions based on Ferroelectric-Dielectric Hf0.5Zr0.5O2/A12O3 Capacitor Stacks. In Proceedings of the 2018 48th European Solid-State Device Research Conference (ESSDERC), Dresden, Germany, 3–6 September 2018. [Google Scholar]

- Mikolajick, T.; Schroeder, U.; Slesazeck, S. The Past, the Present, and the Future of Ferroelectric Memories. IEEE Trans. Electron Devices 2020, 67, 1434–1443. [Google Scholar] [CrossRef]

- Fujii, S.; Kamimuta, Y.; Ino, T.; Nakasaki, Y.; Takaishi, R.; Saitoh, M. First demonstration and performance improvement of ferroelectric HfO2-based resistive switch with low operation current and intrinsic diode property. In Proceedings of the 2016 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 14–16 June 2016. [Google Scholar]

- Hwang, J.; Goh, Y.; Jeon, S. Effect of Insertion of Dielectric Layer on the Performance of Hafnia Ferroelectric Devices. IEEE Trans. Electron Devices 2021, 68, 841–845. [Google Scholar] [CrossRef]

- Blom, P.W.M.; Wolf, R.M.; Cillessen, J.F.M.; Krijn, M.P.C.M. Ferroelectric Schottky Diode. Phys. Rev. Lett. 1994, 73, 2107–2110. [Google Scholar] [CrossRef]

- Hsiang, K.-Y.; Liao, C.-Y.; Wang, J.-F.; Lou, Z.-F.; Lin, C.-Y.; Chiang, S.-H.; Liu, C.-W.; Hou, T.-H.; Lee, M.-H. Unipolar Parity of Ferroelectric-Antiferroelectric Characterized by Junction Current in Crystalline Phase Hf1−xZrxO2 Diodes. Nanomaterials 2021, 11, 2685. [Google Scholar] [CrossRef]

- Luo, Q.; Cheng, Y.; Yang, J.; Cao, R.; Ma, H.; Yang, Y.; Huang, R.; Wei, W.; Zheng, Y.; Gong, T.; et al. A highly CMOS compatible hafnia-based ferroelectric diode. Nat. Commun. 2020, 11, 1391. [Google Scholar] [CrossRef]

- Chen, A. A review of emerging non-volatile memory (NVM) technologies and applications. Solid-State Electron. 2016, 125, 25–38. [Google Scholar] [CrossRef]

- Hoffman, J.; Pan, X.; Reiner, J.W.; Walker, F.J.; Han, J.P.; Ahn, C.H.; Ma, T.P. Ferroelectric Field Effect Transistors for Memory Applications. Adv. Mater. 2010, 22, 2957–2961. [Google Scholar] [CrossRef]

- Mo, F.; Tagawa, Y.; Jin, C.; Ahn, M.; Saraya, T.; Hiramoto, T.; Kobayashi, M. Experimental Demonstration of Ferroelectric HfO2 FET with Ultrathin-body IGZO for High-Density and Low-Power Memory Application. In Proceedings of the 2019 Symposium on VLSI Technology, Kyoto, Japan, 9–14 June 2019. [Google Scholar]

- Mo, F.; Tagawa, Y.; Jin, C.; Ahn, M.; Saraya, T.; Hiramoto, T.; Kobayashi, M. Low-Voltage Operating Ferroelectric FET with Ultrathin IGZO Channel for High-Density Memory Application. IEEE J. Electron Devices Soc. 2020, 8, 717–723. [Google Scholar] [CrossRef]

- Hoffmann, M.; Tan, A.J.; Shanker, N.; Liao, Y.-H.; Wang, L.-C.; Bae, J.-H.; Hu, C.; Salahuddin, S. Fast Read-After-Write and Depolarization Fields in High Endurance n-Type Ferroelectric FETs. IEEE Electron Device Lett. 2022, 43, 717–720. [Google Scholar] [CrossRef]

- Gaddam, V.; Das, D.; Jeon, S. Insertion of HfO2 Seed/Dielectric Layer to the Ferroelectric HZO Films for Heightened Remanent Polarization in MFM Capacitors. IEEE Trans. Electron Devices 2020, 67, 745–750. [Google Scholar] [CrossRef]

- Okuno, J.; Kunihiro, T.; Konishi, K.; Materano, M.; Ali, T.; Kuehnel, K.; Seidel, K.; Mikolajick, T.; Schroeder, U.; Tsukamoto, M.; et al. 1T1C FeRAM Memory Array Based on Ferroelectric HZO With Capacitor Under Bitline. IEEE J. Electron Devices Soc. 2022, 10, 29–34. [Google Scholar] [CrossRef]

- Breyer, E.T.; Mulaosmanovic, H.; Mikolajick, T.; Slesazeck, S. Reconfigurable NAND/NOR logic gates in 28 nm HKMG and 22 nm FD-SOI FeFET technology. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017. [Google Scholar]

- Breyer, E.T.; Mulaosmanovic, H.; Mikolajick, T.; Slesazeck, S. Perspective on ferroelectric, hafnium oxide based transistors for digital beyond von-Neumann computing. Appl. Phys. Lett. 2021, 118, 050501. [Google Scholar] [CrossRef]

- Berdan, R.; Marukame, T.; Ota, K.; Yamaguchi, M.; Saitoh, M.; Fujii, S.; Deguchi, J.; Nishi, Y. Low-power linear computation using nonlinear ferroelectric tunnel junction memristors. Nat. Electron. 2020, 3, 259–266. [Google Scholar] [CrossRef]

- Jerry, M.; Chen, P.-Y.; Zhang, J.; Sharma, P.; Ni, K.; Yu, S.; Datta, S. Ferroelectric FET Analog Synapse for Acceleration of Deep Neural Network Training. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017. [Google Scholar]

- Wang, P.; Yu, S. Ferroelectric devices and circuits for neuro-inspired computing. MRS Commun. 2020, 10, 538–548. [Google Scholar] [CrossRef]

- Mulaosmanovic, H.; Ocker, J.; Müller, S.; Noack, M.; Müller, J.; Polakowski, P.; Mikolajick, T.; Slesazeck, S. Novel ferroelectric FET based synapse for neuromorphic systems. In Proceedings of the 2017 Symposium on VLSI Technology, Kyoto, Japan, 5–8 June 2017. [Google Scholar]

- Han, J.-K.; Yun, S.-Y.; Yu, J.-M.; Jeon, S.-B.; Choi, Y.-K. Artificial Multisensory Neuron with a Single Transistor for Multimodal Perception through Hybrid Visual and Thermal Sensing. ACS Appl. Mater. Interfaces 2023, 15, 5449–5455. [Google Scholar] [CrossRef]

- Lee, D.H.; Park, G.H.; Kim, S.H.; Park, J.Y.; Yang, K.; Slesazeck, S.; Mikolajick, T.; Park, M.H. Neuromorphic devices based on fluorite-structured ferroelectrics. InfoMat 2022, 4, e12380. [Google Scholar] [CrossRef]

- Fan, Z.; Chen, J.; Wang, J. Ferroelectric HfO2-based materials for next-generation ferroelectric memories. J. Adv. Dielectr. 2016, 6, 1630003. [Google Scholar] [CrossRef]

- Chung, W.; Si, M.; Ye, P.D. First Demonstration of Ge Ferroelectric Nanowire FET as Synaptic Device for Online Learning in Neural Network with High Number of Conductance State and Gmax/Gmin. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018. [Google Scholar]

- Si, M.; Ye, P.D. The Critical Role of Charge Balance on the Memory Characteristics of Ferroelectric Field-Effect Transistors. IEEE Trans. Electron Devices 2021, 68, 5108–5113. [Google Scholar] [CrossRef]

- Saha, A.K.; Si, M.; Ni, K.; Datta, S.; Ye, P.D.; Gupta, S. Ferroelectric Thickness Dependent Domain Interactions in FEFETs for Memory and Logic: A phase-Field Model based Analysis. In Proceedings of the 2020 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 12–18 December 2020. [Google Scholar]

- Lyu, X.; Si, M.; Sun, X.; Capano, M.A.; Wang, H.; Ye, P.D. Ferroelectric and Anti-Ferroelectric Hafnium Zirconium Oxide: Scaling Limit, Switching Speed and Record High Polarization Density. In Proceedings of the 2019 Symposium on VLSI Technology, Kyoto, Japan, 9–14 June 2019. [Google Scholar]

- Saitoh, M.; Ichihara, R.; Yamaguchi, M.; Suzuki, K.; Takano, K.; Akari, K.; Takahashi, K.; Kamiya, Y.; Matsuo, K.; Kamimuta, Y.; et al. HfO2-based FeFET and FTJ for Ferroelectric-Memory Centric 3D LSI towards Low-Power and High-Density Storage and AI Applications. In Proceedings of the 2020 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 12–18 December 2020. [Google Scholar]

- Marinella, M.J.; Agarwal, S.; Hsia, A.; Richter, I.; Jacobs-Gedrim, R.; Niroula, J.; Plimpton, S.J.; Ipek, E.; James, C.D. Multiscale Co-Design Analysis of Energy, Latency, Area, and Accuracy of a ReRAM Analog Neural Training Accelerator. IEEE J. Emerg. Sel. Top. Circuits Syst. 2018, 8, 86–101. [Google Scholar] [CrossRef]

- Yang, S.-T.; Li, X.-Y.; Yu, T.-L.; Wang, J.; Fang, H.; Nie, F.; He, B.; Zhao, L.; Lü, W.-M.; Yan, S.-S.; et al. High-Performance Neuromorphic Computing Based on Ferroelectric Synapses with Excellent Conductance Linearity and Symmetry. Adv. Funct. Mater. 2022, 32, 2202366. [Google Scholar] [CrossRef]

- Yu, S.; Chen, P.-Y. Emerging Memory Technologies: Recent Trends and Prospects. IEEE Solid-State Circuits Mag. 2016, 8, 43–56. [Google Scholar] [CrossRef]

- Yang, R. In-memory computing with ferroelectrics. Nat. Electron. 2020, 3, 237–238. [Google Scholar] [CrossRef]

- Fuller, E.J.; Keene, S.T.; Melianas, A.; Wang, Z.; Agarwal, S.; Li, Y.; Tuchman, Y.; James, C.D.; Marinella, M.J.; Yang, J.J. Parallel programming of an ionic floating-gate memory array for scalable neuromorphic computing. Science 2019, 364, 570–574. [Google Scholar] [CrossRef]

- Yu, J.; Li, Y.; Sun, W.; Zhang, W.; Gao, Z.; Dong, D.; Yu, Z.; Zhao, Y.; Lai, J.; Ding, Q. Energy efficient and robust reservoir computing system using ultrathin (3.5 nm) ferroelectric tunneling junctions for temporal data learning. In Proceedings of the 2021 Symposium on VLSI Technology, Kyoto, Japan, 13–19 June 2021. [Google Scholar]

- Chen, L.; Wang, T.-Y.; Dai, Y.-W.; Cha, M.-Y.; Zhu, H.; Sun, Q.-Q.; Ding, S.-J.; Zhou, P.; Chua, L.; Zhang, D.W. Ultra-low power Hf0.5Zr0.5O2 based ferroelectric tunnel junction synapses for hardware neural network applications. Nanoscale 2018, 10, 15826–15833. [Google Scholar] [CrossRef]

- Ota, K.; Yamaguchi, M.; Berdan, R.; Marukame, T.; Nishi, Y.; Matsuo, K.; Takahashi, K.; Kamiya, Y.; Miyano, S.; Deguchi, J.; et al. Performance Maximization of In-Memory Reinforcement Learning with Variability-Controlled Hf1−xZrxO2 Ferroelectric Tunnel Junctions. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019. [Google Scholar]

- Berdan, R.; Marukame, T.; Kabuyanagi, S.; Ota, K.; Saitoh, M.; Fujii, S.; Deguchi, J.; Nishi, Y. In-memory Reinforcement Learning with Moderately-Stochastic Conductance Switching of Ferroelectric Tunnel Junctions. In Proceedings of the 2019 Symposium on VLSI Technology, Kyoto, Japan, 9–14 June 2019. [Google Scholar]

- Luo, Y.-C.; Hur, J.; Yu, S. Ferroelectric Tunnel Junction Based Crossbar Array Design for Neuro-Inspired Computing. IEEE Trans. Nanotechnol. 2021, 20, 243–247. [Google Scholar] [CrossRef]

- Goh, Y.; Hwang, J.; Kim, M.; Lee, Y.; Jung, M.; Jeon, S. Selector-less Ferroelectric Tunnel Junctions by Stress Engineering and an Imprinting Effect for High-Density Cross-Point Synapse Arrays. ACS Appl. Mater. Interfaces 2021, 13, 59422–59430. [Google Scholar] [CrossRef]

- Kim, S.; Lee, K.; Oh, M.-H.; Lee, J.-H.; Park, B.-G.; Kwon, D. Physical Unclonable Functions Using Ferroelectric Tunnel Junctions. IEEE Electron Device Lett. 2021, 42, 816–819. [Google Scholar] [CrossRef]

- Lim, S.; Goh, Y.; Lee, Y.K.; Ko, D.H.; Hwang, J.; Kim, M.; Jeong, Y.; Shin, H.; Jeon, S.; Jung, S.-O. A Highly Integrated Crosspoint Array Using Self-rectifying FTJ for Dual-mode Operations: CAM and PUF. In Proceedings of the ESSCIRC 2022- IEEE 48th European Solid State Circuits Conference (ESSCIRC), Milan, Italy, 19–22 September 2022. [Google Scholar]

- Bae, H.; Moon, T.; Nam, S.G.; Lee, K.-H.; Kim, S.; Hong, S.; Choe, D.-H.; Jo, S.; Lee, Y.; Heo, J. Ferroelectric Diodes with Sub-ns and Sub-fJ Switching and Its Programmable Network for Logic-in-Memory Applications. In Proceedings of the 2021 Symposium on VLSI Technology, Kyoto, Japan, 13–19 June 2021. [Google Scholar]

- Zhang, Z.; Zhang, F.; Zhang, Y.; Xu, G.; Wu, Z.; Zhang, Q.; Li, Y.; Yin, H.; Luo, J.; Wang, W.; et al. Ultradense One-Memristor Ternary-Content-Addressable Memory Based on Ferroelectric Diodes. IEEE Electron Device Lett. 2023, 44, 64–67. [Google Scholar] [CrossRef]

- Kao, R.-W.; Peng, H.-K.; Chen, K.-Y.; Wu, Y.-H. HfZrOx-Based Switchable Diode for Logic-in-Memory Applications. IEEE Trans. Electron Devices 2021, 68, 545–549. [Google Scholar] [CrossRef]

- Ma, T.P.; Han, J.-P. Why is Nonvolatile Ferroelectric Memory Field-Effect Transistor Still Elusive? IEEE Electron Device Lett. 2002, 23, 386–388. [Google Scholar] [CrossRef]

- Bae, H.; Nam, S.G.; Moon, T.; Lee, Y.; Jo, S.; Choe, D.-H.; Kim, S.; Lee, K.-H.; Heo, J. Sub-ns Polarization Switching in 25 nm FE FinFET toward Post CPU and Spatial-Energetic Mapping of Traps for Enhanced Endurance. In Proceedings of the 2020 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 12–18 December 2020. [Google Scholar]

- Liao, C.-Y.; Hsiang, K.-Y.; Lou, Z.-F.; Tseng, H.-C.; Lin, C.-Y.; Li, Z.-X.; Hsieh, F.-C.; Wang, C.-C.; Chang, F.-S.; Ray, W.-C.; et al. Endurance > 1011 Cycling of 3D GAA Nanosheet Ferroelectric FET with Stacked HfZrO2 to Homogenize Corner Field Toward Mitigate Dead Zone for High-Density eNVM. In Proceedings of the 2022 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), Honolulu, HI, USA, 12–17 June 2022. [Google Scholar]

- Chen, C.-K.; Fang, Z.; Hooda, S.; Lal, M.; Chand, U.; Xu, Z.; Pan, J.; Tsai, S.-H.; Zamburg, E.; Thean, A.V.-Y. First Demonstration of Ultra-low Dit Top-Gated Ferroelectric Oxide-Semiconductor Memtransistor with Record Performance by Channel Defect Self-Compensation Effect for BEOL-Compatible Non-Volatile Logic Switch. In Proceedings of the 2022 International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2022. [Google Scholar]

- Yu, S. Neuro-Inspired Computing With Emerging Nonvolatile Memorys. Proc. IEEE 2018, 106, 260–285. [Google Scholar] [CrossRef]

- Jeong, D.S.; Hwang, C.S. Nonvolatile Memory Materials for Neuromorphic Intelligent Machines. Adv. Mater. 2018, 30, e1704729. [Google Scholar] [CrossRef]

- Oh, S.; Kim, T.; Kwak, M.; Song, J.; Woo, J.; Jeon, S.; Yoo, I.K.; Hwang, H. HfZrOx-Based Ferroelectric Synapse Device with 32 Levels of Conductance States for Neuromorphic Applications. IEEE Electron Device Lett. 2017, 38, 732–735. [Google Scholar] [CrossRef]

- Nako, E.; Toprasertpong, K.; Nakane, R.; Takenaka, M.; Takagi, S. Experimental demonstration of novel scheme of HZO/Si FeFET reservoir computing with parallel data processing for speech recognition. In Proceedings of the 2022 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), Honolulu, HI, USA, 12–17 June 2022. [Google Scholar]

- Chung, W.; Si, M.; Shrestha, P.R.; Campbell, J.P.; Cheung, K.P.; Peide, D.Y. First Direct Experimental Studies of Hf0.5Zr0.5O2 Ferroelectric Polarization Switching Down to 100-picosecond in Sub-60mV/dec Germanium Ferroelectric Nanowire FETs. In Proceedings of the 2018 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 18–22 June 2018. [Google Scholar]

- Bae, H.; Park, T.J.; Noh, J.; Chung, W.; Si, M.; Ramanathan, S.; Peide, D.Y. First demonstration of robust tri-gate β-Ga2O3 nano-membrane field-effect transistors. Nanotechnology 2021, 33, 125201. [Google Scholar] [CrossRef] [PubMed]

- Noh, J.; Alajlouni, S.; Tadjer, M.J.; Culbertson, J.C.; Bae, H.; Si, M.; Zhou, H.; Bermel, P.A.; Shakouri, A.; Peide, D.Y. High Performance β-Ga2O3 Nano-Membrane Field Effect Transistors on a High Thermal Conductivity Diamond Substrate. IEEE J. Electron Devices Soc. 2019, 7, 914–918. [Google Scholar] [CrossRef]

- Luo, Z.-D.; Zhang, S.; Liu, Y.; Zhang, D.; Gan, X.; Seidel, J.; Liu, Y.; Han, G.; Alexe, M.; Hao, Y. Dual-Ferroelectric-Coupling-Engineered Two-Dimensional Transistors for Multifunctional In-Memory Computing. ACS Nano 2022, 16, 3362–3372. [Google Scholar] [CrossRef]

- Francois, T.; Grenouillet, L.; Coignus, J.; Blaise, P.; Carabasse, C.; Vaxelaire, N.; Magis, T.; Aussenac, F.; Loup, V.; Pellissier, C.; et al. Demonstration of BEOL-compatible ferroelectric Hf0.5Zr0.5O2 scaled FeRAM co-integrated with 130nm CMOS for embedded NVM applications. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019. [Google Scholar]

- Mikolajick, T.; Park, M.H.; Begon-Lours, L.; Slesazeck, S. From Ferroelectric Material Optimization to Neuromorphic Devices. Adv. Mater. 2022, e2206042. [Google Scholar] [CrossRef]

- Okuno, J.; Kunihiro, T.; Konishi, K.; Maemura, H.; Shuto, Y.; Sugaya, F.; Materano, M.; Ali, T.; Kuehnel, K.; Seidel, K. SoC compatible 1T1C FeRAM memory array based on ferroelectric Hf0. 5Zr0. 5O2. In Proceedings of the 2020 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 16–19 June 2020. [Google Scholar]

- Sung, M.; Rho, K.; Kim, J.; Cheon, J.; Choi, K.; Kim, D.; Em, H.; Park, G.; Woo, J.; Lee, Y.; et al. Low Voltage and High Speed 1Xnm 1T1C FE-RAM with Ultra-Thin 5nm HZO. In Proceedings of the 2021 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 11–16 December 2021. [Google Scholar]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yoo, J.; Song, H.; Lee, H.; Lim, S.; Kim, S.; Heo, K.; Bae, H. Recent Research for HZO-Based Ferroelectric Memory towards In-Memory Computing Applications. Electronics 2023, 12, 2297. https://doi.org/10.3390/electronics12102297

Yoo J, Song H, Lee H, Lim S, Kim S, Heo K, Bae H. Recent Research for HZO-Based Ferroelectric Memory towards In-Memory Computing Applications. Electronics. 2023; 12(10):2297. https://doi.org/10.3390/electronics12102297

Chicago/Turabian StyleYoo, Jaewook, Hyeonjun Song, Hongseung Lee, Seongbin Lim, Soyeon Kim, Keun Heo, and Hagyoul Bae. 2023. "Recent Research for HZO-Based Ferroelectric Memory towards In-Memory Computing Applications" Electronics 12, no. 10: 2297. https://doi.org/10.3390/electronics12102297

APA StyleYoo, J., Song, H., Lee, H., Lim, S., Kim, S., Heo, K., & Bae, H. (2023). Recent Research for HZO-Based Ferroelectric Memory towards In-Memory Computing Applications. Electronics, 12(10), 2297. https://doi.org/10.3390/electronics12102297