A 52-to-57 GHz CMOS Phase-Tunable Quadrature VCO Based on a Body Bias Control Technique

Abstract

1. Introduction

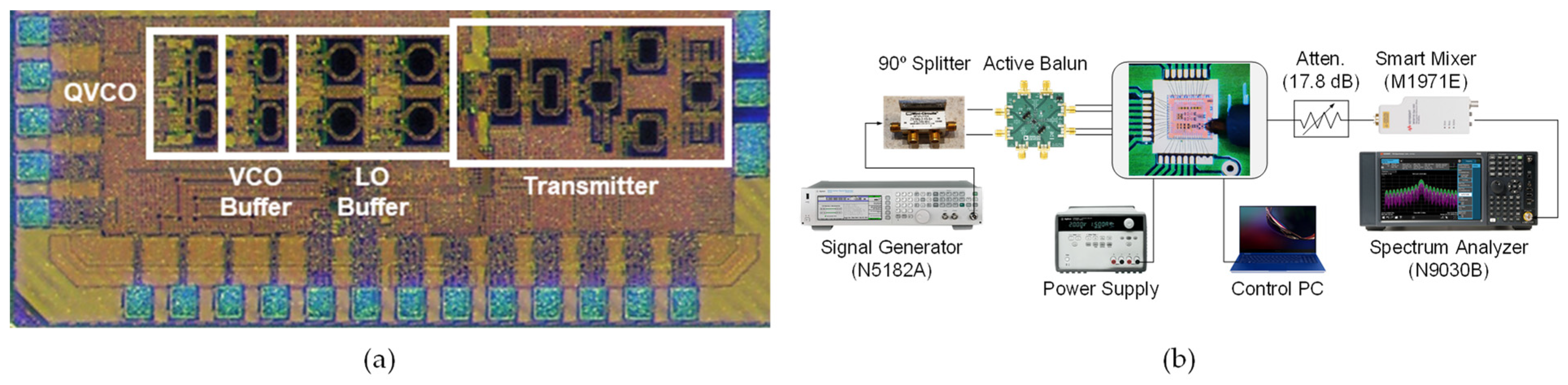

2. Circuit Design

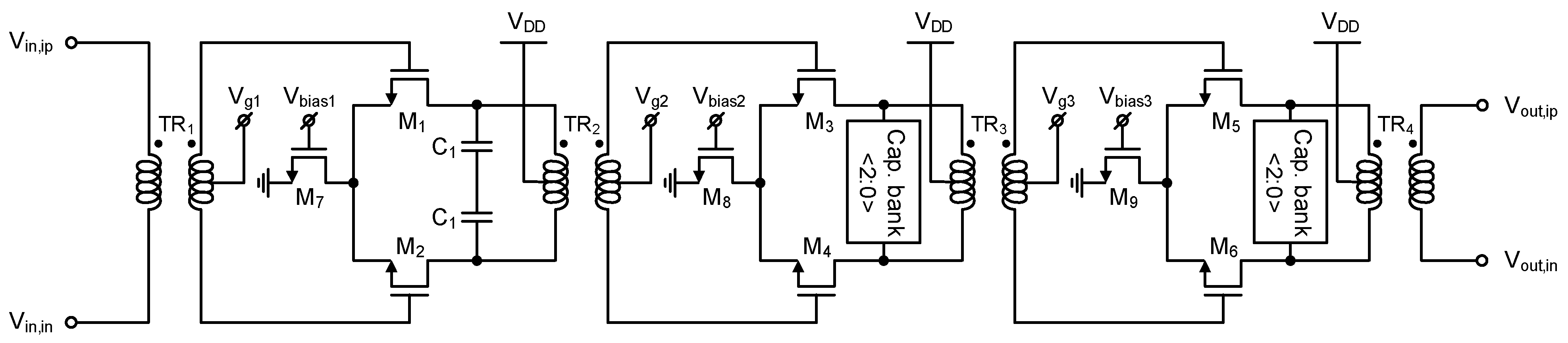

2.1. Phase-Tunable In-Phase Injection-Coupled (IPIC) QVCO

2.2. Quadrature LO Generator with the Proposed QVCO and Phase-Tunable Buffer

3. Implementation Results

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Lien, J.; Gillian, N.; Karagozler, M.E.; Amihood, P.; Schwesig, C.; Olson, E.; Raja, H.; Poupyrev, I. Soli: Ubiquitous Gesture Sensing with Millimeter Wave Radar. ACM Trans. Graph. 2016, 35, 142. [Google Scholar] [CrossRef]

- Shopov, S.; Girma, M.G.; Hasch, J.; Cahoon, N.; Voinigescu, S.P. Ultralow-Power Radar Sensors for Ambient Sensing in the V-Band. IEEE Trans. Microw. Theory Tech. 2017, 65, 5401–5410. [Google Scholar] [CrossRef]

- Zhou, P.; Cheng, K.; Han, X.; Fang, X.; Fang, Y.; He, R.; Long, Y.; Liu, Y. IEEE 802.11 ay-based mmWave WLANs: Design Challenges and Solutions. IEEE Commun. Surv. Tutor. 2018, 20, 1654–1681. [Google Scholar] [CrossRef]

- Wu, R.; Minami, R.; Tsukui, Y.; Kawai, S.; Seo, Y.; Sato, S.; Kimura, K.; Kondo, S.; Ueno, T.; Fajri, N.; et al. 64-QAM 60-GHz CMOS Transceivers for IEEE 802.11ad/ay. IEEE J. Solid-State Circuits 2017, 52, 2871–2891. [Google Scholar] [CrossRef]

- Ha, J.K.; Noh, C.K.; Lee, J.S.; Kang, H.J.; Kim, Y.M.; Kim, T.H.; Jung, H.N.; Lee, S.H.; Cho, C.S.; Kim, Y.J. RF Transceiver for the Multi-Mode Radar Applications. Sensors 2021, 21, 1563. [Google Scholar] [CrossRef] [PubMed]

- Lee, Y.; Kim, S.; Shin, H. A 55-GHz Highly Linear Direct RF Transmitter in 40 nm CMOS. In Proceedings of the 17th European Microwave Integrated Circuits Conference (EuMIC), Milan, Italy, 26–27 September 2022; pp. 177–180. [Google Scholar]

- Piri, F.; Bassi, M.; Lacaita, N.; Mazzanti, A.; Svelto, F. A > 40 dB IRR, 44% Fractional-Bandwidth Ultra-Wideband mm-Wave Quadrature LO Generator for 5G Networks in 55 nm CMOS. In Proceedings of the International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 11–15 February 2018; pp. 368–370. [Google Scholar]

- Lee, Y.; Kim, S.; Shin, H. A 24 GHz CMOS Direct-Conversion RF Receiver with I/Q Mismatch Calibration for Radar Sensor Applications. Sensors 2022, 22, 8246. [Google Scholar] [CrossRef] [PubMed]

- Wu, L.; Leung, H.F.; Li, A.; Luong, H.C. A 4-Element 60-GHz CMOS Phased-Array Receiver with Beamforming Calibration. IEEE Trans. Circuits Syst. I Reg. Pap. 2017, 64, 642–652. [Google Scholar] [CrossRef]

- Wu, L.; Li, A.; Luong, H.C. A 4-Path 42.8-to-49.5 GHz LO Generation with Automatic Phase Tuning for 60 GHz Phased-Array Receivers. IEEE J. Solid-State Circuits 2013, 48, 2309–2322. [Google Scholar] [CrossRef]

- Siriburanon, T.; Kondo, S.; Katsuragi, M.; Liu, H.; Kimura, K.; Deng, W.; Okada, K.; Matsuzawa, A. A Low-Power Low-Noise mm-Wave Subsampling PLL Using Dual-Step-Mixing ILFD and Tail-Coupling Quadrature Injection-Locked Oscillator for IEEE 802.11ad. IEEE J. Solid-State Circuits 2016, 51, 1246–1260. [Google Scholar] [CrossRef]

- Kim, H.-T.; Park, B.-S.; Song, S.-S.; Moon, T.-S.; Kim, S.-H.; Kim, J.-M.; Chang, J.-Y.; Ho, Y.-C. A 28-GHz CMOS Direct Conversion Transceiver with Packaged 2 × 4 Antenna Array for 5G Cellular System. IEEE J. Solid State Circuits 2018, 53, 1245–1259. [Google Scholar] [CrossRef]

- Scheir, K.; Vandersteen, G.; Rolain, Y.; Wambacq, P. A 57-to-66 GHz Quadrature PLL in 45 nm Digital CMOS. In Proceedings of the International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 8–12 February 2009; pp. 494–496. [Google Scholar]

- Chang, H.-Y.; Chan, C.-C.; Li, S.-M.; Yeh, H.-N.; Shen, I.Y.-E.; Huang, G.-L. Design and Analysis of CMOS Low-Phase-Noise Low Quadrature Error V-Band Subharmonically Injection-Locked Quadrature FLL. IEEE Trans. Microw. Theory Tech. 2018, 66, 2851–2866. [Google Scholar] [CrossRef]

- Decanis, U.; Ghilioni, A.; Monaco, E.; Mazzanti, A.; Svelto, F. A Low-Noise Quadrature VCO Based on Magnetically Coupled Resonators and a Wideband Frequency Divider at Millimeter Waves. IEEE J. Solid-State Circuits 2011, 46, 2943–2955. [Google Scholar] [CrossRef]

- Wu, L.; Luong, H.C. A 49-to-62 GHz Quadrature VCO with Bimodal Enhanced-Magnetic-Tuning Technique. IEEE Trans. Circuits Syst. I Reg. Pap. 2014, 61, 3025–3033. [Google Scholar] [CrossRef]

- Xi, T.; Guo, S.; Gui, P.; Huang, D.; Fan, Y.; Morgan, M. Low-Phase-Noise 54-GHz Transformer-Coupled Quadrature VCO and 76-/90-GHz VCOs in 65-nm CMOS. IEEE Trans. Microw. Theory Tech. 2016, 64, 2091–2103. [Google Scholar] [CrossRef]

- Szortyka, V.; Shi, Q.; Raczkowski, K.; Parvais, B.; Kuijk, M.; Wambacq, P. A 42 mW 200 fs-Jitter 60 GHz Sub-Sampling PLL in 40 nm CMOS. IEEE J. Solid-State Circuits 2015, 50, 2025–2036. [Google Scholar] [CrossRef]

- Zhang, L.; Kuo, N.-C.; Niknejad, A.M. A 37.5–45 GHz Superharmonic-Coupled QVCO with Tunable Phase Accuracy in 28 nm CMOS. IEEE J. Solid-State Circuits 2019, 54, 2754–2764. [Google Scholar] [CrossRef]

- Yi, X.; Boon, C.C.; Liu, H.; Lin, J.F.; Lim, W.M. A 57.9-to-68.3 GHz 24.6 mW Frequency Synthesizer with In-Phase Injection-Coupled QVCO in 65 nm CMOS Technology. IEEE J. Solid-State Circuits 2014, 49, 347–359. [Google Scholar] [CrossRef]

- Pellerano, S.; Callender, S.; Shin, W.; Wang, Y.; Kundu, S.; Agrawal, A.; Sagazio, P.; Carlton, B.; Sheikh, F.; Amadjikpe, A.; et al. A Scalable 71-to-76 GHz 64-Element Phased-Array Transceiver Module with 2 × 2 Direct-Conversion IC in 22 nm FinFET CMOS Technology. In Proceedings of the International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 17–21 February 2019; pp. 174–176. [Google Scholar]

- Kim, J.; Shin, J.; Kim, S.; Shin, H. A Wide-Band CMOS LC VCO with Linearized Coarse Tuning Characteristics. IEEE Trans. Circuits Syst. II Exp. Briefs 2008, 55, 399–403. [Google Scholar]

- Shin, J.; Shin, H. A 1.9–3.8 GHz Fractional-N PLL Frequency Synthesizer with Fast Auto-Calibration of Loop Bandwidth and VCO Frequency. IEEE J. Solid-State Circuits 2012, 47, 665–674. [Google Scholar] [CrossRef]

- Lee, Y.; Kim, B.; Shin, H. 28-GHz Direct-Conversion RF Transmitter with Precise and Wide-Range Mismatch Calibration Techniques. Electronics 2022, 11, 840. [Google Scholar] [CrossRef]

- Chang, S.; Shin, H. 2.4-GHz CMOS Bluetooth RF Receiver with Improved IM2 Distortion Tolerance. IEEE Trans. Microw. Theory Tech. 2020, 68, 4589–4598. [Google Scholar] [CrossRef]

| This Work | [19] | [18] | [20] | [17] | [16] | [15] | [14] | |

|---|---|---|---|---|---|---|---|---|

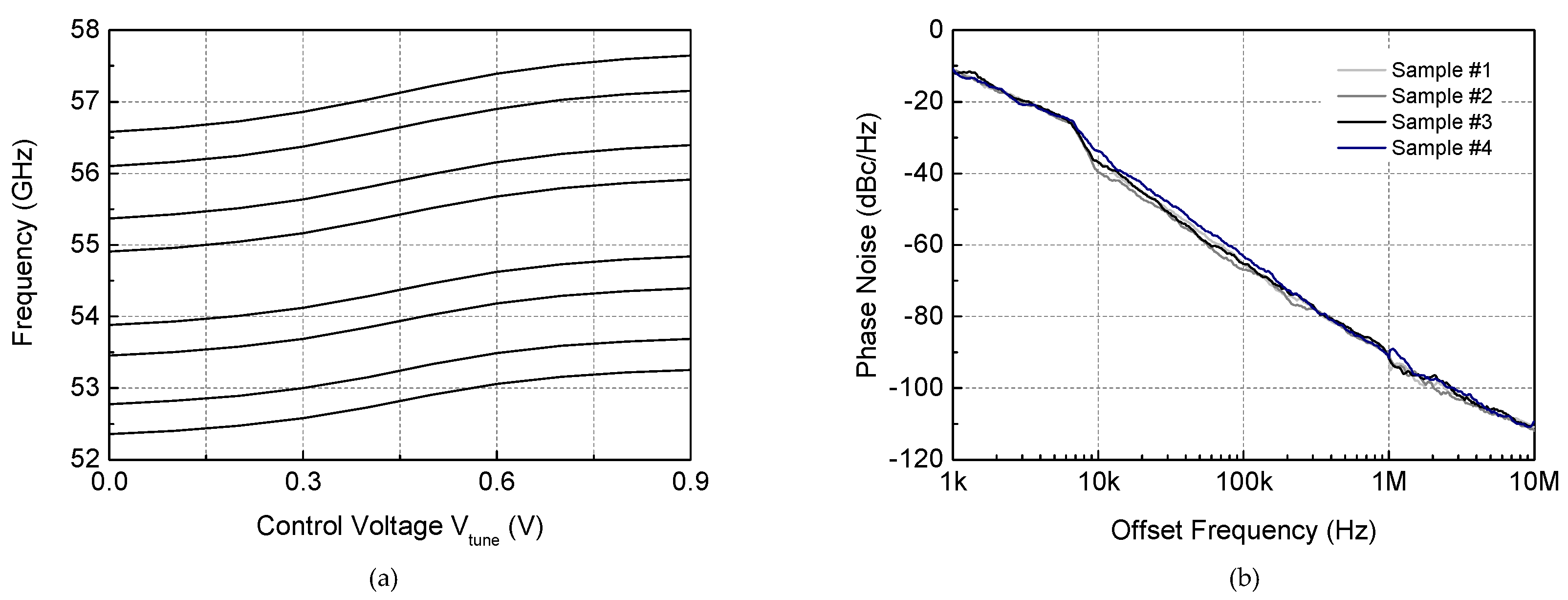

| Frequency Range (GHz) | 52.4–57.6 | 37.5–45.1 | 53.8–63.3 | 57.9–68.3 | 51.7–56.6 | 48.8–62.3 | 56.0–60.4 | 55.6–59.1 |

| Frequency-Tuning Range (%) | 9.5 | 18.4 | 16.2 | 16.6 | 9.1 | 24 | 7.5 | 4.1 |

| I/Q Phase-Tuning Method | Body bias | Coupling gm stage | Tank varactor | None | None | None | None | None |

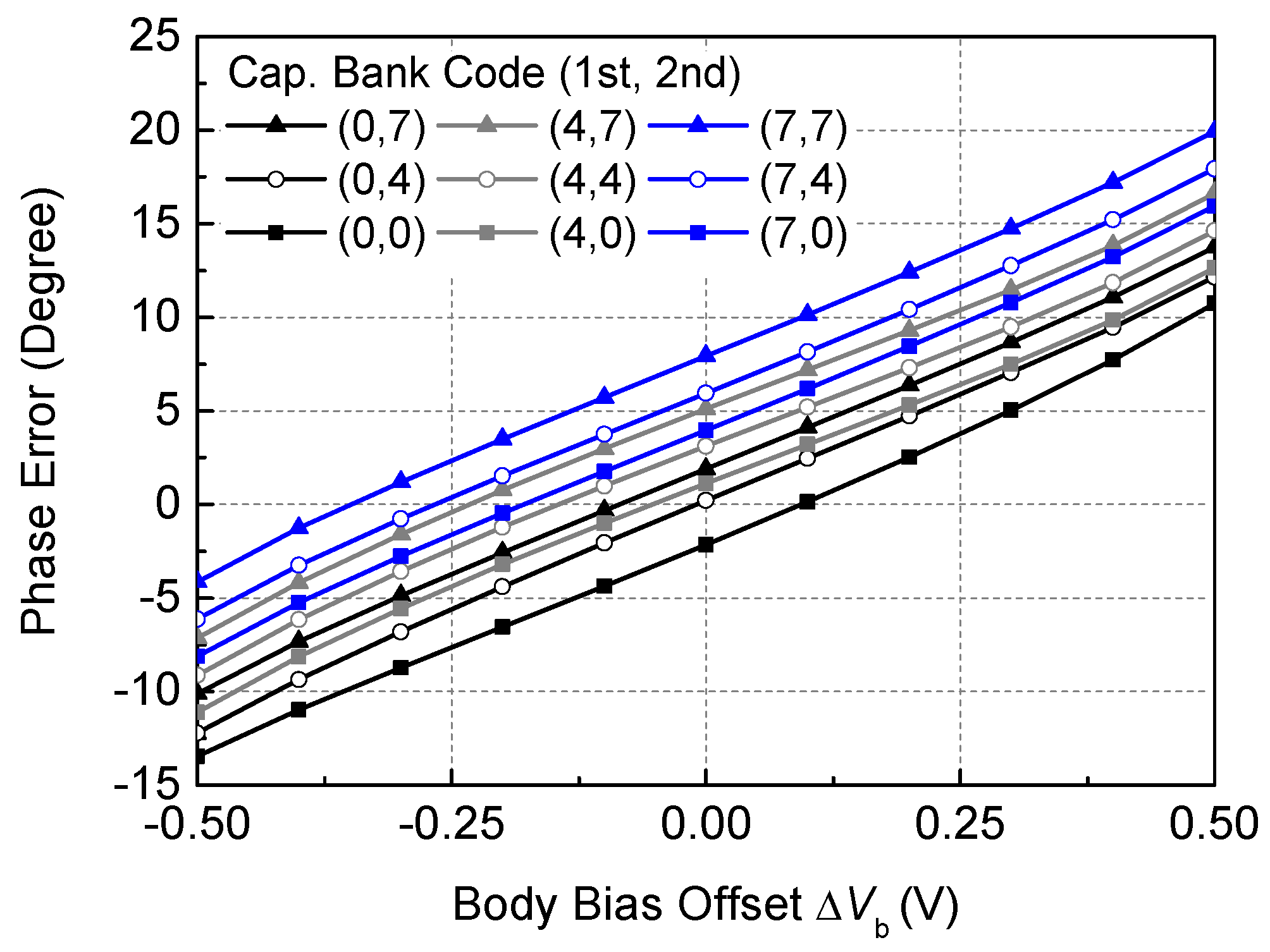

| I/Q Phase-Tuning Range (Degrees) | −13.4–+10.7 (−22.7–+20.0) 3 | +0.1–+2.5 | −25.0–+25.0 | – | – | – | – | – |

| Phase Noise @1 MHz (dBc/Hz) | −91.8 | −94.3 | −94.5 | −94.2 | −95.5 | −89.8 | −96 | −83.2 |

| FoM 1 (dBc/Hz) | −172.4 | −177.4 | −178.4 | −179.6 | −176.4 | −172.7 | −177.9 | −165.8 |

| FoMT 2 (dBc/Hz) | −172.0 | −182.7 | −182.6 | −184.0 | −175.5 | −180.4 | −175.5 | −161.5 |

| Supply Voltage (V) | 0.9 | 0.75 | 0.9 | 1.2 | 0.8 | 1.2 | 1.0 | 1.2 |

| Power Dissipation (mW) | 26.2 | 8.4 | 14 | 11.4 | 24 | 16 | 22 | 18 |

| CMOS Process (nm) | 40 | 28 | 40 | 65 | 65 | 65 | 65 | 90 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lee, S.; Lee, Y.; Shin, H. A 52-to-57 GHz CMOS Phase-Tunable Quadrature VCO Based on a Body Bias Control Technique. Electronics 2023, 12, 2679. https://doi.org/10.3390/electronics12122679

Lee S, Lee Y, Shin H. A 52-to-57 GHz CMOS Phase-Tunable Quadrature VCO Based on a Body Bias Control Technique. Electronics. 2023; 12(12):2679. https://doi.org/10.3390/electronics12122679

Chicago/Turabian StyleLee, Seongmin, Yongho Lee, and Hyunchol Shin. 2023. "A 52-to-57 GHz CMOS Phase-Tunable Quadrature VCO Based on a Body Bias Control Technique" Electronics 12, no. 12: 2679. https://doi.org/10.3390/electronics12122679

APA StyleLee, S., Lee, Y., & Shin, H. (2023). A 52-to-57 GHz CMOS Phase-Tunable Quadrature VCO Based on a Body Bias Control Technique. Electronics, 12(12), 2679. https://doi.org/10.3390/electronics12122679