A Q-Band CMOS Image-Rejection Receiver Integrated with LO and Frequency Dividers

Abstract

1. Introduction

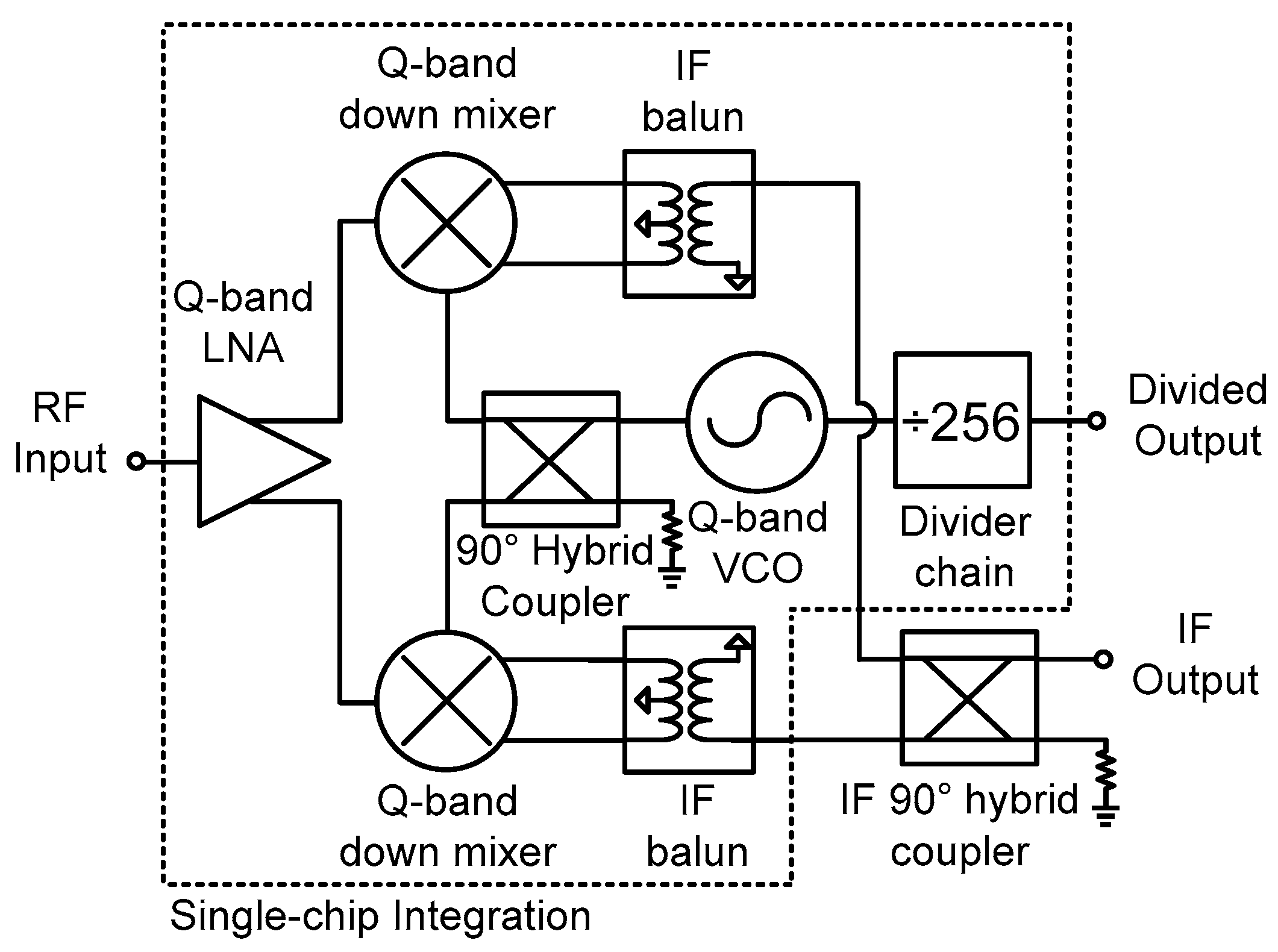

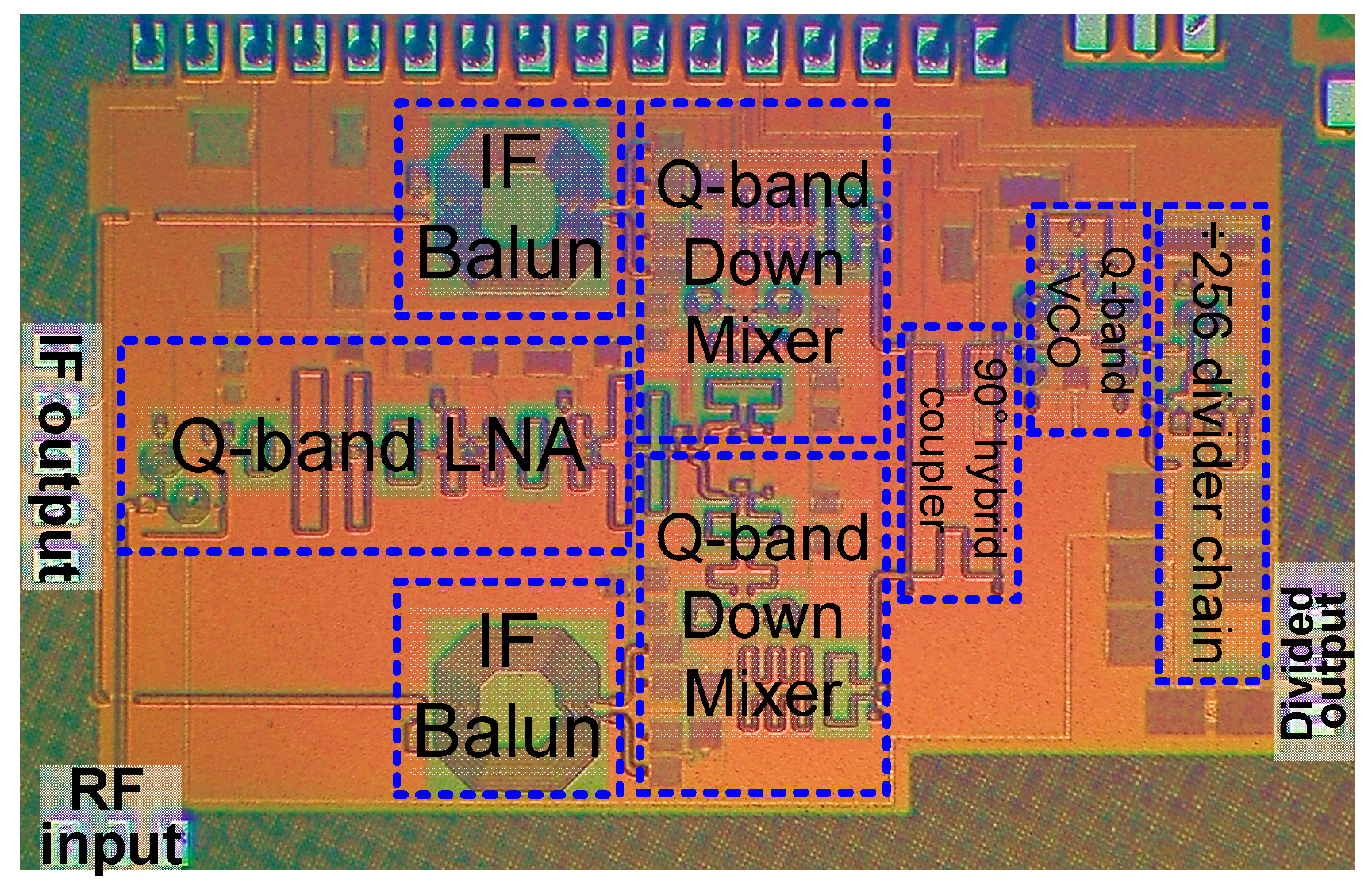

2. Q-Band Image-Rejection Receiver Architecture

3. Circuit Blocks of the Q-Band Image-Rejection Receiver

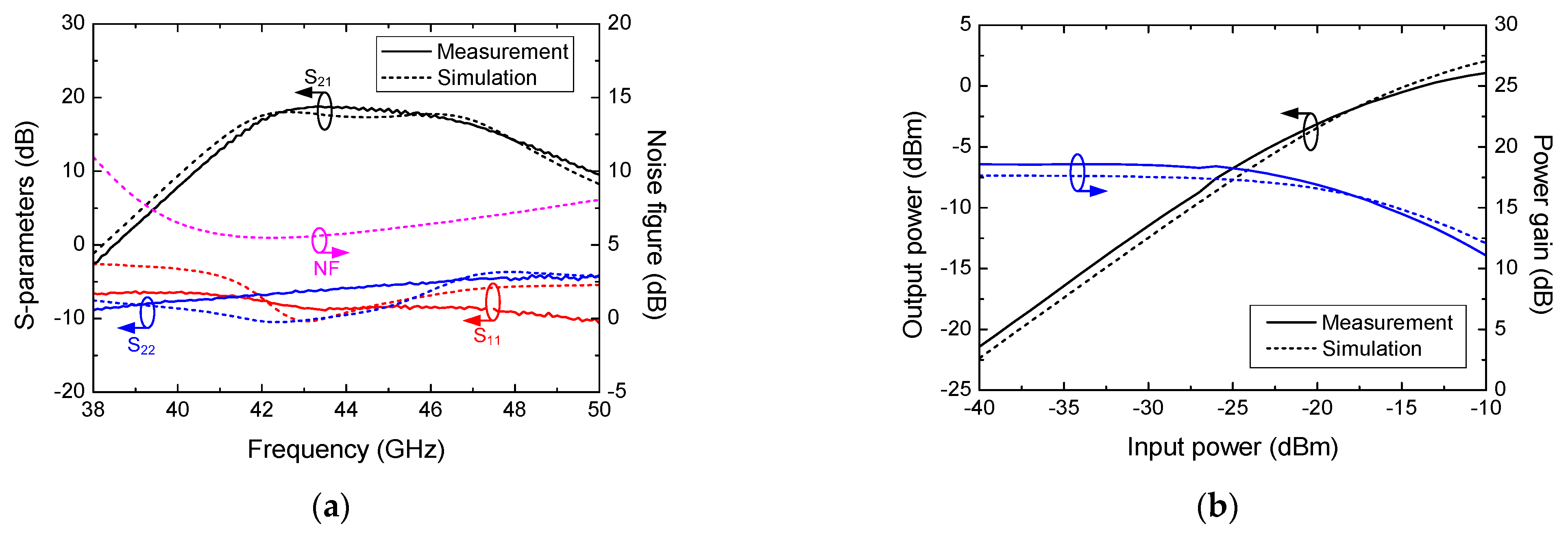

3.1. Q-Band LNA

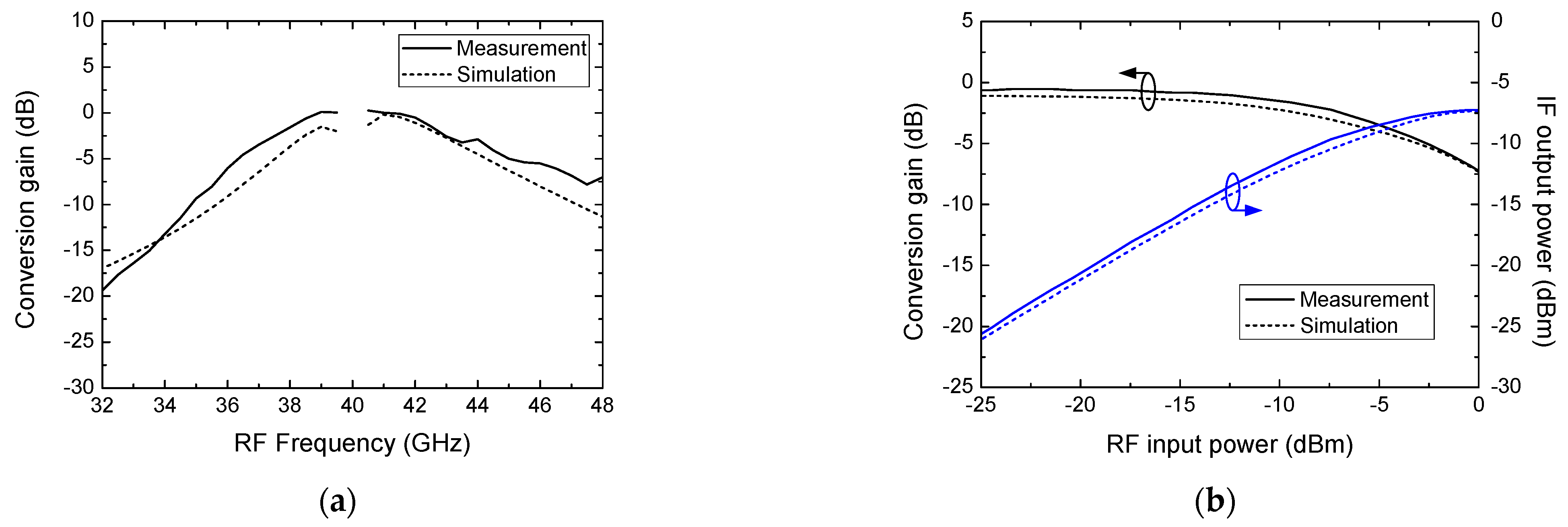

3.2. Q-Band Down-Conversion Mixer

3.3. Q-Band Voltage-Controlled Oscillator

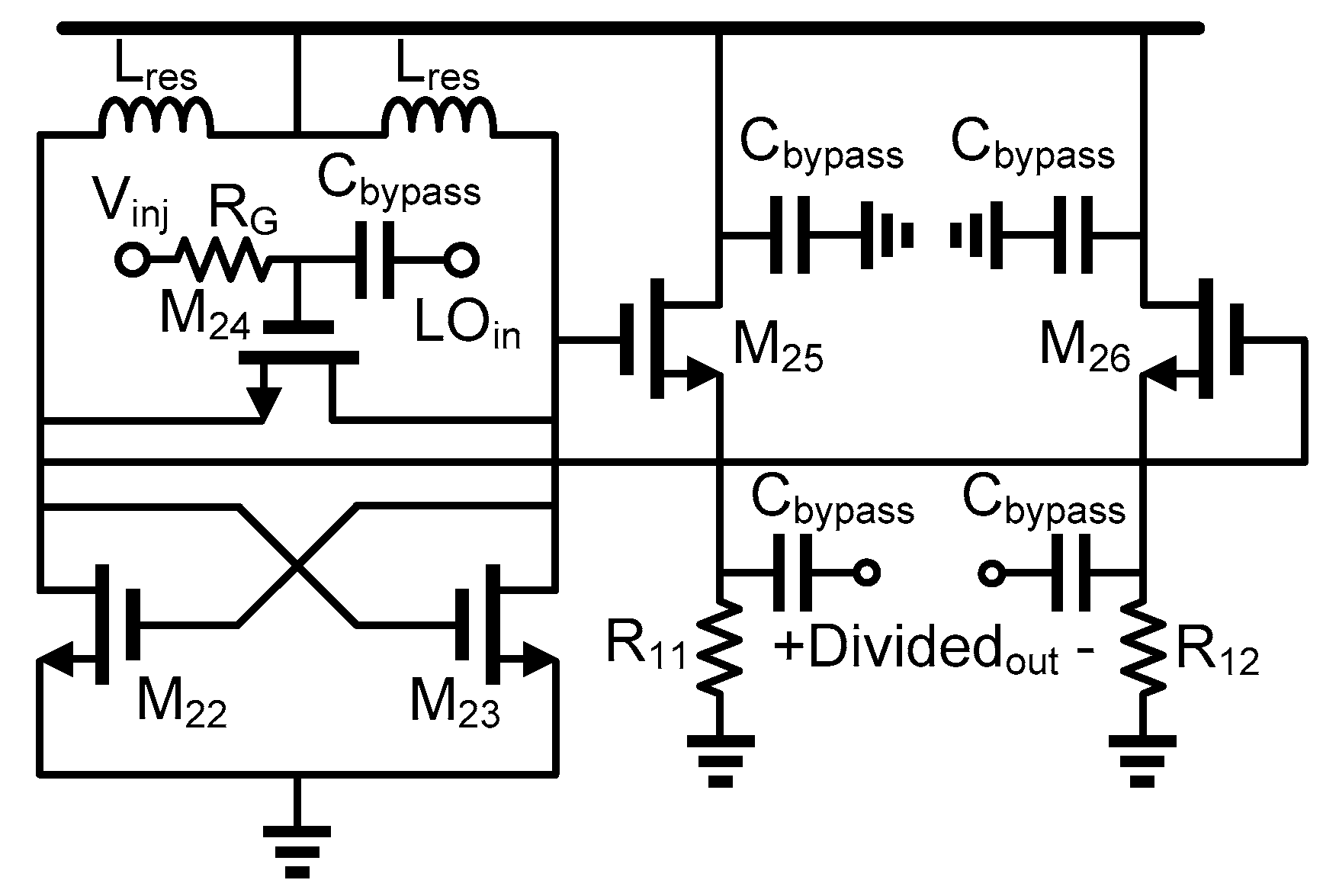

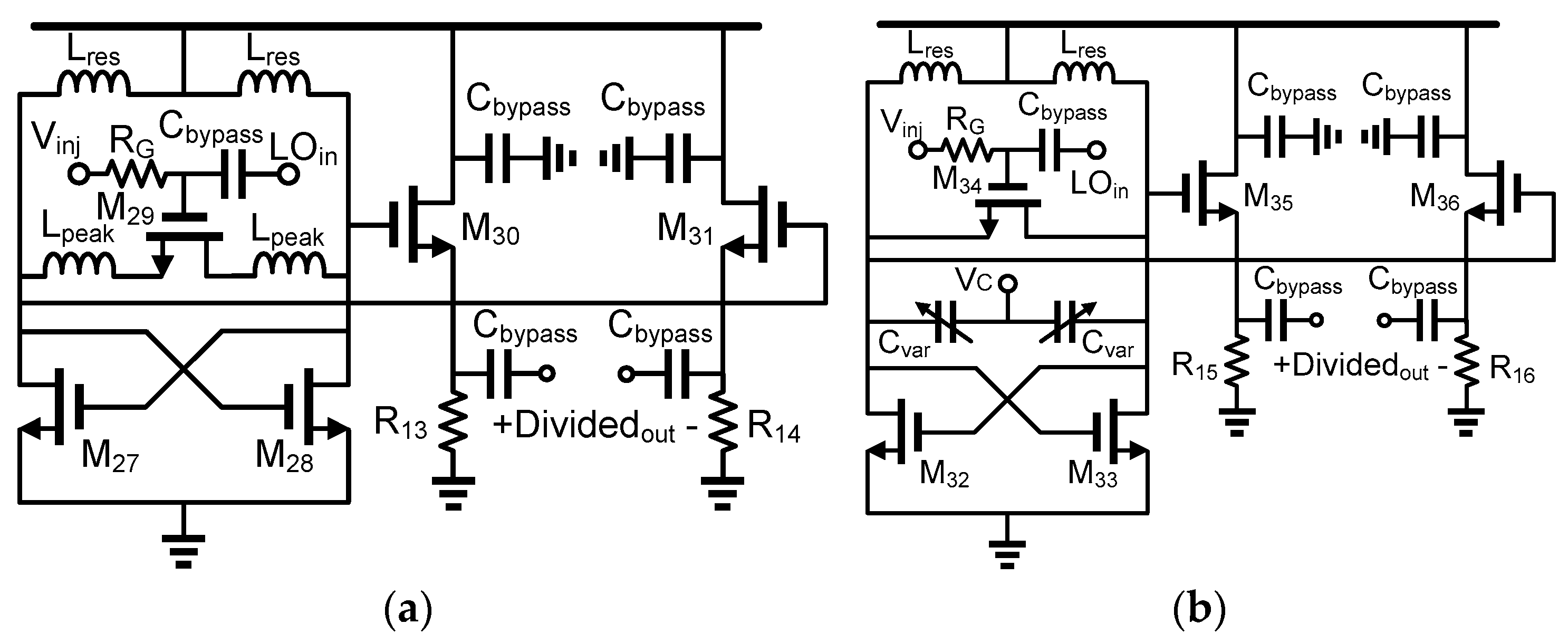

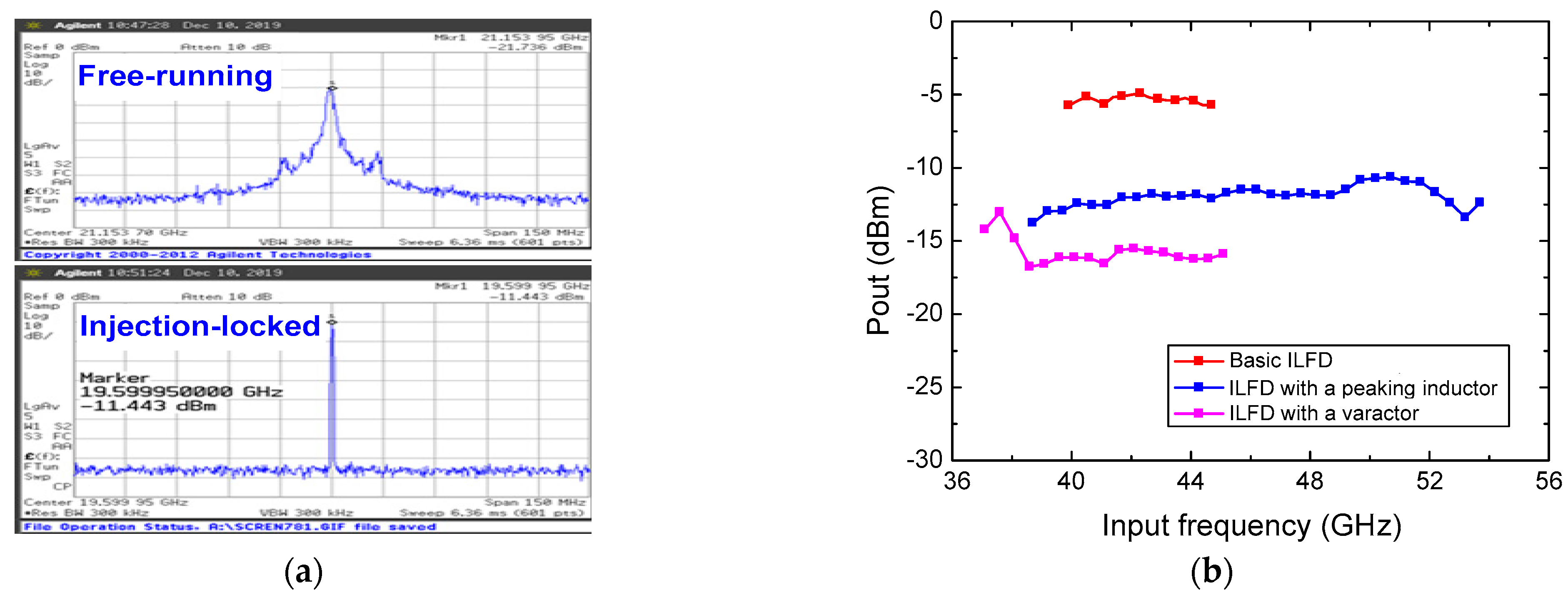

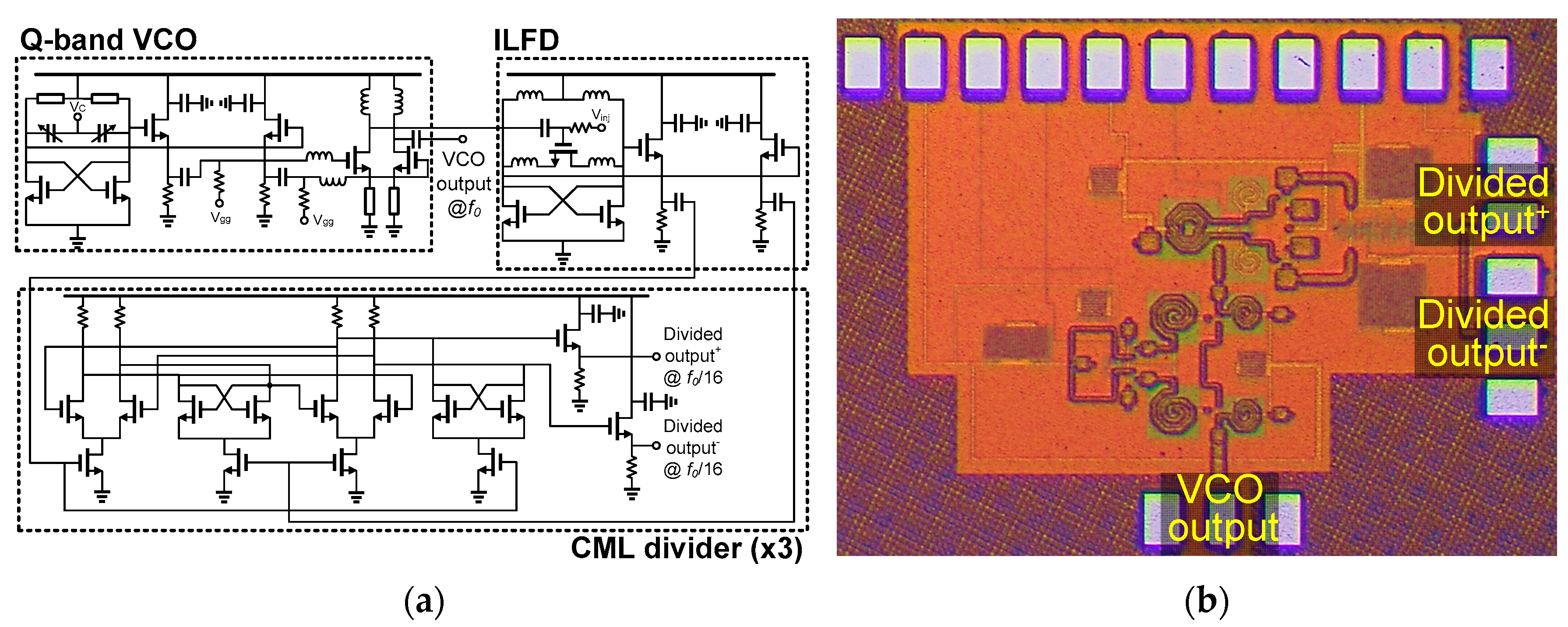

3.4. Frequency Divider Chain

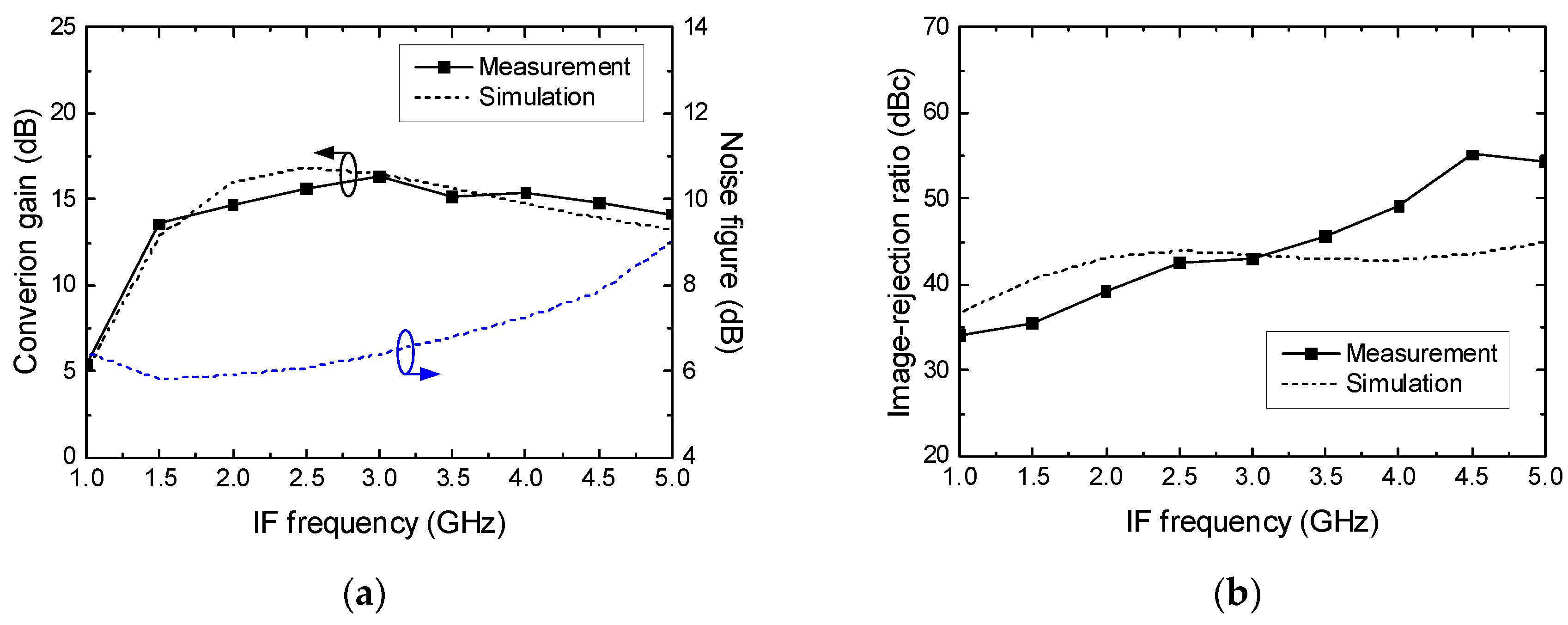

4. Measurement of the Q-Band Image-Rejection Receiver

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Kim, S.; Kim, B.; Lee, Y.; Kim, S.; Shin, H. A 28 GHz direct conversion receiver in 65nm CMOS for 5G mmWave radio. In Proceedings of the International System-on-Chip Design Conference (ISOCC), Jeju, Korea, 6–9 October 2019; pp. 29–30. [Google Scholar]

- Wong, A.C.-W.; Devita, G.; Wu, S.-M.; Lauria, F.; Eid, M.; Illuromi, O.; Ogunkunle, S.; Modigliana, A. A 4Rx, 4Tx Ka-band transceiver in 40 nm bulk CMOS technology for satellite terminal applications. In Proceedings of the IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Atlanta, GA, USA, 7–9 June 2021; pp. 211–214. [Google Scholar]

- Liu, X.; Yang, C.; Yang, Z.; Guo, Y.; Jin, J.; Shi, L.; Xu, Q.; Wu, L.; Zhou, J. Area-Efficient 28-GHz Four-Element Phased-Array Transceiver Front-End Achieving 25.2% Tx Efficiency at 15.68-dBm Output Power. IEEE Trans. Microw. Theory Tech. 2023, 71, 654–668. [Google Scholar] [CrossRef]

- Yuan, Y.; Li, N.; Zhou, J.; Gao, H.; Wang, S.; Lu, H.; Gu, Q.J.; Song, C.; Xu, Z. A Compact Ka-Band Eight-Element Four-Beam Receiver for Low-Earth-Orbit Satellite Communications in 65-nm CMOS. IEEE Microw. Wireless Tech. Lett. 2023, 33, 883–886. [Google Scholar] [CrossRef]

- Kim, H.-T.; Park, B.-S.; Song, S.-S.; Moon, T.-S.; Kim, S.-H.; Kim, J.-M.; Chang, J.-Y.; Ho, Y.-C. A 28-GHz CMOS Direct Conversion Transceiver with Packaged 2 × 4 Antenna Array for 5G Cellular System. IEEE J. Solid State Circ. 2018, 53, 1245–1259. [Google Scholar] [CrossRef]

- Lee, Y.; Kim, S.; Shin, H. A 24 GHz CMOS Direct-Conversion RF Receiver with I/Q Mismatch Calibration for Radar Sensor Applications. Sensors 2022, 22, 8246. [Google Scholar] [CrossRef] [PubMed]

- Shiramizu, N.; Nakamura, T.; Masuda, T.; Washio, K. A 24-GHz low-power fully integrated receiver with image-rejection using rich-transformer direct-stacked/coupled technique. In Proceedings of the IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Anaheim, CA, USA, 23–25 May 2010; pp. 369–372. [Google Scholar]

- Fonte, A.; Plutino, F.; Moquillon, L.; Razafimandimby, S.; Pruvost, S. 5G 26 GHz and 28 GHz bands SiGe:C receiver with very high-linearity and 56 db dynamic range. In Proceedings of the 2018 13th European Microwave Integrated Circuits Conference (EuMIC), Madrid, Spain, 23 September 2018; pp. 57–60. [Google Scholar]

- Ma, Q.; Chung, H.; Rebeiz, G.M. A 4-channel 10–40 GHz wideband receiver with integrated frequency quadrupler for high resolution millimeter-wave imaging systems. In Proceedings of the 2018 IEEE MTT-S International Microwave Symposium (IMS), Philadelphia, PA, USA, 10–15 June 2018; pp. 883–886. [Google Scholar]

- Milner, L.E.; Harvey, J.T.; Parker, M.E.; Hall, L.T.; Rodriguez, M.C.; Heimlich, M.C.; Mahon, S.J. A 25 to 45 GHz SiGe receiver MMIC. In Proceedings of the 2016 11th European Microwave Integrated Circuits Conference (EuMIC), London, UK, 3–4 October 2016; pp. 548–551. [Google Scholar]

- Huang, M.-Y.; Chi, T.; Wang, F.; Li, S.; Huang, T.-Y.; Wang, H. A 24.5–43.5 GHz compact RX with calibration-free 32-56 dB full-frequency instantaneously wideband image rejection supporting multi-Gb/s 64-QAM/256-QAM for multi-band 5G massive MIMO. In Proceedings of the IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Boston, MA, USA, 2–4 June 2019; pp. 275–278. [Google Scholar]

- El-Nozahi, M.; Amer, A.; Sanchez-Sinencio, E.; Entesari, K. A Millimeter-Wave (24/31-GHz) Dual-Band Switchable Harmonic Receiver in 0.18-μm SiGe Process. IEEE Trans. Microw. Theory Tech. 2010, 58, 2717–2730. [Google Scholar] [CrossRef]

- Li, G.; Ma, Q.; Rebeiz, G.M. A 20–44-GHz Image-Rejection Receiver With >75-dB Image-Rejection Ratio in 22-nm CMOS FD-SOI for 5G Applications. IEEE Trans. Microw. Theory Tech. 2020, 68, 2823–2832. [Google Scholar]

- Huang, M.-Y.; Chi, T.; Li, S.; Huang, T.-Y.; Wang, H. A 24.5–43.5-GHz ultra-compact CMOS receiver front end with calibration-free instantaneous full-band image rejection for multiband 5G massive MIMO. IEEE J. Solid State Circ. 2020, 55, 1177–1186. [Google Scholar] [CrossRef]

- Quadrelli, F.; Manente, D.; Seebacher, D.; Padovan, F.; Bassi, M.; Mazzanti, A.; Bevilacqua, A. A Broadband 22–31-GHz Bidirectional Image-Reject Up/Down Converter Module in 28-nm CMOS for 5G Communications. IEEE J. Solid State Circ. 2022, 57, 1968–1981. [Google Scholar] [CrossRef]

- Gao, L.; Rebeiz, G.M. A 20–42-GHz IQ Receiver in 22-nm CMOS FD-SOI With 2.7–4.2-dB NF and −25-dBm IP1dB for Wideband 5G Systems. IEEE Trans. Microw. Theory Tech. 2021, 69, 4951–4960. [Google Scholar] [CrossRef]

- Singh, R.; Mondal, S.; Paramesh, J. A Millimeter-Wave Receiver Using a Wideband Low-Noise Amplifier with One-Port Coupled Resonator Loads. IEEE Trans. Microw. Theory Tech. 2020, 68, 3794–3803. [Google Scholar] [CrossRef]

- Razavi, B. RF Microelectronics; Prentice Hall: Hoboken, NJ, USA, 2012. [Google Scholar]

- Hartley, R. Modulation System. U.S. Patent 1,666,206, 17 April 1928. [Google Scholar]

- Gilbert, B. A precise four-quadrant multiplier with subnanosecond response. IEEE J. Solid State Circ. 1968, 3, 365–373. [Google Scholar] [CrossRef]

- Sulivan, P.J.; Xavier, B.A.; Ku, W.H. Low voltage performance of a microwave CMOS Gilbert cell mixer. IEEE J. Solid State Circ. 1997, 32, 1151–1155. [Google Scholar] [CrossRef]

- Lee, S.-J.; Kim, B.; Lee, K. A novel high-speed ring oscillator for multiphase clock generation using negative skewed delay scheme. IEEE J. Solid State Circ. 1997, 32, 289–291. [Google Scholar]

- Castañeda-Aviña, P.R.; Tlelo-Cuautle, E.; De la Fraga, L.G. Phase noise optimization of integrated ring voltage-controlled oscillators by metaheuristics. AIMS Math. 2022, 7, 14826–14839. [Google Scholar] [CrossRef]

- Maggio, G.M.; Feo, O.D.; Kennedy, M.P. VCOs can be designed using ring-type, colpitts, and cross-coupled structures. IEEE Trans. Circ. Syst. I Fundam. Theory Appl. 1999, 46, 1118–1130. [Google Scholar] [CrossRef]

- Hajimiri, A.; Lee, T.H. Design issues in CMOS differential LC oscillators. IEEE J. Solid State Circ. 1999, 34, 717–724. [Google Scholar] [CrossRef]

- Razavi, B. Design of Integrated Circuits for Optical Communications; McGraw-Hill: New York, NY, USA, 2003. [Google Scholar]

- Alioto, M.; Palumbo, G. Model and Design of Bipolar and MOS Current-Mode Logic: CML, ECL and SCL Digital Circuits; Springer Science & Business Media: Berlin/Heidelberg, Germany, 2006. [Google Scholar]

- Tiebout, M. A CMOS Direct Injection-Locked Oscillator Topology as High-Frequency Low-Power Frequency Divider. IEEE J. Solid State Circ. 2004, 39, 1170–1174. [Google Scholar] [CrossRef]

- Cheng, J.-H.; Tsai, J.-H.; Huang, T.-W. Design of a 90.9% Locking Range Injection-Locked Frequency Divider with Device Ratio Optimization in 90-nm CMOS. IEEE Trans. Microw. Theory Tech. 2016, 65, 187–197. [Google Scholar] [CrossRef]

| Parameter | Value | Parameter | Value |

|---|---|---|---|

| M1–M7 | 1 × 10 μm | Cdc, Cbypass | 880 fF |

| L1 | 380 pH | C1 | 160 fF |

| L2 | 460 pH | CN | 8.8 fF |

| Parameter | Value | Parameter | Value | Parameter | Value |

|---|---|---|---|---|---|

| M8, M9 | 2 × 20 μm | R3, R4 | 730 Ω | C3 | 203 fF |

| M10–M13 | 2 × 12 μm | R5, R7 | 68 Ω | Cbypass | 880 fF |

| M14, M15 | 2 × 30 μm | R6, R8 | 92 Ω | CIF | 5 pF |

| RG | 5 kΩ | LS | 240 pH | ||

| R1, R2 | 340 Ω | C2 | 139 fF |

| Parameter | Value | Parameter | Value |

|---|---|---|---|

| M16, M17 | 1.5 × 12 μm | L5, L6 | 250 pH |

| M18, M19 | 1.5 × 20 μm | L7, L8 | 195 pH |

| M20, M21 | 3 × 20 μm | Cbypass | 880 fF |

| RG | 5 kΩ | Cvar | 51.6–146 fF |

| R9, R10 | 100 Ω |

| Parameter | Value | Parameter | Value |

|---|---|---|---|

| M22, M23, M27, M28, M32, M33 | 3 × 13 μm | Lres | 290 pH |

| M24, M29, M34 | 2 × 24 μm | Lpeak | 120 pH |

| M25, M26, M30, M31, M35, M36 | 3 × 20 μm | Cbypass | 1.4 pF |

| RG | 5 kΩ | Cvar | 41–167 fF |

| R11–R16 | 80 Ω |

| Ref. | Process | RF Freq. (GHz) | Architecture | CG 1 (dB) | NF 2 (dB) | IP1dB (dBm) | IMRR (dBc) | Pdc (mW) |

|---|---|---|---|---|---|---|---|---|

| [6] | 65 nm CMOS | 22.5–26.1 | LNA + Mixer + AMPIF 3 + AMPLO 4 + PPFLO 5 | 31.5 | 4.8 | −35.2 | - | 127.44 |

| [9] | 0.12 μm SiGe | 10–40 | LNA + Mixer + VGAIF 6 + ×4 + AMPLO 4 | 39 | 6.8 | −33 | - | 130 |

| [10] | 0.13 μm SiGe | 25–45 | LNA + Mixer + ×3 + AMPLO 4 | 21 | 5 | - | 30 | - |

| [11] | 45 nm SOI CMOS | 24–44 | LNA + Mixer + AMPIF 3 + AMPLO 4 | 35.2 | 3.2 | −25.5 | 32 | 60 |

| [13] | 22 nm SOI CMOS | 20–44 | LNA + Mixer + AMPIF 3 + AMPLO 4 | 28.5 | 3.3 | −25 | 75 | 70 |

| [16] | 22 nm SOI CMOS | 19.5–42 | LN-VGA + mixer + LPF + AMPIF 3 + AMPLO 4 + IQGEN 7 | 25.3 | 2.7 | −23 | - | 102 |

| [17] | 65 nm CMOS | 26.5–32.5 | LNA + Mixer + BuffIF 8 + AMPLO 4 + PPFLO5 | 29.5 | 5.3 | −28 | - | 33 |

| This work | 65 nm CMOS | 41.5–45 | LNA + Mixer + VCO + 1/256 divider | 16.4 | 5.8 | −28 | 35.6 | 91.9 + 294 (divider chain) |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lee, H.; Jeon, S. A Q-Band CMOS Image-Rejection Receiver Integrated with LO and Frequency Dividers. Electronics 2023, 12, 3069. https://doi.org/10.3390/electronics12143069

Lee H, Jeon S. A Q-Band CMOS Image-Rejection Receiver Integrated with LO and Frequency Dividers. Electronics. 2023; 12(14):3069. https://doi.org/10.3390/electronics12143069

Chicago/Turabian StyleLee, Hyunkyu, and Sanggeun Jeon. 2023. "A Q-Band CMOS Image-Rejection Receiver Integrated with LO and Frequency Dividers" Electronics 12, no. 14: 3069. https://doi.org/10.3390/electronics12143069

APA StyleLee, H., & Jeon, S. (2023). A Q-Band CMOS Image-Rejection Receiver Integrated with LO and Frequency Dividers. Electronics, 12(14), 3069. https://doi.org/10.3390/electronics12143069