A Self-Triggered Digitally Assisted Hybrid LDO with 110 ns Settling Time in 65 nm CMOS

Abstract

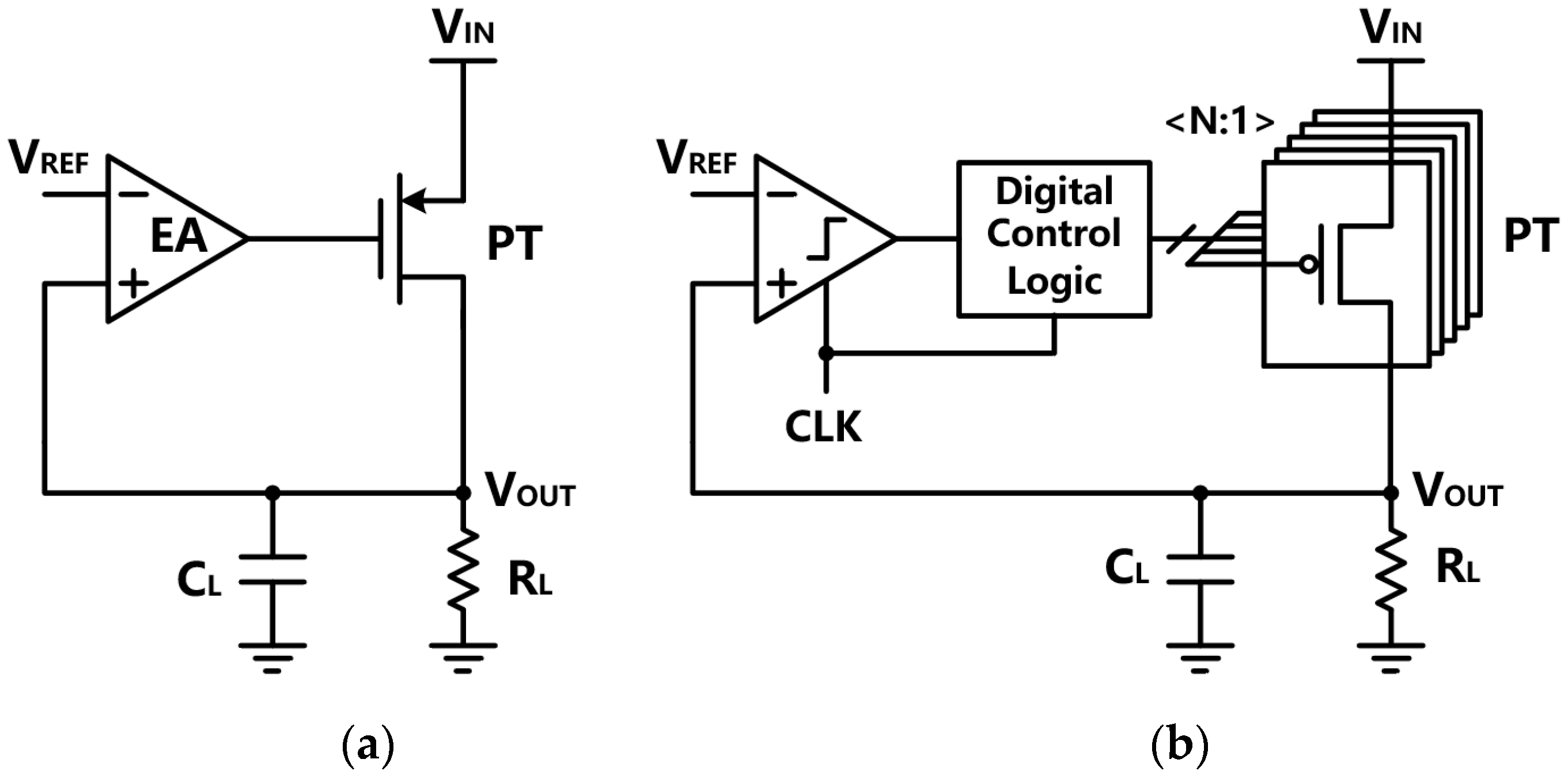

:1. Introduction

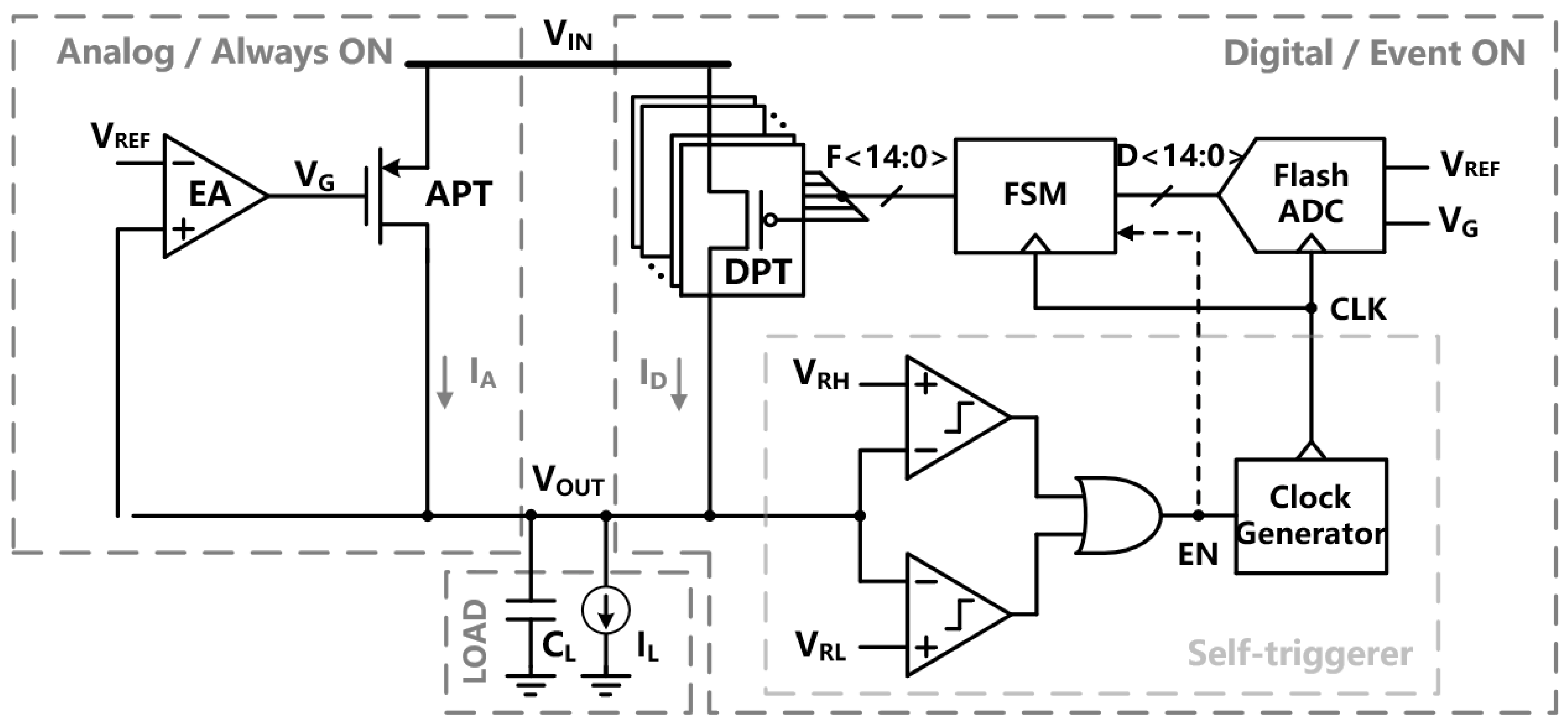

2. Proposed Architecture

2.1. Architecture of the DA-HLDO

2.2. Static and Dynamic Performance

2.3. Power Supply Rejection Ratio

3. Implementation of Core Circuit

3.1. Analog Error Amplifier

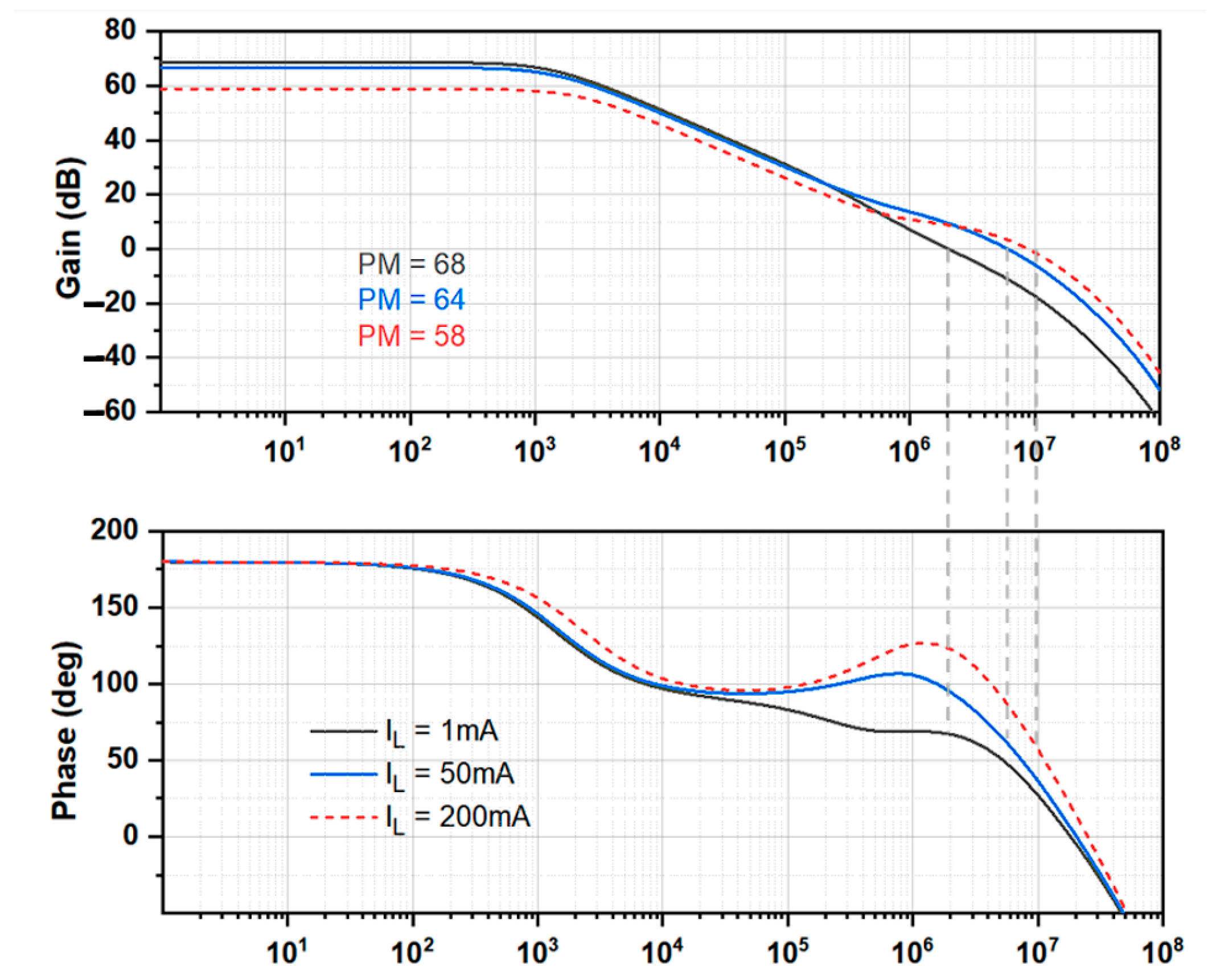

3.2. Stability Analysis

3.3. Event-Driven Comparator

3.4. Clock Generator

3.5. Flash ADC

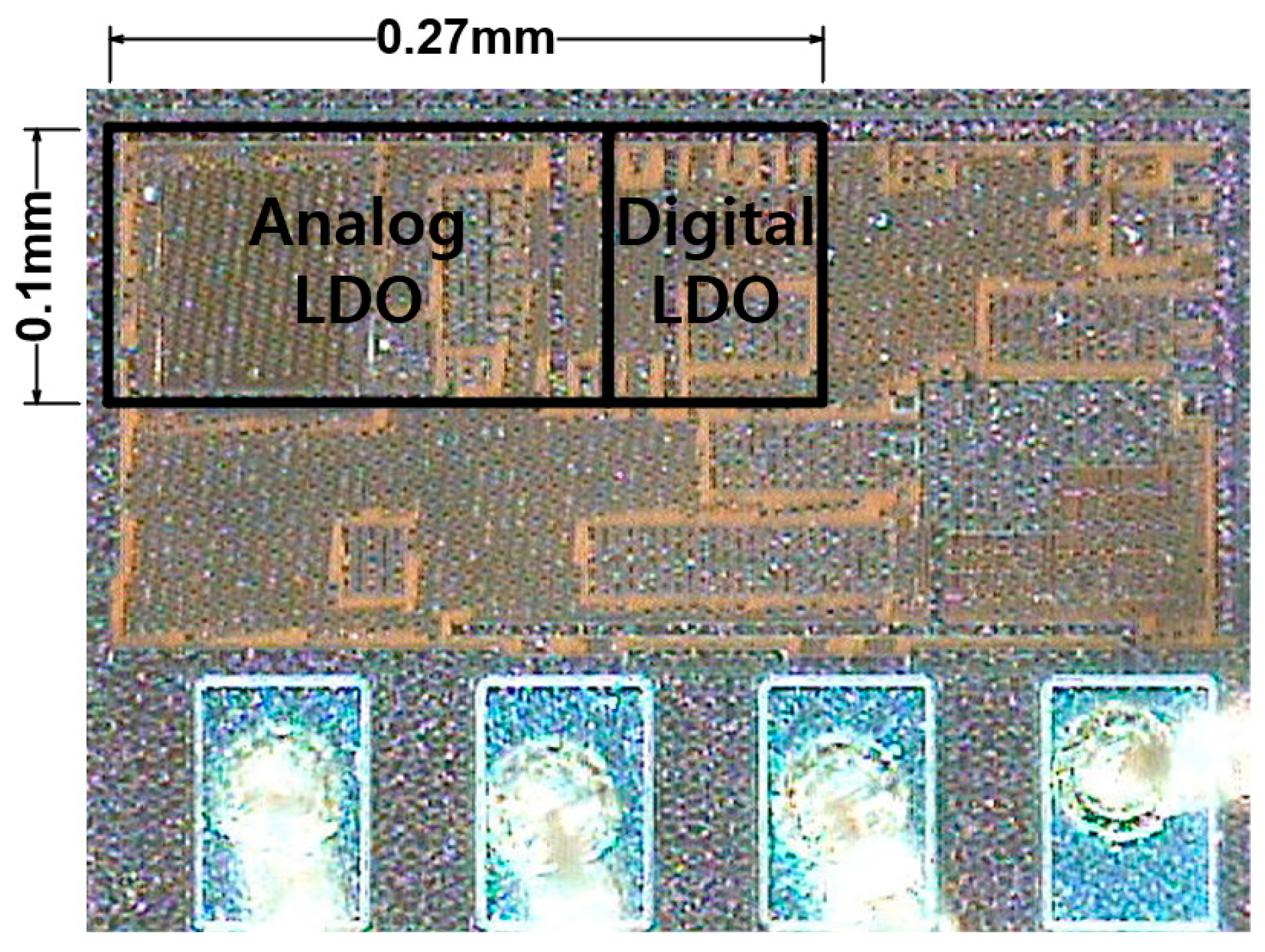

4. Measurement Results

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- MC13892 Data Sheet, (April 2014). NXP Semiconductors. Available online: http://www.nxp.com (accessed on 19 July 2020).

- Duong, Q. Multiple-Loop Design Technique for High-Performance Low-Dropout Regulator. IEEE J. Solid-State Circuits 2017, 52, 2533–2549. [Google Scholar]

- Hazucha, P.P.; Karnik, T.; Bloechel, B.A.; Parsons, C.; Finan, D.; Borkar, S. Area-efficient linear regulator with ultra-fast load regulation. IEEE J. Solid-State Circuits 2005, 40, 933–940. [Google Scholar]

- Milliken, R.J.; Silva-Martinez, J.; Sanchez-Sinencio, E. Full on-chip CMOS low-dropout voltage regulator. IEEE Trans. Circuits Syst. I Reg. Pap. 2007, 54, 1879–1890. [Google Scholar]

- Al-Shyoukh, M.; Lee, H.; Perez, R. A transient-enhanced low-quiescent current low-dropout regulator with buffer impedance attenuation. IEEE J. Solid-State Circuits 2007, 42, 1732–1742. [Google Scholar]

- Lau, S.K.; Mok, P.K.T.; Leung, K.N. A low-dropout regulator for SoC with Q-reduction. IEEE J. Solid-State Circuits 2007, 42, 658–664. [Google Scholar]

- Guo, J.; Leung, K.N. A 6-µ chip-area-efficient output-capacitorless LDO in 90-nm CMOS technology. IEEE J. Solid-State Circuits 2010, 45, 1896–1905. [Google Scholar]

- Or, P.Y.; Leung, K.N. An output-capacitorless low-dropout regulator with direct voltage-spike detection. IEEE J. Solid-State Circuits 2010, 45, 458–466. [Google Scholar]

- Kim, G.S.; Park, J.K.; Ko, G.H.; Baek, D. Capacitor-Less Low-Dropout (LDO) Regulator with 99.99% Current Efficiency Using Active Feedforward and Reverse Nested Miller Compensations. IEEE Access 2019, 7, 98630–98638. [Google Scholar]

- Okuma, Y. 0.5-V input DLDO with 98.7% current efficiency and 2.7-quiescent current in 65 nm CMOS. In Proceedings of the IEEE Custom Integrated Circuits Conference 2010, San Jose, CA, USA, 19–22 September 2010. [Google Scholar]

- Lee, Y.H. A low quiescent current asynchronous digital-LDO with PLL-modulated fast-DVS power management in 40 nm SoC for MIPS performance improvement. IEEE J. Solid-State Circuits 2013, 48, 1018–1030. [Google Scholar]

- Gangopadhyay, S.; Somasekhar, D.; Tschanz, J.W.; Raychowdhury, A. A 32 nm embedded fully-digital phase-locked low dropout regulator for fine grained power management in digital circuits. IEEE J. Solid-State Circuits 2014, 49, 2684–2693. [Google Scholar]

- Nasir, S.B.; Gangopadhyay, S.; Raychowdhury, A. 5.6 A 0.13 μm fully digital low-dropout regulator with adaptive control and reduced dynamic stability for ultra-wide dynamic range. In Proceedings of the 2015 IEEE International Solid-State Circuits Conference—(ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 22–26 February 2015; pp. 98–99. [Google Scholar]

- Salem, L.G.; Warchall, J.; Mercier, P.P. 20.3 A 100 nA-to-2 mA successive-approximation digital LDO with PD compensation and sub-LSB duty control achieving a 15.1 ns response time at 0.5 V. In Proceedings of the 2017 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 5–9 February 2017; pp. 340–341. [Google Scholar]

- Huang, M.; Lu, Y.; Sin, S.W.; Seng-Pan, U.; Martins, R.P. A fully integrated DLDO with coarse-fine-tuning and burst-mode operation. IEEE Trans. Circuits Syst. II Exp. Briefs 2016, 63, 683–687. [Google Scholar]

- Yang, F.; Mok, P.K.T. A nanosecond-transient fine-grained DLDO with multi-step switching scheme and asynchronous adaptive pipeline control. IEEE J. Solid-State Circuits 2017, 52, 2463–2474. [Google Scholar]

- Lee, Y.J. A 200-mA digital low drop-out regulator with coarse-fine dual loop in mobile application processor. IEEE J. Solid-State Circuits 2017, 52, 64–76. [Google Scholar]

- Kim, D.; Seok, M. A fully integrated digital low-dropout regulator based on event-driven explicit time-coding architecture. IEEE J. Solid-State Circuits 2017, 52, 3071–3080. [Google Scholar]

- Chen, W.C.; Ping, S.Y.; Huang, T.C.; Lee, Y.H.; Chen, K.H.; Wey, C.L. A switchable digital-analog low-dropout regulator for analog dynamic voltage scaling technique. IEEE J. Solid-State Circuits 2014, 49, 740–750. [Google Scholar]

- Nasir, S.B.; Raychowdhury, A. Embedded hybrid LDO topologies for digital load circuits. In Proceedings of the 2016 IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), Jeju, Republic of Korea, 25–28 October 2016; pp. 43–46. [Google Scholar]

- Cheah, M.; Mandal, D.; Bakkaloglu, B.; Kiaei, S. A 100-mA 99.11% current efficiency 2-mVpp ripple digitally controlled LDO with active ripple suppression. IEEE Trans. Very Large Scale Integr. Syst. 2017, 25, 696–704. [Google Scholar]

- Huang, M.; Lu, Y.; Seng-Pan, U.; Martins, R.P. An analog-assisted tri-loop digital low-dropout regulator. IEEE J. Solid-State Circuits 2018, 53, 20–34. [Google Scholar]

- Park, J.E.; Jeong, D.K. A fully integrated 700 mA event-driven digital low-dropout regulator with residue-tracking loop for fine-grained power management unit. In Proceedings of the 2018 IEEE Symposium on VLSI Circuits, Honolulu, HI, USA, 18–22 June 2018; pp. 231–232. [Google Scholar]

- Lu, Y.; Yang, F.; Chen, F.; Mok, P.K.T. A 500 mA analog-assisted digital-LDO-based on-chip distributed power delivery grid with cooperative regulation and IR-drop reduction in 65 nm CMOS. In Proceedings of the 2018 IEEE International Solid-State Circuits Conference—(ISSCC), San Francisco, CA, USA, 11–15 February 2018; pp. 310–312. [Google Scholar]

- Lu, Y.; Yang, F.; Chen, F.; Mok, P.K.T. A distributed power delivery grid based on analog-assisted DLDOs with cooperative regulation and IR-drop reduction. IEEE Trans. Circuits Syst. I Reg. Pap. 2020, 67, 2859–2871. [Google Scholar]

- Liu, X.; Krishnamurthy, H.K.; Na, T.; Weng, S.; Ahmed, K.Z.; Ravichandran, K.; Tschanz, J.; De, V. 14.7 A modular hybrid LDO with fast load-transient response and programmable PSRR in 14 nm CMOS featuring dynamic clamp tuning and time-constant compensation. In Proceedings of the 2019 IEEE International Solid-State Circuits Conference-(ISSCC), San Francisco, CA, USA, 17–21 February 2019; pp. 234–236. [Google Scholar]

- Zhou, D.; Jiang, J.; Liu, Q.; Soenen, E.G.; Kinyua, M.; Martinez, J.S. A 245-mA digitally assisted dual-loop low-dropout regulator. IEEE J. Solid-State Circuits 2020, 55, 2140–2150. [Google Scholar]

- Jung, J.H.; Hong, S.K.; Kwon, O.K. A fast transient response hybrid LDO with highly accurate DC voltage using countable bidirectional binary search and soft swap switching. IEEE Trans. Circuits Syst. II Exp. Briefs 2020, 67, 3272–3276. [Google Scholar]

- Kwok, K.C.; Mok, P.K.T. Pole-zero tracking frequency compensation for low dropout regulator. In Proceedings of the 2002 IEEE International Symposium on Circuits and Systems (ISCAS), Phoenix-Scottsdale, AZ, USA, 26–29 May 2002; p. 4. [Google Scholar]

- Briseno-Vidrios, C. A 44-fJ/Conversion step 200-MS/s pipeline ADC employing current-mode MDACs. IEEE J. Solid-State Circuits 2018, 53, 3280–3292. [Google Scholar]

- Huang, M. 20.4 An output-capacitor-free analog-assisted digital low-dropout regulator with tri-loop control. In Proceedings of the 2017 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 5–9 February 2017; pp. 342–343. [Google Scholar]

- Magod, R.; Bakkaloglu, B.; Manandhar, S. A 1.24 μA Quiescent Current NMOS Low Dropout Regulator with Integrated Low Power Oscillator-Driven Charge-Pump and Switched-Capacitor Pole Tracking Compensation. IEEE J. Solid-State Circuits 2018, 53, 2356–2367. [Google Scholar]

- Nasir, S.B.; Sen, S.; Raychowdhury, A. Switched-Mode-Control based hybrid LDO for fine-grain power management of digital load circuits. IEEE J. Solid-State Circuits 2018, 53, 569–581. [Google Scholar]

| Analog LDO | Digital LDO | |

|---|---|---|

| Quantization Error | NO | Yes |

| Dropout Voltage | High | Low |

| Area Efficiency | Low | High |

| Settling Time | Slow | Fast |

| PSRR | Good | Poor |

| Output Ripple | No | Yes |

| Publication | [13] | [16] | [24] | [32] | [33] | [27] | This Work |

| ISSCC’15 | JSSC’18 | JSSC’17 | JSSC’18 | JSSC’18 | JSSC’20 | ||

| Process [nm] | 130 | 65 | 130 | 250 | 130 | 40 | 65 |

| Architecture | Digital | Digital | Analog | Analog | Hybrid | Hybrid | Hybrid |

| Active Area [mm2] | 0.355 | 0.158 | 0.1825 | 0.108 | 0.0818 | 0.056 | 0.027 |

| VIN (V) | 0.5–1.2 | 0.6–1.0 | 1.05–2.0 | 1.5–3.3 | 1.1–1.2 | 1.25–1.4 | 1.1–1.2 |

| VOUT (V) | 0.45–1.14 | 0.55–0.95 | 2 | 1.0–3.0 | 0.8–1.1 | 1.1–1.25 | 0.9–1.0 |

| IL, MAX [mA] | 4.6 | 500 | 300 | 150 | 12 | 245 | 200 |

| CL [nF] | 1 | 1.5 | 1000 | 1000 | 0.5 | 20 | 8 |

| IQ [μA] | 24–221 | 300 | 14-120 | 100 | 163.2 | 300 | 200 |

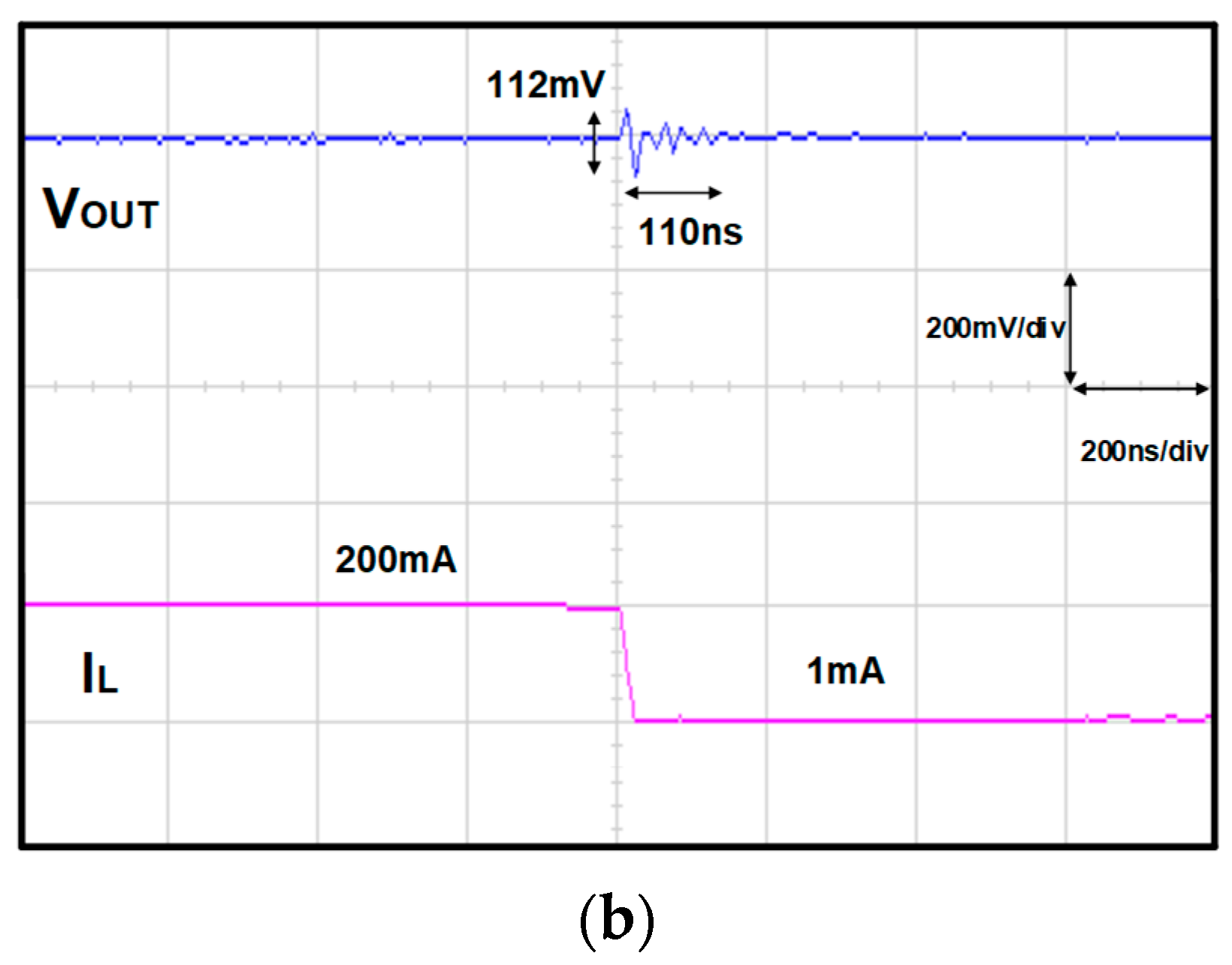

| ΔVout [mV] @ΔIL [mA] | <40 @0.7 | 50 @100 | 56 @300 | 160 @150 | 240 @10 | 71 @240 | 112 @200 |

| Ts [us] | 1.1 | 0.025 | 0.25 | 200 | 0.052 | 0.52 | 0.11 |

| PSR [dB] @ 1 MHz for Max Load | N/A | N/A | −12 | −36 | N/A | −43 | −40 |

| FoM [ps] * | >45 | 2.3 | 12.44 | 7.4 | 166 | 7.4 | 4.48 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jin, Z.; Kim, G.; Baek, D. A Self-Triggered Digitally Assisted Hybrid LDO with 110 ns Settling Time in 65 nm CMOS. Electronics 2023, 12, 3215. https://doi.org/10.3390/electronics12153215

Jin Z, Kim G, Baek D. A Self-Triggered Digitally Assisted Hybrid LDO with 110 ns Settling Time in 65 nm CMOS. Electronics. 2023; 12(15):3215. https://doi.org/10.3390/electronics12153215

Chicago/Turabian StyleJin, Zhenbo, Gwangsub Kim, and Donghyun Baek. 2023. "A Self-Triggered Digitally Assisted Hybrid LDO with 110 ns Settling Time in 65 nm CMOS" Electronics 12, no. 15: 3215. https://doi.org/10.3390/electronics12153215

APA StyleJin, Z., Kim, G., & Baek, D. (2023). A Self-Triggered Digitally Assisted Hybrid LDO with 110 ns Settling Time in 65 nm CMOS. Electronics, 12(15), 3215. https://doi.org/10.3390/electronics12153215