An Input Up to 100-V High Voltage LDO Based a Novel Pre-Regulation and a Simple Clamp Current Circuit

Abstract

:1. Introduction

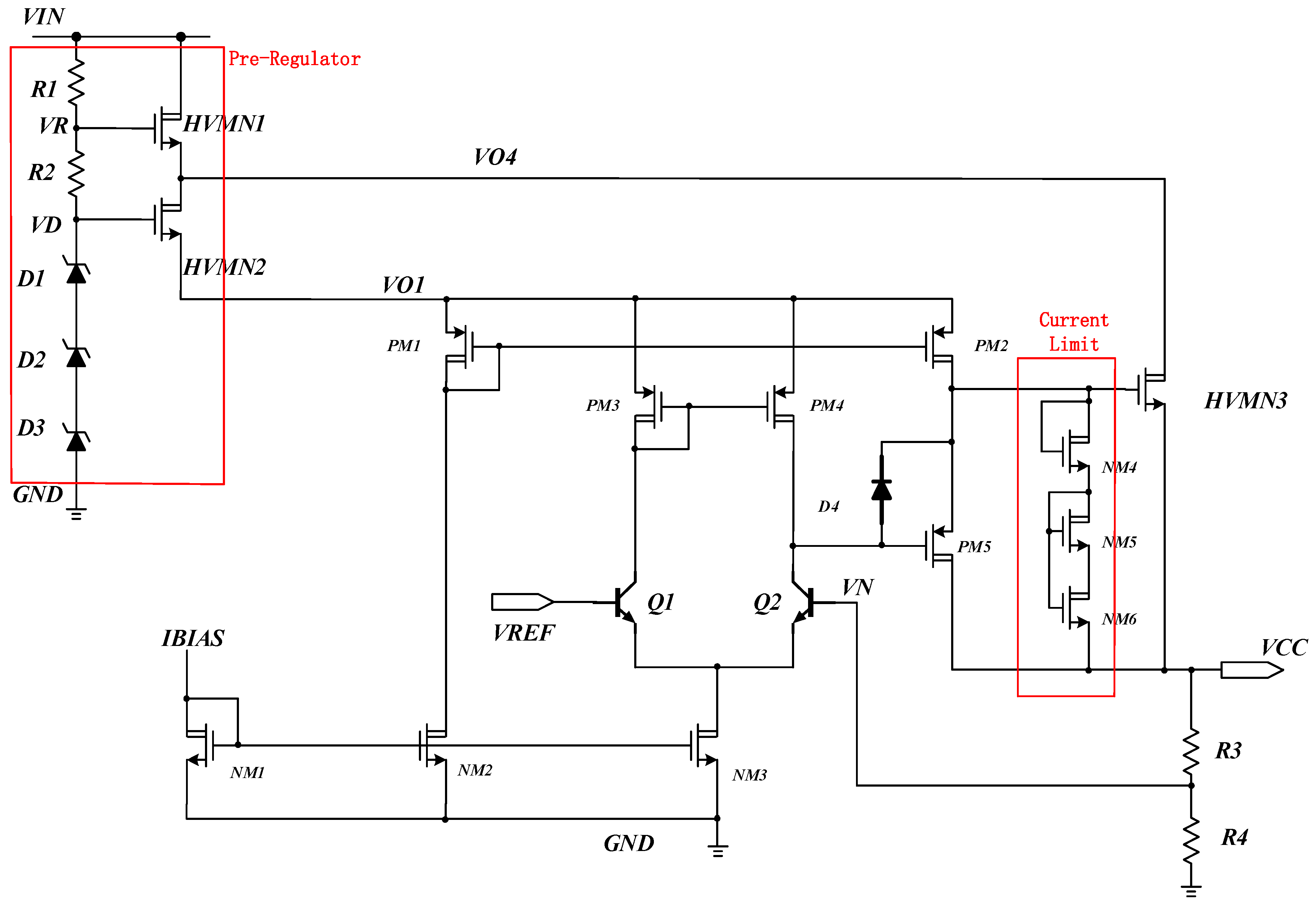

2. Designed High Voltage LDO Structure

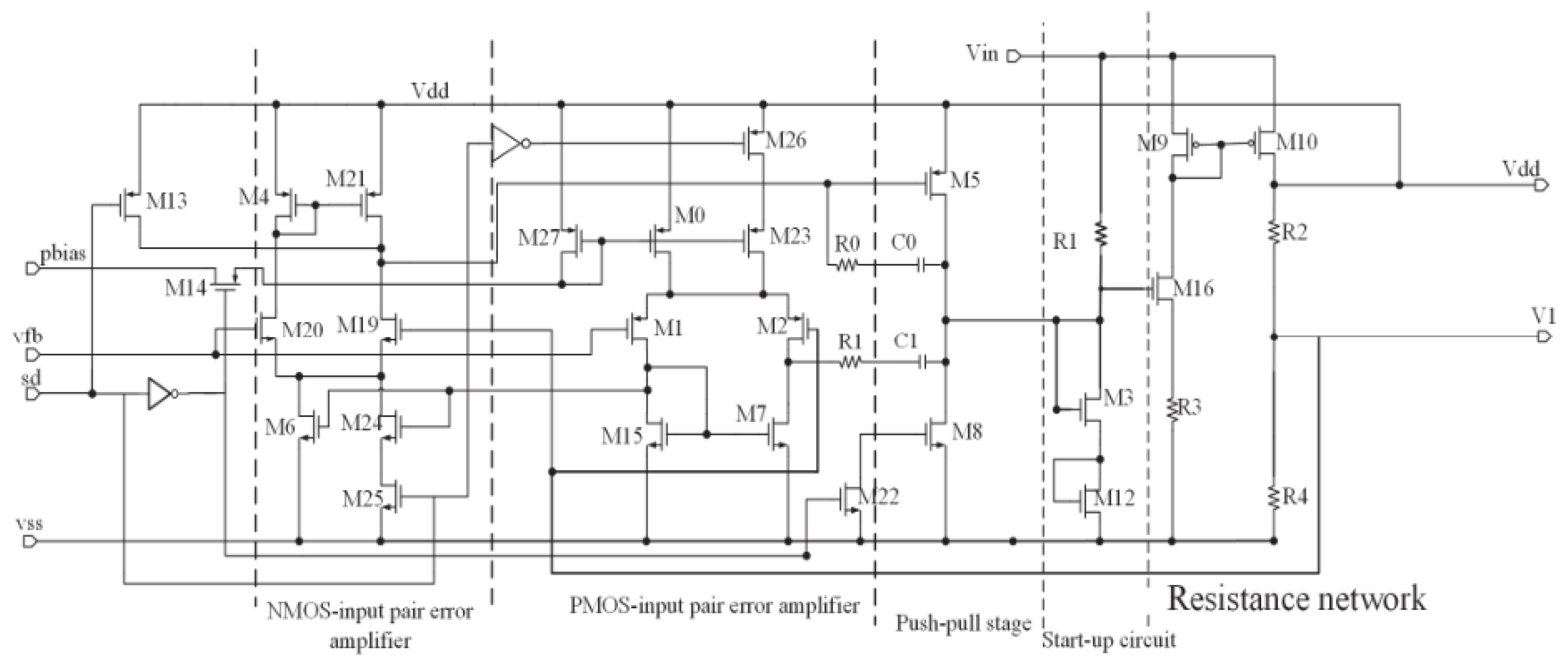

2.1. Pre-Regulator and Error Amplifier

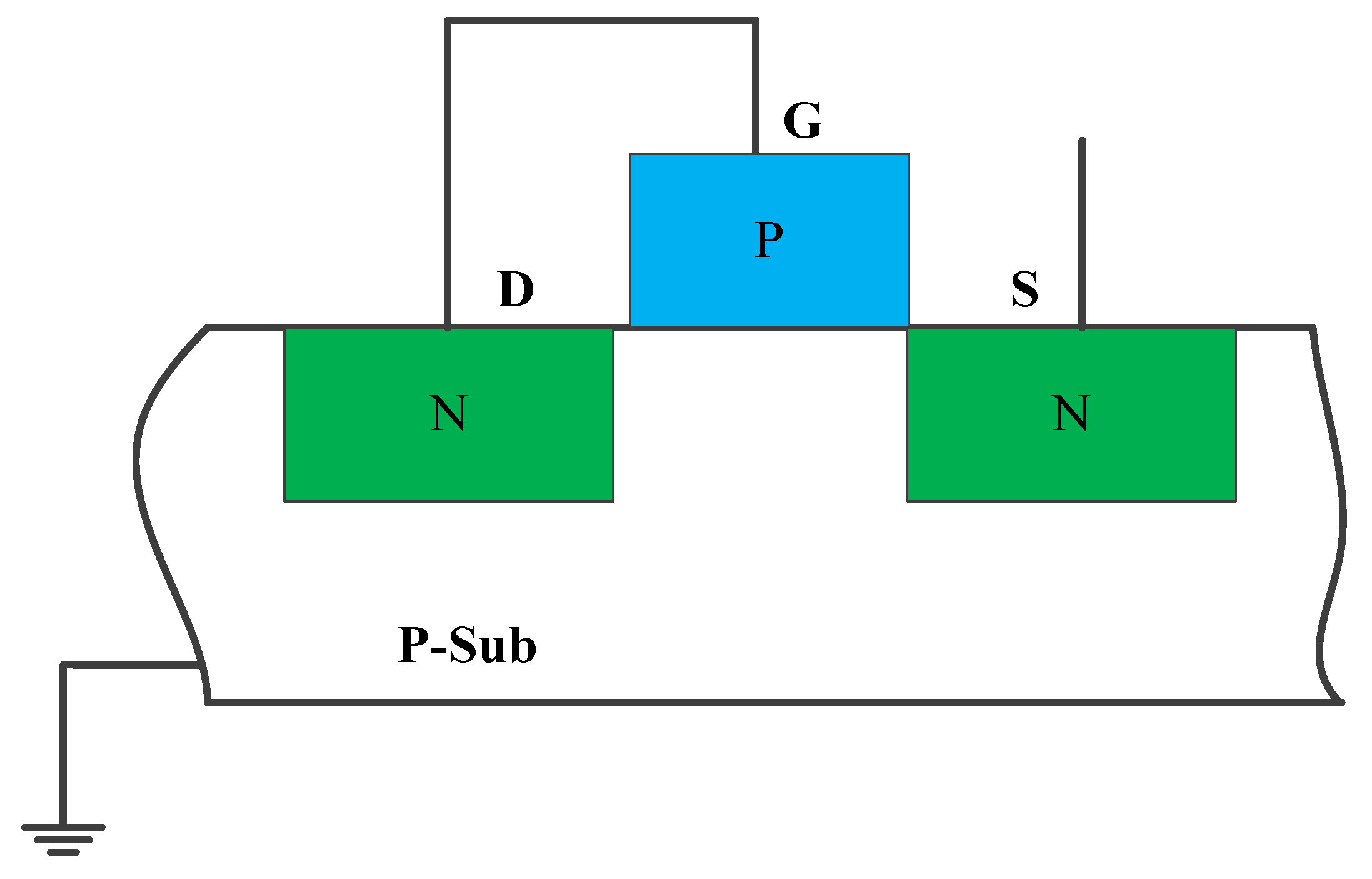

2.2. Power Transistors

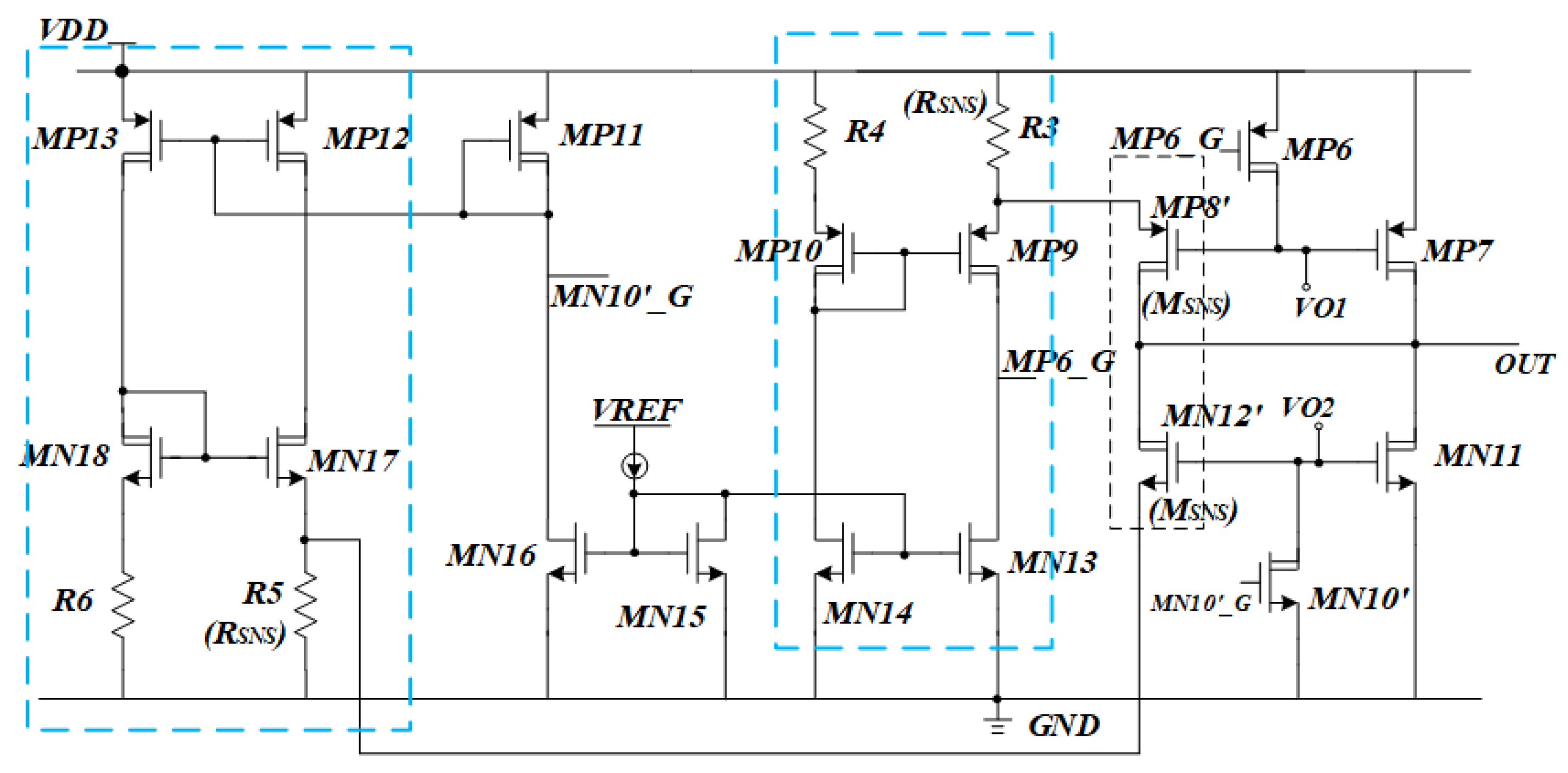

2.3. Current Limiting Technique

3. Simulation and Measurement Results

3.1. Simulation Result and Analysis

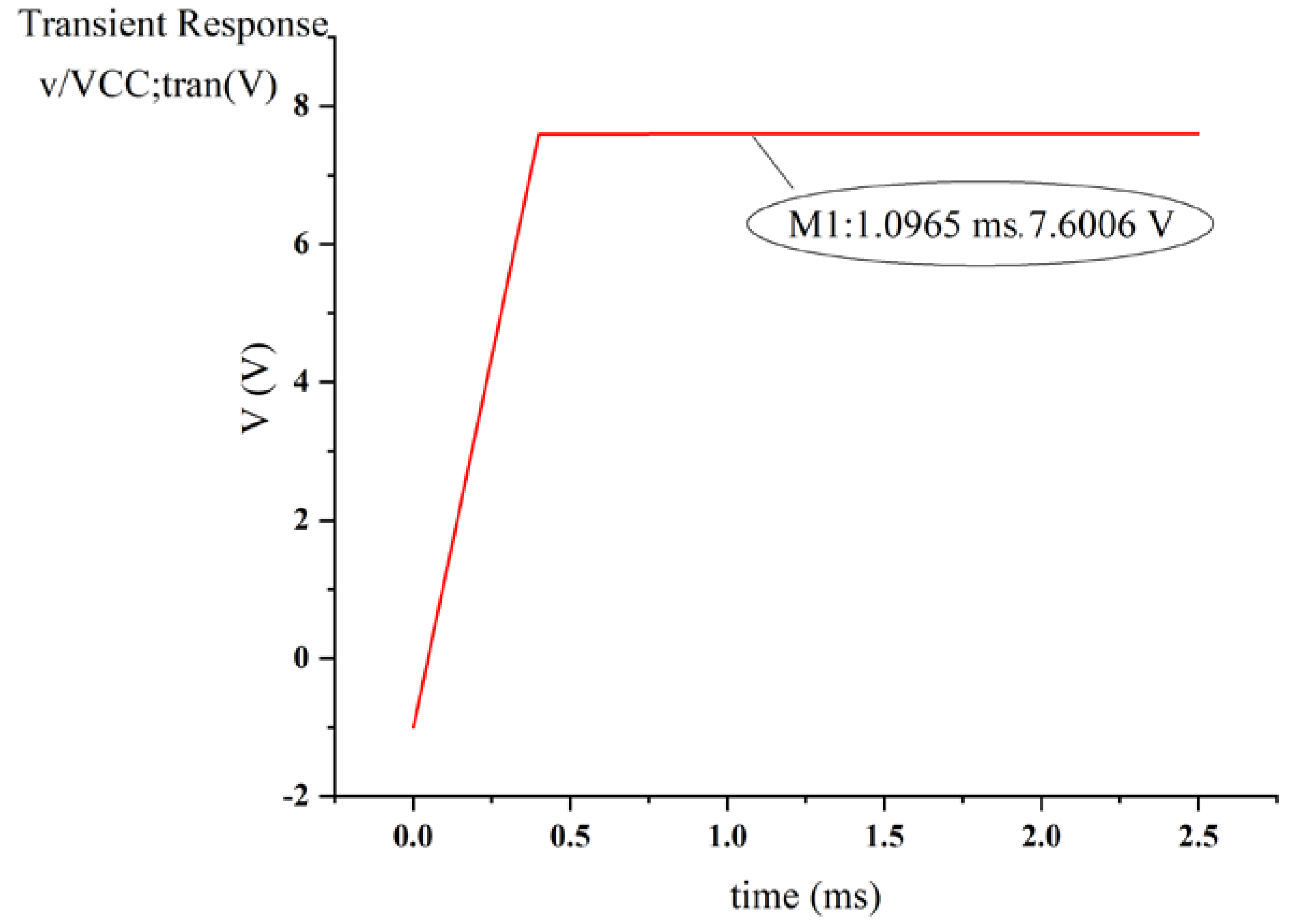

3.1.1. Startup Simulation

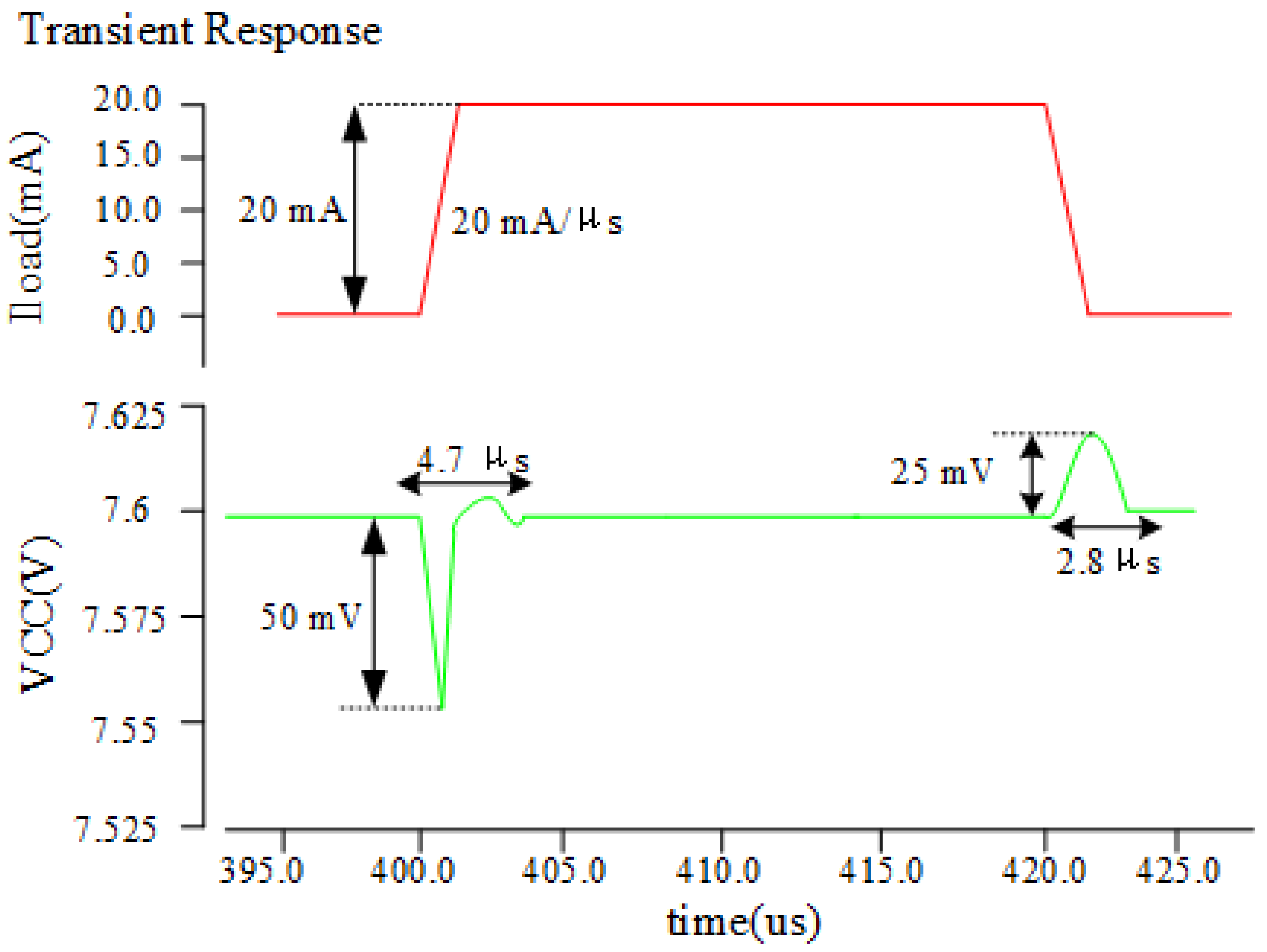

3.1.2. Transient Response

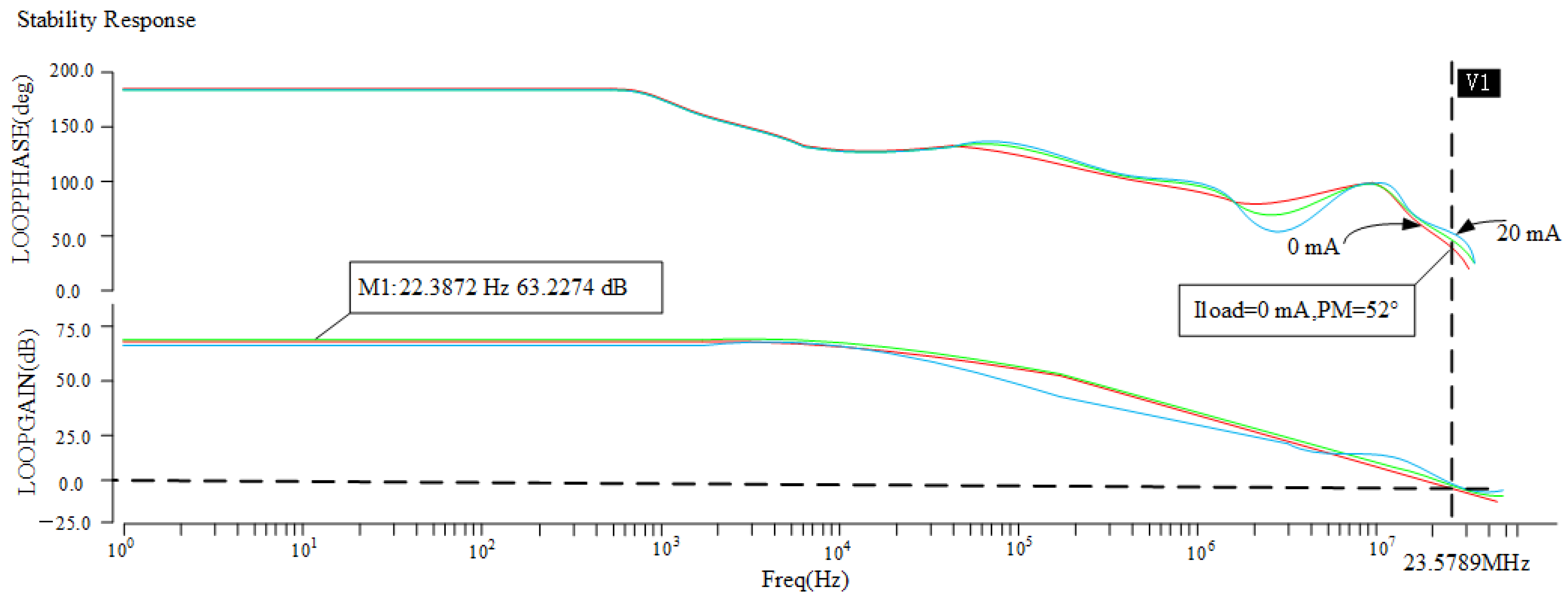

3.1.3. Loop Stability

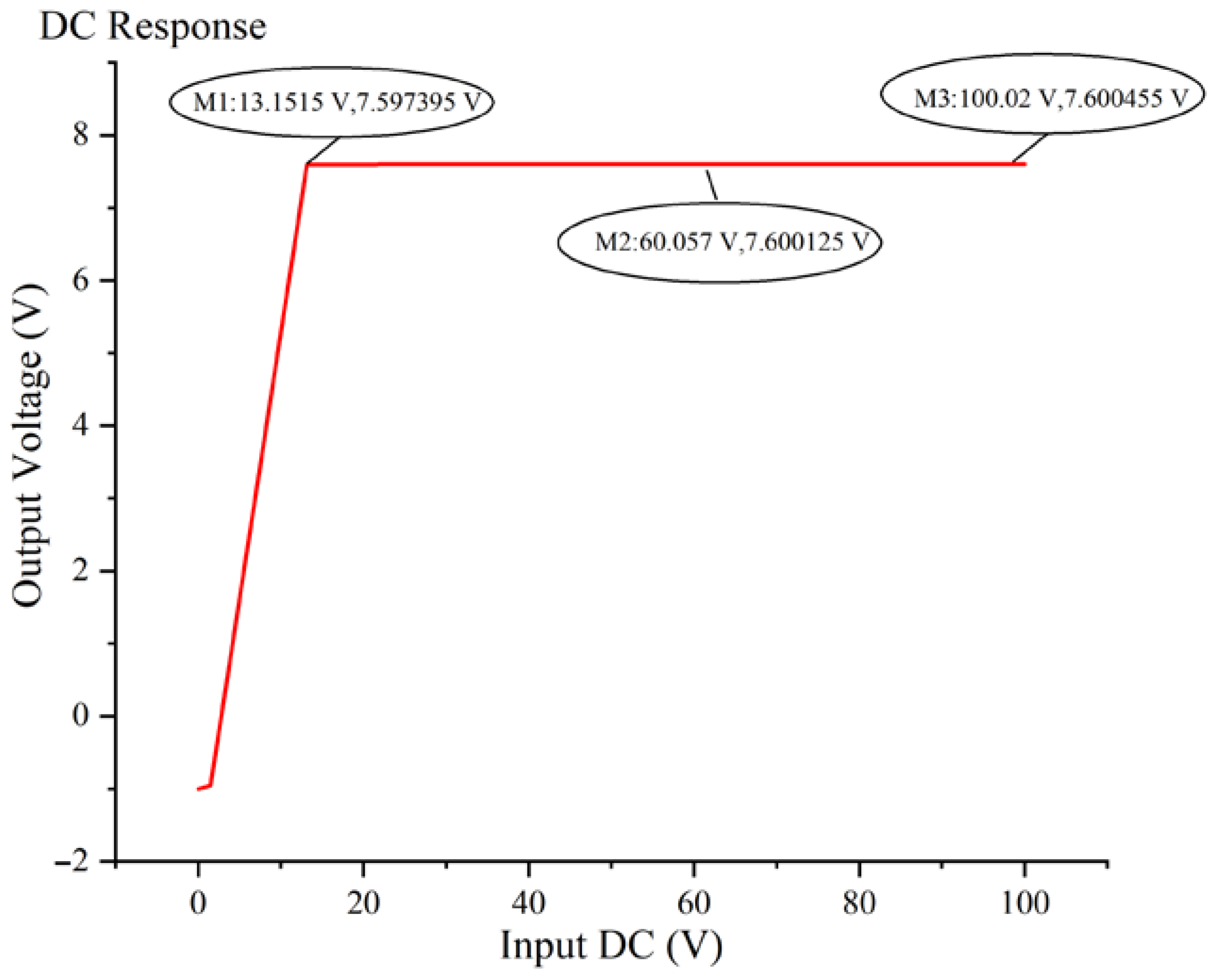

3.1.4. Line Regulation

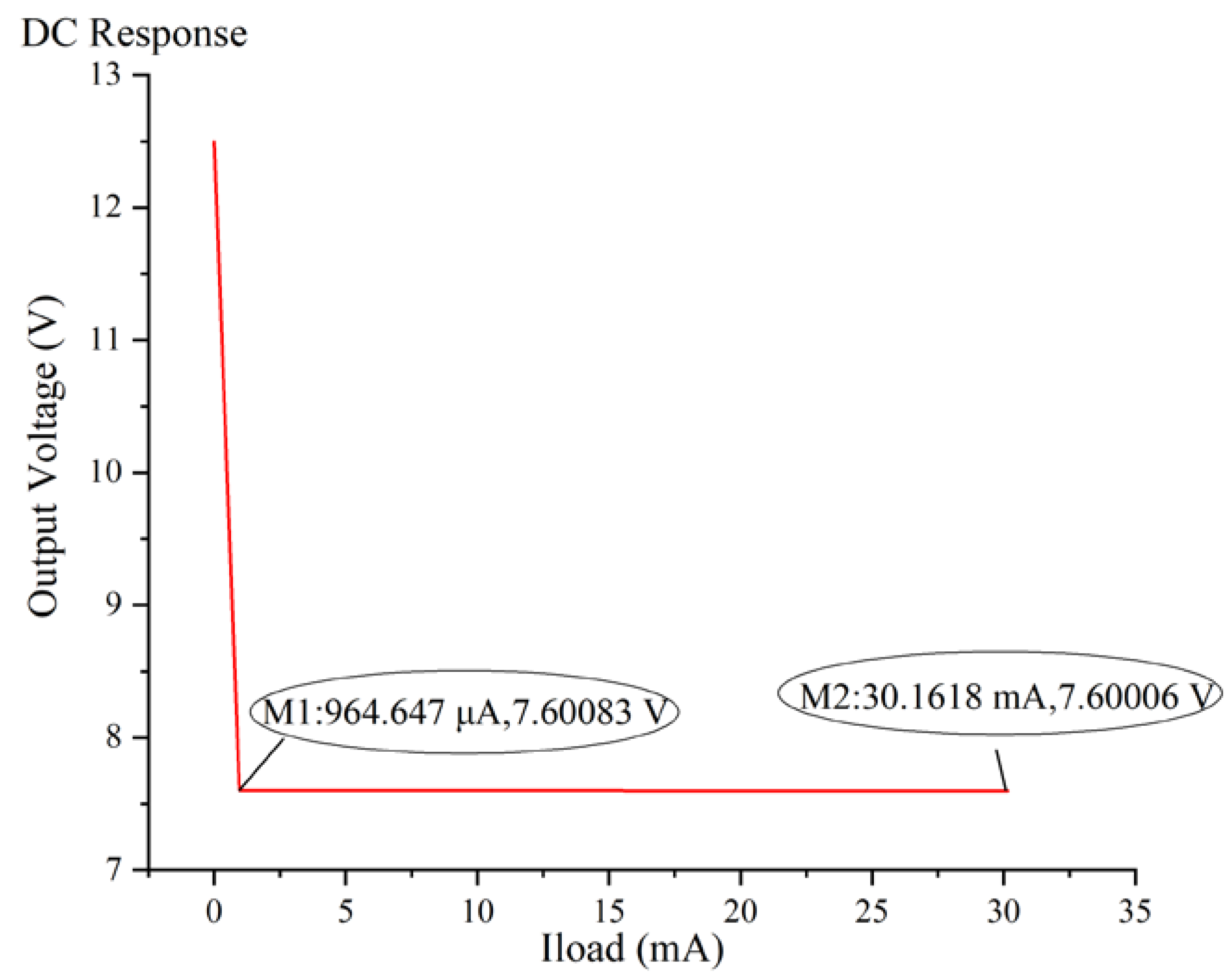

3.1.5. Load Regulation

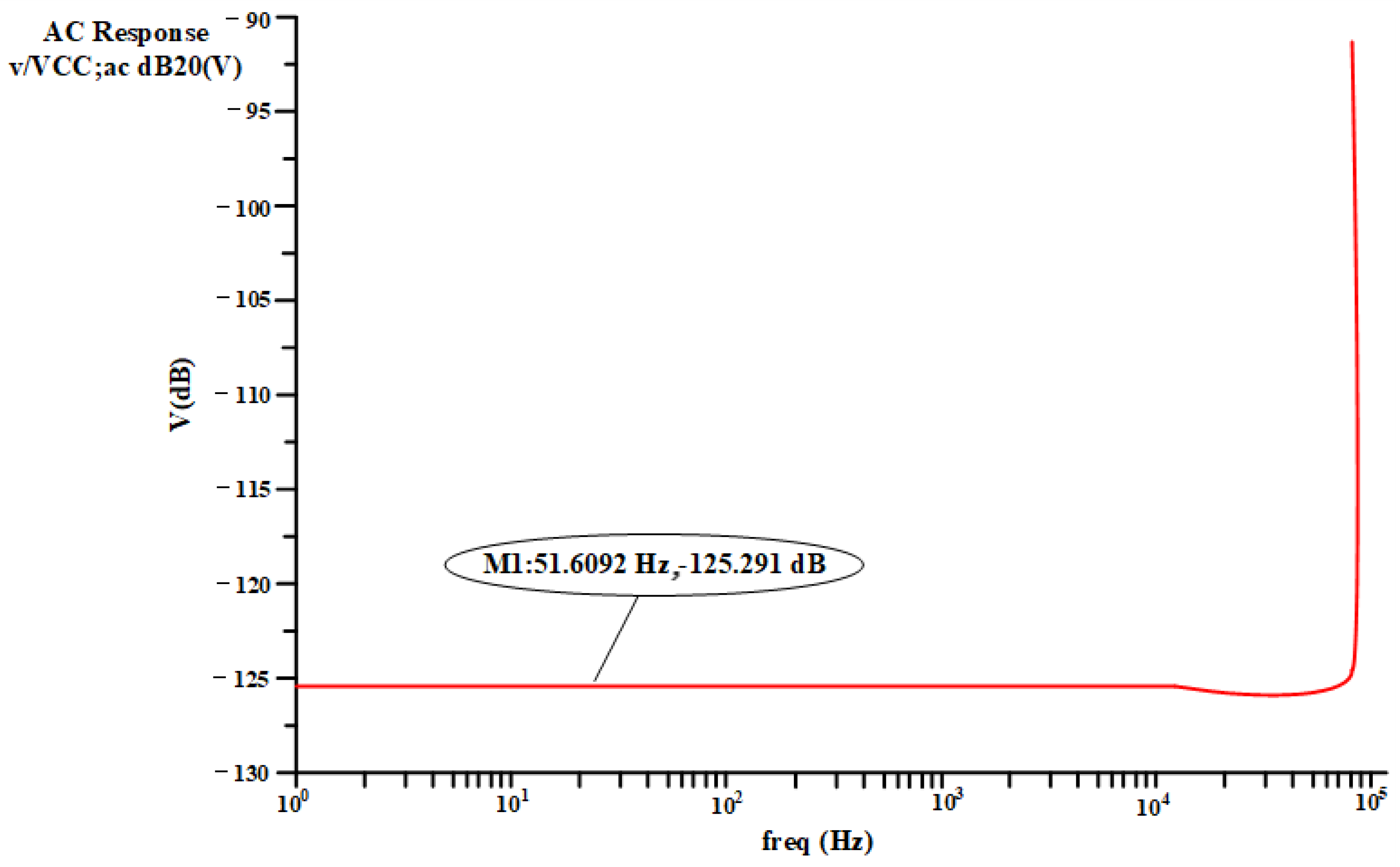

3.1.6. PSRR (Power Supply Ripple Rejection)

3.1.7. Current Limit

3.2. Measurement Results

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Ren, Y.; Huang, S.; Duan, Q.; Ding, Y.; Li, M. A 1500 mA load current LDO with wide power supply range in lithium-ion battery. In Proceedings of the 2018 13th IEEE Conference on Industrial Electronics and Applications (ICIEA), Wuhan, China, 31 May–2 June 2018; pp. 2141–2144. [Google Scholar] [CrossRef]

- Yin, J.; Huang, S.; Duan, Q.; Cheng, Y. An 800 mA load current LDO with wide input voltage range. In Proceedings of the 2017 International Conference on Circuits, Devices and Systems (ICCDS), Chengdu, China, 5–8 September 2017; pp. 174–178. [Google Scholar] [CrossRef]

- Ryzhkov, V.A.; Karpovich, M.S.; Surin, I.K.; Vasilyev, V.Y. High-voltage low drop output voltage regulator with output current fold-back protection in 250 nm BCD technology. In Proceedings of the 2016 17th International Conference of Young Specialists on Micro/Nanotechnologies and Electron Devices (EDM), Erlagol, Russia, 30 June–4 July 2016; pp. 549–554. [Google Scholar] [CrossRef]

- Wang, Y.; Ding, L.; Bao, Z.; Yang, H.; Jin, X. High current operational amplifier with current limiting protection circuit. IET Circuits Devices Syst. 2020, 14, 251–259. [Google Scholar] [CrossRef]

- Guo, J.; Leung, K.N. A fold-back current-limit circuit with load-insensitive quiescent current for CMOS low dropout regulator. In Proceedings of the 2009 IEEE International Symposium on Circuits and Systems (ISCAS), Taipei, Taiwan, 24–27 May 2009; pp. 2417–2420. [Google Scholar] [CrossRef]

- Matyscak, J.; Radhostem, R.P. Output Current Limiter for a Linear Regulator. US Patent US 2021/0018944 A1, 21 January 2021. [Google Scholar]

- Zhang, N.; Gu, J. LDO Circuit Device and Overcurrent Protection Circuit of LDO Circuit. US Patent US 2020/0333816 A1, 22 October 2020. [Google Scholar]

- Xiao, B.; Venkatachala, P.K.; Xu, Y.; ElShater, A.; Lee, C.Y.; Leuenberger, S.; Moon, U.K. An 80 mA capacitor-less LDO with 6.5 μA quiescent current and no frequency compensation using adaptive-deadzone ring amplifier. In Proceedings of the IEEE Asian Solid-State Circuits Conference, Macao SAR, China, 4–6 November 2019. [Google Scholar]

- Sakolski, O.; Poongodan, P.K.; Vanselow, F.; Maurer, L. A feedforward compensated high-voltage linear regulator with fast response, high-current sinking capability. IEEE Solid-State Circuits Lett. 2020, 3, 114–117. [Google Scholar] [CrossRef]

- Hu, D.; Zhang, G.; Tong, M.S. A new design for low drop-out regulator with broadband high power supply rejection. In Proceedings of the 2020 IEEE International Conference on Computational Electromagnetics (ICCEM), Singapore, 24–26 August 2020; pp. 281–282. [Google Scholar] [CrossRef]

- Lavalle-Aviles, F.; Torres, J.; Sánchez-Sinencio, E. A high power supply rejection and fast settling time capacitor-less LDO. IEEE Trans. Power Electron. 2019, 34, 474–484. [Google Scholar] [CrossRef]

- Tang, J.; Dai, C.; Ouyang, L.; Wang, Y.; Zou, W. A design of high voltage pre-regulator circuit for LED driver. In Proceedings of the 2021 9th International Symposium on Next Generation Electronics (ISNE), Changsha, China, 9–11 July 2021; pp. 1–4. [Google Scholar] [CrossRef]

- Ho, M.; Guo, J.; Mak, K.H.; Goh, W.L.; Bu, S.; Zheng, Y.; Tang, X.; Leung, K.N. A CMOS low-dropout regulator with dominant-pole substitution. IEEE Trans. Power Electron. 2016, 31, 6362–6371. [Google Scholar] [CrossRef]

- Adorni, N.; Stanzione, S.; Boni, A. A 10-mA LDO with 16-nA IQ and operating from 800-mV supply. IEEE J. Solid-State Circuits 2020, 55, 404–413. [Google Scholar] [CrossRef]

- Fan, S.; Li, H.; Guo, Z.; Geng, L. A 5.2 μA quiescent current LDO regulator with high stability and wide load range for CZT detectors. IEEE Trans. Nucl. Sci. 2017, 64, 1087–1094. [Google Scholar] [CrossRef]

| Parameters | Value | ||||||

|---|---|---|---|---|---|---|---|

| Load current (mA) | 0 | 15 | 16 | 17 | 18 | 19 | 20 |

| Output voltage (V) | 7.701 | 7.701 | 7.64 | 6.78 | 6.73 | 0.7 | −0.05 |

| Parameters | Value | ||||||

|---|---|---|---|---|---|---|---|

| VIN (V) | 20 | 25 | 30 | 35 | 40 | 45 | 50 |

| VCC (V) | 7.6520 | 7.6516 | 7.6511 | 7.6513 | 7.6508 | 7.6509 | 7.6508 |

| VIN (V) | 55 | 60 | 65 | 70 | 75 | 80 | 85 |

| VCC (V) | 7.6506 | 7.6504 | 7.6505 | 7.6502 | 7.6501 | 7.6500 | 7.6500 |

| Parameters | Value | ||

|---|---|---|---|

| VIN (V) | 130 | 135 | 140 |

| VCC (V) | 7.6738 | 7.6737 | 7.6754 |

| Parameter | Unit | This Work | [3] | [12] | [13] | [14] | [15] | |

|---|---|---|---|---|---|---|---|---|

| Sim | Test | |||||||

| Technology | nm | 180 | - | 180 | 55 | 180 | 400 | 250 |

| Area | mm2 | 0.2178 | - | 0.15 | 0.042 | 0.216 | No | 1.42 |

| Max. load | mA | 30 | 19 | No | 10 | 150 | 1500 | 800 |

| Supply voltage | V | 13–100 | 140 | 70 | 0.8 | 2.9–3.3 | 3.9–20 | 3.9–20 |

| Output voltage | V | 7.6 | 7.6508 | 66 | 0.6 | 2.8 | 2.5 | 2.5 |

| PM | ° | 52 | - | No | No | 62.1 | No | No |

| Line regulation | mV/V | 0.035 | 0.0226 | 90 (no load) | 0.5 | 1.25 | No | 0.5093 |

| Load regulation | mV/mA | 0.0256 | 0.0003 | 1.7 | 1.05 | 0.25 | 0.0013 | 0.0458 |

| PSRR (@1 kHz) | dB | −125 | - | No | 42.7 | <−50 | No | No |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Li, L.; Lai, X.; Jin, D.; Shi, L.; Xu, S. An Input Up to 100-V High Voltage LDO Based a Novel Pre-Regulation and a Simple Clamp Current Circuit. Electronics 2023, 12, 3257. https://doi.org/10.3390/electronics12153257

Li L, Lai X, Jin D, Shi L, Xu S. An Input Up to 100-V High Voltage LDO Based a Novel Pre-Regulation and a Simple Clamp Current Circuit. Electronics. 2023; 12(15):3257. https://doi.org/10.3390/electronics12153257

Chicago/Turabian StyleLi, Linxi, Xinquan Lai, Dinghai Jin, Lingfeng Shi, and Siting Xu. 2023. "An Input Up to 100-V High Voltage LDO Based a Novel Pre-Regulation and a Simple Clamp Current Circuit" Electronics 12, no. 15: 3257. https://doi.org/10.3390/electronics12153257