Figure 1.

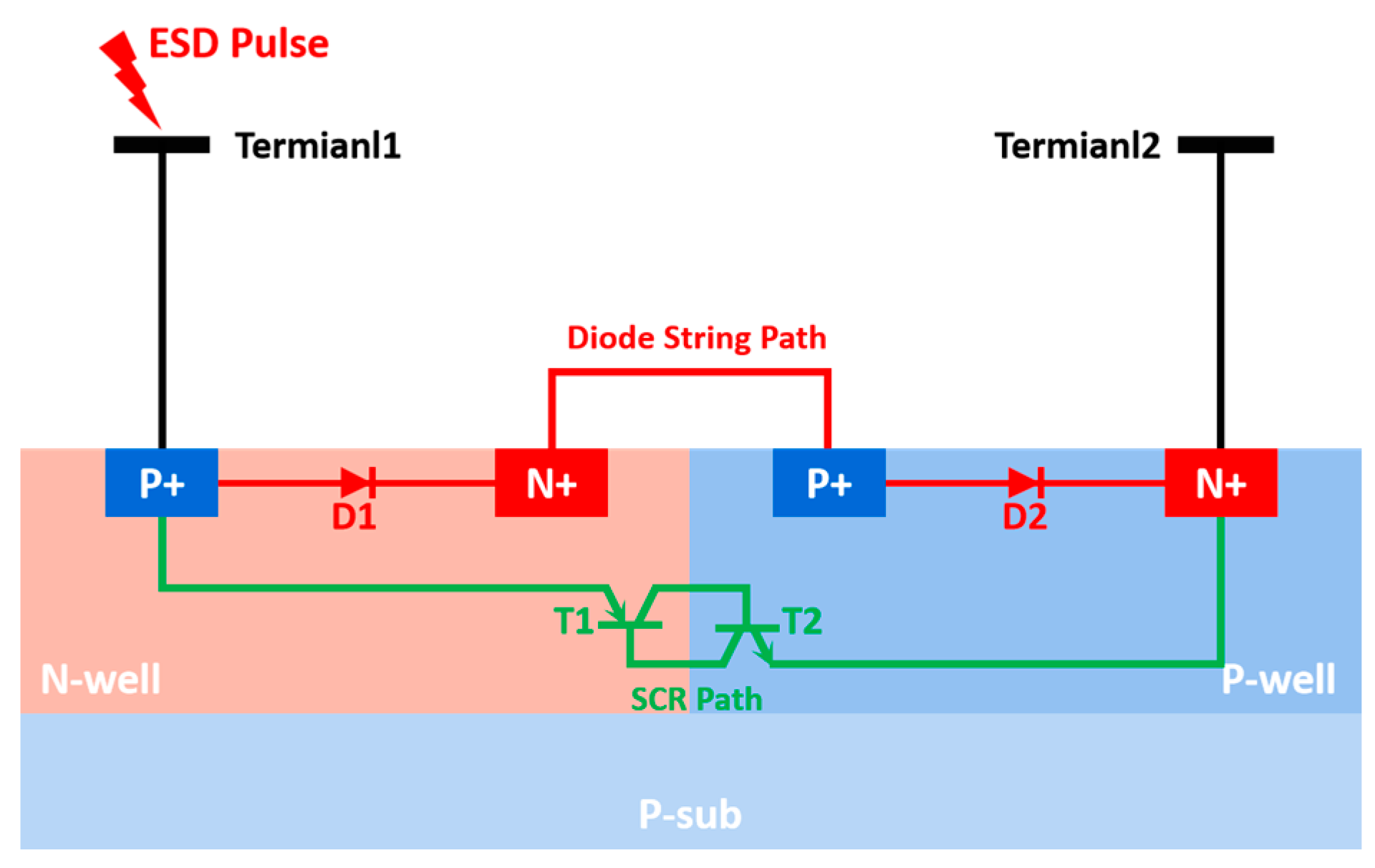

Cross-sectional structure view and equivalent schematic of the DTSCR. The diode string path (marked in red) is used as the trigger structure of the DTSCR. The SCR path (marked in green) drains the main ESD current.

Figure 1.

Cross-sectional structure view and equivalent schematic of the DTSCR. The diode string path (marked in red) is used as the trigger structure of the DTSCR. The SCR path (marked in green) drains the main ESD current.

Figure 2.

Cross-sectional view of the device structure and equivalent schematics of the MDTSCR under positive ESD stress (a) and negative ESD stress (b). The diode string path (marked in red) is used as the trigger structure of the MDTSCR. The parasitic SCR in a positive ESD strike (marked in green) is the main current conduction path, while under negative ESD stress, due to the extension of the SCR path, partial ESD current is also discharged through both the PNP path (marked in purple) and NPN path (marked in yellow).

Figure 2.

Cross-sectional view of the device structure and equivalent schematics of the MDTSCR under positive ESD stress (a) and negative ESD stress (b). The diode string path (marked in red) is used as the trigger structure of the MDTSCR. The parasitic SCR in a positive ESD strike (marked in green) is the main current conduction path, while under negative ESD stress, due to the extension of the SCR path, partial ESD current is also discharged through both the PNP path (marked in purple) and NPN path (marked in yellow).

Figure 3.

Cross-sectional view of the device structure and equivalent schematics of the EDTSCR under positive ESD stress (a) and negative ESD stress (c). The diode string path (marked in red) is used as the trigger structure of the EDTSCR. Due to the gate coupling effect in a positive (b) or negative (d) ESD strike, the MOS structure (marked in blue and white) will turn on quickly and offer additional current paths. The parasitic SCR (marked in green), as the main current conduction path, degrades under negative ESD stress due to the extension of the SCR path, resulting in the partial ESD current being discharged through both the PNP path (marked in purple) and NPN path (marked in yellow).

Figure 3.

Cross-sectional view of the device structure and equivalent schematics of the EDTSCR under positive ESD stress (a) and negative ESD stress (c). The diode string path (marked in red) is used as the trigger structure of the EDTSCR. Due to the gate coupling effect in a positive (b) or negative (d) ESD strike, the MOS structure (marked in blue and white) will turn on quickly and offer additional current paths. The parasitic SCR (marked in green), as the main current conduction path, degrades under negative ESD stress due to the extension of the SCR path, resulting in the partial ESD current being discharged through both the PNP path (marked in purple) and NPN path (marked in yellow).

Figure 4.

Simulated doping concentration profile of the designed EDTSCR.

Figure 4.

Simulated doping concentration profile of the designed EDTSCR.

Figure 5.

Simulated current density profile of the EDTSCR at 1 ns under positive ESD stress (a) and negative ESD stress (b). As the trigger structure of the EDTSCR, the ESD current only passes through the diode string path when the input voltage exceeds about 1.4 V.

Figure 5.

Simulated current density profile of the EDTSCR at 1 ns under positive ESD stress (a) and negative ESD stress (b). As the trigger structure of the EDTSCR, the ESD current only passes through the diode string path when the input voltage exceeds about 1.4 V.

Figure 6.

Simulated current density profile of the EDTSCR at 3 ns under positive ESD stress (a) and negative ESD stress (b). At this moment, the positive feedback of the parasitic SCR has been formed in a positive ESD strike so that the SCR path drains a large amount of the ESD current instead of the diode string. While under negative ESD stress, the diode string path is still the main discharge path due to the extension of the SCR path.

Figure 6.

Simulated current density profile of the EDTSCR at 3 ns under positive ESD stress (a) and negative ESD stress (b). At this moment, the positive feedback of the parasitic SCR has been formed in a positive ESD strike so that the SCR path drains a large amount of the ESD current instead of the diode string. While under negative ESD stress, the diode string path is still the main discharge path due to the extension of the SCR path.

Figure 7.

Simulated current density profile of the EDTSCR at 10 ns under positive ESD stress (a) and negative ESD stress (b). After the device is completely turned on, both the PNP path and NPN path can conduct. It is worth noting that the complementary MOS transistor pair instead of the SCR dominates the current conduction in a negative ESD strike because the parasitic PNP and NPN in the MOS transistors destroy the positive feedback needed for SCR path formation.

Figure 7.

Simulated current density profile of the EDTSCR at 10 ns under positive ESD stress (a) and negative ESD stress (b). After the device is completely turned on, both the PNP path and NPN path can conduct. It is worth noting that the complementary MOS transistor pair instead of the SCR dominates the current conduction in a negative ESD strike because the parasitic PNP and NPN in the MOS transistors destroy the positive feedback needed for SCR path formation.

Figure 8.

Simulated current density profile of the NMOS and PMOS in the EDTSCR at 3 ns: (a) positive ESD strike, PMOS; (b) positive ESD strike, NMOS; (c) negative ESD strike, PMOS; (d) negative ESD strike, NMOS. The channel current of the surface complementary NMOS and PMOS pair is significantly larger than the parasitic BJT current in both directions due to the gate coupling effect.

Figure 8.

Simulated current density profile of the NMOS and PMOS in the EDTSCR at 3 ns: (a) positive ESD strike, PMOS; (b) positive ESD strike, NMOS; (c) negative ESD strike, PMOS; (d) negative ESD strike, NMOS. The channel current of the surface complementary NMOS and PMOS pair is significantly larger than the parasitic BJT current in both directions due to the gate coupling effect.

Figure 9.

The distribution of the embedded NMOS channel current (b) is extracted along the tangent line in the Z direction (a) at different moments. The individual MOS channel current density accounts for about 20% of the total current density at 1 ns, which means that the embedded MOS structure contributes to the quick response of the device. As the rising voltage boosts, the parasitic BJT also starts to work, and the current density in the Z direction increases with time.

Figure 9.

The distribution of the embedded NMOS channel current (b) is extracted along the tangent line in the Z direction (a) at different moments. The individual MOS channel current density accounts for about 20% of the total current density at 1 ns, which means that the embedded MOS structure contributes to the quick response of the device. As the rising voltage boosts, the parasitic BJT also starts to work, and the current density in the Z direction increases with time.

Figure 10.

The percentage of channel current to total current with different channel lengths along the tangent line in the Z direction at different moments: (a) 1 ns and (b) 3 ns. When triggered at 1 ns, the shorter the channel length is, the larger the channel current proportion is due to the smaller gate capacitance, making the channel path easier to generate. After the device is triggered at 3 ns, the channel current ratios of the different channel lengths are approximately the same.

Figure 10.

The percentage of channel current to total current with different channel lengths along the tangent line in the Z direction at different moments: (a) 1 ns and (b) 3 ns. When triggered at 1 ns, the shorter the channel length is, the larger the channel current proportion is due to the smaller gate capacitance, making the channel path easier to generate. After the device is triggered at 3 ns, the channel current ratios of the different channel lengths are approximately the same.

Figure 11.

Experimental setup for the TLP. The low-bias (0.5 V) DC current is measured after each pulse, while the response toward the pulse voltage is averaged in a window from 70% to 90% of the pulse width.

Figure 11.

Experimental setup for the TLP. The low-bias (0.5 V) DC current is measured after each pulse, while the response toward the pulse voltage is averaged in a window from 70% to 90% of the pulse width.

Figure 12.

TLP characteristics of the DTSCR, MDTSCR, and EDTSCR: (a) TLP under positive ESD stress; (b) TLP under negative ESD stress. The EDTSCR shows much higher second failure current (It2) values and smaller ON resistance (Ron) values than the DTSCR and MDTSCR under both positive and negative stress. Both the MDTSCR and EDTSCR at positive strike achieve a stronger ESD robustness than the negative ones.

Figure 12.

TLP characteristics of the DTSCR, MDTSCR, and EDTSCR: (a) TLP under positive ESD stress; (b) TLP under negative ESD stress. The EDTSCR shows much higher second failure current (It2) values and smaller ON resistance (Ron) values than the DTSCR and MDTSCR under both positive and negative stress. Both the MDTSCR and EDTSCR at positive strike achieve a stronger ESD robustness than the negative ones.

Figure 13.

The transient voltage waveform of the DTSCR, MDTSCR, and EDTSCR under a 100 V positive VFTLP pulse. When the EDTSCR is turned on, its transient voltage peaks at 240 ps while both the DTSCR and MDTSCR peak at 300 ps, which means that EDTSCR has a lower voltage overshoot of 4.25 V and a faster turn-on ability.

Figure 13.

The transient voltage waveform of the DTSCR, MDTSCR, and EDTSCR under a 100 V positive VFTLP pulse. When the EDTSCR is turned on, its transient voltage peaks at 240 ps while both the DTSCR and MDTSCR peak at 300 ps, which means that EDTSCR has a lower voltage overshoot of 4.25 V and a faster turn-on ability.

Table 1.

Comparison of experimental measurements with the MDTSCR and EDTSCR under positive (pos) and negative (neg) ESD strikes.

Table 1.

Comparison of experimental measurements with the MDTSCR and EDTSCR under positive (pos) and negative (neg) ESD strikes.

| Device | (V) | (V) | It2

(mA/um) | (Ω) | FOM

(mA/um2) |

|---|

| DTSCR | 1.40 | 1.31 | 28.1 | 1.78 | 2.34 |

| MDTSCR (pos) | 1.38 | 1.14 | 37.3 | 1.12 | 3.10 |

| MDTSCR (neg) | 1.38 | / | 36.0 | 1.34 | 3.00 |

| EDTSCR (pos) | 1.38 | 1.25 | 48.2 | 0.92 | 4.01 |

| EDTSCR (neg) | 1.37 | / | 37.8 | 1.05 | 3.15 |