1. Introduction

Passively tunable microwave elements such as phase shifters facilitate electrical beam steering by feeding phased antenna arrays. Typically, the phase shifting reconfigurability is achieved through semiconductor switches such as p-i-n diodes [

1,

2], varactors [

3], varactor diodes [

4], RF MEMS [

5,

6] (periodically loaded with capacitive switches that are electrically actuated), and ferroelectrics [

7]. The achievable ~µs tuning speeds provide excellent temporal resolution in beam switching, whereas their digital switching in nature significantly affects the spatial resolution.

To address this shortcoming and target the beam direction at a higher spatial resolution, nematic liquid crystal (LC) can be introduced as a continuously tunable dielectric medium for continuous phase shift controlled by a low-amplitude bias voltage [

8,

9,

10]. Arguably, LC-enabled RF tunable front-end devices and technologies are steadily evolving to provide essential functions for phased-array non-mechanical beam steering with continuous-tuning, low-insertion-loss, lighter, smaller, and less power-hungry advantages aimed at end-users in various industries. Although the true commercialization of LC-based phased array systems has yet to occur due to the difficulties listed in [

9], each new generation of designs (device structure or material innovation) feeds the end-users’ demands slightly more and produces subsequent incremental contributions to information and communication technology services. For instance, the evolution of microwave LC material development (e.g., from 5CB, E7 to GT3-24002 and W1825) is evidenced by the simultaneous increased dielectric tunability and reduced dissipation factor, i.e., an improved figure-of-merit (FoM), as evidenced in [

10,

11,

12].

However, when combining LC with specific guided structures (transmission line or waveguide), there is limited in-depth investigation on decomposing the device’s insertion loss into various materials’ dissipations, i.e., a lack of quantification of conductor loss and dielectric loss, which significantly limits the loss optimization opportunity from the device physics perspective. Resultantly, there is no knowledge of the feasibility of using LC as an electronically tunable medium to realize a passive 0–10 V continuously variable 0–π analog phase shifter with sufficiently low insertion loss (e.g., well below 2 dB specification) across a broad spectrum of 1–67 GHz, which motivates the ongoing research reported in this communication.

Regardless of the particular transmission line structure used to accommodate these tunable dielectric materials (i.e., LC) to realize an LC-based phase shifter (assuming a transmission type), the tuning principle and, therefore, the theoretical maximum tuning range occur when the wave occupancy volume ratio (WOVR) (defined by our previous work [

13]) is assumed to be 100% in the tunable dielectric (i.e., LC) with respect to the overall dielectric volume space (including tunable and not tunable). By the standard electrically tuned bias method [

12], the minimum permittivity of the device structure (

) occurs in the reference perpendicular condition of the LC director when coupled to a microwave signal field. In contrast, the maximum dielectric constant of the device (

) occurs at the parallel state of the LC director [

13]. Based on these well-established principles,

Figure 1 below quantifies the maximum differential phase shift achievable with these academically recognized and commercially available nematic LC materials. Accordingly, the minimum effective line length (

) with LC to achieve a differential phase shift

of 0–2π at frequency f is shown in

Figure 2, based on the mathematical relationship [

12,

13] with the line length, frequency, and effective dielectric constant, as described in Equation (1), where

is the light velocity in a vacuum.

It is well worth noting that not only does the employment of tunable dielectrics (i.e., LCs) matter, but understanding the limits and capabilities of PCB substrate materials (non-tunable) can also tip the balance, because the dielectric constant impacts the WOVR and hence the phase shift and insertion loss performance. The waveguide perturbation tests are thus performed for RT5880 and RO3003 (substrate materials both from Rogers Corporation) at different frequencies (10 GHz, 30 GHz, 50 GHz), with

Table 1 providing the constitutive parameters of the dielectric constants (

) and dissipation factors (tan

) defined as per Equation (2), where

denotes the total effective conductivity caused by ionic conduction and displacement current.

2. Materials and Methods

The phase shifter is constructed in an inverted microstrip line (IMSL) topology with metals and dielectrics (tunable and non-tunable) as arranged and denoted in

Figure 3a. One of our recently fabricated and assembled LC-filled IMSL phase shifter device prototypes [

14] is shown in

Figure 3b, as an evolution from early developments [

12,

15] with a lack of in-depth understanding on various materials’ dissipative losses for device optimization.

In this communication, the designs and calculation models are performed using MATLAB and Ansys HFSS (full-wave simulations). By way of illustration,

Figure 4 shows the wave port mode of the LC-filled IMSL phase shifter analyzed at 60 GHz.

The effective core line length () is designed to achieve 0–π shift at 60 GHz. A straight-line circuit (free from bending-related radiation and mismatching losses) is targeted using the highly anisotropic LC material (GT3-24002) with a layer thickness () of 125 µm. Low-loss PCB laminate RT5880 with a substrate thickness () of 787 µm is applied with the copper (Cu) clad thickness () of 17 µm and the Cu core line cross-sectional width () of 220 µm.

Accordingly,

is calculated from Equation (1), shown earlier in

Section 1, for achieving 0–π shift, and 0–2π shift, respectively. The

results in phase (data processed in the format of differential phase shifts) are validated in

Figure 5, with

of 1.35 cm for achieving the targeted 0–π shift capability, and 2.7 cm for the 0–2π shift functionality at 60 GHz.

Figure 6 presents the

results in amplitude (dB), identifying the maximum insertion loss (at 0 V bias state) from 1.46 dB to 1.74 dB across ∆f/f = ±10% (i.e., 54 GHz to 67 GHz with the center frequency of 60 GHz) for the 0–π shift design, and from 2.74 dB to 3.33 dB for the 0–2π shift design, respectively. Note that for the

(amplitude in dB) in

Figure 6, regarding the different line lengths, the relationship between

(dB) and the line length is nonlinear (as analyzed and discussed in our previous work [

13,

16]), as it is complicated by the different loss mechanisms (to be shown in Equations (6)–(11) in

Section 3), resultantly causing the closed-form solution and simplified formula to fail to work accurately. This is why numerical simulation is introduced and, more specifically, this work proposes the use of the full-wave power dissipation analysis method to identify each loss fraction dissipated by each element of the device, the achievement of which will bridge the gap that experimental analysis cannot resolve (to separate diverse loss components from diverse materials constituting the device).

The

in amplitude (i.e., return loss) are also quantified for the corresponding 0 V and 10 V biasing states, as well as for the two designs of different lengths (

of 1.35 cm for 0–π shift, and 2.7 cm for 0–2π shift at 60 GHz). As shown in

Figure 7, the reflection losses are well below 20 dB for all the tuning states under analysis and across the spectrum of 1–67 GHz. This indicates decent impedance-matched performance with no concern regarding the dielectric-anisotropy-induced impedance spikes for this designed geometry. Furthermore, the 10 V biasing state exhibits a lower return loss than the 0 V driving ones (validated for both designs of 0–π shift and 0–2π shift).

One of the focuses and novelties of this communication is, as the title suggests, rethinking the LC IMSL phase shifter design via the proposed loss dissipation analysis (to be shown in

Section 3) that decomposes each loss element with parameterized geometry sizes, the contribution of which cannot be achieved by traditional experimental measurements (e.g., it is not possible to characterize and separate each metal loss and each dielectric loss component by a vector network analyzer). Analytical and numerical simulations are thereby introduced in this work to bridge the gap and perform the loss component quantification to boost the understanding of which element dominates the insertion loss.

3. Full-Wave Power Dissipation Analysis and Results

The results are further analyzed by performing a full-wave power dissipation analysis using HFSS for all materials comprising the device. This assumes that an input power () of 100% is injected, calculating the output power (, i.e., transmission), reflected power (, i.e., reflection), as well as the dissipated power in the materials (i.e., metal losses and dielectric losses).

Based on the assumption of

= 100% and the obtained

, the output power (

, i.e., transmission) is derived by Equation (3) governing this two-port network, and hence is given in Equation (4).

Similarly, the reflected power (

, i.e., reflection) can be derived by Equation (5) and given in Equation (6) as below.

For the dissipated power in metals (Cu core line and Al substrate as grounding plane), the principle of calculating these conductor losses follows Ohm’s Law by taking the integrals over the metal surface. By way of illustration, the IMSL core line’s metal loss per unit length can be expressed in the phasor form (

) given in Equation (7) by incorporating our previous derivation [

13]. The peak phasor form of conductor loss for the grounding Al substrate can be given in a similar way.

Loss dissipated in the volume of dielectrics (e.g., LC, RT5880 PCB substrate, and glue/spacer mixture in this work) can be derived analytically from a parallel capacitor model filled with lossy dielectrics [

13]. Note that the cross-sectional size of the LC-filled cavity is far less than half the guided wavelength for 1–67 GHz under analysis; hence, a TEM nature is assumed (i.e., without higher-order waveguide modes) and the quasi-static approach based on circuit theory can be used. Accordingly, the peak phasor forms of the LC volumetric loss per unit length at the lossy 0 V biasing state are given by Equation (8).

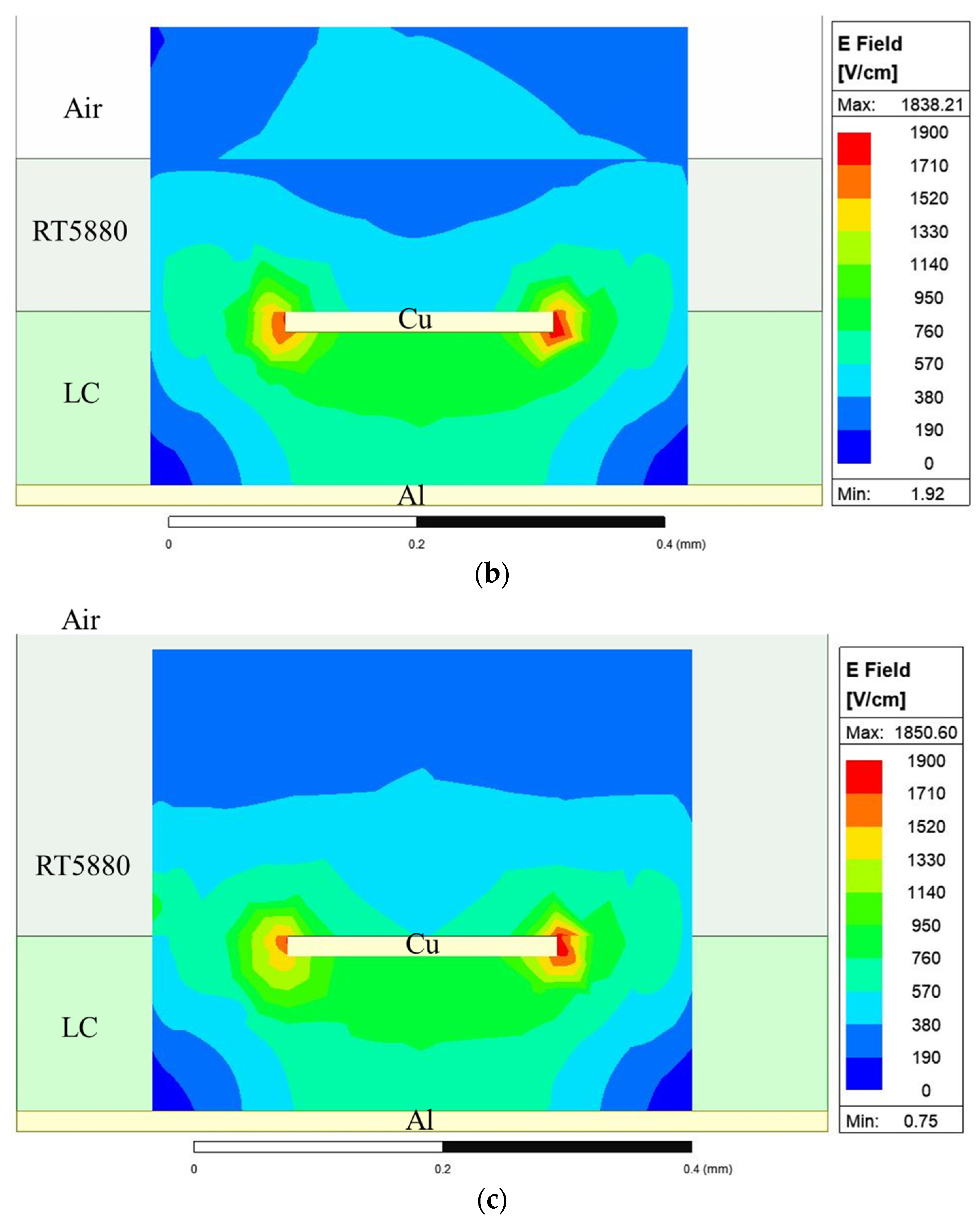

As charges are not uniformly distributed, the E field features a skin effect and proximity effect, which are significantly different from that at electrostatics. Thus, 3D full-wave simulations in HFSS are thereby performed to numerically quantify these effects and also to integrate the line length to produce the surface loss (for metals) and volumetric loss (for dielectrics). This is done by integrating the surface loss density (e.g.,

for the core line) over the metal surface (dS), and integrating the volume loss density (e.g.,

for the LC) over the dielectric volume (dV), as specified in Equations (9) and (10), respectively. The mathematical manipulations are performed in the HFSS field calculator for the volumetric phasor field data generated from the finite element analysis.

The remaining loss fraction that is not dissipated by the device itself can be indicated as radiation and hence is derived by Equation (11), with

denoting the total losses of all metals, and

representing the total losses from all dielectrics.

The loss decomposition analysis results are presented in

Figure 8, being specifically analyzed at 60 GHz for the 0 V biasing (lossy state of analysis interest). Obviously, the LC dielectric loss (21.28%) contributes the most significant part, followed by the core line metal loss of 5.19% (under the assumption of no surface roughness), and then the grounding Al metal loss (2.04%) and radiation loss of 1.39%. The material absorption losses in the glue/spacer mixture and RT5880 PCB substrate are infinitesimal (0.04% and 0.35%, respectively).

The effect of the PCB substrate thickness

is well known to dominate the characteristics of a standard microstrip line, whereas it is of minor importance for an inverted microstrip line (IMSL). Instead, the liquid crystal layer thickness (

) is of paramount significance to the IMSL. This is due mainly to the wave-occupied volume ratio (WOVR), as illustrated differently in

Figure 9a,b at 60 GHz.

Based on this understanding, the impacts of

on the transmission line performance are quantified in

Figure 10,

Figure 11,

Figure 12 and

Figure 13 by comparing devices using

= 0.787 mm and

= 0.127 mm (RT5880 PCB), respectively. Note that for the change in

, the port size and air box sizes are rearranged accordingly to capture any radiation effect. The size arrangement of the assigned wave port for the calculation is a modeling-related representation problem concerning how to confine the signal (wave) as input (and output), which is different from (and out of scope for) the device’s physical governing equations as shown before. Here, the work follows the standard practice of assigning the wave port for the IMSL structure by balancing the computational efficiency and modeling accuracy (capturing all the possible modes in the dielectrics surrounding the electrodes). The other dimension sizes (

= 0.125 mm and

= 1.35 cm) are kept equalized between both designs. As also visualized in

Figure 9b,c, the WOVR of the

= 0.127 mm design is higher than that of the

= 0.787 mm design. This is supported by the results of the achievable differential phase shift in

Figure 10, exhibiting a 5° difference at 60 GHz.

Regarding the forward transmission (), the = 0.787 mm design exhibits a lower insertion loss (for both 0 V and 10 V biasing states) below 35 GHz. The 0.127 mm thick design exhibits a lower insertion loss (both 0 V and 10 V biasing states) above 45 GHz. Nevertheless, the difference is only 0.04 dB at 60 GHz between both designs.

In terms of the effective dielectric constant and hence the guided wavelength reported in

Figure 13, it is verified that the effective dielectric constant of the

= 0.787 mm design is larger than that of the

= 0.127 mm one, the value of which at 10 V is larger than that at 0 V bias. Accordingly, the guided wavelength of the

= 0.787 mm design is smaller than that of the

= 0.127 mm one, the value of which at 10 V is smaller than that at 0 V bias. Consequently, the minimum guided wavelength is 2.57 mm for 67 GHz at 10 V bias.

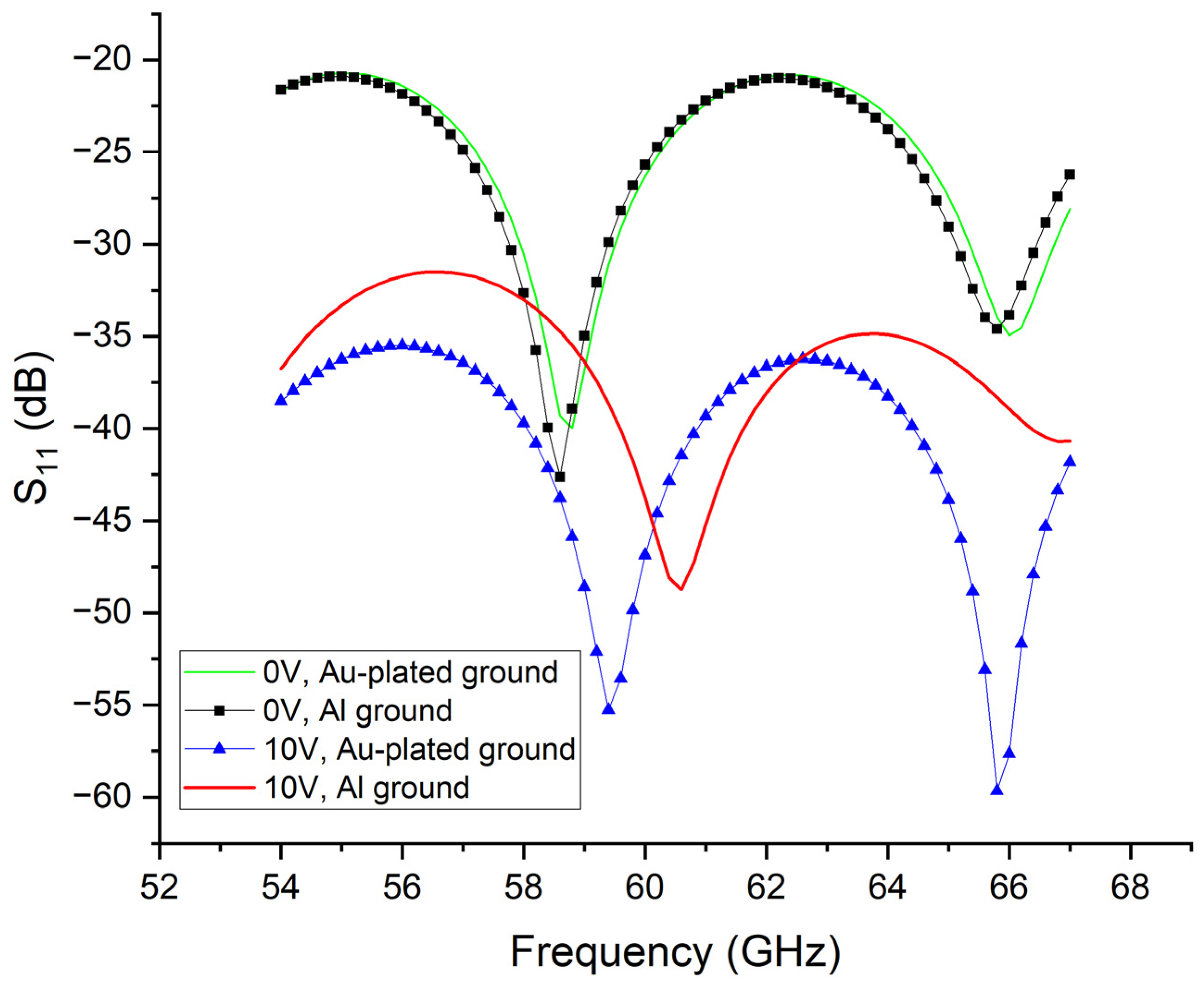

Further investigation is conducted on the impact of the grounding plane’s conductivity by comparing a gold (Au)-plated ground plane versus aluminum (Al) ground without plating.

Figure 14,

Figure 15,

Figure 16 and

Figure 17 present the phase shift, insertion loss, and return loss results. The gold-plated one reduces the insertion loss by 0.01 dB at 67 GHz (for both 0 V and 10 V biasing states).

The effect of the core line’s conductivity is also investigated and reported in

Figure 17 and

Figure 18. To be more specific, a 0.01 dB improvement in

is obtained by using a silver (Ag)-plated Cu core line compared to a Cu core line without Ag plating.

As shown in

Figure 19, loss decomposition analysis (with the same calculating principle as

Figure 8) is performed at 60 GHz for the cases of

Figure 14,

Figure 15,

Figure 16,

Figure 17 and

Figure 18. With the design of a 125 μm thick LC dielectric layer, the circuit is dominated by dielectric loss. Therefore, reducing the surface roughness or using a more conductive electrode has a minor effect in mitigating the insertion loss.

Note that the dimension above gives the characteristic impedance = 54 Ω at 0 V bias. This is obtained under the quasi-TEM mode condition that applies to the LC IMSL, for which the characteristic impedance can be calculated computationally based on = , where denotes the time-averaged power transmitted (which is obtained by integrating the Poynting vector across the IMSL’s cross-section), and represents the longitudinal current.

To fine-tune the impedance to match 50 Ω, one can either reduce or increase (both can contribute a higher WOVR and hence higher tuning range and shorter line length to achieve π shift). We derive the design of IMSL with = 125 μm (GT3-24002), = 0.787 mm (RT 5880), = 0.248 mm (Cu core line), = 13.5 mm (effective tunable line length to achieve 0–π phase shift).

4. Discussion

From our previous analytical analysis [

13], the LC dielectric loss per unit volume P =

, where E denotes the electric field intensity within the volume of analysis, f is the frequency of analysis,

is the relative permittivity of the dielectric volume of analysis. Reducing the LC layer thickness

in this work exhibits doubling effects. First, it means reducing the distance between the core line and the ground plane, thus increasing the local peaking of the electric field intensity E at the conductor surface (fixed area) and hence increasing the conductor loss (as per Ampere’s law [

17] regarding the integration loop). Secondly, reducing

means reducing the LC volume but increasing E. Integrating the increased E over the reduced volume will jointly contribute to a reduced or increased dielectric volumetric loss, depending on which factor dominates the integral operation. It is reasonable to predict qualitatively that when reducing the LC thickness

to a certain value, the conductor loss will start to dominate. In this case, the surface roughness and conductivity of the conductors (mainly core line) will play an important role. The surface roughness will further increase the conductor loss as compared to the current study (without considering the surface roughness), which will exhibit a more dominant role of the conductor loss towards the insertion loss degradation. Note that the quantitative impact of the surface roughness on the insertion loss and other aspects of performance is a debatable topic, with a host of different models and experiments available in the literature [

18,

19,

20,

21,

22], to which the interested readers can refer in order to explore this further.

Recall the results analysis performed for an all-optically-controlled LC-based microstrip [

23]; for a

< 10 um cell, conductor loss dominates. Instead, increasing the LC cell thickness

, the conductor losses reduce, as evidenced in

Figure 20 below regarding the dissipative power analysis results of the Cu core line and the grounding transparent metal film, i.e., a conductive indium tin oxide (ITO) coating on an optically transparent polyethylene terephthalate (PET) substrate (denoted as transparent substrate in

Figure 20). Interestingly, the conductor loss is found to vary linearly with 1/

, as quantified in

Figure 21.

The intention and key contribution of this work (as a significant follow-up milestone based on our previous experimentally prototyped LC phase shifters) is not to produce a brand-new device topology to compete with other state-of-the-art phase shifters, but, instead, to contribute to solving and understanding the fundamental yet very important IMSL structure with LC via a new power dissipative analysis approach, which quantifies the conventionally unclear problem regarding each material loss element of the device with diverse geometry-coupled effects. Not limited to the IMSL topology, the proposed power dissipative analysis method can be generalized to other device structures (e.g., shielded coplanar waveguide [

16], dielectric waveguide [

24], dielectric image line [

25], substrate integrated waveguide [

26]) and enhance the state-of-the-art LC-based tunable microwave phase shifter design.