Recovery Effect of Hot-Carrier Stress on γ-ray-Irradiated 0.13 μm Partially Depleted SOI n-MOSFETs

Abstract

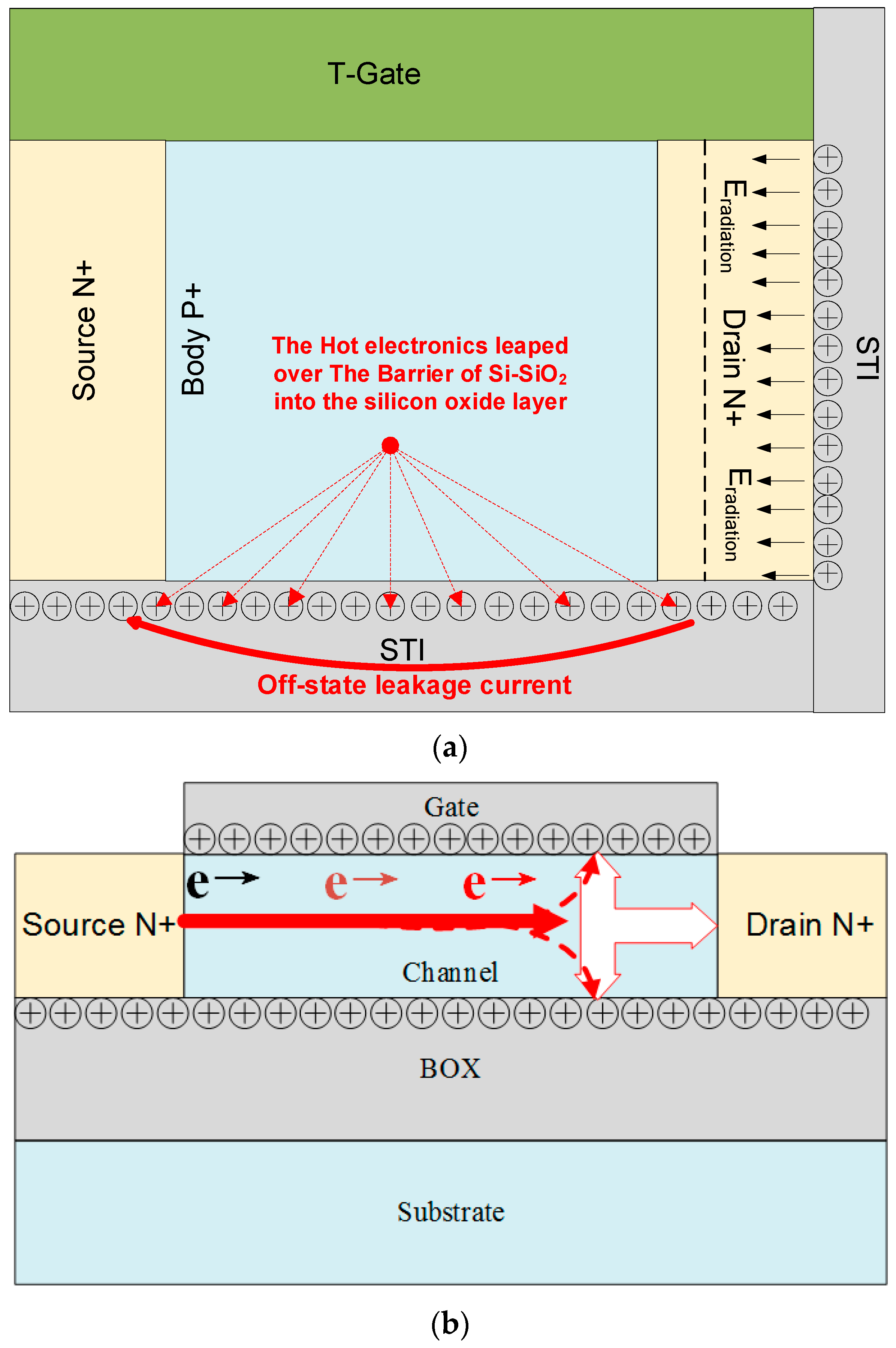

:1. Introduction

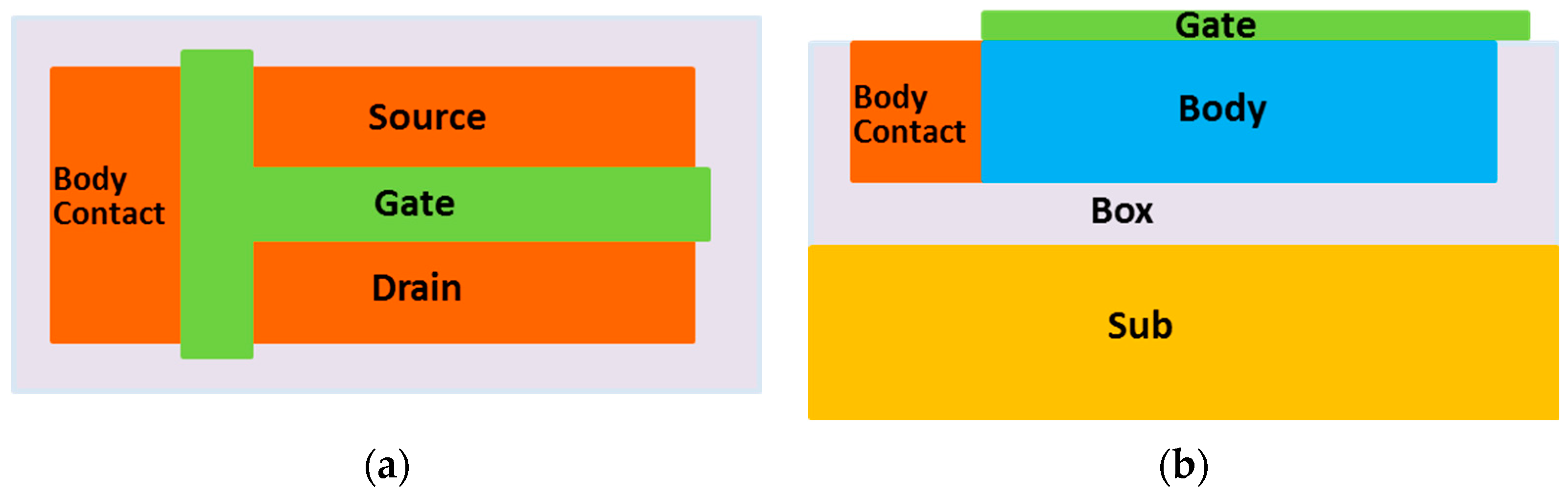

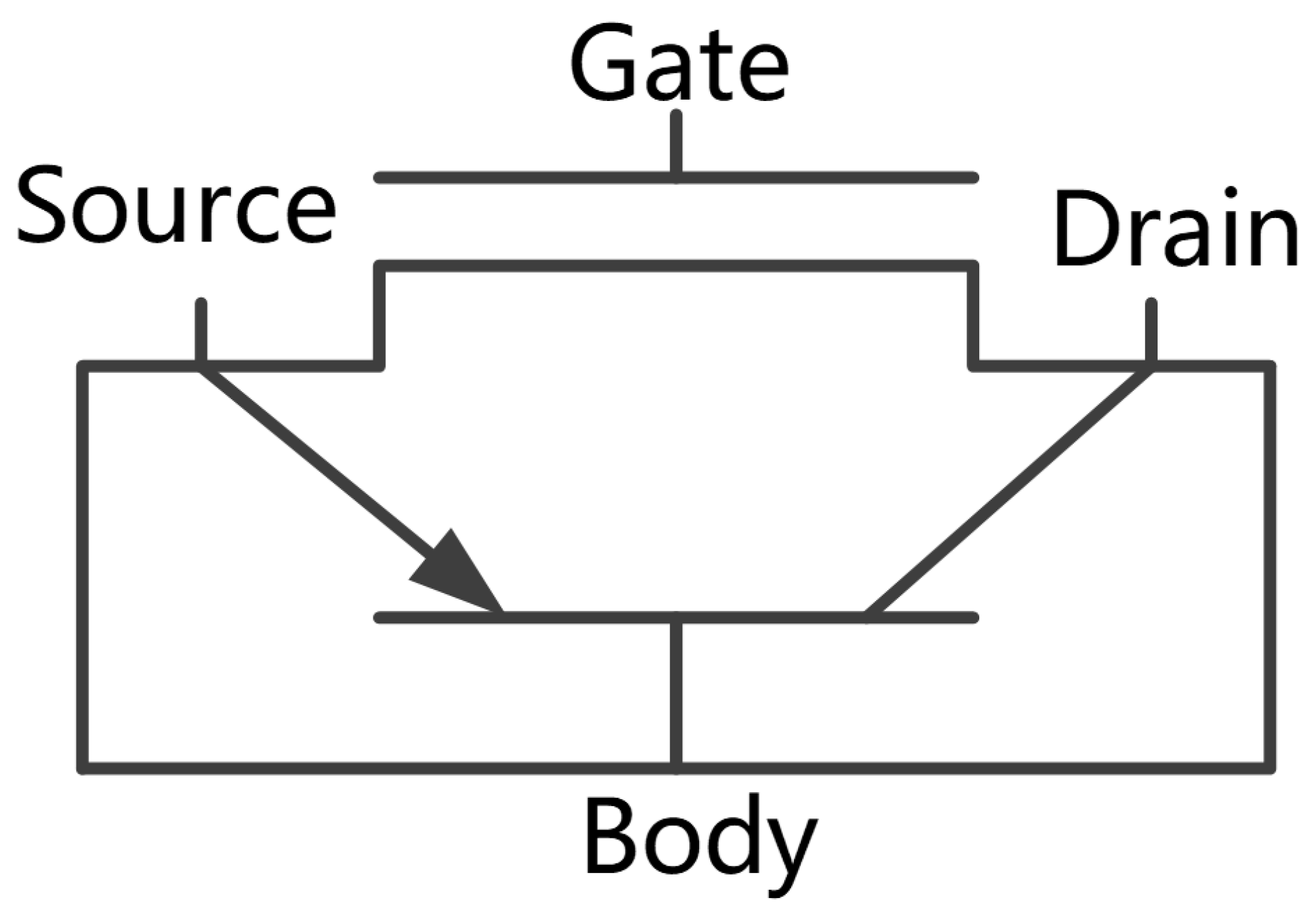

2. Device and Experimental Details

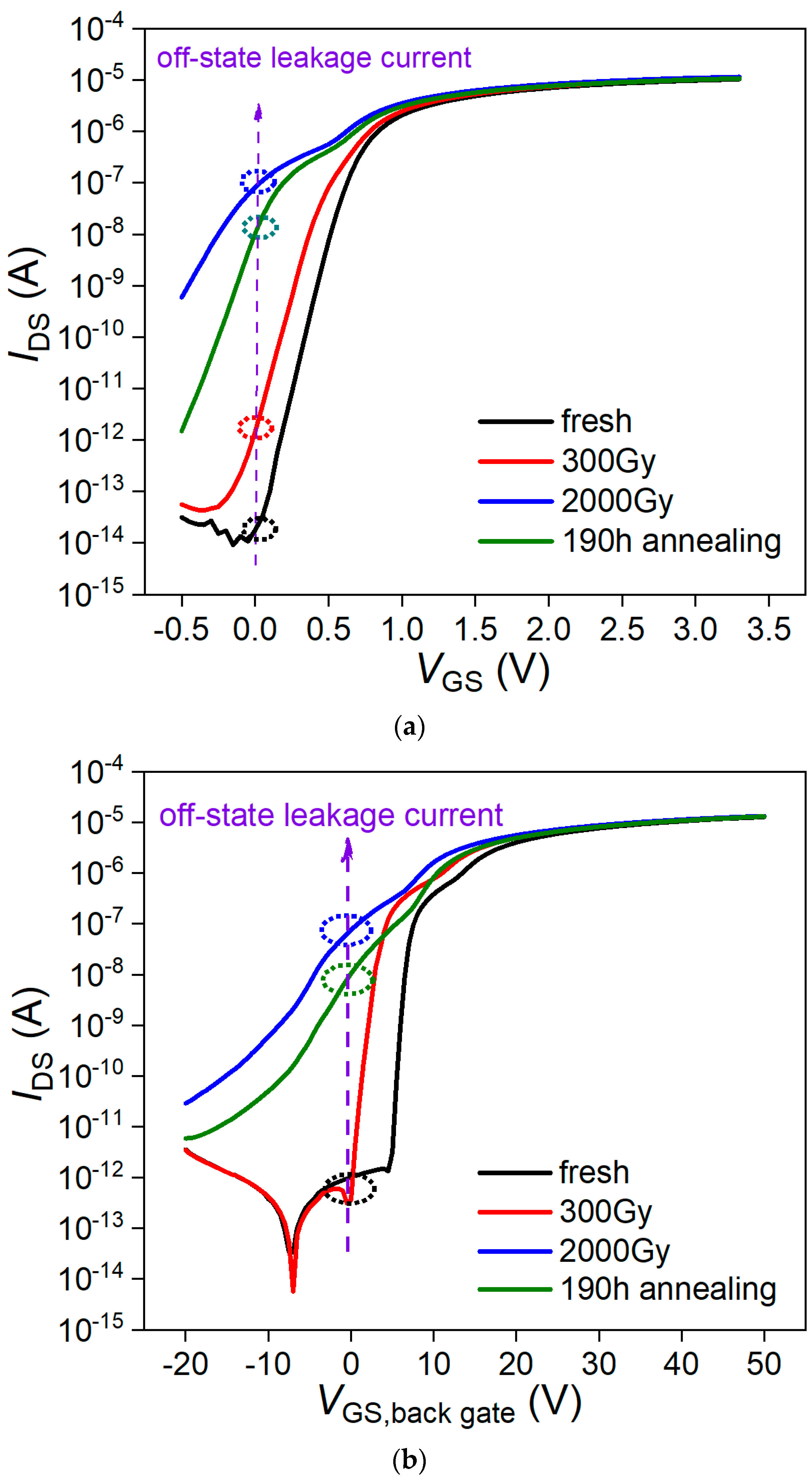

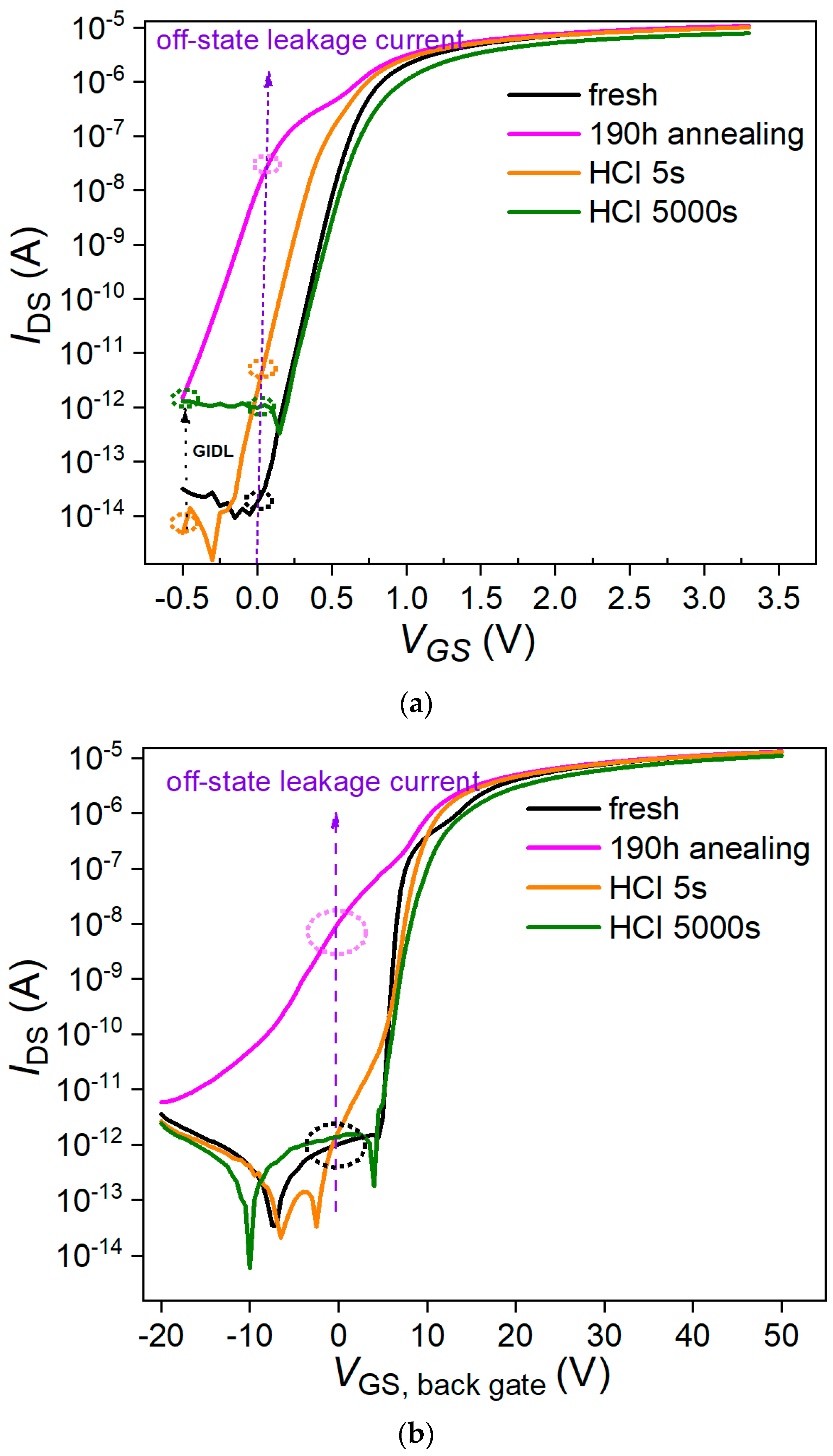

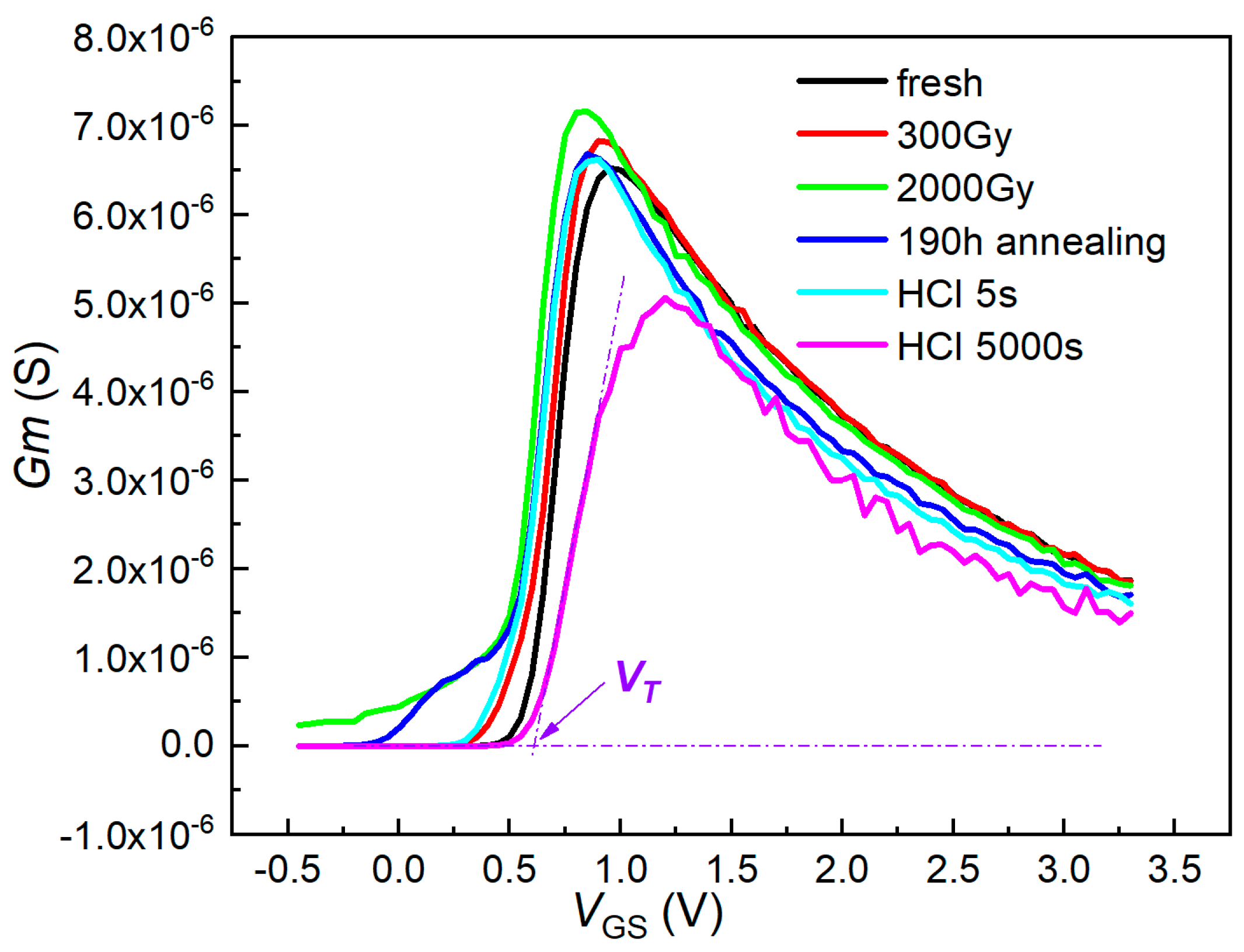

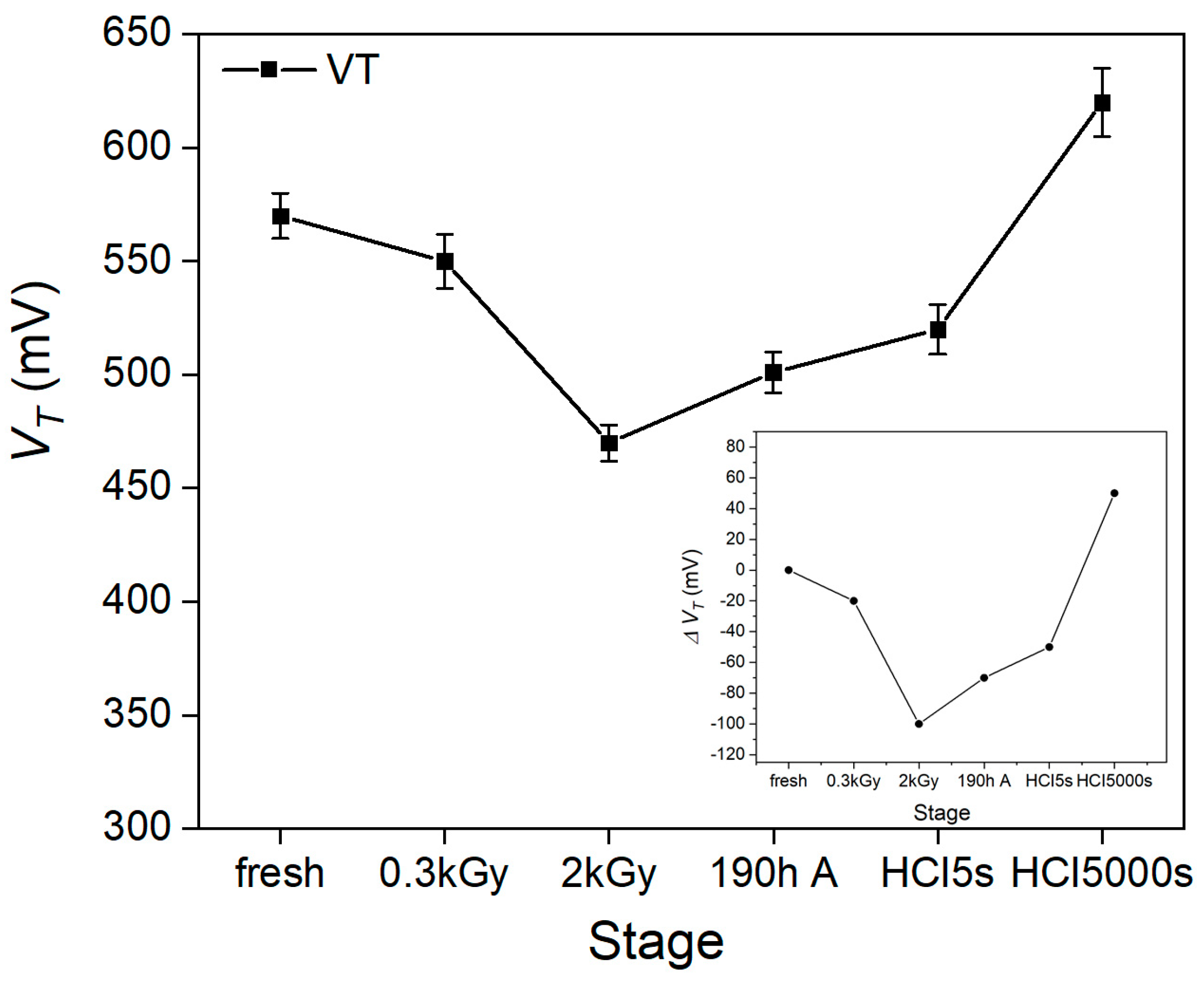

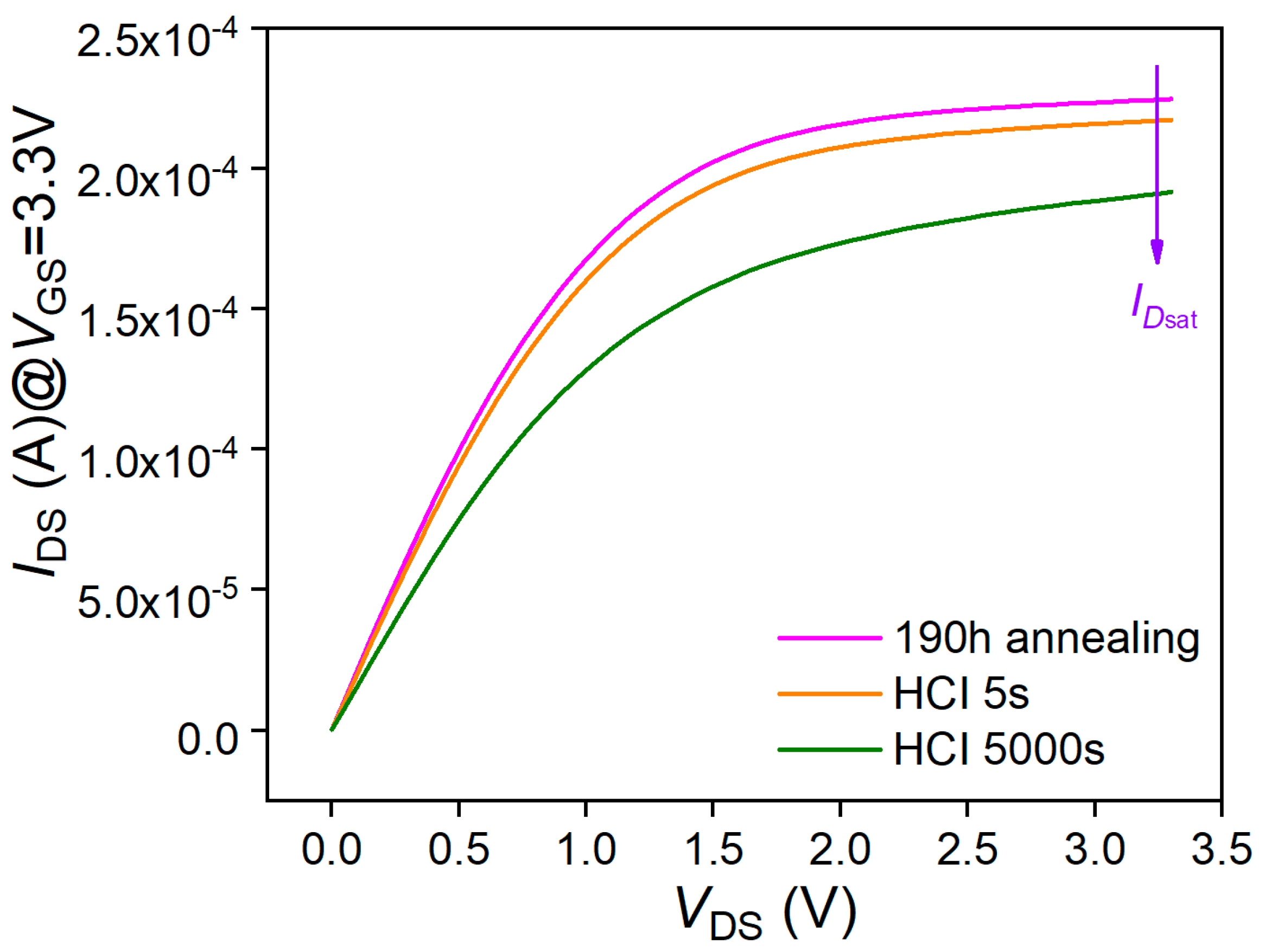

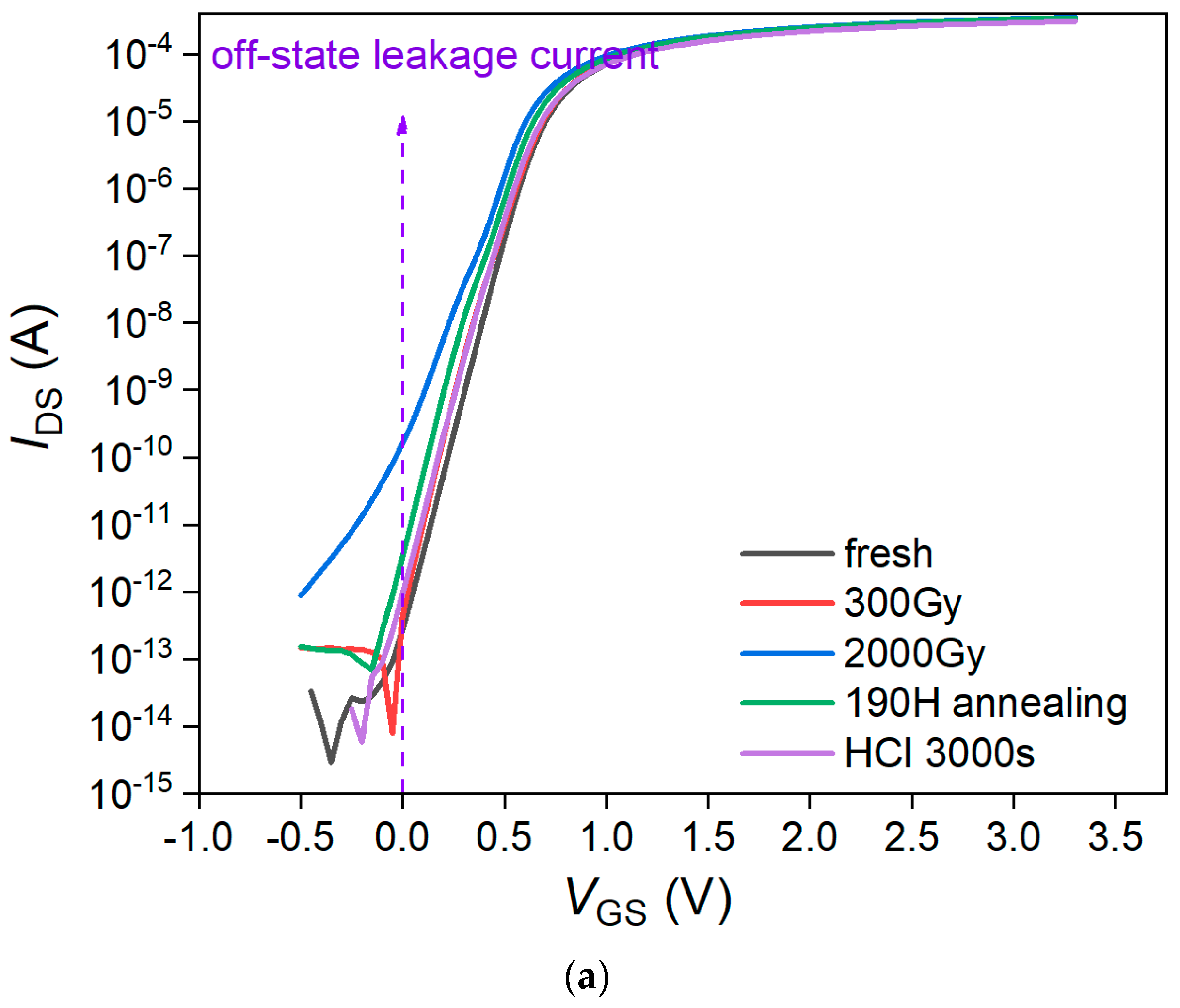

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

Nomenclature

| PD SOI | Partially Depleted Silicon-On-Insulator |

| MOSFET | Metal–Oxide–Semiconductor Field Effect Transistor |

| HCI | Hot Carrier Injection |

| MOS | Metal Oxide Semiconductor |

| CMOS | Complementary Metal–Oxide–Semiconductor |

| TID | Total Ionizing Dose |

| BOX | Buried Oxide |

| VLSI | Very Large-Scale Integration |

| RT | Room Temperature |

| GIDL | Gate-Induced Drain Leakage |

| STI | Shallow Trench Isolation |

References

- Oldham, T.R.; McLean, F.B. Total ionizing dose effects in MOS oxides and devices. IEEE Trans. Nucl. Sci. 2003, 50, 483–499. [Google Scholar] [CrossRef]

- Brewer, R.M.; Zhang, E.X.; Gorchichko, M.; Wang, P.F.; Cox, J.; Moran, S.L.; Ball, D.R.; Sierawski, B.D.; Fleetwood, D.M.; Schrimpf, R.D.; et al. Total ionizing dose responses of 22-nm FDSOI and 14-nm bulk FinFET charge-trap transistors. IEEE Trans. Nucl. Sci. 2021, 68, 677–686. [Google Scholar] [CrossRef]

- Jiang, R.; Zhang, E.X.; McCurdy, M.W.; Wang, P.; Gong, H.; Yan, D.; Schrimpf, R.D.; Fleetwood, D.M. Dose-rate dependence of the total-ionizing-dose response of GaN-based HEMTs. IEEE Trans. Nucl. Sci. 2018, 66, 170–176. [Google Scholar] [CrossRef]

- Wang, P.F.; Zhang, E.X.; Chuang, K.H.; Liao, W.; Gong, H.; Arutt, C.N.; Ni, K.; Mccurdy, M.W.; Verbauwhede, I.; Bury, E.; et al. X-ray and proton radiation effects on 40 nm CMOS physically unclonable function devices. IEEE Trans. Nucl. Sci. 2018, 65, 1519–1524. [Google Scholar] [CrossRef]

- Wang, P.F.; Zhang, E.X.; Fleetwood, D.M.; McCurdy, M.W.; Lin, J.-T.; Alles, M.L.; Davidson, J.L.; Alphenaar, B.W.; Schrimpf, R.D. Effects of Charge Generation and Trapping on the X-ray Response of Strained AlGaN/GaN HEMTs. In Proceedings of the 2021 IEEE 14th International Conference on ASIC (ASICON), Kunming, China, 26–29 October 2021; IEEE: Piscataway, NJ, USA, 2021; pp. 1–4. [Google Scholar] [CrossRef]

- Musseau, O. Single-event effects in SOI technologies and devices. IEEE Trans. Nucl. Sci. 1996, 43, 603–613. [Google Scholar] [CrossRef]

- McWhorter, P.; Miller, S.; Miller, W. Modeling the anneal of radiation-induced trapped holes in a varying thermal environment. IEEE Trans. Nucl. Sci. 1990, 37, 1682–1689. [Google Scholar] [CrossRef]

- Liu, B.; Li, Y.; Wen, L.; Zhang, X.; Guo, Q. Effects of Hot Pixels on Pixel Performance on Backside Illuminated Complementary Metal Oxide Semiconductor (CMOS) Image Sensors. Sensors 2023, 23, 6159. [Google Scholar] [CrossRef]

- Li, X.; Cui, J.; Zheng, Q.; Li, P.; Cui, X.; Li, Y.; Guo, Q. Study of the Within-Batch TID Response Variability on Silicon-Based VDMOS Devices. Electronics 2023, 12, 1403. [Google Scholar] [CrossRef]

- Zhang, Y.W.; Huang, H.X.; Bi, D.W.; Tang, M.; Zhang, Z. Investigation of unique total ionizing dose effects in 0.2 µm partially-depleted silicon-on-insulator technology. Nucl. Instrum. Methods Phys. Res. Sect. A Accel. Spectrometers Detect. Assoc. Equip. 2014, 745, 128–132. [Google Scholar] [CrossRef]

- Fan, S.; Hu, Z.-Y.; Zhang, Z.-X.; Ning, B.-X.; Bi, D.-W.; Dai, L.-H.; Zhang, M.-Y.; Zhang, L.-Q. Total ionizing dose induced single transistor latchup in 130-nm PDSOI input/output NMOSFETs. Chin. Phys. B 2017, 26, 036103. [Google Scholar] [CrossRef]

- Huang, H.-X.; Bi, D.-W.; Peng, C.; Zhang, Y.-W.; Zhang, Z.-X. The Enhanced Role of Shallow-Trench Isolation in Ionizing Radiation Damage of Narrow Width Devices in 0.2 μm Partially-Depleted Silicon-on-Insulator Technology. Chin. Phys. Lett. 2013, 30, 080701. [Google Scholar] [CrossRef]

- Zheng, Q.-W.; Cui, J.-W.; Zhou, H.; Yu, D.-Z.; Yu, X.-F.; Lu, W.; Guo, Q.; Ren, D.-Y. Analysis of functional failure mode of commercial deep sub-micron SRAM induced by total dose irradiation. Chin. Phys. B 2015, 24, 106106. [Google Scholar] [CrossRef]

- Yeh, W.-K.; Wang, W.-H.; Fang, Y.-K.; Chen, M.-C.; Yang, F.-L. Hot-carrier-induced degradation for partially depleted SOI 0.25–0.1/spl mu/m CMOSFET with 2-nm thin gate oxide. IEEE Trans. Electron. Devices 2002, 49, 2157–2162. [Google Scholar] [CrossRef]

- Cui, J.; Xue, Y.; Yu, X.; Ren, D.; Lu, J.; Zhang, X. Total dose irradiation and hot-carrier effects of sub-micro NMOSFETs. J. Semicond. 2012, 33, 014006. [Google Scholar] [CrossRef]

- Rafí, J.M.; Simoen, E.; Mercha, A.; Hayama, K.; Campabadal, F.; Ohyama, H.; Claeys, C. Electrical stress on irradiated thin gate oxide partially depleted SOI nMOSFETs. Microelectron. Eng. 2007, 84, 2081–2084. [Google Scholar] [CrossRef]

- Huang, D.H.; King, E.E.; Wang, J.J.; Ormond, R.; Palkuti, L. Correlation between channel hot-electron degradation and radiation-induced interface trapping in N-channel LDD devices. IEEE Trans. Nucl. Sci. 1991, 38, 1336–1341. [Google Scholar] [CrossRef]

- Dai, L.; Liu, X.; Zhang, M.; Zhang, L.; Hu, Z.; Bi, D.; Zhang, Z.; Zou, S. Degradation induced by TID radiation and hot-carrier stress in 130-nm short channel PDSOI NMOSFETs. Microelectron. Reliab. 2017, 74, 74–80. [Google Scholar] [CrossRef]

- McBrayer, J.D.; Fleetwood, D.M.; Pastorek, R.A.; Jones, R.V. Correlation of hot-carrier and radiation effects in MOS transistors. IEEE Trans. Nucl. Sci. 1985, 32, 3935–3939. [Google Scholar] [CrossRef]

- Palkuti, L.J.; Ormond, R.D.; Hu, C.; Chung, J. Correlation between channel hot-electron degradation and radiation-induced interface trapping in MOS devices. IEEE Trans. Nucl. Sci. 1989, 36, 2140–2146. [Google Scholar] [CrossRef]

- Silvestri, M.; Gerardin, S.; Paccagnella, A.; Faccio, F.; Gonella, L. Channel hot carrier stress on irradiated 130-nm NMOSFETs. IEEE Trans. Nucl. Sci. 2008, 55, 1960–1967. [Google Scholar] [CrossRef]

- Silvestri, M.; Gerardin, S.; Paccagnella, A.; Faccio, F. Degradation induced by X-ray irradiation and channel hot carrier stresses in 130-nm NMOSFETs with enclosed layout. IEEE Trans. Nucl. Sci. 2008, 55, 3216–3223. [Google Scholar] [CrossRef]

- Zheng, Q.-W.; Cui, J.-W.; Zhou, H.; Yu, D.-Z.; Yu, X.-F.; Guo, Q. Hot-carrier effects on total dose irradiated 65 nm n-type metal-oxide-semiconductor field-effect transistors. Chin. Phys. Lett. 2016, 33, 076102. [Google Scholar] [CrossRef]

- Zhao, J.; Zheng, Q.; Cui, J.; Zhou, H.; Liang, X.; Yu, X.; Guo, Q. A study on effects of total ionizing dose on hot carrier effect of PD I/O SOI PMOSFETs. Results Phys. 2019, 13, 102223. [Google Scholar] [CrossRef]

- Lai, P.T.; Xu, J.P.; Wong, W.M.; Lo, H.; Cheng, Y. Correlation between hot-carrier-induced interface states and GIDL current increase in n-MOSFET’s. IEEE Trans. Electron. Devices 1998, 45, 521–528. [Google Scholar] [CrossRef]

- Groeseneken, G.; Degraeve, R.; Nigam, T.; Bosch, G.V.D.; Maes, H. Hot carrier degradation and time-dependent dielectric breakdown in oxides. Microelectron. Eng. 1999, 49, 27–40. [Google Scholar] [CrossRef]

- Zhou, H.; Liu, Y.; Zhang, Y. Total-ionizing-dose induced enhanced hot-carrier injection effect in the 130 nm partially depleted SOI I/O nMOSFETs. Jpn. J. Appl. Phys. 2020, 59, 031001. [Google Scholar] [CrossRef]

- Dai, M.; Song, Z.; Lin, C.-H.; Dong, Y.; Wu, T.; Chu, J. Multi-functional multi-gate one-transistor process-in-memory electronics with foundry processing and footprint reduction. Commun. Mater. 2022, 3, 41. [Google Scholar] [CrossRef]

- Schwank, J.R.; Ferlet-Cavrois, V.; Shaneyfelt, M.R.; Paillet, P.; Dodd, P. Radiation effects in SOI technologies. IEEE Trans. Nucl. Sci. 2003, 50, 522–538. [Google Scholar] [CrossRef]

- Paillet, P.; Herve, D.; Leray, J.L.; Devine, R. Evidence of negative charge trapping in high temperature annealed thermal oxide. IEEE Trans. Nucl. Sci. 1994, 41, 473–478. [Google Scholar] [CrossRef]

- Wang, T.; Chang, T.-E.; Huang, C. Interface trap induced thermionic and field emission current in off-state MOSFET’s. In Proceedings of the 1994 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 11–14 December 1994; IEEE: Piscataway, NJ, USA, 1994; pp. 161–164. [Google Scholar] [CrossRef]

- Majkusiak, B. Gate tunnel current in an MOS transistors. IEEE Trans. Electron. Devices 1990, 37, 1087–1092. [Google Scholar] [CrossRef]

- Tam, S.; Ko, P.-K.; Hu, C. Lucky-electron model of channel hot-electron injection in MOSFET’s. IEEE Trans. Electron. Devices 1984, 31, 1116–1125. [Google Scholar] [CrossRef]

- Tsuno, M.; Suga, M.; Tanaka, M.; Shibahara, K.; Miura-Mattausch, M.; Hirose, M. Physically-based threshold voltage determination for MOSFET’s of all gate lengths. IEEE Trans. Electron. Devices 1999, 46, 1429–1434. [Google Scholar] [CrossRef]

- Ortiz-Conde, A.; Sánchez, F.J.G.; Liou, J.J.; Cerdeira, A.; Estrada, M.; Yue, Y. A review of recent MOSFET threshold voltage extraction methods. Microelectron. Reliab. 2002, 42, 583–596. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lin, L.; Cong, Z.; Jia, C. Recovery Effect of Hot-Carrier Stress on γ-ray-Irradiated 0.13 μm Partially Depleted SOI n-MOSFETs. Electronics 2023, 12, 4233. https://doi.org/10.3390/electronics12204233

Lin L, Cong Z, Jia C. Recovery Effect of Hot-Carrier Stress on γ-ray-Irradiated 0.13 μm Partially Depleted SOI n-MOSFETs. Electronics. 2023; 12(20):4233. https://doi.org/10.3390/electronics12204233

Chicago/Turabian StyleLin, Lan, Zhongchao Cong, and Chunlei Jia. 2023. "Recovery Effect of Hot-Carrier Stress on γ-ray-Irradiated 0.13 μm Partially Depleted SOI n-MOSFETs" Electronics 12, no. 20: 4233. https://doi.org/10.3390/electronics12204233