In this section, we present a novel global routing algorithm that forms the core of our methodology. By utilizing a triangular grid graph and a maximum flow model, the algorithm efficiently discovers paths for global planning. The algorithm consists of four main stages. In the initial stage, we construct a global triangular grid graph, enabling us to effectively identify and utilize all available routing resources on the PCB. Moving to the second stage, we update the graph based on the determined routing order. In the third stage, we formulate the global routing problem as a maximum flow model. To solve this model, we employ the Edmonds–Karp algorithm [

22], which efficiently discovers the global routing.

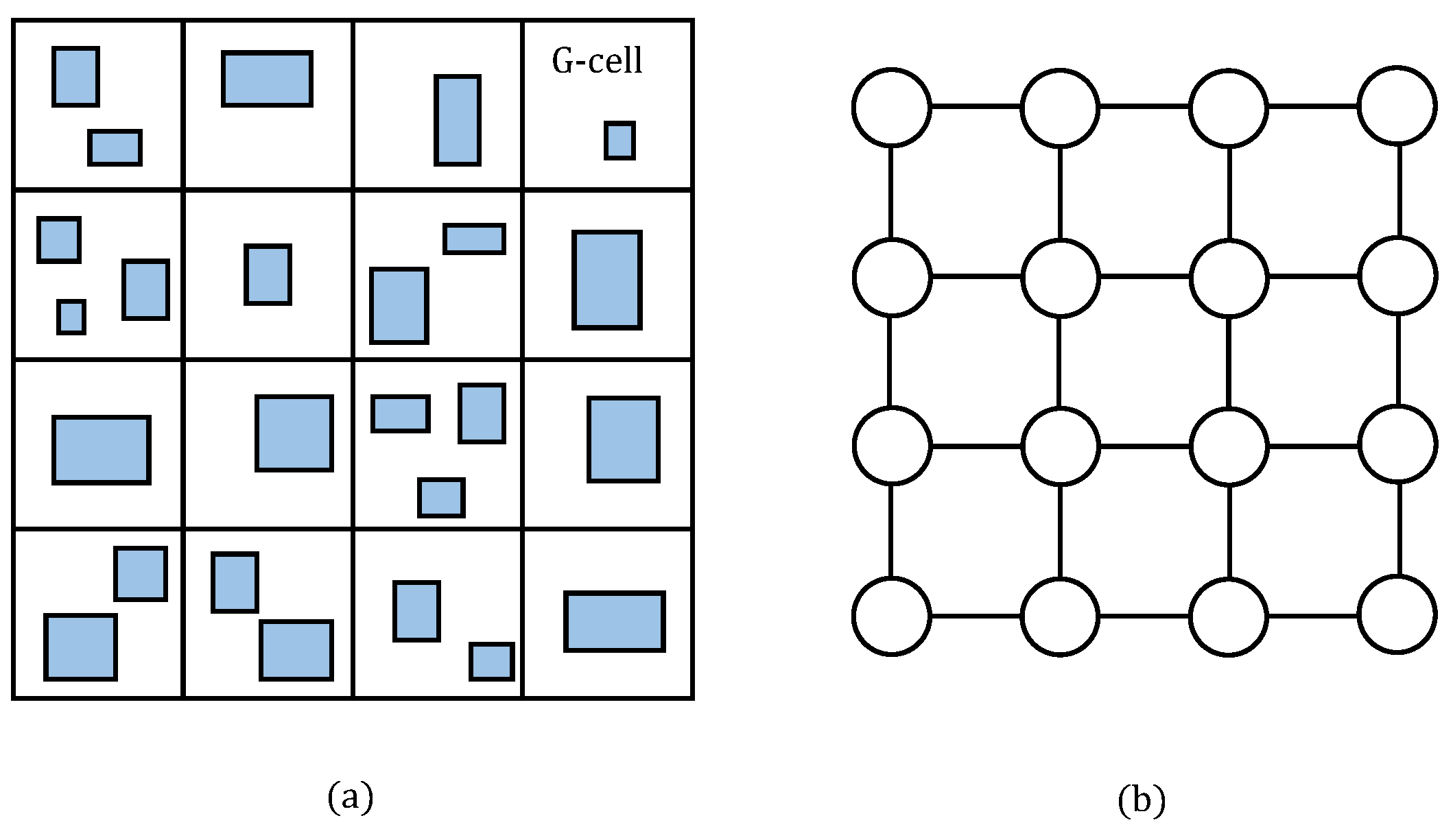

3.3.1. Triangular Grid Graph Construction

We consider all items on the printed circuit board as vertices in our diagram, including center points of pads, vias or obstacles, boundary vertices, and end points of tracks. These vertices are treated as obstacles, restricting direct passage. We then calculate the Euclidean distance between all pairs of vertices and sort them. Using an R-tree, we add edges to the graph and determine if they intersect with existing edges. Once all edges are constructed, we start from the first edge and traverse all connected vertices to build the first triangular face, and then we repeat this process to locate all triangular faces. We record all vertex, edge, and face relations as

and construct the triangular grid graph

, where

V represents the set of vertices,

E represents the set of edges, and

F represents the set of faces, as shown in

Figure 8.

We choose to use triangles instead of rectangles to reduce model size and simplify construction and calculation. Assuming there is only one pad in each footprint on the printed circuit board and n pads in total, the number of vertices generated in the triangular grid graph is . If we were to use a rectangle grid like the Hanan grid, we would need to include even more vertices—totaling over —as we would need to add the vertices of the boundary of each pad’s component. This would result in a great increase in the number of data needed to represent the graph. Furthermore, traversing each cell in the Hanan grid would take significantly longer than in the triangular grid.

3.3.2. Graph Local Modification

Our model not only supports the sequential routing of nets in a given order but also enables the simultaneous routing of multiple nets with adjacent starting and ending points. This is achieved by merging several nets into a super-net. Prior to routing, we must update the area where the starting and ending points are located. Using the triangular grid graph

G as a basis, we delete the vertices, edges, and faces where the starting and ending points reside. Then, we construct the smallest rectangular grid that can contain all starting points as the starting face, and the same is performed for the ending face. These rectangular faces are constructed to ensure that the paths are at a 90-degree angle from the starting or ending points, which facilitates subsequent path search and calculations. The remaining vertices are then reconnected to construct a new dynamic updating graph

, as shown in

Figure 9.

In

, we can identify edge sequences that represent the gaps and regions that the routing must traverse. Each face in

is viewed as a point, and the dual graph

of this graph is a flow network, as depicted in

Figure 10. In this network, the starting face serves as the source point and the ending face serves as the sink point. The direction of the network is always from the source point to the sink point, and the capacity of the network is defined as the maximum capacity allowed on each edge in

. Therefore,

can also be interpreted as a flow network model, where the vertices of

correspond to the faces of

and the edges of

pass through the edges of

.

3.3.3. Capacity Definition

In the graph

, the capacity of all edges should be determined based on the actual boundary of the PCB items corresponding to the vertices, rather than simply calculating the Euclidean distance between the two vertices on the edge.

Figure 11 illustrates this concept, where the vertices A and B correspond to rectangular items. We define the left-bottom coordinate and right-top coordinate of their boundary as

and

, respectively. The horizontal capacity, vertical capacity, and maximum capacity of this edge are denoted as

,

, and

, respectively, and they can be calculated as follows:

By applying these equations, we can obtain the preliminary capacity of all edges. However, in order to reduce the error, we need to calculate the capacity of edges that do not belong to the starting face and ending face a few more times. This is because there is a relationship among the capacities of each edge in a triangular grid. As shown in

Figure 11b, when calculating the capacity

of an edge

e, we consider the two adjacent triangular grids that share the edge, as well as the other edges

a,

b,

c, and

d of these grids. The capacity

can be calculated as follows:

By incorporating these iterative calculations, the capacity of the entire graph will reflect the actual boundaries of the PCB items more accurately. Consequently, this refined capacity estimation will yield improved results when searching for the maximum flow.

3.3.4. Global Routing Problem Modeling

We have provided the fundamental definition of the maximum flow model in

Section 2.1 and introduced our network flow model in

Section 3.3.2. Now, we can integrate the current global routing problem into our constructed model. The notation utilized in this section is summarized in

Table 1.

According to the graph

, we officially declare the global routing problem to be an integer linear programming (ILP) formulation as follows:

We propose a model for computing the optimal flow of nets in a given graph

, where each face of the graph represents a possible area for routing the nets. We define directed flows

as those where

i and

j correspond to the center points of two faces, and

is the edge shared by these faces. The decision variable

denotes whether net

k flows through the edge

, and it can only take values of 0 or 1. The objective function (

10) aims to minimize the cost of routing nets through the graph, where

is the cost of net

k on edge

, typically defined as the distance between

i and

j.

To ensure a feasible routing solution, we impose four constraints on the model. Constraints (10a) and (10b) ensure that the maximum flow of each net is limited, and the flow must follow the direction from the source to the sink . The maximum value of n corresponds to the total number of nets, in order to maximize the total flow. Constraint (10c) guarantees balance between the net flows entering and leaving each vertex, except for the source and sink vertices. This is the most fundamental constraint of the network flow model, ensuring that each net path is continuous from start to end. Finally, constraint (10d) limits the total flow of all nets on each edge, considering their capacity and the flow value of each net.

Due to the strict constraints and decision variables of the maximum flow problem, solving this ILP problem is NP-hard, requiring enormous time and computational resources. For a medium-sized PCB, the runtime may require several hours [

23]. To address this, we apply maximum flow algorithms to more efficiently solve the problem.

3.3.5. Maximum Flow Algorithm Pathfinding

A maximum flow can only be achieved through available edges from the starting face to the ending face. While obtaining the specific value of this maximum flow is not necessary, it is crucial to find all the augmenting paths of the graph. Our algorithm utilizes the Edmond–Karp (EK) algorithm, which employs the Breadth-First Search (BFS) method to locate these paths.

To begin, we use a minimum priority queue Q to store the visited face and its weight, sorting elements from smallest to largest by their weight. We set the starting face and its initial weight value and add it to Q. We then iterate through the elements in the queue, obtaining the current face and continuing to find adjacent faces, updating their weights, and adding them to the queue.

When the face reaches the ending face, we retrace all the visited faces to obtain the result of the augmenting path. Lastly, we update the flow value of all the edges that the path goes through. Each time we search for a net, we find an augmenting path.

Algorithm 2 provides the pseudo-code for our process.

| Algorithm 2 Our maximum flow algorithm |

Require: the dynamic updating triangular gird graph . Ensure: a triangular grid face augmenting path .

- 1:

Set minimum priority queue , the result of path , all attempt paths . - 2:

Set starting face , ending face , , mark the starting face as visited. - 3:

while

do - 4:

pick the first element . - 5:

Obtain all neighbor relations of . - 6:

for do - 7:

. - 8:

if then - 9:

. - 10:

. - 11:

, mark as visited. - 12:

if then - 13:

while do - 14:

Obtain all elements ending with . - 15:

Update the value of the flow through the edge between and . - 16:

. - 17:

return . - 18:

return not found.

|

In Algorithm 2, the includes several conditions:

Forward arc condition: The sum of the flow value of an edge and the new flow value cannot exceed the edge’s capacity.

Backward arc condition: The flow value of an edge cannot be less than the new net cost, i.e., the difference between the flow value and the net cost must be greater than or equal to zero.

Access condition: This face must not have been visited before.

The correctness of the max-flow algorithm can only be guaranteed if these three conditions are satisfied. The first two conditions are significant as they ensure the existence of augmented paths in the flow network, as discussed in Equation (

3). The calculation of the weight

is as follows.

where

represent the center of the next face

, the starting point, the ending point, the middle point of all starting points, and the middle point of all ending points, and their coordinates will be added to the calculation.

is the formula for calculating the Manhattan distance between two points:

The term refers to a guide line that connects directly from to . This guide line adjusts the weight of the faces it passes through to concentrate all wires in the intermediate region, thereby improving the utilization and routability of the routing area. The constants also play an important role in determining W. When , the algorithm’s result will be closer to the guide line. On the other hand, if is not much larger than and , the algorithm’s result depends more on a heuristic search, which may deviate significantly from the expected outcome and require more time.

The algorithm is called in a loop. Once augmented paths in the form of triangular grids are found for all nets, the flow values on edges of are updated, and the directions of flows passing through all edges roughly follow from the source point to the sink point. The time complexity of the algorithm is , where m is the number of nets and n is the number of faces in the graph .

3.3.6. Flow Decomposition

We utilize flow decomposition to extract the approximate set of routing paths for each net. This technique enables us to determine the number and direction of flows that can pass through each edge, based on the flow value and previously obtained face paths. In triangular grids, there are only three simple cases of flow direction on each triangular face, as illustrated in

Figure 12.

Based on the three aforementioned cases, our triangular grid algorithm has an edge over rectangular ones as it can easily decompose flow. In rectangular grids, the number and direction of flow in each of the four edges make the situations to be discussed more numerous and complicated. To avoid crossing during decomposition, we follow the “same direction principle”. We start by obtaining the first starting point

, the first ending point

, and the last ending point

, and then we obtain a cross product

:

In a triangular grid face, we obtain the midpoint

of the current edge

and the midpoint

on the other two edges

of the face, and we obtain another cross product

:

If the directions of and are the same, the situation indicates that vectors to and to have been rotated clockwise or counterclockwise in the same direction. We choose to use edge for flow decomposition, and if it is not feasible, edge is chosen. We then subtract the flow value of the chosen edge from the total flow value of the wire which includes the wire width and spacing to ensure that the decomposed path satisfies the constraints. If the flow value of one of the edges is 0, we consider choosing the other edge. We ensure that paths starting from other starting points are as similar as possible to paths that have been in decomposition in turn and there is no crossover. Finally, we obtain the planned paths of all wires, which can be used in future detail routing. These paths are added to the triangular grid graph and partake in the global routing of the rest of the unrouted nets.