Asymmetric 5.5 GHz Three-Stage Voltage-Controlled Ring-Oscillator in 65 nm CMOS Technology

Abstract

:1. Introduction

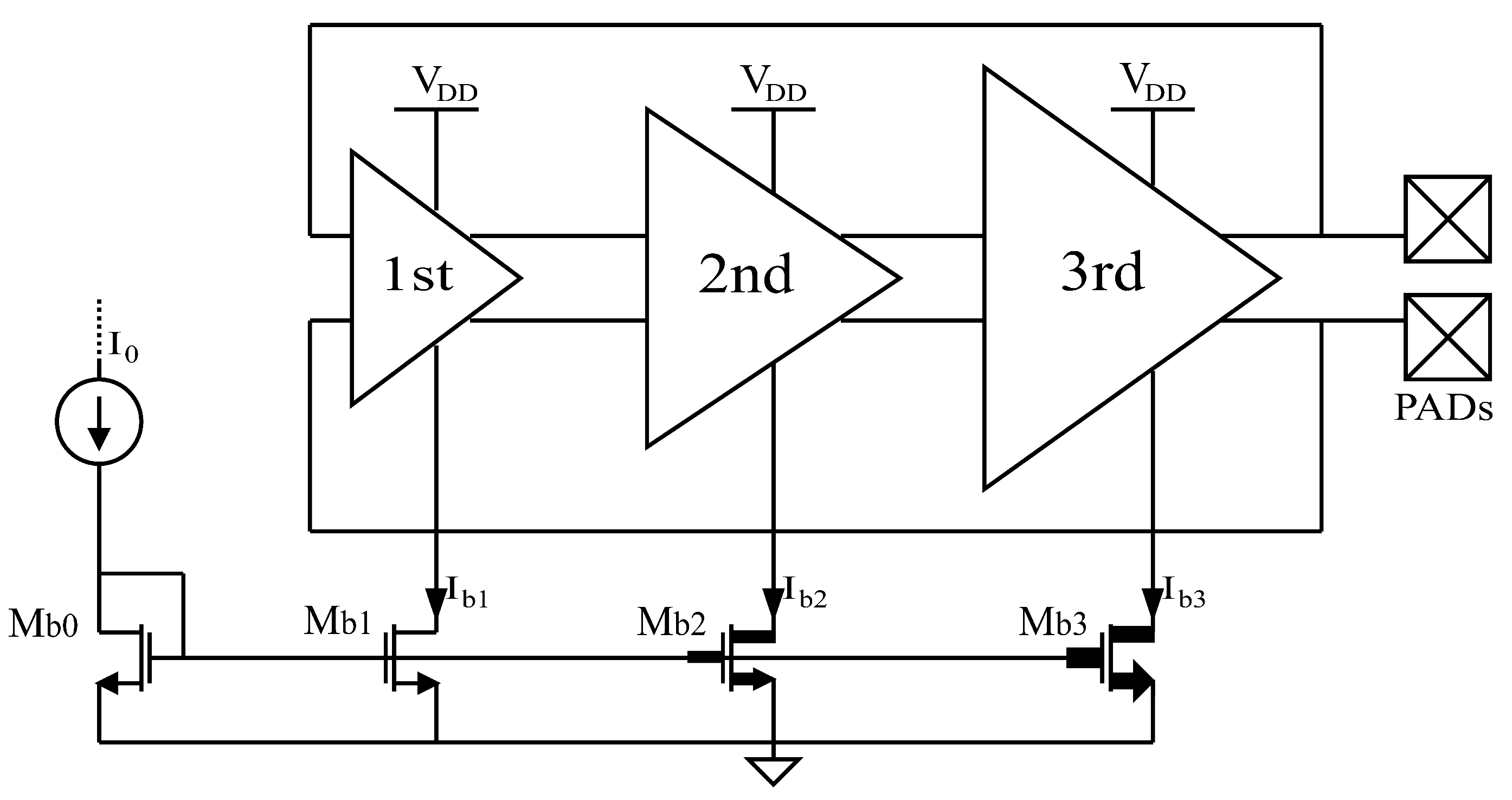

2. System Model of the Proposed RO-VCO

3. Schematic Design of the RO-VCO

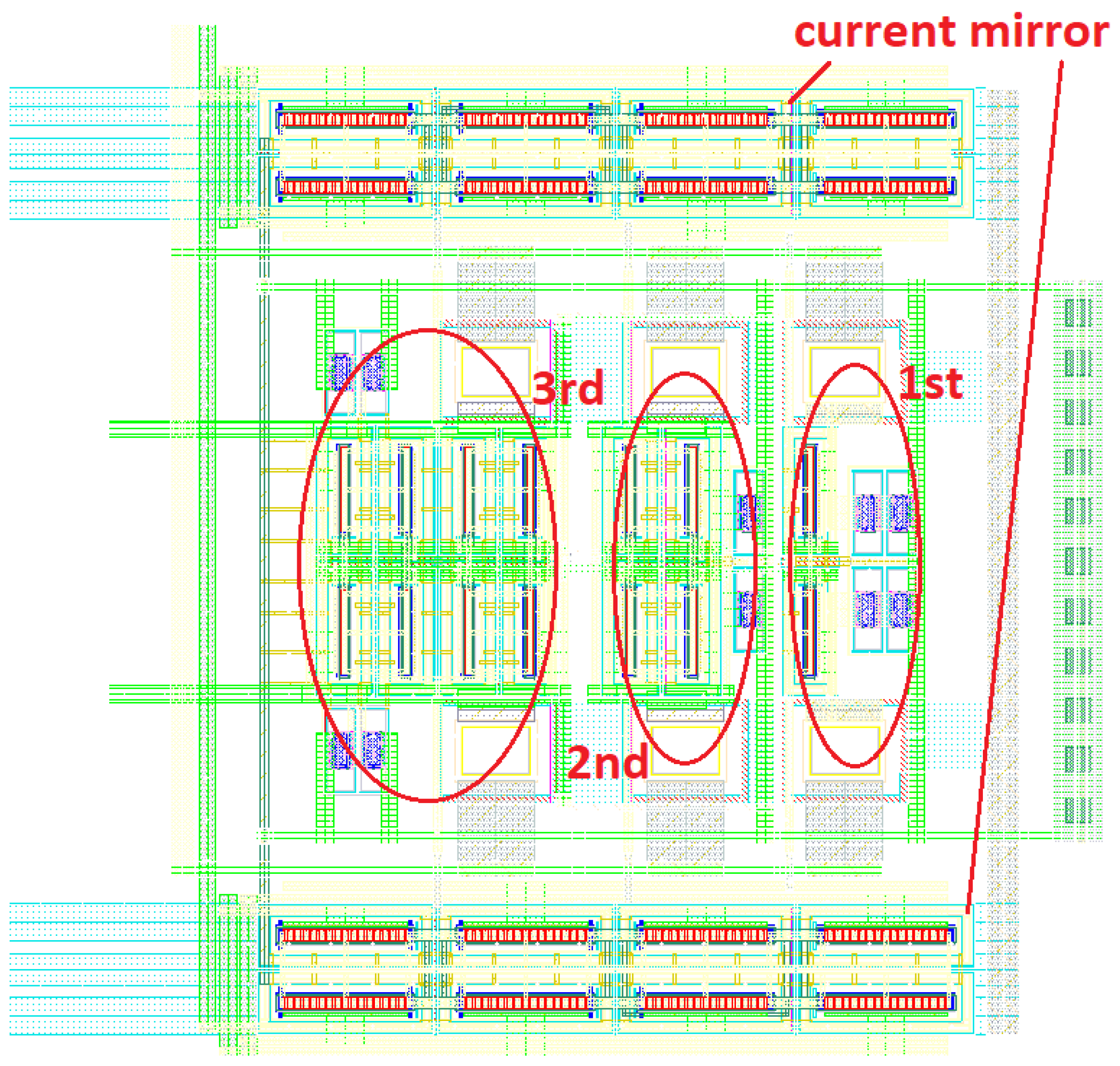

4. Layout Design of the RO-VCO

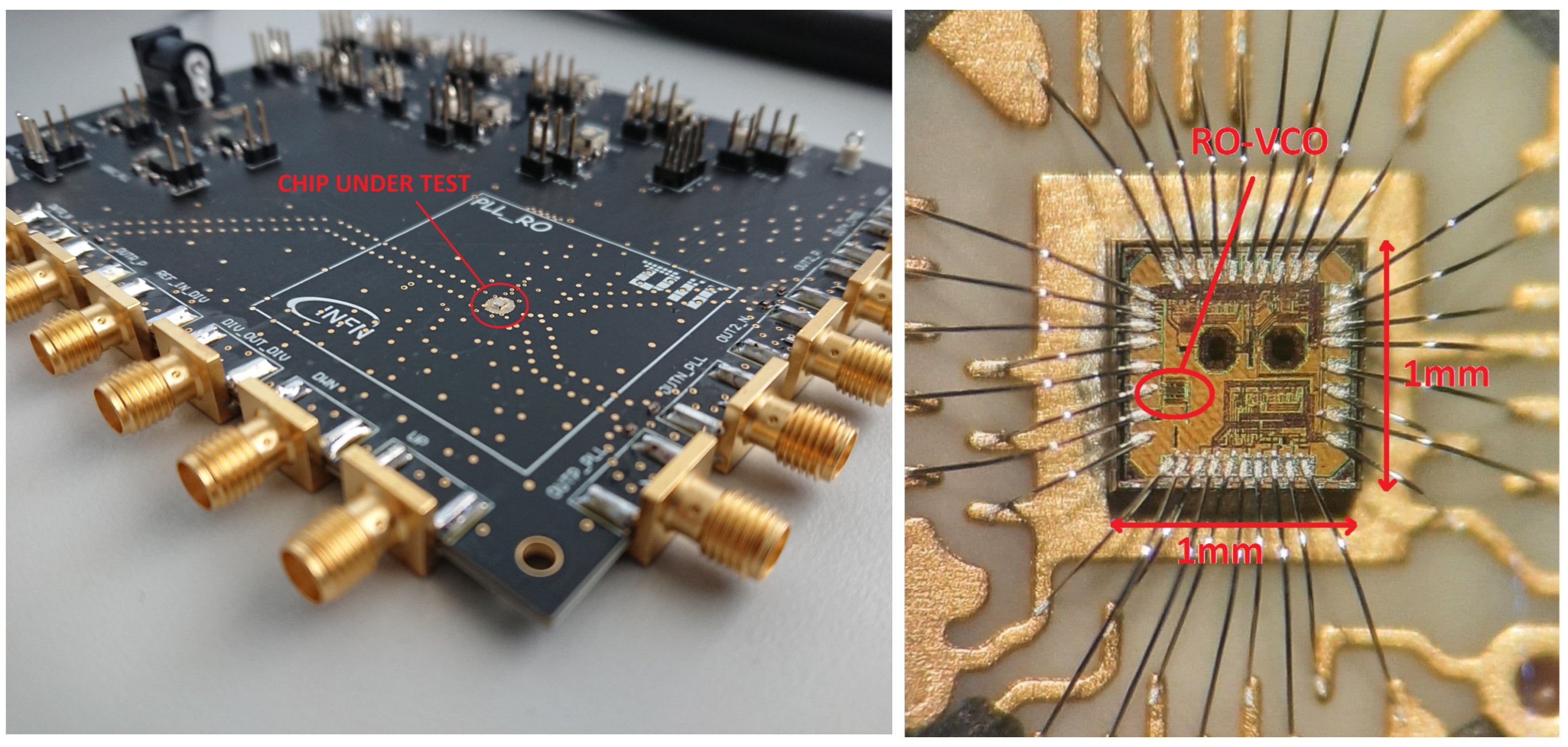

5. Experimental Characterization

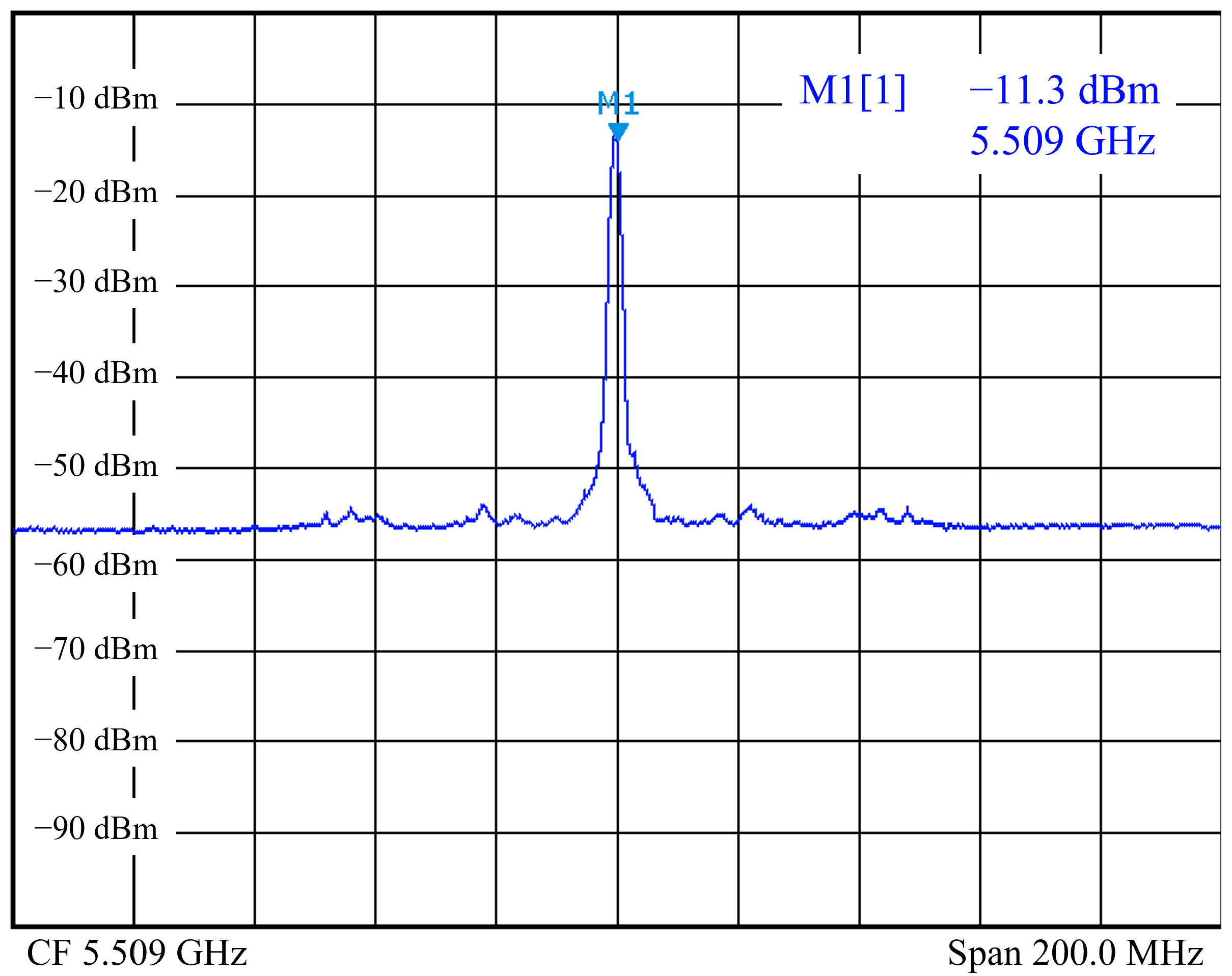

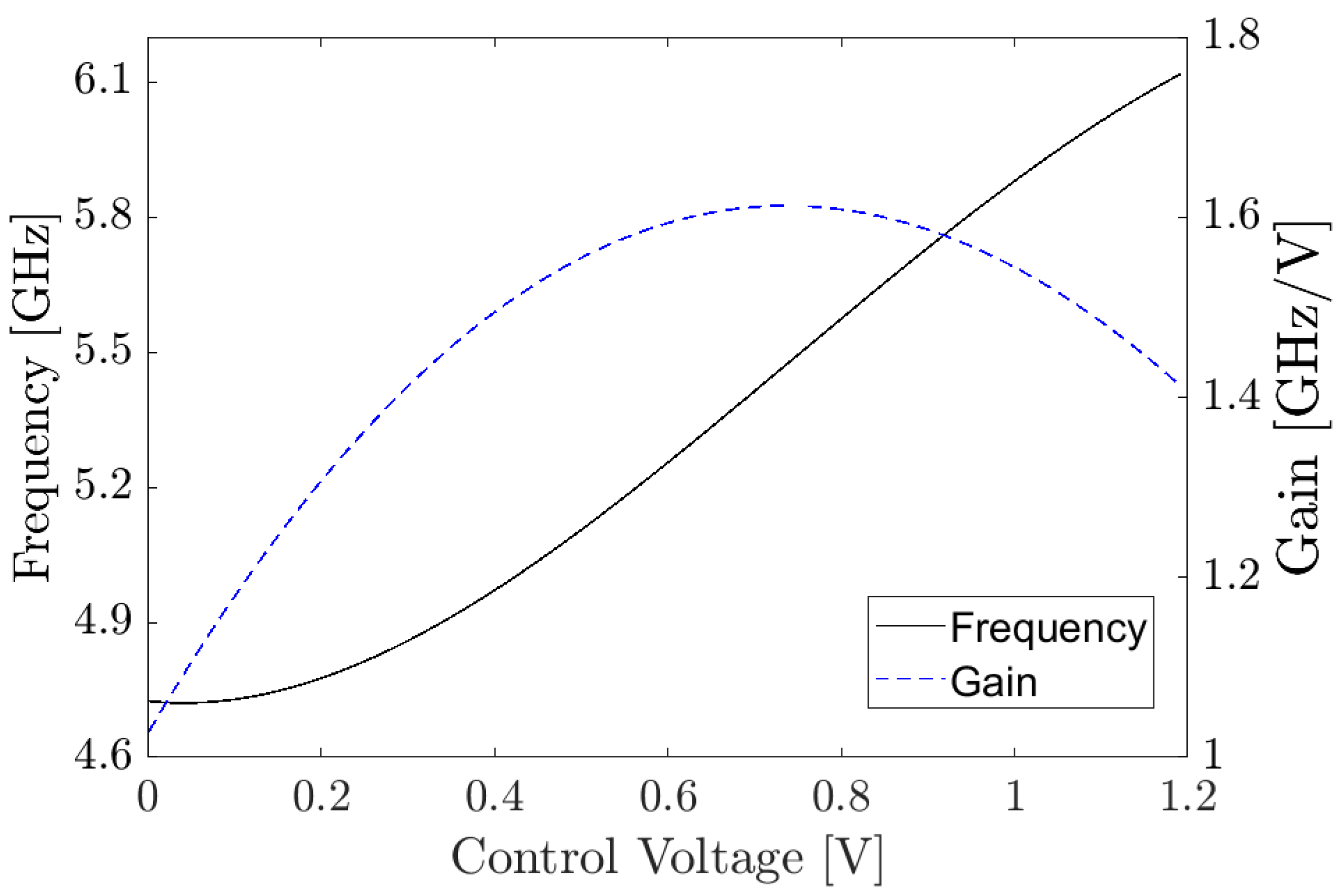

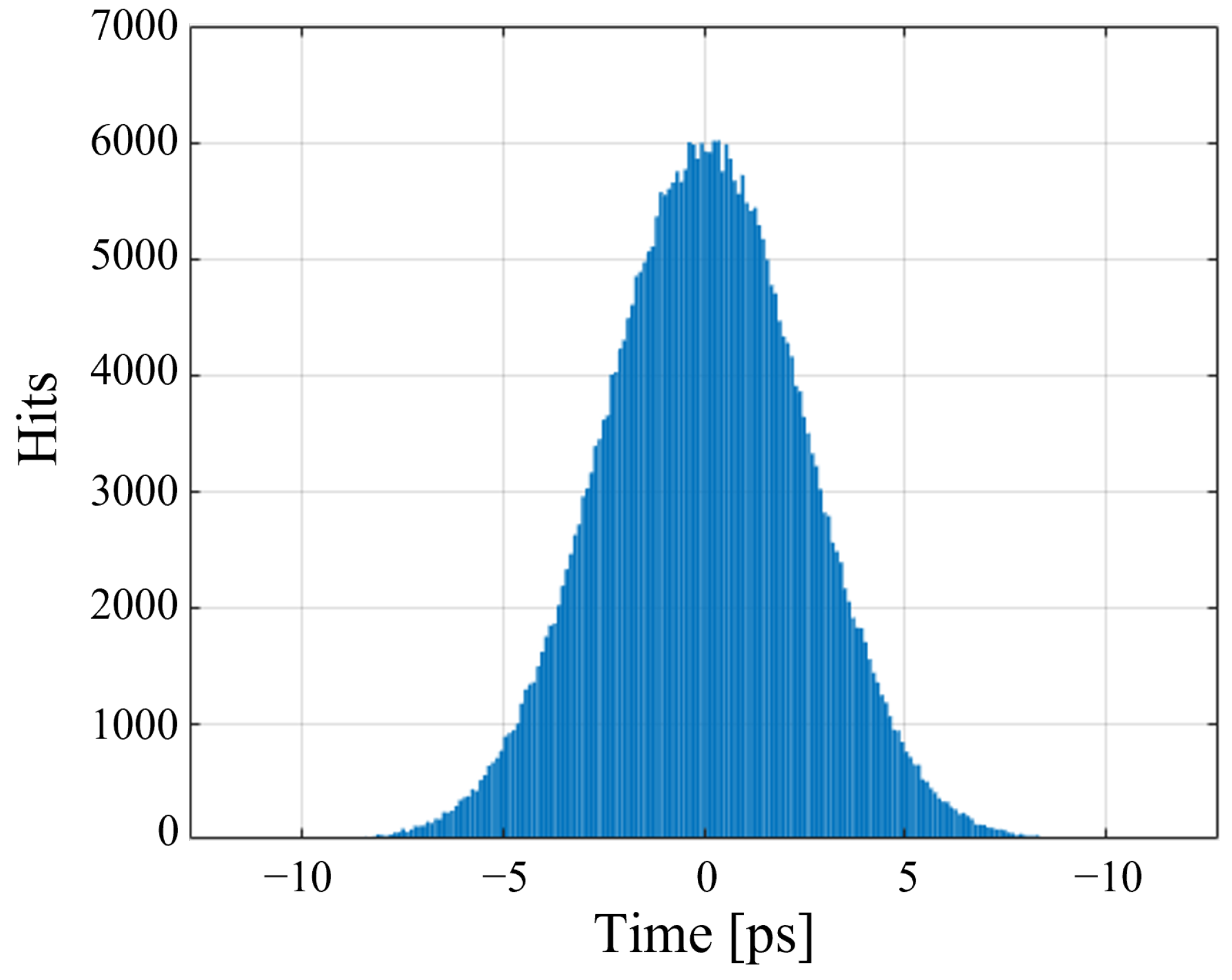

5.1. Electrical Characterization

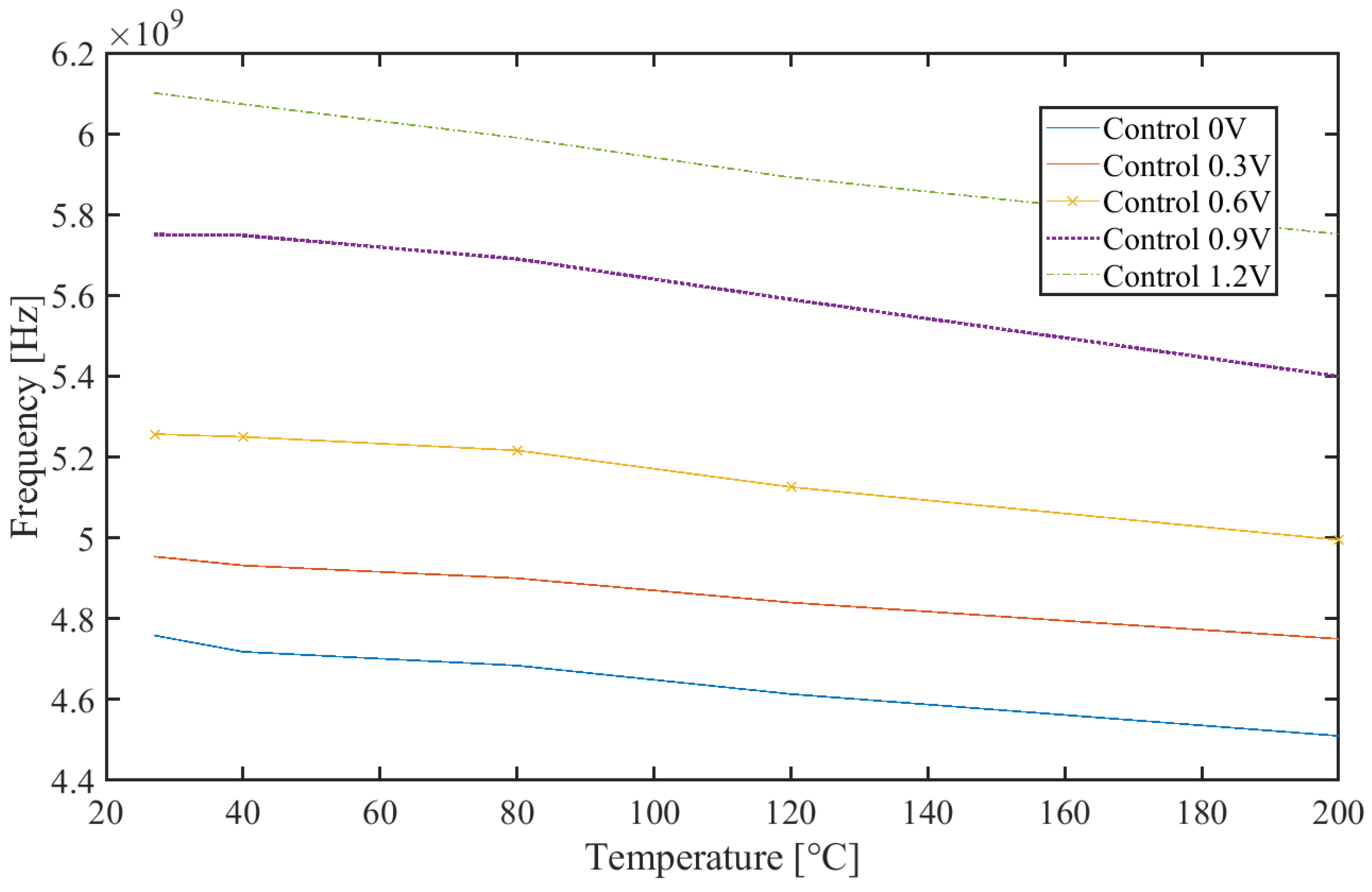

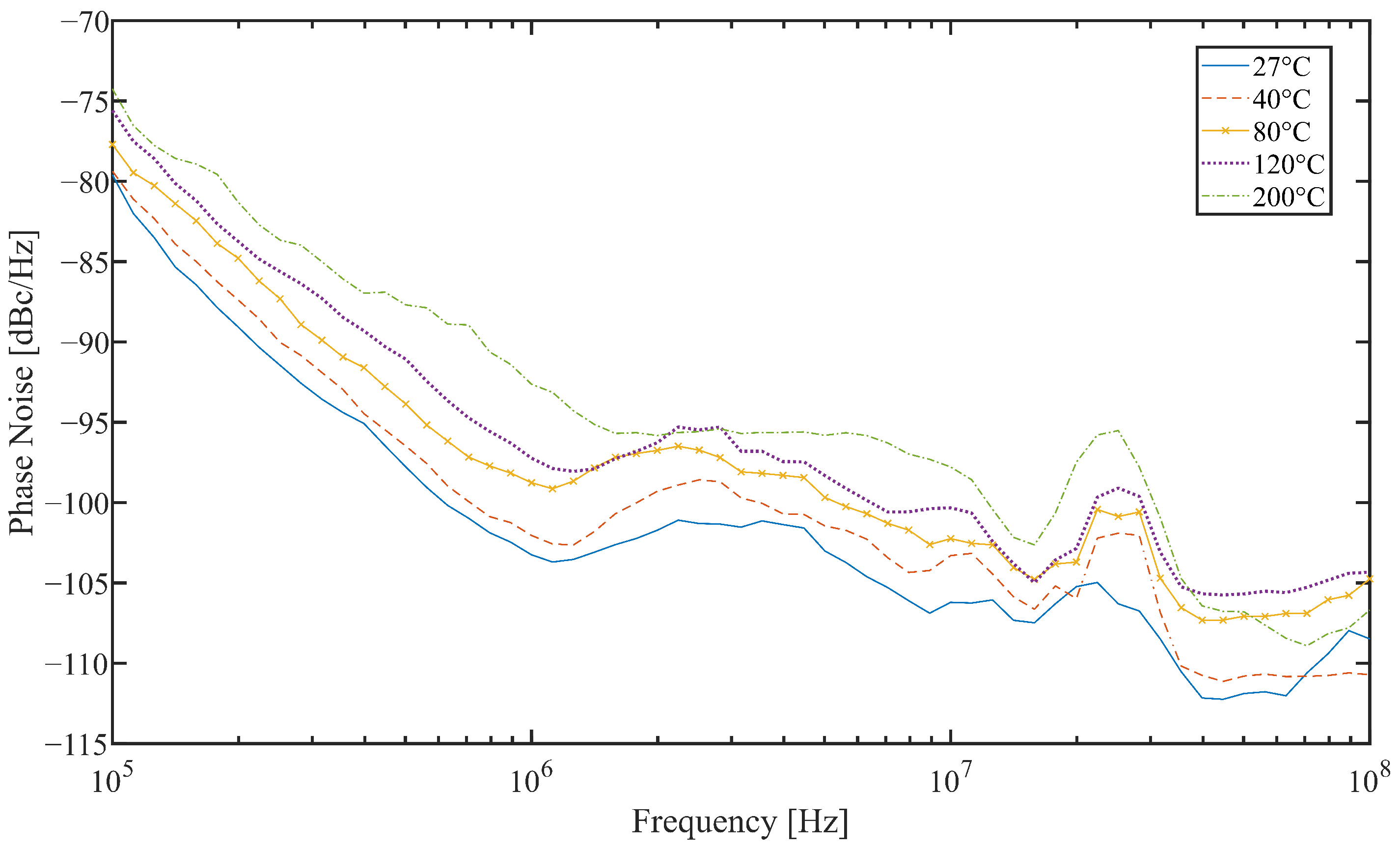

5.2. Thermal Characterization

6. State-of-the-Art Comparison

7. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Dubitzky, W.; Kurowski, K.; Schott, B. Large-Scale Computing Techniques for Complex System Simulations; John Wiley & Sons: Hoboken, NJ, USA, 2012. [Google Scholar]

- Buchty, R.; Heuveline, V.; Karl, W.; Weiss, J.-P. A survey on hardware-aware and heterogeneous computing on multicore processors and accelerators. Concurr. Comput. Pract. Exp. 2012, 24, 663–675. [Google Scholar] [CrossRef]

- Karimi, N.; Kong, Z.; Chakrabarty, K.; Gupta, P.; Patil, S. Testing of Clock-Domain Crossing Faults in Multi-core System-on-Chip. In Proceedings of the 2011 Asian Test Symposium, New Delhi, India, 20–23 November 2011; pp. 7–14. [Google Scholar]

- Adetomi, A.; Enemali, G.; Arslan, T. Clock buffers, nets, and trees for on-chip communication: A novel network access technique in FPGAs. In Proceedings of the 2017 IEEE International Parallel and Distributed Processing Symposium Workshops, Lake Buena Vista, FL, USA, 29 May 2017–2 June 2017; pp. 219–222. [Google Scholar]

- Restle, P.J.; McNamara, T.G.; Webber, D.A.; Camporese, P.J.; Eng, K.F.; Jenkins, K.A.; Allen, D.H.; Rohn, M.J.; Quaranta, M.P.; Boerstler, D.W.; et al. A clock distribution network for microprocessors. In Proceedings of the IEEE JSSC, Honolulu, HI, USA, 15–17 June 2000; Volume 36, pp. 792–799. [Google Scholar]

- Deutsch, A.; Kopcsay, G.V.; Restle, P.J.; Smith, H.H.; Katopis, G.; Becker, W.D.; Coteus, P.W.; Surovic, C.W.; Rubin, B.J.; Dunne, R.P.; et al. When are transmission-line effects important for on-chip interconnections? IEEE Trans. Microw. Theory Tech. 1997, 45, 1836–1846. [Google Scholar]

- Farshidi, A.; Behjat, L.; Rakai, L. David Westwick A Multiobjective Cooptimization of Buffer and Wire Sizes in High-Performance Clock Trees. IEEE Trans. Circuits Syst. II Express Briefs 2017, 64, 412–416. [Google Scholar]

- Mestice, M.; Neri, B.; Ciarpi, G.; Saponara, S. Analysis and Design of Integrated Blocks for a 6.25 GHz Spacefibre PLL. Sensors 2020, 20, 4013. [Google Scholar] [CrossRef]

- Li, P.; Tian, T.; Wu, B.; Ye, T. A Novel Self-Biased Phase-Locked Loop Scheme for WLAN Applications. Electronics 2021, 10, 2077. [Google Scholar]

- Danilo, M.; Gabriele, C.; Sergio, S. Design and Verification of a 6.25 GHz LC-Tank VCO integrated in 65 nm CMOS Technology Operating 340 up to 1 Grad TID. IEEE Trans. Nucl. Sci. 2021, 68, 2524–2532. [Google Scholar]

- Ciarpi, G.; Puccioni, G.; Mestice, M.; Monda, D.; Rossi, D.; Saponara, S. A 2 GHz Wide Tuning Range LC-Tank Digitally Controlled Oscillator in 28 nm CMOS Technology. In Applications in Electronics Pervading Industry, Environment and Society: APPLEPIES; Springer International Publishing: Cham, Switzerland, 2023; in press. [Google Scholar]

- Monda, D.; Ciarpi, G.; Saponara, S. Analysis and Comparison of Rad-Hard Ring and LC-Tank Controlled Oscillators in 65 nm for SpaceFibre Applications. Sensors 2020, 20, 4612. [Google Scholar] [CrossRef]

- Mestice, M.; Biondi, G.; Ciarpi, G.; Rossi, D.; Saponara, S. A Low-Area, Low-Power, Wide Tuning Range Digitally Controlled Oscillator for Power Management Systems in 28 nm CMOS technology. In Applications in Electronics Pervading Industry, Environment and Society: APPLEPIES; Springer International Publishing: Cham, Switzerland, 2023; in press. [Google Scholar]

- Farahabadi, P.M.; Miar-Naimi, H.; Ebrahimzadeh, A. Closed-form analytical equations for amplitude and frequency of high-frequency CMOS ring oscillators. IEEE Trans. Circuits Syst. I Regul. Pap. 2009, 56, 2669–2677. [Google Scholar] [CrossRef]

- Voinigescu, S. High-Frequency Integrated Circuits; Cambridge University Press: Cambridge, UK, 2013. [Google Scholar]

- Monda, D.; Ciarpi, G.; Saponara, S. Analysis and Comparison of Ring and LC-tank Oscillators for 65 nm Integration of Rad-Hard VCO for SpaceFibre Applications. Sensors 2020, 627, 25–32. [Google Scholar]

- Jin, J.; Jin, Y.; Gan, Y. A 500 kHz to 150 MHz Multi-Output Clock Generator Using Analog PLL and Open-Loop Fractional Divider with 0.13 µm CMOS. Electronics 2022, 11, 2347. [Google Scholar]

- Chen, Q.; Shan, Q.; Wei, Z.; Wang, X.; Huang, S.; Liu, Y. A Low-Power ADPLL with Calibration-Free RO-Based Injection-Locking TDC for BLE Applications. Electronics 2022, 11, 1953. [Google Scholar] [CrossRef]

- Alvero-Gonzalez, L.M.; Medina, V.; Kampus, V.; Paton, S.; Hernandez, L.; Gutierrez, E. Ring-Oscillator with Multiple Transconductors for Linear Analog-to-Digital Conversion. Electronics 2021, 10, 1408. [Google Scholar] [CrossRef]

- Heydari, P. Design and analysis of low-voltage current-mode logic buffers. In Proceedings of the Fourth International Symposium on Quality Electronic Design, San Jose, CA, USA, 24–26 March 2003; pp. 293–298. [Google Scholar]

- Saponara, S.; Ciarpi, G. Electrical, Electromagnetic, and Thermal Measurements of 2-D and 3-D Integrated DC/DC Converters. IEEE Trans. Instrum. Meas. 2018, 67, 1078–1090. [Google Scholar] [CrossRef]

- Zhang, C.; Li, Z.; Fang, J.; Zhao, J.; Guo, Y.; Chen, J. A novel high-speed CMOS fully-differential ring VCO. In Proceedings of the 12th IEEE International Conference on Solid-State and Integrated Circuit Technology, Guilin, China, 28–31 October 2014; pp. 1372–1375. [Google Scholar]

- Goyal, B.; Suman, S.; Ghosh, P.K. Design and analysis of improved performance ring VCO based on differential pair configuration. In Proceedings of the International Conference on Electrical, Electronics, and Optimization Techniques (ICEEOT), Chennai, India, 3–5 March 2016; pp. 3468–3472. [Google Scholar]

- Kinger, B.; Suman, S.; Sharma, K.G.; Ghosh, P.K. Design of Improved Performance Voltage Controlled Ring Oscillator. In Proceedings of the Fifth International Conference on Advanced Computing & Communication Technologies, Haryana, India, 21–22 February 2015; pp. 441–445. [Google Scholar]

- Suman, S.; Sharma, K.G.; Ghosh, P.K. Design of PLL using improved performance ring VCO. In Proceedings of the International Conference on Electrical, Electronics, and Optimization Techniques (ICEEOT), Chennai, India, 3–5 March 2016; pp. 3478–3483. [Google Scholar]

- Liu, H.Q.; Goh, W.L.; Siek, L.; Lim, W.M.; Zhang, Y.P. A Low-Noise Multi-GHz CMOS Multiloop Ring Oscillator with Coarse and Fine Frequency Tuning. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2009, 17, 571–577. [Google Scholar]

- Coombs, D.; Elkholy, A.; Nandwana, R.K.; Elmallah, A.; Hanumolu, P.K. A 2.5-to-5.75 GHz 5 mW 0.3 psrms-jitter cascaded ring-based digital injection-locked clock multiplier in 65 nm CMOS. In Proceedings of the 2017 IEEE ISSCC, San Francisco, CA, USA, 5–9 February 2017; pp. 152–153. [Google Scholar]

- Yen, C.; Nasrollahpour, M.; Hamedi-Hagh, S. Low-power and high-frequency ring oscillator design in 65 nm CMOS technology. In Proceedings of the IEEE 12th International Conference on ASIC (ASICON), Guiyang, China, 25–28 October 2017; pp. 533–536. [Google Scholar]

- Samaras, D.; Tsimpos, A.; Hatzopoulos, A. A novel wide frequency range 65 nm CMOS VCO. In Proceedings of the 2022 IFIP/IEEE 30th International Conference on Very Large Scale Integration (VLSI-SoC), Patras, Greece, 3–5 October 2022; pp. 1–4. [Google Scholar]

- Samaras, D.; Hatzopoulos, A. High performance, wide tuning range 65 nm CMOS tunable Voltage Controlled Ring Oscillator up to 11 GHz. In Proceedings of the 2020 9th International Conference on Modern Circuits and Systems Technologies (MOCAST), Bremen, Germany, 7–9 September 2020; pp. 1–4. [Google Scholar]

- Askari, S.; Saneei, M.; Salem, S. Design and Analysis of Wide Tuning Range Ring VCO in 65 nm CMOS Technology. Radioelectron. Commun. Syst. 2019, 62, 232–240. [Google Scholar]

| Name | W | L | Values |

|---|---|---|---|

| 24 µm | 60 nm | - | |

| - | - | 640 | |

| 48 µm | 60 nm | - | |

| - | - | 320 | |

| 96 µm | 60 nm | - | |

| - | - | 160 | |

| - | - | 350 fF | |

| 89.6 µm | 240 nm | - | |

| 89.6 µm | 240 nm | - | |

| 179.2 µm | 240 nm | - | |

| 358.4 µm | 240 nm | - |

| Ref. | [22] | [23] | [24,25] | [26] | [27] |

|---|---|---|---|---|---|

| Technology (nm) | 180 | 180 | 130 | 130 | 65 |

| Frequency Range (GHz) | 4.9–5.9 | 5.3–6.6 | 2.2–3.5 | 7.30–7.86 | 2.5–5.75 |

| Silicon Area (mm2) | n.a. | 3.18 × 10 | n.a. | 1.6 × 10 | 9.0 × 10 |

| Power Consumption (mW) | 8.1 | 2.9–6.8 | 0.031–0.052 | 60 | 5.3 |

| Extra Output Buffer Needed | yes | yes | yes | yes | yes |

| Phase Noise @ 1 MHz (dBc/Hz) | −86.7 | n.a. | n.a. | −103.4 | −113 |

| Maximum Temperature (°C) | n.a. | n.a. | n.a. | n.a. | n.a. |

| Data Type | Simul. | Simul. | Simul. | Meas. | Meas. |

| FoM @ 1 MHz (dBc/Hz) | n.a. | n.a. | n.a. | −181 | −185.5 |

| Ref. | [28] | [29] | [30] | [31] | This work |

| Technology (nm) | 65 | 65 | 65 | 65 | 65 |

| Frequency Range (GHz) | 3.7–6.5 | 2.75–5.7 | 2.4–11 | 4.25–21.31 | 4.7–6.1 |

| Silicon Area (mm2) | 1.10 × 10−2 | n.a. | n.a | 5.4 × 10 | 1.00 × 10 |

| Power Consumption (mW) | 2.3 | 29 | 20 | 33.13 | 15.45 |

| Extra Output Buffer Needed | yes | yes | yes | yes | integrated |

| Phase Noise @ 1 MHz (dBc/Hz) | −71.0 | −78.13 | −90.08 | −90.47 | −103.2 |

| Maximum Temperature (°C) | n.a. | 125 | n.a. | 75 | 200 |

| Data Type | Simul. | Simul. | Simul. | Simul. | Meas. |

| FoM @ 1 MHz (dBc/Hz) | −161.8 | n.a | n.a. | −180.5 | −186 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ciarpi, G.; Monda, D.; Mestice, M.; Rossi, D.; Saponara, S. Asymmetric 5.5 GHz Three-Stage Voltage-Controlled Ring-Oscillator in 65 nm CMOS Technology. Electronics 2023, 12, 778. https://doi.org/10.3390/electronics12030778

Ciarpi G, Monda D, Mestice M, Rossi D, Saponara S. Asymmetric 5.5 GHz Three-Stage Voltage-Controlled Ring-Oscillator in 65 nm CMOS Technology. Electronics. 2023; 12(3):778. https://doi.org/10.3390/electronics12030778

Chicago/Turabian StyleCiarpi, Gabriele, Danilo Monda, Marco Mestice, Daniele Rossi, and Sergio Saponara. 2023. "Asymmetric 5.5 GHz Three-Stage Voltage-Controlled Ring-Oscillator in 65 nm CMOS Technology" Electronics 12, no. 3: 778. https://doi.org/10.3390/electronics12030778

APA StyleCiarpi, G., Monda, D., Mestice, M., Rossi, D., & Saponara, S. (2023). Asymmetric 5.5 GHz Three-Stage Voltage-Controlled Ring-Oscillator in 65 nm CMOS Technology. Electronics, 12(3), 778. https://doi.org/10.3390/electronics12030778