A Novel Word Line Driver Circuit for Compute-in-Memory Based on the Floating Gate Devices

Abstract

1. Introduction

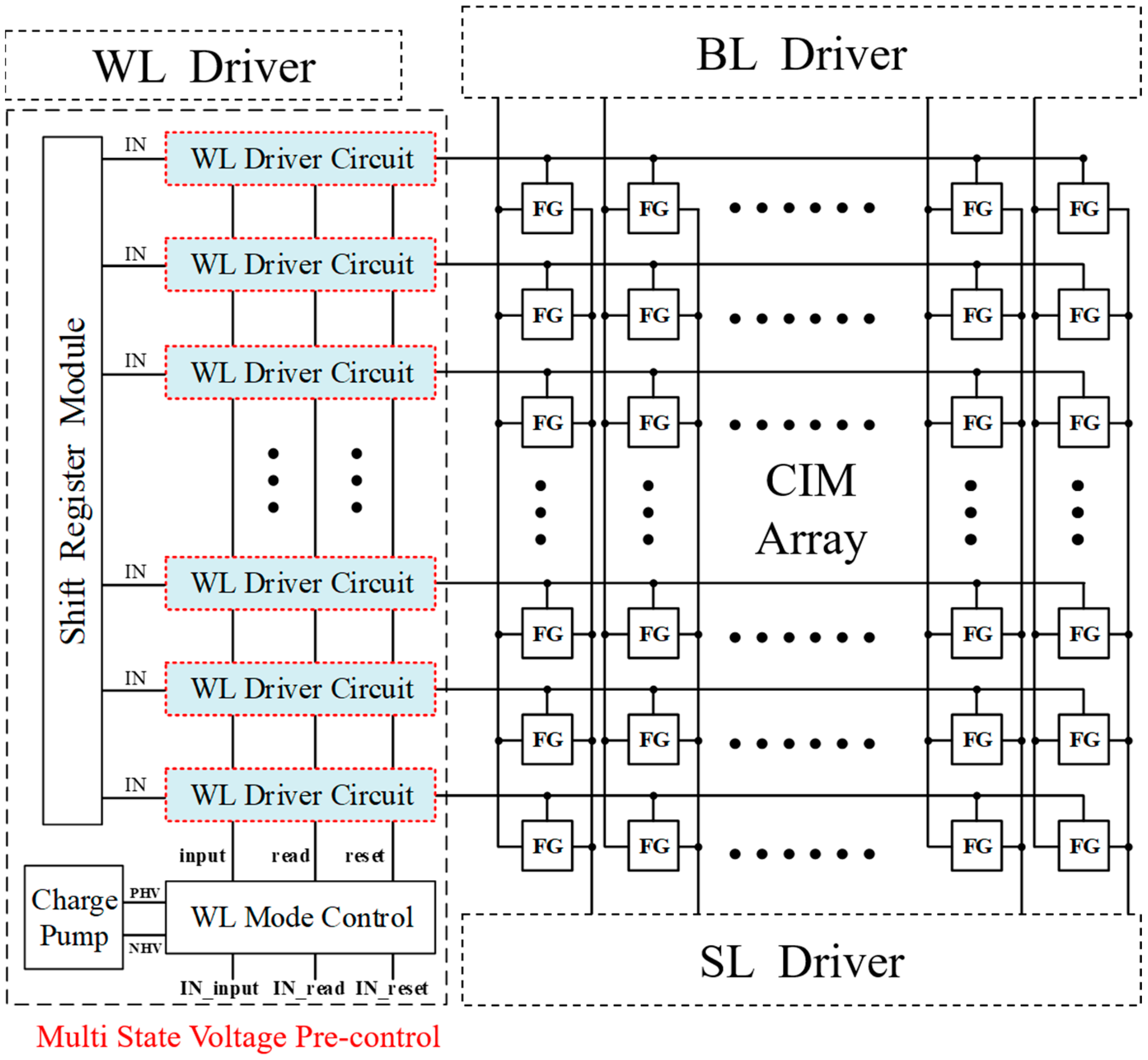

2. Proposed WLDC for CIM

2.1. Architecture of the CIM Array WLDC

2.2. Conventional WLDC Based on Level Shifter

2.3. Proposed NovelWLDC

2.3.1. The Principle of Weight Writing and Convolution Operation

2.3.2. The Principle of Weight Erasing

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Sze, V.; Chen, Y.H.; Emer, J.; Suleiman, A.; Zhang, Z. Hardware for Machine Learning: Challenges and Opportunities. In Proceedings of the 2017 IEEE Custom Integrated Circuits Conference (CICC), Austin, TX, USA, 30 April–3 May 2017; pp. 1–8. [Google Scholar] [CrossRef]

- Sahay, S.; Bavandpour, M.; Mahmoodi, M.R.; Strukov, D. Energy-Efficient Moderate Precision Time-Domain Mixed-Signal Vector-by-Matrix Multiplier Exploiting 1T-1R Arrays. IEEE J. Explor. Solid-State Comput. Devices Circuits 2020, 6, 18–26. [Google Scholar] [CrossRef]

- Rizzo, T.; Strangio, S.; Iannaccone, G. Time Domain Analog Neuromorphic Engine Based on High-Density Non-Volatile Memory in Single-Poly CMOS. IEEE Access 2022, 10, 49154–49166. [Google Scholar] [CrossRef]

- Shukla, P.; Muralidhar, A.; Iliev, N.; Tulabandhula, T.; Fuller, S.B.; Trivedi, A.R. Ultralow-Power Localization of Insect-Scale Drones: Interplay of Probabilistic Filtering and Compute-in-Memory. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2022, 30, 68–80. [Google Scholar] [CrossRef]

- Kim, S.; Baek, M.H.; Hwang, S.; Jang, T.; Park, K.; Park, B.G. A Novel Vector-matrix Multiplication (VMM) Architecture based on NAND Memory Array. J. Semicond. Technol. Sci. 2020, 20, 242–248. [Google Scholar] [CrossRef]

- Paliy, M.; Strangio, S.; Ruiu, P.; Rizzo, T.; Iannaccone, G. Analog Vector-Matrix Multiplier Based on Programmable Current Mirrors for Neural Network Integrated Circuits. IEEE Access 2020, 8, 203525–203537. [Google Scholar] [CrossRef]

- Yan, B.; Yang, Q.; Chen, W.H.; Chang, K.T.; Su, J.W.; Hsu, C.H.; Li, S.H.; Lee, H.Y.; Sheu, S.S.; Ho, M.S.; et al. RRAM-based Spiking Nonvolatile Computing-In-Memory Processing Engine with Precision-Configurable In Situ Nonlinear Activation. In Proceedings of the 2019 Symposium on VLSI Technology, Kyoto, Japan, 9–14 June 2019; pp. T86–T87. [Google Scholar] [CrossRef]

- Ma, C.; Ji, Y.; Qiao, C.; Zhou, T.; Qi, L.; Li, Y. An Energy-Efficient Level Shifter Using Time Borrowing Technique for Ultra Wide Voltage Conversion from Sub-200mV to 3.0V. In Proceedings of the 2021 IEEE International Symposium on Circuits and Systems (ISCAS), Daegu, Republic of Korea, 22–28 May 2021; pp. 1–5. [Google Scholar] [CrossRef]

- Cha, H.K.; Zhao, D.N.; Cheong, J.H.; Guo, B.; Yu, H.B.; Je, M. A CMOS High-Voltage Transmitter IC for Ultrasound Medical Imaging Applications. IEEE Trans. Circuits Syst. II-Express Briefs 2013, 60, 316–320. [Google Scholar] [CrossRef]

- Palomeque, M.D.; Rodriguez, V.A.; Delgado, R.M. A High-Voltage Floating Level Shifter for A Multi-Stage Charge-Pump in A Standard 1.8 V/3.3 V CMOS Process. Aeu-Int. J. Electron. Commun. 2022, 156, 154389. [Google Scholar] [CrossRef]

- Zhao, W.; Alvarez, A.B.; Ha, Y. A 65-nm 25.1-ns 30.7-fJ Robust Subthreshold Level Shifter With Wide Conversion Range. IEEE Trans. Circuits Syst. II Express Briefs 2015, 62, 671–675. [Google Scholar] [CrossRef]

- Xie, S.; Ni, C.; Sayal, A.; Jain, P.; Hamzaoglu, F.; Kulkarni, J.P. 16.2 eDRAM-CIM: Compute-In-Memory Design with Reconfigurable Embedded-Dynamic-Memory Array Realizing Adaptive Data Converters and Charge-Domain Computing. In Proceedings of the 2021 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 13–22 February 2021; pp. 248–250. [Google Scholar] [CrossRef]

- Rana, V.; Pasotti, M.; Carissimi, M. Row Decoder for Embedded Phase Change Memory Using Low Voltage Transistors. Microelectron. J. 2018, 81, 117–122. [Google Scholar] [CrossRef]

- Monga, K.; Chaturvedi, N.; Gurunarayanan, S. A Dual-Mode In-Memory Computing Unit Using Spin Hall-Assisted MRAM for Data-Intensive Applications. IEEE Trans. Magn. 2021, 57, 1–10. [Google Scholar] [CrossRef]

- Hung, J.M.; Li, X.; Wu, J.; Chang, M.F. Challenges and Trends in Developing Nonvolatile Memory-Enabled Computing Chips for Intelligent Edge Devices. IEEE Trans. Electron Devices 2020, 67, 1444–1453. [Google Scholar] [CrossRef]

- Yantır, H.E.; Eltawil, A.M.; Salama, K.N. IMCA: An Efficient In-Memory Convolution Accelerator. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2021, 29, 447–460. [Google Scholar] [CrossRef]

- Rana, V.; Sinha, R. Stress Relaxed Multiple Output High-Voltage Level Shifter. IEEE Trans. Circuits Syst. II Express Briefs 2018, 65, 176–180. [Google Scholar] [CrossRef]

- Osaki, Y.; Hirose, T.; Kuroki, N.; Numa, M. A Low-Power Level Shifter With Logic Error Correction for Extremely Low-Voltage Digital CMOS LSIs. IEEE J. Solid-State Circuits 2012, 47, 1776–1783. [Google Scholar] [CrossRef]

- Zhou, J.; Wang, C.; Liu, X.; Zhang, X.; Je, M. An Ultra-Low Voltage Level Shifter Using Revised Wilson Current Mirror for Fast and Energy-Efficient Wide-Range Voltage Conversion from Sub-Threshold to I/O Voltage. IEEE Trans. Circuits Syst. I Regul. Pap. 2015, 62, 697–706. [Google Scholar] [CrossRef]

| Operation Mode | Operation State | Signal | Explanation |

|---|---|---|---|

| weight writing | work | HVINPUT | weight input positive voltage |

| stop | HVGND | high-voltage gnd | |

| convolution operation | work | HVREAD | convolution operation positive voltage |

| stop | HVGND | high-voltage gnd | |

| weight erasing | work | HVRESET | weight erase negative voltage |

| stop | HVGND | high-voltage gnd |

| Transistor | W/L (µm) | Transistor | W/L (µm) |

|---|---|---|---|

| PM1 | 0.7/1 | NM1 | 2/0.6 |

| PM2 | 0.7/0.65 | NM2 | 2/0.6 |

| PM3 | 0.7/0.65 | NM3 | 0.7/0.6 |

| PM4 | 1/0.65 | NM4 | 0.7/0.6 |

| PM5 | 1/0.65 | NM5 | 0.7/0.6 |

| PM6 | 2/0.65 | NM6 | 2/0.6 |

| PM7 | 10/0.65 | NM7 | 8/0.6 |

| VPHV | VLV | VNHV | VINPUT_READ | VRESET | IN | OUT |

|---|---|---|---|---|---|---|

| HVINPUT | HVGND | HVGND | HVINPUT | HVGND | VDD | HVINPUT |

| HVINPUT | HVGND | HVGND | HVINPUT | HVGND | GND | HVGND |

| HVINPUT | HVGND | HVGND | HVREAD | HVGND | VDD | HVREAD |

| HVINPUT | HVGND | HVGND | HVREAD | HVGND | GND | HVGND |

| VDD | VDD | HVRESET | HVGND | HVRESET | VDD | HVRESET |

| VDD | VDD | HVRESET | HVGND | HVRESET | GND | HVRESET |

| Parameter | [8] | [9] | [10] | [11] | [17] | This Work |

|---|---|---|---|---|---|---|

| Input voltage (V) | 0.2 | 1.8 | 3–8.5 | 0.3 | 1.8 | 1.2 |

| Output voltage (V) | 3 | 9.8–12.8 | 5.35–12.4 | 1.2 | 4.5–13.5 | 10/5/−10 |

| Operating frequency (MHz) | 1 | 1.25 | 10 | 1 | 10 | 10 |

| Rise/Fall time (ns) | 10.01 | 40–50 | 1.8 | 25 | 2.5–8 | 3.01/2.39/4.89 |

| Output load (pF) | - | 15 | - | - | 0.015 | 1 |

| Static power (nW) | 0.6 | 774 | - | 2.5 | 0.37 | 0.1 |

| Total power (nW) | 11,233 | - | 26,500 | 22.4 | - | 249 |

| Power-delay product (nW.ns) | 113,453 | - | 47,700 | 560 | - | 749.5 |

| Layout area (µm2) * | 651 | 2628 | 1043 | 469 | 960 | 595 |

| Negative voltage support | No | No | No | No | No | Yes |

| Multi-voltages transmission | No | No | Yes | No | Yes | Yes |

| Process technology | 45 nm | 0.18 µm | 0.18 µm | 65 nm | 0.11 µm | 65 nm |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Gu, X.; Che, R.; Dong, Y.; Yu, Z. A Novel Word Line Driver Circuit for Compute-in-Memory Based on the Floating Gate Devices. Electronics 2023, 12, 1185. https://doi.org/10.3390/electronics12051185

Gu X, Che R, Dong Y, Yu Z. A Novel Word Line Driver Circuit for Compute-in-Memory Based on the Floating Gate Devices. Electronics. 2023; 12(5):1185. https://doi.org/10.3390/electronics12051185

Chicago/Turabian StyleGu, Xiaofeng, Rao Che, Yating Dong, and Zhiguo Yu. 2023. "A Novel Word Line Driver Circuit for Compute-in-Memory Based on the Floating Gate Devices" Electronics 12, no. 5: 1185. https://doi.org/10.3390/electronics12051185

APA StyleGu, X., Che, R., Dong, Y., & Yu, Z. (2023). A Novel Word Line Driver Circuit for Compute-in-Memory Based on the Floating Gate Devices. Electronics, 12(5), 1185. https://doi.org/10.3390/electronics12051185