Advances in Microelectronics and Semiconductor Engineering

Topic Information

Dear Colleagues,

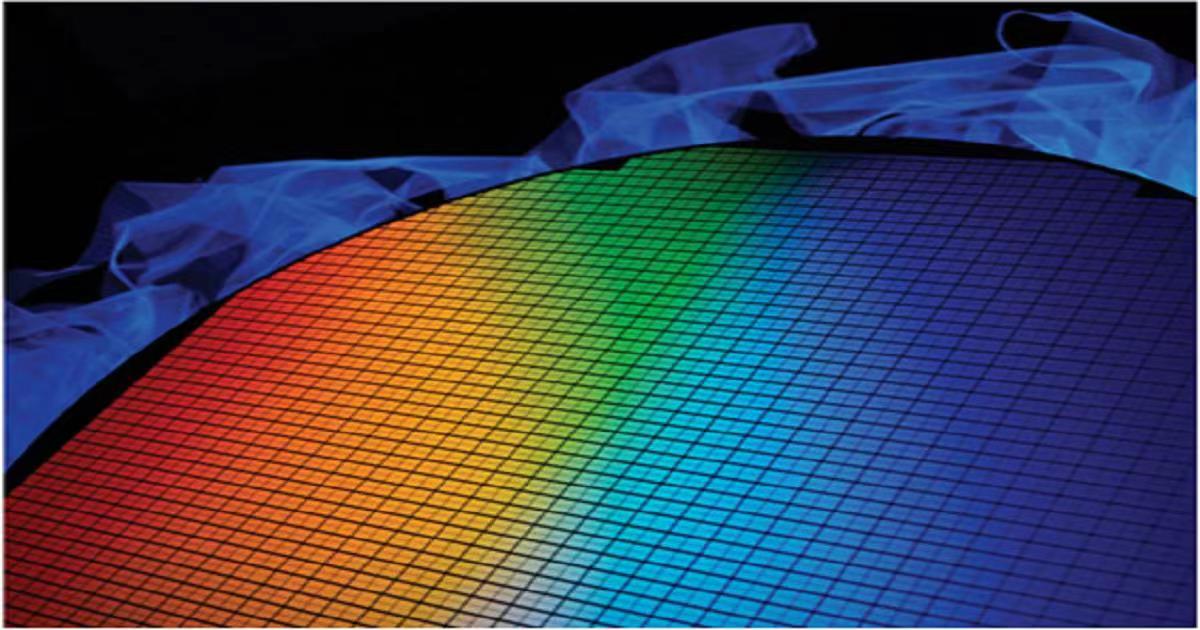

Silicon microelectronics is at the heart of modern electronics, finding applications in the computing, data processing, data storage, communications, and Internet of Things fields. Its development has been guided by Moore’s law since the 1970s and is now reaching its physical limits related to device dimension, integration density, and complexity both in CMOS and memory technologies. To overcome these limits, new challenges have been addressed regarding new material integration for FEOL and BEOL purposes, new processes for material growth, deposition, doping, etching and patterning, new device architectures for better scalability, improved physical characterization techniques for CD metrology, and advanced device and interconnect electrical characterization methodologies.

Dr. Gerard Ghibaudo

Dr. Francis Balestra

Topic Editors

Keywords

- new materials

- integration processes

- device architectures

- physical characterization and metrology

- electrical characterization and reliability

- CMOS

- memories

- cryogenic electronics

- beyond CMOS

- 3D integration