A −31.7 dBm Sensitivity 0.011 mm2 CMOS On-Chip Rectifier for Microwave Wireless Power Transfer

Abstract

1. Introduction

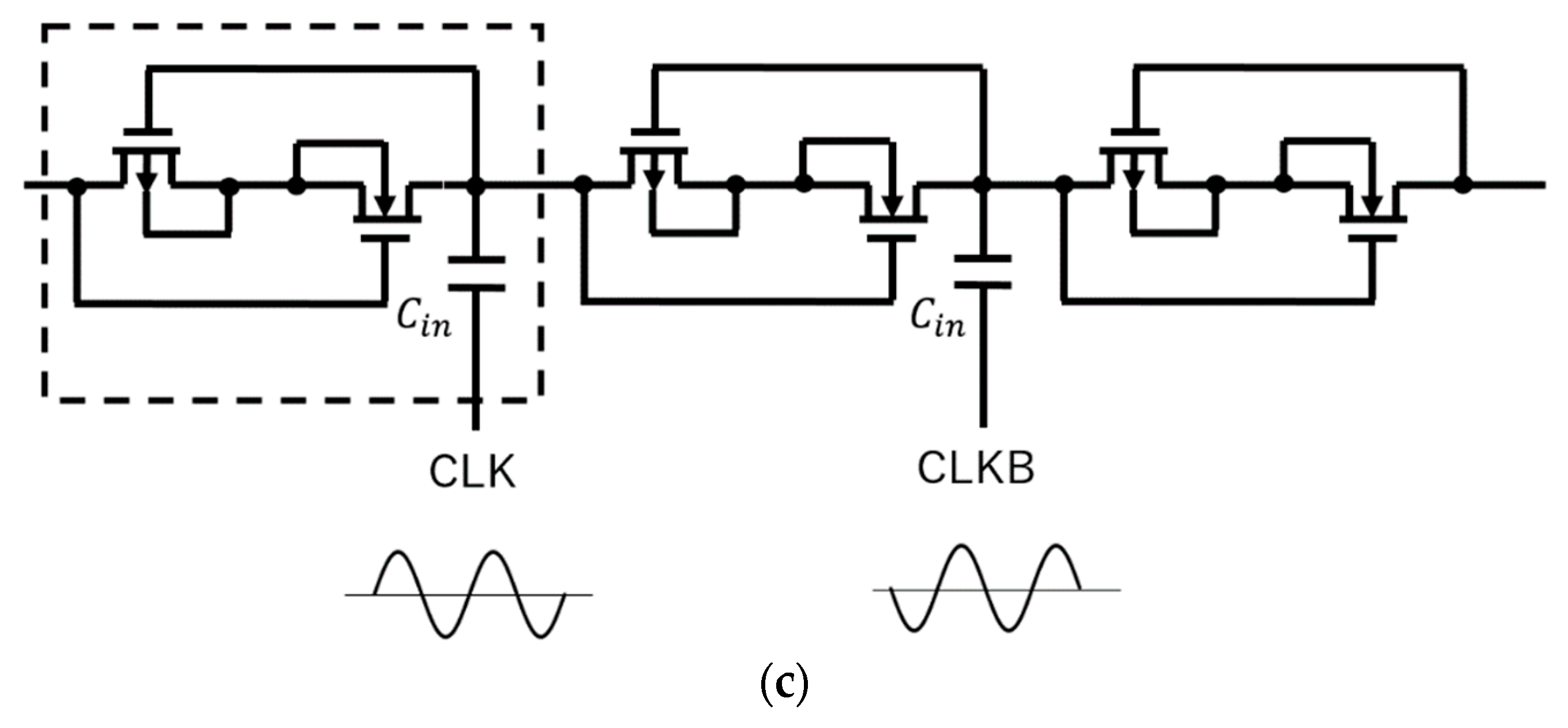

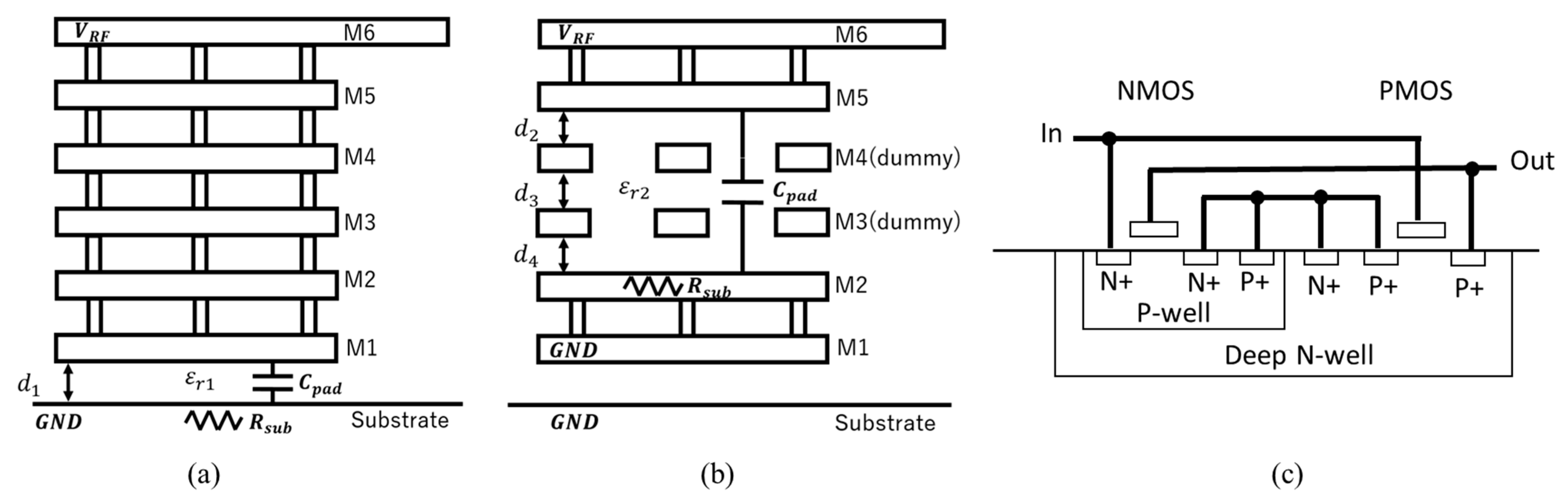

2. Rectifying Circuits

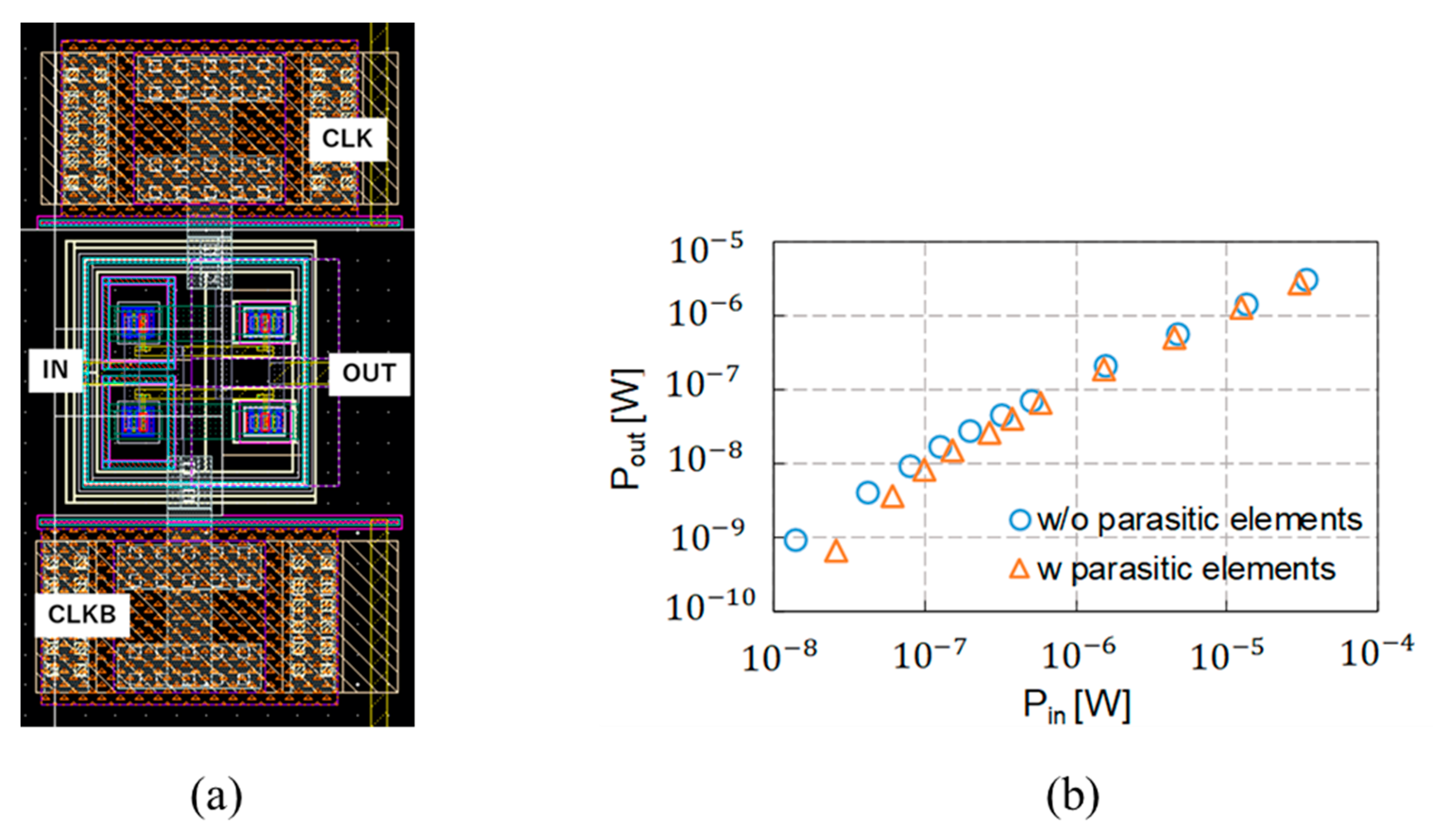

3. Optimization of Circuit Parameters and Layout Design

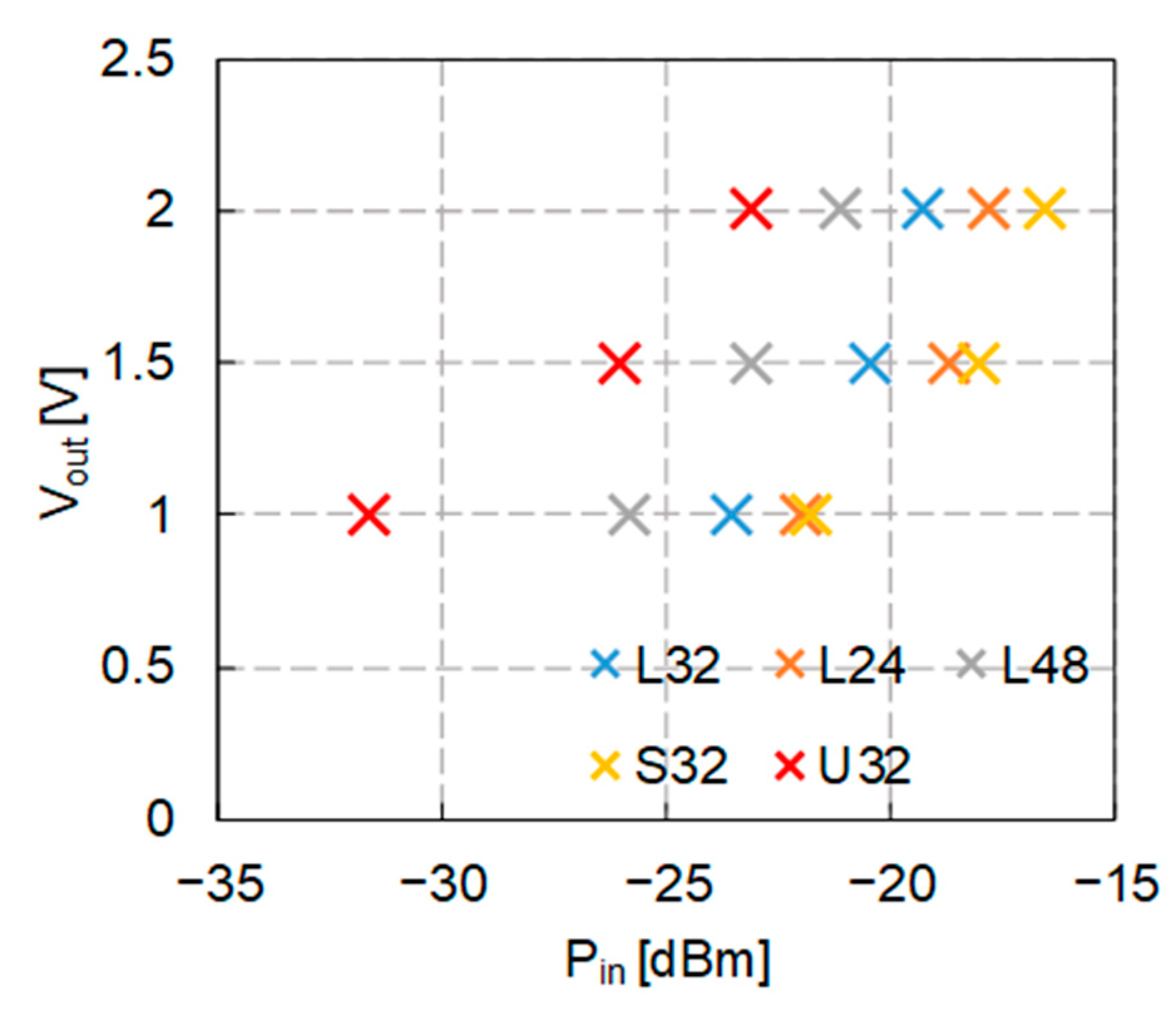

4. Measurement Result

5. Comparison with Previous Works

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Bi, S.; Ho, C.K.; Zhang, R. Wireless Powered Communication: Opportunities and Challenges. IEEE Commun. Mag. 2015, 53, 117–125. [Google Scholar] [CrossRef]

- Maenaka, K. Sensors in Network (5)–Future Sensor Systems in Internet of Things or Trillion Sensor Universe. Sens. Mater. 2016, 28, 1247–1254. [Google Scholar] [CrossRef]

- Brown, W.C. The history of power transmission by radio waves. IEEE Trans. Microw. Theory Tech. 1984, 32, 1230–1242. [Google Scholar] [CrossRef]

- Friis, H.T. A Note on a Simple Transmission Formula. Proc. IRE 1946, 34, 254–256. [Google Scholar] [CrossRef]

- Tabuchi, Y.; Tanzawa, T. Rectenna with Serially Connected Diodes for Micro-watt Energy Harvesting. In Proceedings of the 2020 IEEE Wireless Power Transfer Conference (WPTC), Seoul, Republic of Korea, 15–19 November 2020; pp. 57–60. [Google Scholar] [CrossRef]

- Yamazaki, Y.; Tsuchiaki, M.; Tanzawa, T. A Design Window for Device Parameters of Rectifying Diodes in 2.4 GHz Mi-cro-watt RF Energy Harvesting. In Proceedings of the 2019 IEEE Asia-Pacific Microwave Conference (APMC), Singapore, 10–13 December 2019; pp. 135–137. [Google Scholar] [CrossRef]

- Stoopman, M.; Keyrouz, S.; Visser, H.J.; Philips, K.; Serdijn, W.A. Co-Design of a CMOS Rectifier and Small Loop Antenna for Highly Sensitive RF Energy Harvesters. IEEE J. Solid-State Circuits 2014, 49, 622–634. [Google Scholar] [CrossRef]

- Falkenstein, E.; Roberg, M.; Popović, Z. Low-Power Wireless Power Delivery. IEEE Trans. Microw. Theory Tech. 2012, 60, 2277–2286. [Google Scholar] [CrossRef]

- Hashimoto, T.; Tanzawa, T. Design Space Exploration of Antenna Impedance and On-Chip Rectifier for Microwave Wireless Power Transfer. Electronics 2022, 11, 3218. [Google Scholar] [CrossRef]

- Kotani, K.; Ito, T. Self-Vth-Cancellation High-Efficiency CMOS Rectifier Circuit for UHF RFIDs. IEICE Trans. Electron. 2009, E92-C, 153–160. [Google Scholar] [CrossRef]

- Safarian, Z.; Hashemi, H. A Wirelessly-Powered Passive RF CMOS Transponder with Dynamic Energy Storage and Sensitivity Enhancement. In Proceedings of the 2011 IEEE Radio Frequency Integrated Circuits Symposium, Baltimore, MD, USA, 5–7 June 2011; pp. 1–4. [Google Scholar] [CrossRef]

- Kang, J.; Chiang, P.; Natarajan, A. Bootstrapped Rectifier-Antenna Co-Integration for Increased Sensitivity in Wirelessly-Powered Sensors. IEEE Trans. Microw. Theory Tech. 2018, 66, 5031–5041. [Google Scholar] [CrossRef]

- Oh, S.; Wentzloff, D.D. A −32dBm sensitivity RF power harvester in 130 nm CMOS. In Proceedings of the 2012 IEEE Radio Frequency Integrated Circuits Symposium, Montreal, QC, Canada, 17–19 June 2012; pp. 483–486. [Google Scholar] [CrossRef]

- Wu, Z.; Zhao, Y.; Sun, Y.; Min, H.; Yan, N. A Self-Bias Rectifier with 27.6% PCE at −30dBm for RF Energy Harvesting. In Proceedings of the 2021 IEEE International Symposium on Circuits and Systems (ISCAS), Daegu, Republic of Korea, 22–28 May 2021; pp. 1–5. [Google Scholar] [CrossRef]

- Shetty, D.; Steffan, C.; Bösch, W.; Grosinger, J. Sub-GHz RF Energy Harvester including a Small Loop Antenna. In Proceedings of the 2022 IEEE Asian Solid-State Circuits Conference (A-SSCC), Taipei, Taiwan, 6–9 November 2022; pp. 1–3. [Google Scholar] [CrossRef]

- Lian, W.X.; Ramiah, H.; Chong, G.; Kishore Kumar, P.C. A Differential RF Front-end CMOS Transformer Matching for Ambient RF Energy Harvesting Systems. In Proceedings of the 2021 IEEE Asia Pacific Conference on Circuit and Systems (APCCAS), Penang, Malaysia, 22–26 November 2021; pp. 133–136. [Google Scholar] [CrossRef]

- Gariboldi, R.; Pulvirenti, F. A 70 mΩ Intelligent High Side Switch with Full Diagnostics. IEEE J. Solid-State Circuits 1996, 31, 915–923. [Google Scholar] [CrossRef]

- Levacq, D.; Liber, C.; Dessard, V.; Flandre, D. Composite ULP diode fabrication, modelling and applications in multi-Vth FD SOI CMOS technology. Solid-State Electron. 2004, 48, 1017–1025. [Google Scholar] [CrossRef]

- Papotto, G.; Carrara, F.; Palmisano, G. A 90-nm CMOS Threshold-Compensated RF Energy Harvester. IEEE J. Solid-State Circuits 2011, 46, 1985–1997. [Google Scholar] [CrossRef]

- Le, T.; Mayaram, K.; Fiez, T. Efficient Far-Field Radio Frequency Energy Harvesting for Passively Powered Sensor Networks. IEEE J. Solid-State Circuits 2008, 43, 1287–1302. [Google Scholar] [CrossRef]

- Umeda, T.; Yoshida, H.; Sekine, S.; Fujita, Y.; Suzuki, T.; Otaka, S. A 950-MHz Rectifier Circuit for Sensor Network Tags With 10-m Distance. IEEE J. Solid-State Circuits 2006, 41, 35–41. [Google Scholar] [CrossRef]

| Parameter | Description | Parameter | Description |

|---|---|---|---|

| Frequency of input power | Number of fingers of each switching transistor | ||

| Output voltage of RF–DC CP | Input capacitance per stage | ||

| Gate length of switching transistors | Number of stages | ||

| Gate width of NMOSFET |

| Parameters | Trial Values | Optimum Value |

|---|---|---|

| Transistor type | 1 V, 2.5 V | 1 V CMOS |

| Threshold voltage | lvt, std, hvt | lvt |

| 60, 120, 240 | 60 | |

| (1) 1.2, (2) 5, (3) 5 | 1.2 | |

| (1) 1, (2) 2, (3) 4 | 1 | |

| 100, 500, 1000 | 100 | |

| 16, 24, 32, 48 | 32 |

| Rectifier Name | Rectifier Type | Number of Stages |

|---|---|---|

| L32 | Latch | 32 |

| L24 | Latch | 24 |

| L48 | Latch | 48 |

| S32 | Single diode | 32 |

| U32 | ULPD | 32 |

| Rectifier Pattern | Number of Stages | Rectifier Type | Sensitivity [dBm] | |

|---|---|---|---|---|

| SPICE | Measurement | |||

| L32 | 32 | Latch | −32.5 | −23.6 |

| L24 | 24 | Latch | −33.2 | −22.0 |

| L48 | 48 | Latch | −32.9 | −25.8 |

| S32 | 32 | Single diode | −29.1 | −21.8 |

| U32 | 32 | ULPD | −25.8 | −31.7 |

| 100 | 1 | |

| −7.0 | −17.0 | |

| −10.0 | −17.2 |

| Designs | Technology [nm] | Number of Stages | Rectifier Type | Input Signal Type | Load Condition | Area [mm2] | Sensitivity [dBm] |

|---|---|---|---|---|---|---|---|

| This work | 65 | 32 | ULPD | Balanced | 10 GΩ/1 V | 0.011 | −31.7 |

| [7] | 90 | 5 | Latch | Balanced | Cap.load/1 V | 0.029 | −27.0 |

| [13] | 130 | 50 | SD | Unbalanced | Cap.load/1 V | 0.080 | −32.1 |

| [14] | 130 | 6 | Gate biasing | Balanced | Cap.load/1 V | 0.064 | −20.4 |

| [15] | 130 | 5 | Gate biasing | Unbalanced | 1 GΩ/1 V | 0.02 | −33.0 |

| [16] | 65 | 5 | Latch | Balanced | Cap.load/1 V | 0.28 | −17.8 |

| [19] | 90 | 17 | SD | Balanced | Cap.load/1 V | 0.019 | −24.0 |

| [20] | 250 | 36 | SD | Balanced | N.A. | 0.4 | −22.6 |

| [21] | 300 | 6 | SD | Unbalanced | 1.5 V/0.4 μA | 0.104 | −14.0 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Hashimoto, T.; Nekozuka, H.; Toeda, Y.; Otani, M.; Fukuoka, Y.; Tanzawa, T. A −31.7 dBm Sensitivity 0.011 mm2 CMOS On-Chip Rectifier for Microwave Wireless Power Transfer. Electronics 2023, 12, 1400. https://doi.org/10.3390/electronics12061400

Hashimoto T, Nekozuka H, Toeda Y, Otani M, Fukuoka Y, Tanzawa T. A −31.7 dBm Sensitivity 0.011 mm2 CMOS On-Chip Rectifier for Microwave Wireless Power Transfer. Electronics. 2023; 12(6):1400. https://doi.org/10.3390/electronics12061400

Chicago/Turabian StyleHashimoto, Takuma, Hikaru Nekozuka, Yoshitaka Toeda, Masayuki Otani, Yasuhiko Fukuoka, and Toru Tanzawa. 2023. "A −31.7 dBm Sensitivity 0.011 mm2 CMOS On-Chip Rectifier for Microwave Wireless Power Transfer" Electronics 12, no. 6: 1400. https://doi.org/10.3390/electronics12061400

APA StyleHashimoto, T., Nekozuka, H., Toeda, Y., Otani, M., Fukuoka, Y., & Tanzawa, T. (2023). A −31.7 dBm Sensitivity 0.011 mm2 CMOS On-Chip Rectifier for Microwave Wireless Power Transfer. Electronics, 12(6), 1400. https://doi.org/10.3390/electronics12061400