Comparative Study of the Parameter Acquisition Methods for the Cauer Thermal Network Model of an IGBT Module

Abstract

:1. Introduction

2. IGBT Module Structure and Heat Transfer Process

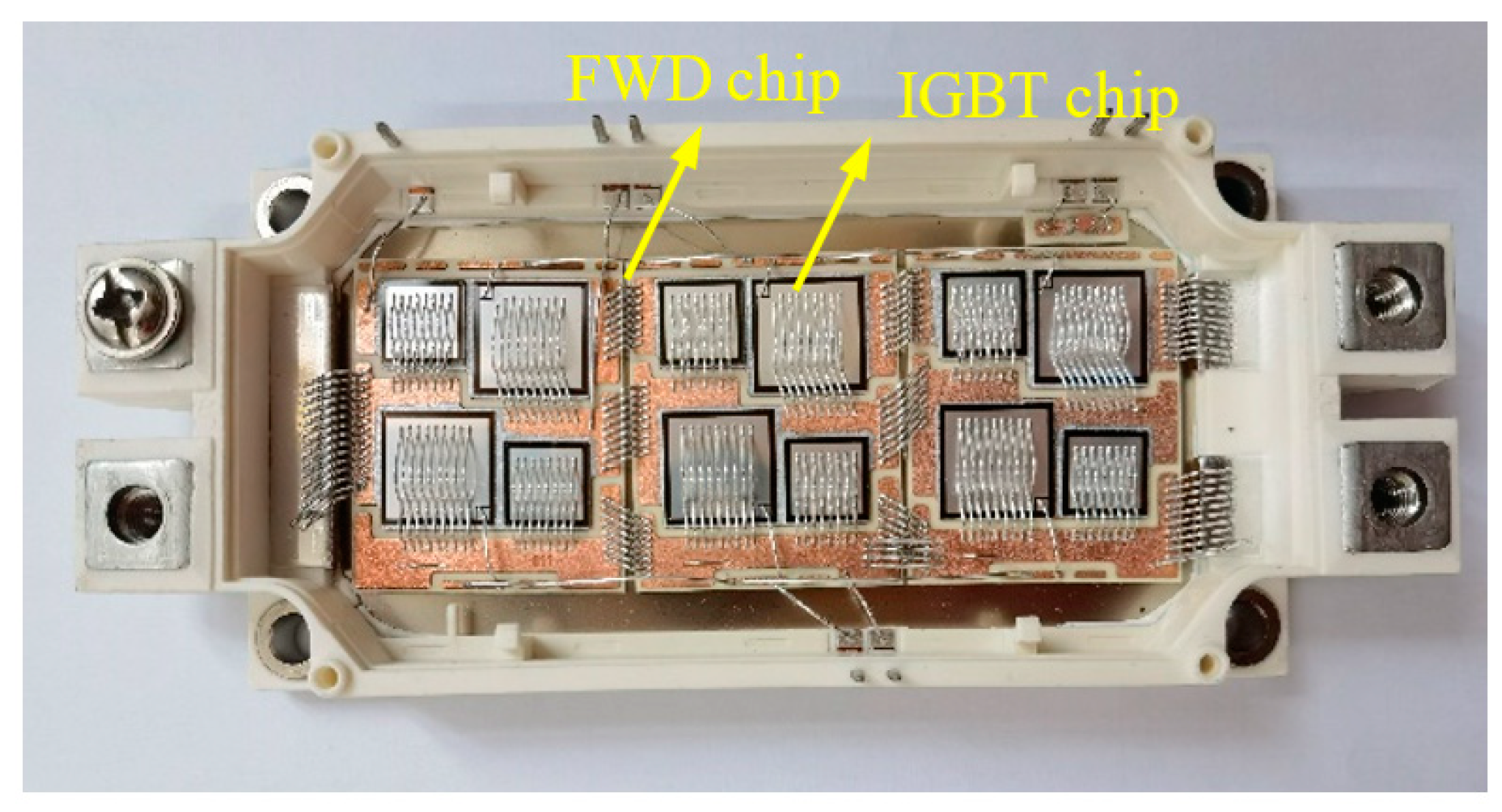

2.1. IGBT Module Structure for the Experiment

2.2. Simplification of the Heat Transfer Process of the IGBT Module

- (1)

- The heat dissipation process considers the heat conduction process only from the chip to the heat sink.

- (2)

- The three-dimensional heat conduction problem of the IGBT module is simplified to a one-dimensional heat conduction problem.

- (3)

- The thermal coupling effect between IGBT chips is ignored.

3. Modeling Process of the RC Thermal Network Model of the IGBT Module

3.1. Cauer Thermal Network Model Structure

3.2. Determining the Parameters of the RC Thermal Network Model by Using the Transient Thermal Impedance Curve Test and Structure Function

3.3. Determining the Parameters of the RC Thermal Network Model by Using Theoretical Formulas

4. Experimental Measurement of the IGBT Chip Junction Temperature

4.1. Power Cycling Test Process

4.2. Measuring the Junction Temperature by Using the IR Thermal Imaging Method

4.3. Measuring the Junction Temperature by Using the TSEPs

5. Obtaining the Junction Temperature of the IGBT Module by Using FE Analysis

6. Results and Discussion

6.1. Comparison of Junction Temperatures by Using TSEP, IR Measurement, and FE Analysis

6.2. Comparison of the Experimental Junction Temperatures and Those Calculated by the RC Thermal Network Models Obtained by the Two Methods

6.3. Comparison of the Junction Temperatures Obtained by the FE Analysis and Those Calculated by the RC Thermal Network Models Obtained by the Two Methods

7. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Oh, H.; Han, B.; McCluskey, P.; Han, C.; Youn, B.D. Physics-of-failure, condition monitoring, and prognostics of insulated gate bipolar transistor modules: A review. IEEE Trans. Power Electron. 2014, 30, 2413–2426. [Google Scholar] [CrossRef]

- Sathik, M.H.M.; Sundararajan, P.; Sasongko, F.; Pou, J.; Natarajan, S. Comparative analysis of IGBT parameters variation under different accelerated aging tests. IEEE Trans. Electron. Devices 2020, 67, 1098–1105. [Google Scholar] [CrossRef]

- Scheuermann, U.; Hecht, U. Power cycling lifetime of advanced power modules for different temperature swings. In Proceedings of the PCIM, Nuremberg, Germany, 14–16 May 2002. [Google Scholar]

- Schilling, O.; Schäfer, M.; Mainka, K.; Thoben, M.; Sauerland, F. Power cycling testing and FE modelling focussed on Al wire bond fatigue in high power IGBT modules. Microelectron. Reliab. 2012, 52, 2347–2352. [Google Scholar] [CrossRef]

- Lutz, J.; Schlangenotto, H.; Scheuermann, U.; Doncker, R. Semiconductor Power Devices: Physics, Characteristics, Reliability; Springer: Berlin, Germany, 2011. [Google Scholar]

- Ciappa, M. Selected failure mechanisms of modern power modules. Microelectron. Reliab. 2002, 42, 653–667. [Google Scholar] [CrossRef]

- Wang, H.; Ke, M.; Blaabjerg, F. Design for reliability of power electronic systems. In Proceedings of the 38th Annual Conference on IEEE Industrial Electronics Society, Montreal, QC, Canada, 25 October 2012; pp. 33–44. [Google Scholar]

- Fabis, P.M.; Shum, D.; Windischmann, H. Thermal modeling of diamond-based power electronics packaging. In Proceedings of the Fifteenth Annual IEEE Semiconductor Thermal Measurement and Management Symposium, San Diego, CA, USA, 9 March 1999; pp. 98–104. [Google Scholar]

- Górecki, K.; Górecki, P.; Zarębski, J. Measurements of parameters of the thermal model of the IGBT module. IEEE Trans. Instrum. Meas. 2019, 68, 4864–4875. [Google Scholar] [CrossRef]

- Dupont, L.; Avenas, Y.; Jeannin, P.O. Comparison of junction temperature evaluations in a power IGBT module using an IR camera and three thermosensitive electrical parameters. IEEE Trans. Ind. Appl. 2013, 49, 1599–1608. [Google Scholar] [CrossRef] [Green Version]

- Sathik, M.H.M.; Pou, J.; Prasanth, S.; Muthu, V.; Simanjorang, R.; Gupta, A.K. Comparison of IGBT junction temperature measurement and estimation methods-a review. In Proceedings of the Asian Conference on Energy, Power and Transportation Electrification, Singapore, 24 October 2017; pp. 1–8. [Google Scholar]

- Wuhua, L.; Yuxiang, C.; Haoze, L.; Yu, Z.; Huan, Y. Review and prospect of junction temperature extraction principle of high power semiconductor devices. Proc. CSEE 2016, 36, 3546–3557. [Google Scholar]

- Scognamillo, C.; Fregonese, S.; Zimmer, T.; d’Alessandro, V.; Catalano, A.P. A Technique for the In-Situ Experimental Extraction of the Thermal Impedance of Power Devices. IEEE Trans. Power Electron. 2022, 37, 11511–11515. [Google Scholar] [CrossRef]

- Hung, T.Y.; Chiang, S.Y.; Chou, C.Y.; Chiu, C.C.; Chiang, K.N. Thermal design and transient analysis of insulated gate bipolar transistors of power module. In Proceedings of the 12th IEEE Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems, Las Vegas, NV, USA, 2 June 2010; pp. 1–5. [Google Scholar]

- Özkol, E.; Hartmann, S.; Pâques, G. Improving the power cycling performance of the emitter contact of IGBT modules: Implementation and evaluation of stitch bond layouts. Microelectron. Reliab. 2014, 54, 2796–2800. [Google Scholar] [CrossRef]

- Górecki, P.; Górecki, K. Methods of Fast Analysis of DC–DC Converters—A Review. Electronics 2021, 10, 2920. [Google Scholar] [CrossRef]

- Li, H.; Hu, Y.; Liu, S.; Li, Y.; Liao, X.; Liu, Z. An improved thermal network model of the IGBT module for wind power converters considering the effects of base-plate solder fatigue. IEEE Trans. Device Mater. Reliab. 2016, 16, 570–575. [Google Scholar] [CrossRef]

- Zhihong, W.; Xiezu, S.; Yuan, Z. IGBT junction and coolant temperature estimation by thermal model. Microelectron. Reliab. 2018, 87, 168–182. [Google Scholar] [CrossRef]

- Luo, Z.; Ahn, H.; Nokali, M.A.E. A thermal model for insulated gate bipolar transistor module. IEEE Trans. Power Electron. 2004, 19, 902–907. [Google Scholar] [CrossRef]

- Akbari, M.; Bahman, A.S.; Bina, M.T.; Eskandari, B.; Iannuzzo, F.; Blaabjerg, F. A multi-layer RC thermal model for power modules adaptable to different operating conditions and aging. In Proceedings of the 20th European Conference on Power Electronics and Applications, Riga, Latvia, 17 September 2018; pp. 1–10. [Google Scholar]

- Bahman, A.S.; Ma, K.; Ghimire, P.; Iannuzzo, F.; Blaabjerg, F. A 3-D-lumped thermal network model for long-term load profiles analysis in high-power IGBT modules. IEEE J. Emerg. Sel. Top. Power Electron. 2016, 4, 1050–1063. [Google Scholar] [CrossRef] [Green Version]

- Bahman, A.S.; Ma, K.; Blaabjerg, F. A lumped thermal model including thermal coupling and thermal boundary conditions for high-power IGBT modules. IEEE Trans. Power Electron. 2017, 33, 2518–2530. [Google Scholar] [CrossRef] [Green Version]

- Li, H.; Liao, X.; Zeng, Z.; Hu, Y.; Li, Y.; Liu, S.; Ran, L. Thermal coupling analysis in a multichip paralleled IGBT module for a DFIG wind turbine power converter. IEEE Trans. Energy Convers. 2016, 32, 80–90. [Google Scholar] [CrossRef] [Green Version]

- Gachovska, T.K.; Tian, B.; Hudgins, J.L.; Qiao, W.; Donlon, J.F. A real-time thermal model for monitoring of power semiconductor devices. IEEE Trans. Ind. Appl. 2015, 51, 3361–3367. [Google Scholar] [CrossRef]

- Batard, C.; Ginot, N.; Antonios, J. Lumped dynamic electrothermal model of IGBT module of inverters. IEEE Trans. Compon. Packag. Manuf. Technol. 2015, 5, 355–364. [Google Scholar] [CrossRef]

- Li, J.; Chen, Z.; Liu, S.; Deng, E.; Zhao, Z. Study on the Cauer Thermal Network Model of Press Pack IGBTs. In Proceedings of the International Conference on Advanced Electronic Materials, Computers and Materials Engineering, Singapore, 14 September 2018; Volume 439, p. 052012. [Google Scholar]

- Deng, E.; Wenzel, O.; Zhao, Z.; Zhang, Y.; Ying, X.; Li, J.; Huang, Y. Research on the Multiphysics Field-Circuit Coupling Model of Press Pack IGBT Considering the Application of Hybrid HVDC Breakers. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 9, 4854–4864. [Google Scholar] [CrossRef]

- Deng, E.; Zhao, Z.; Zhang, P.; Luo, X.; Li, J.; Huang, Y. Study on the method to measure thermal contact resistance within press pack IGBTs. IEEE Trans. Power Electron. 2018, 34, 1509–1517. [Google Scholar] [CrossRef]

- Li, L.; Xu, Y.; Li, Z.; Wang, P.; Wang, B. The effect of electro-thermal parameters on IGBT junction temperature with the aging of module. Microelectron. Reliab. 2016, 66, 58–63. [Google Scholar] [CrossRef]

- Li, H.; Liao, X.; Li, Y.; Liu, S.; Hu, Y.; Zeng, Z.; Ran, L. Improved thermal couple impedance model and thermal analysis of multi-chip paralleled IGBT module. In Proceedings of the IEEE Energy Conversion Congress and Exposition, Montreal, QC, Canada, 20 September 2015; pp. 3748–3753. [Google Scholar]

- Floros, G.; Chatzigeorgiou, C.; Evmorfopoulos, N.; Stamoulis, G. THANOS: Eliminating Redundant States in Transient Thermal Analysis. In Proceedings of the 25th International Workshop on Thermal Investigations of ICs and Systems (THERMINIC), Lecco, Italy, 25 September 2019; pp. 1–5. [Google Scholar]

- Masana, F.N. A new approach to the dynamic thermal modelling of semiconductor packages. Microelectron. Reliab. 2001, 41, 901–912. [Google Scholar] [CrossRef]

- Meng, J.; Wen, X.; Zhong, Y.; Qiu, Z.; Kong, L. A thermal model for electrothermal simulation of power modules. In Proceedings of the International Conference on Electrical Machines and Systems, Busan, Republic of Korea, 26 October 2013; pp. 1635–1638. [Google Scholar]

- Masana, F.N. Thermal characterisation of power modules. Microelectron. Reliab. 2000, 40, 155–161. [Google Scholar] [CrossRef]

- Vermeersch, B.; De Mey, G. A fixed-angle heat spreading model for dynamic thermal characterization of rear-cooled substrates. In Proceedings of the 23rd Annual IEEE Semiconductor Thermal Measurement and Management Symposium, San Jose, CA, USA, 18 March 2007; pp. 95–101. [Google Scholar]

- David, R. Computerized Thermal analysis of hybrid circuits. IEEE Trans. Parts Hybrids Packag. 1977, 13, 283–290. [Google Scholar] [CrossRef]

- Zimmer, C.R. Computer simulation of hybrid integrated circuits including combined electrical and thermal effects. Act. Passiv. Electron. Compon. 1983, 10, 171–176. [Google Scholar] [CrossRef] [Green Version]

- Masana, F.N. A closed form solution of junction to substrate thermal resistance in semiconductor chips. IEEE Trans. Compon. Packag. Manuf. Technol. Part A 1996, 19, 539–545. [Google Scholar] [CrossRef]

- Choi, U.M.; Blaabjerg, F.; Jørgensen, S. Power cycling test methods for reliability assessment of power device modules in respect to temperature stress. IEEE Trans. Power Electron. 2018, 33, 2531–2551. [Google Scholar] [CrossRef] [Green Version]

- Tseng, H.K.; Wu, M.L. Electro-thermal-mechanical modeling of wire bonding failures in IGBT. In Proceedings of the 8th International Microsystems, Packaging, Assembly and Circuits Technology Conference, Taipei, Taiwan, 22 October 2013; pp. 152–157. [Google Scholar]

- Zhao, J.; Qin, F.; An, T.; Bie, X.; Fang, C. Electro-thermal and thermal-mechanical FE analysis of IGBT module with different bonding wire shape. In Proceedings of the 18th International Conference on Electronic Packaging Technology, Harbin, China, 16 August 2017; pp. 548–551. [Google Scholar]

| Each Layer | Rth/(°C/W) | Cth/(J/°C) |

|---|---|---|

| IGBT chip | 0.0169 | 0.8542 |

| Chip solder | 0.0131 | 0.4032 |

| Upper Cu layer on the DBC | 0.008 | 0.1377 |

| DBC ceramic layer | 0.0107 | 3.3457 |

| Lower Cu layer on the DBC | 0.0078 | 3.5861 |

| DBC solder | 0.0265 | 28.199 |

| Cu baseplate | 0.057 | 79.772 |

| Material Layer | Length (mm) | Width (mm) | Thickness (μm) | Rth (°C/W) | Cth (J/°C) |

|---|---|---|---|---|---|

| IGBT chip | 13.5 | 13.5 | 140 | 7.41 × 10−3 | 5.94 × 10−2 |

| Chip solder | 13.5 | 13.5 | 150 | 1.44 × 10−2 | 4.59 × 10−2 |

| Upper Cu layer on the DBC | 30.0 | 14.5 | 300 | 3.94 × 10−3 | 0.19 |

| DBC ceramic layer | 40.0 | 32.0 | 380 | 9.07 × 10−2 | 0.24 |

| Lower Cu layer on the DBC | 38.0 | 30.0 | 380 | 4.09 × 10−3 | 0.30 |

| DBC solder | 38.0 | 30.0 | 300 | 2.08 × 10−2 | 0.13 |

| Cu baseplate | 122.0 | 62.0 | 3000 | 2.08 × 10−2 | 3.79 |

| Experimental Conditions | Load Current Waveform | Icmax (A) | ton/toff (s) | Tw (°C) |

|---|---|---|---|---|

| DC-1 |  | 140 | 4/4 | 45 |

| DC-2 | 400 | 2/2 | 45 |

| Material | Thermal Conductivity (W/m∙K) | Resistivity (mΩ∙mm) | Density (kg/m3) | Specific Heat (J/kg∙K) |

|---|---|---|---|---|

| Al [40] | 237 | 2.65 × 10−2 | 2.70 × 103 | 900 |

| Si [40] | 148 | 7.7 × 103 | 2.33 × 103 | 700 |

| SnAgCu305 solder [21] | 57 | 1.04 × 10−1 | 7.30 × 103 | 230 |

| Al2O3 [41] | 20 | 1 × 1018 | 3.96 × 103 | 753 |

| Cu [40] | 400 | 1.68 × 10−2 | 8.92 × 103 | 380 |

| Tj-TSEP (°C) | Tj,mean-IR Camera (°C) | Error (Tj-TSEP − Tj,mean-IR Camera) (°C) | Tj,max-IR Camera (°C) | Error(Tj-TSEP − Tj,max-IR Camera) (°C) | Tj,max-FE (°C) | Error(Tj,max-IR Camera − Tj,max-FE) (°C) | |

|---|---|---|---|---|---|---|---|

| IGBT 1 | 59.58 | 59.09 | −0.49 | 64.82 | 5.24 | 64.37 | 0.45 |

| IGBT 2 | 60.26 | 0.68 | 65.11 | 5.53 | 65.36 | −0.25 | |

| IGBT 3 | 61.09 | 1.51 | 66.06 | 6.48 | 65.41 | 0.65 | |

| Average | 60.15 | 0.57 | - | - | - | - |

| Monitoring Point | FE | Cauer-Theoretical Formulas | Error | Cauer-Test | Error |

|---|---|---|---|---|---|

| TIGBT chip | 65.36 | 63.99 | 2.10% | 58.32 | 10.77% |

| Tchip solder | 65.23 | 63.48 | 2.68 | 57.16 | 12.37% |

| Tupper Cu | 64.73 | 62.49 | 3.46% | 56.26 | 13.09% |

| Tceramics | 64.60 | 62.22 | 3.68% | 55.71 | 13.76% |

| Tlower Cu | 61.40 | 56.01 | 8.78% | 54.99 | 10.44% |

| TDBC solder | 61.28 | 55.73 | 9.06% | 54.47 | 11.11% |

| TCu baseplate | 60.89 | 54.32 | 10.79% | 52.92 | 13.09% |

| Monitoring Point | FE | Cauer-Theoretical Formulas | Error | Cauer-Test | Error |

|---|---|---|---|---|---|

| TIGBT chip | 144.08 | 144.95 | 0.60% | 132.95 | 7.72% |

| Tchip solder | 143.02 | 142.06 | 0.67% | 126.47 | 11.57% |

| Tupper Cu | 138.90 | 136.46 | 1.76% | 121.46 | 12.56 |

| Tceramics | 137.80 | 134.94 | 2.08% | 118.41 | 14.07% |

| Tlower Cu | 111.71 | 99.92 | 10.55% | 114.40 | 2.41% |

| TDBC solder | 110.74 | 98.35 | 11.19% | 111.53 | 0.71% |

| TCu baseplate | 107.51 | 90.38 | 15.93% | 103.36 | 3.86% |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

An, T.; Zhou, R.; Qin, F.; Dai, Y.; Gong, Y.; Chen, P. Comparative Study of the Parameter Acquisition Methods for the Cauer Thermal Network Model of an IGBT Module. Electronics 2023, 12, 1650. https://doi.org/10.3390/electronics12071650

An T, Zhou R, Qin F, Dai Y, Gong Y, Chen P. Comparative Study of the Parameter Acquisition Methods for the Cauer Thermal Network Model of an IGBT Module. Electronics. 2023; 12(7):1650. https://doi.org/10.3390/electronics12071650

Chicago/Turabian StyleAn, Tong, Rui Zhou, Fei Qin, Yanwei Dai, Yanpeng Gong, and Pei Chen. 2023. "Comparative Study of the Parameter Acquisition Methods for the Cauer Thermal Network Model of an IGBT Module" Electronics 12, no. 7: 1650. https://doi.org/10.3390/electronics12071650

APA StyleAn, T., Zhou, R., Qin, F., Dai, Y., Gong, Y., & Chen, P. (2023). Comparative Study of the Parameter Acquisition Methods for the Cauer Thermal Network Model of an IGBT Module. Electronics, 12(7), 1650. https://doi.org/10.3390/electronics12071650