CMOS-Based Memristor Emulator Circuits for Low-Power Edge-Computing Applications

Abstract

:1. Introduction

1.1. Challenges in Memristor Integration

1.2. Applications of Memristors

Memristor Neural Networks

1.3. Memristor for Edge and Neuromorphic Computing Applications

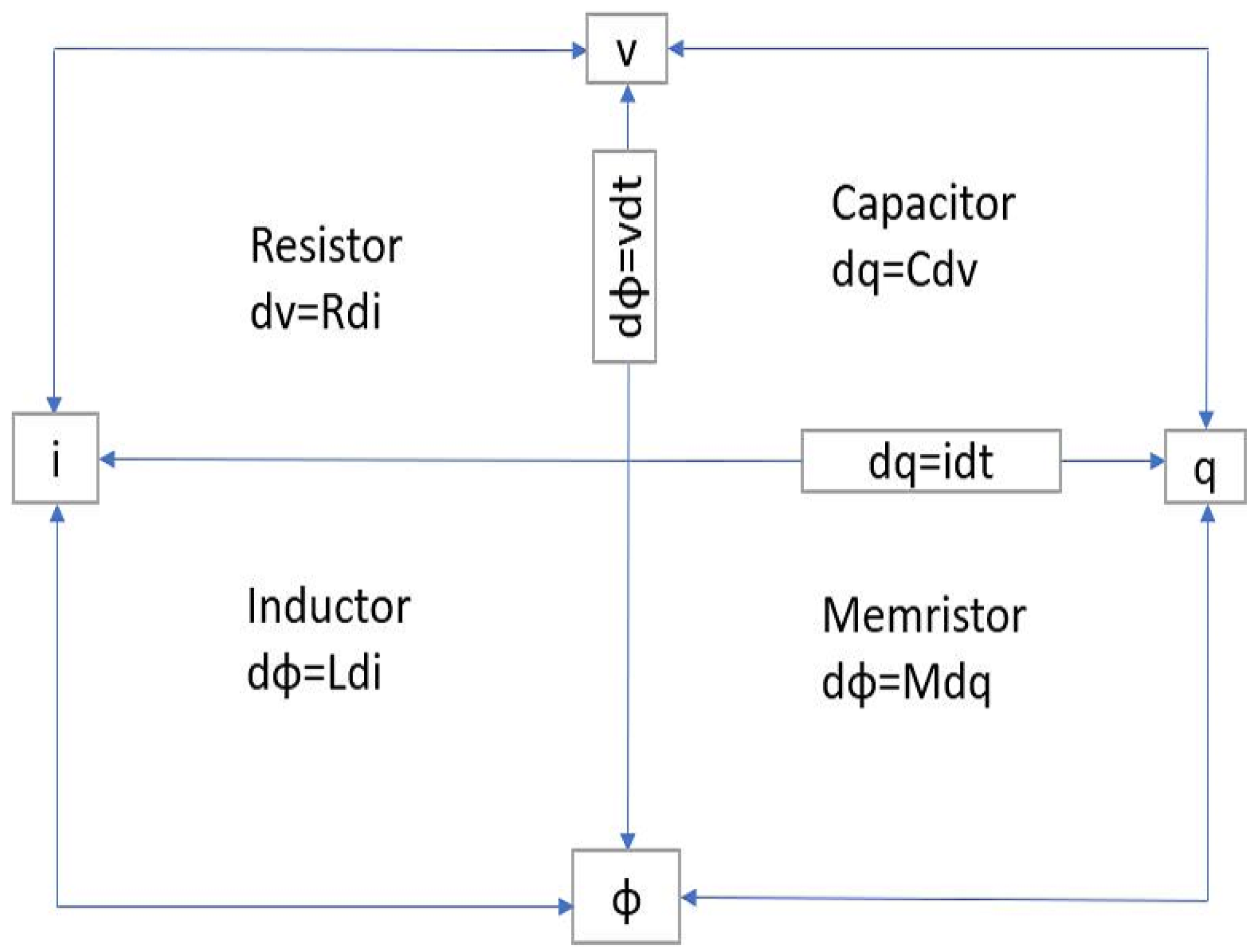

2. Modeling the Memristors

Working Principle of Memristors

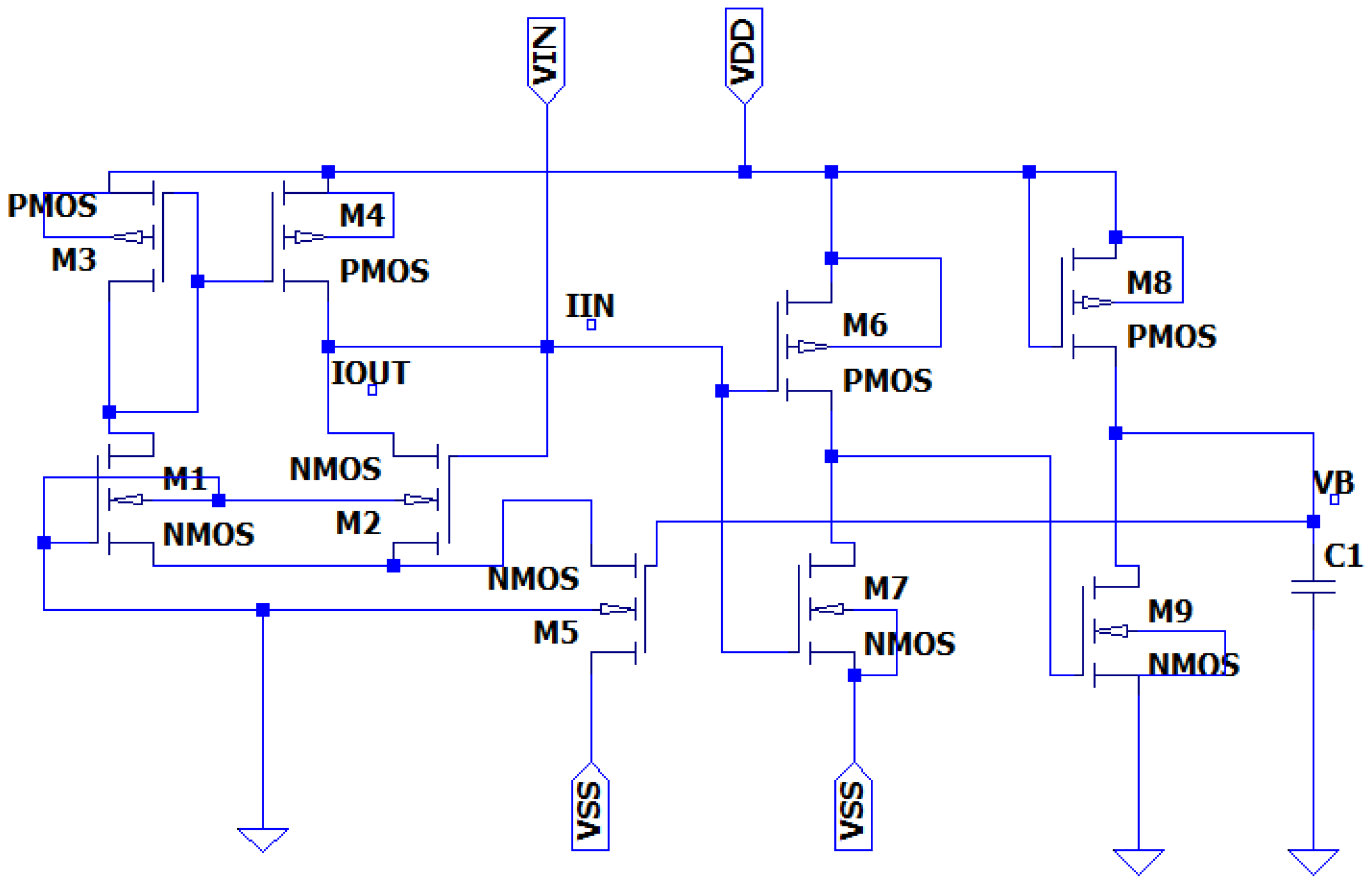

3. Proposed Memristor Circuit and Its Analysis

Memristor Modeling Using CMOS

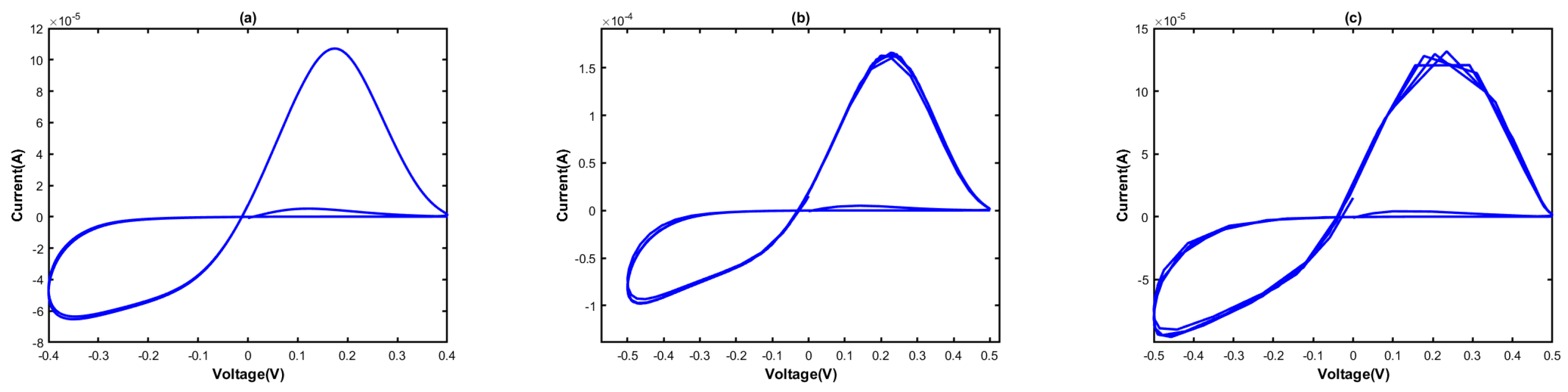

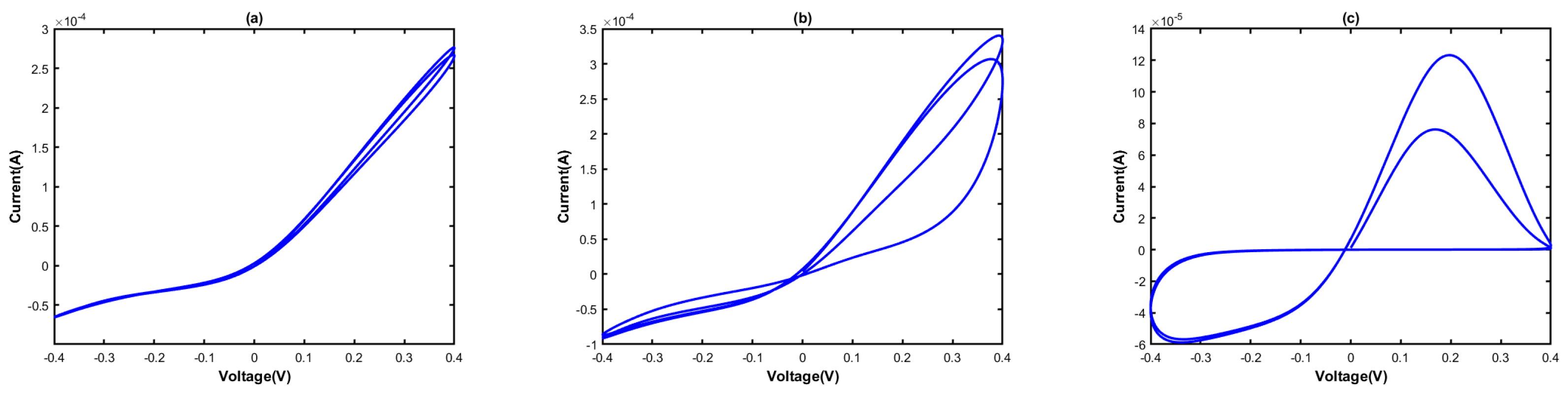

4. Simulation Results and Discussion

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Cao, Y.; Zheng, W.; Zhao, X.; Chang, C.H. An Energy-Efficient Current-Starved Inverter Based Strong Physical Unclonable Function with Enhanced Temperature Stability. IEEE Access 2019, 7, 105287–105297. [Google Scholar] [CrossRef]

- Ananda, Y.R.; Raj, N.; Trivedi, G. A MOS-DTMOS Implementation of Floating Memristor Emulator for High-Frequency Applications. IEEE Trans. Very Large Scale Integr. Syst. 2023, 31, 355–368. [Google Scholar]

- Mokhtar, S.M.A.B.; Abdullah, W.F.H. Memristor-CMOS interfacing circuit SPICE model. In Proceedings of the 2015 IEEE Symposium on Computer Applications & Industrial Electronics (ISCAIE), Langkawi, Malaysia, 12–14 April 2015; pp. 147–150. [Google Scholar]

- Mokhtar, S.M.A.; Abdullah, W.F.H.; Kadiran, K.A.; Rifin, R.; Omar, M. Write and read circuit for memristor analog resistance switching. In Proceedings of the 2017 IEEE 8th Control and System Graduate Research Colloquium (ICSGRC), Shah Alam, Malaysia, 4–5 August 2017; pp. 13–16. [Google Scholar]

- Raja, T.; Mourad, S. Digital logic implementation in memristor-based crossbars. In Proceedings of the 2009 International Conference on Communications, Circuits and Systems, Milpitas, CA, USA, 23–25 July 2009; IEEE: Piscataway, NJ, USA, 2009; pp. 939–943. [Google Scholar]

- Kvatinsky, S.; Satat, G.; Wald, N.; Friedman, E.G.; Kolodny, A.; Weiser, U.C. Memristor-based material implication (IMPLY) logic: Design principles and methodologies. IEEE Trans. Very Large Scale Integr. Syst. 2013, 22, 2054–2066. [Google Scholar] [CrossRef]

- Yadav, P.; Das, B. Memristor-based Memory Cell with Less Noise Margins and Storing Non-Binary Data. In Physics of Semiconductor Devices: 17th International Workshop on the Physics of Semiconductor Devices 2013; Springer: Berlin/Heidelberg, Germany, 2014; pp. 183–187. [Google Scholar]

- Smagulova, K.; Tankimanova, A.; James, A.P. CMOS-Memristor Hybrid Integrated Pixel Sensors. In Proceedings of the 2016 IEEE International Symposium on Nanoelectronic and Information Systems (iNIS), Gwalior, India, 19–21 December 2016; pp. 34–37. [Google Scholar]

- Mokhtar, S.M.A.B.; Abdullah, W.F.H. Re-model fabricated memristor behavior in LT-SPICE and applied in logic circuit. In Proceedings of the 2014 IEEE Symposium on Computer Applications and Industrial Electronics (ISCAIE), Penang, Malaysia, 7–8 April 2014; pp. 106–110. [Google Scholar]

- Alammari, K.; Ahmadi, A.; Ahmadi, M. Hybrid Memristor-CMOS Based Up-Down Counter Design. In Proceedings of the 2020 27th IEEE International Conference on Electronics, Circuits and Systems (ICECS), Glasgow, UK, 23–25 November 2020; pp. 1–4. [Google Scholar]

- Nissi, V.G.; Musala, S.; Veerayya, J. Memristor based full subtractor. In Proceedings of the 2022 International Conference on Communication, Computing and Internet of Things (IC3IoT), Chennai, India, 10–11 March 2022; pp. 1–5. [Google Scholar]

- Khurana, P.S.; Singh, K.; Sharma, A. A Hybrid CMOS-Memristor based Programmable Wien Bridge Oscillator. In Proceedings of the 2018 3rd IEEE International Conference on Recent Trends in Electronics, Information & Communication Technology (RTEICT), Bangalore, India, 18–19 May 2018; pp. 2207–2210. [Google Scholar]

- Verma, A.; Akashe, S. Low-power application for nano scaled Memristor based 2:1 multiplexer. In Proceedings of the 2015 International Conference on Communication Networks (ICCN), Gwalior, India, 19–21 November 2015; pp. 33–36. [Google Scholar]

- Peddi, A.; Y, P.S.; Hassan, S.; Polam, S.R.; R, S.K.; K, K.S. Design of Memristor Based Logic Gates for Low-Power Wireless Sensors in Biomedical Applications. In Proceedings of the 2021 6th International Conference on Signal Processing, Computing and Control (ISPCC), Solan, India, 7–9 October 2021; pp. 364–367. [Google Scholar]

- Krestinskaya, O.; James, A.P.; Chua, L.O. Neuromemristive circuits for edge computing: A review. IEEE Trans. Neural Netw. Learn. Syst. 2019, 31, 4–23. [Google Scholar] [CrossRef] [Green Version]

- Hadis, N.S.M.; Abd Manaf, A.; Herman, S.H.; Ngalim, S.H. ROFF/RON ratio of nano-well fluidic memristor sensor towards hydroxide based liquid detection. In Proceedings of the 2015 IEEE 15th International Conference on Nanotechnology (IEEE-Nano), Rome, Italy, 27–30 July 2015; IEEE: Piscataway, NJ, USA, 2015; pp. 1078–1081. [Google Scholar]

- Carrara, S.; Sacchetto, D.; Doucey, M.A.; Baj-Rossi, C.; De Micheli, G.; Leblebici, Y. Memristive-biosensors: A new detection method by using nanofabricated memristors. Sens. Actuators B Chem. 2012, 171, 449–457. [Google Scholar] [CrossRef] [Green Version]

- Sacchetto, D.; Doucey, M.A.; De Micheli, G.; Leblebici, Y.; Carrara, S. New insight on bio-sensing by nano-fabricated memristors. BioNanoScience 2011, 1, 1–3. [Google Scholar] [CrossRef]

- Krestinskaya, O.; James, A.P. Analogue neuro-memristive convolutional dropout nets. Proc. R. Soc. A 2020, 476, 20200210. [Google Scholar] [CrossRef]

- Kabir, M.; Mummadi, T.; Sundaravadivel, P. Poster: Towards Edge-Intelligent Drowning Detection System. In Proceedings of the 16th International Conference on Underwater Networks and Systems, Boston, MA, USA, 14–16 November 2022. [Google Scholar]

- Sundaravadivel, P.; Fitzgerald, A.; Indic, P. i-SAD: An Edge-Intelligent IoT-Based Wearable for Substance Abuse Detection. In Proceedings of the IEEE International Symposium on Smart Electronic Systems (iSES), Rourkela, India, 16–18 December 2019. [Google Scholar]

- Sundaravadivel, P.; Salvatore, P.; Indic, P. M-SID: An IoT-based Edge-intelligent Framework for Suicidal Ideation Detection. In Proceedings of the IEEE 6th World Forum on Internet of Things (WF-IoT), New Orleans, LA, USA, 2–16 June 2020; pp. 1–6. [Google Scholar]

- Fu, T.; Liu, X.; Gao, H.; Ward, J.E.; Liu, X.; Yin, B.; Wang, Z.; Zhuo, Y.; Walker, D.J.; Joshua Yang, J.; et al. Bioinspired bio-voltage memristors. Nat. Commun. 2020, 11, 1861. [Google Scholar] [CrossRef] [Green Version]

- Elwakil, A.S.; Fouda, M.E.; Radwan, A.G. A simple model of double-loop hysteresis behavior in memristive elements. IEEE Trans. Circuits Syst. II Express Briefs 2013, 60, 487–491. [Google Scholar] [CrossRef]

- Kumngern, M. A floating memristor emulator circuit using operational transconductance amplifiers. In Proceedings of the 2015 IEEE International Conference on Electron Devices and Solid-State Circuits (EDSSC), Singapore, 1–4 June 2015; IEEE: Piscataway, NJ, USA, 2015; pp. 679–682. [Google Scholar]

- Sözen, H.; Çam, U. Electronically tunable memristor emulator circuit. Analog. Integr. Circuits Signal Process. 2016, 89, 655–663. [Google Scholar] [CrossRef]

- Sánchez-López, C.; Mendoza-Lopez, J.; Carrasco-Aguilar, M.; Muñiz-Montero, C. A floating analog memristor emulator circuit. IEEE Trans. Circuits Syst. II Express Briefs 2014, 61, 309–313. [Google Scholar]

- Yeşil, A.; Babacan, Y.; Kaçar, F. A new DDCC based memristor emulator circuit and its applications. Microelectron. J. 2014, 45, 282–287. [Google Scholar] [CrossRef]

- Ranjan, R.K.; Rani, N.; Pal, R.; Paul, S.K.; Kanyal, G. Single CCTA based high frequency floating and grounded type of incremental/decremental memristor emulator and its application. Microelectron. J. 2017, 60, 119–128. [Google Scholar] [CrossRef]

- Ayten, U.E.; Minaei, S.; Sağbaş, M. Memristor emulator circuits using single CBTA. AEU-Int. J. Electron. Commun. 2017, 82, 109–118. [Google Scholar] [CrossRef]

- Chua, L. Memristor-the missing circuit element. IEEE Trans. Circuit Theory 1971, 18, 507–519. [Google Scholar] [CrossRef]

- Strukov, D.B.; Snider, G.S.; Stewart, D.R.; Williams, R.S. The missing memristor found. Nature 2008, 453, 80–83. [Google Scholar] [CrossRef]

- Williams, R.S. How we found the missing memristor. IEEE Spectr. 2008, 45, 28–35. [Google Scholar] [CrossRef]

- Shadaram, A.; Mirzakuchaki, S.; Zakerian, F. A one-memristor cell implementation of a non-volatile memory system. Can. J. Electr. Electron. Eng. 2011, 2, 346–352. [Google Scholar]

- Ho, Y.; Huang, G.M.; Li, P. Nonvolatile memristor memory: Device characteristics and design implications. In Proceedings of the 2009 International Conference on Computer-Aided Design, San Jose, CA, USA, 2–5 November 2009; pp. 485–490. [Google Scholar]

- Kim, H.; Sah, M.P.; Yang, C.; Roska, T.; Chua, L.O. Neural synaptic weighting with a pulse-based memristor circuit. IEEE Trans. Circuits Syst. I Regul. Pap. 2011, 59, 148–158. [Google Scholar] [CrossRef]

- Yesil, A. A new grounded memristor emulator based on MOSFET-C. AEU-Int. J. Electron. Commun. 2018, 91, 143–149. [Google Scholar] [CrossRef]

- Ham, S.J.; Mo, H.S.; Min, K.S. Low-Power VDD/3 Write Scheme with Inversion Coding Circuit for Complementary Memristor Array. IEEE Trans. Nanotechnol. 2013, 12, 851–857. [Google Scholar] [CrossRef]

- Truong, S.N.; Shin, S.; Byeon, S.D.; Song, J.; Min, K.S. New Twin Crossbar Architecture of Binary Memristors for Low-Power Image Recognition with Discrete Cosine Transform. IEEE Trans. Nanotechnol. 2015, 14, 1104–1111. [Google Scholar] [CrossRef]

- Jo, K.H.; Jung, C.M.; Min, K.S.; Kang, S.M. Self-Adaptive Write Circuit for Low-Power and Variation-Tolerant Memristors. IEEE Trans. Nanotechnol. 2010, 9, 675–678. [Google Scholar]

- Solovyeva, E.B.; Azarov, V.A. Comparative Analysis of Memristor Models with a Window Function Described in LTspice. In Proceedings of the 2021 IEEE Conference of Russian Young Researchers in Electrical and Electronic Engineering (ElConRus), St. Petersburg, Russia, 26–28 January 2021; pp. 1097–1101. [Google Scholar]

- Mokhtar, S.M.A.B.; Abdullah, W.F.H.W. Memristor based delay element using current starved inverter. In Proceedings of the RSM 2013 IEEE Regional Symposium on Micro and Nanoelectronics, Daerah Langkawi, Malaysia, 25–27 September 2013; pp. 81–84. [Google Scholar]

- Ranjan, R.K.; Raj, N.; Bhuwal, N.; Khateb, F. Single DVCCTA based high frequency incremental/decremental memristor emulator and its application. AEU-Int. J. Electron. Commun. 2017, 82, 177–190. [Google Scholar] [CrossRef]

- Yadav, N.; Rai, S.K.; Pandey, R. New grounded and floating memristor emulators using OTA and CDBA. Int. J. Circuit Theory Appl. 2020, 48, 1154–1179. [Google Scholar] [CrossRef]

- Vista, J.; Ranjan, A. A Simple Floating MOS-Memristor for High-Frequency Applications. IEEE Trans. Very Large Scale Integr. Syst. 2019, 27, 1186–1195. [Google Scholar] [CrossRef]

- Ghosh, M.; Singh, A.; Borah, S.S.; Vista, J.; Ranjan, A.; Kumar, S. MOSFET-Based Memristor for High-Frequency Signal Processing. IEEE Trans. Electron Devices 2022, 69, 2248–2255. [Google Scholar] [CrossRef]

| Components | Frequency | Power Supply | Elements | Technology | Ref. |

|---|---|---|---|---|---|

| DVC-1 | 1 MHz | 2 V | grounded | 0.5 um CMOS | [43] |

| 1 OTA, CDBA | 1 MHz | ±0.9 V | floating | CMOS 0.18 um | [44] |

| MOSFETs | 13 MHz | 1 V | floating | 0.18 um CMOS technology | [45] |

| 1 CBTA and multiplier | 460 kHz | ±0.9 V | grounded | TSMC 0.18 um | [30] |

| 7 transistors | 50 MHz | ±10 V | grounded | CMOS discrete off the shelf elements | [37] |

| nMmos-3, MOS-CAP-1 | 5 MHz | 1.3 V | floating | 90 nm GPDK CMOS | [46] |

| DDCC-1 | 1 MHz | NA | grounded | 0.35 um CMOS technology | [27] |

| This work | 2 kHz | ±0.9 V | grounded | 45 nm and 16 nm CMOS technology |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ghosh, P.K.; Riam, S.Z.; Ahmed, M.S.; Sundaravadivel, P. CMOS-Based Memristor Emulator Circuits for Low-Power Edge-Computing Applications. Electronics 2023, 12, 1654. https://doi.org/10.3390/electronics12071654

Ghosh PK, Riam SZ, Ahmed MS, Sundaravadivel P. CMOS-Based Memristor Emulator Circuits for Low-Power Edge-Computing Applications. Electronics. 2023; 12(7):1654. https://doi.org/10.3390/electronics12071654

Chicago/Turabian StyleGhosh, Prosenjit Kumar, Shah Zayed Riam, Md Sharif Ahmed, and Prabha Sundaravadivel. 2023. "CMOS-Based Memristor Emulator Circuits for Low-Power Edge-Computing Applications" Electronics 12, no. 7: 1654. https://doi.org/10.3390/electronics12071654