An Overview of Multilevel Inverters Lifetime Assessment for Grid-Connected Solar Photovoltaic Applications

Abstract

:1. Introduction

2. Grid-Connected Power Electronic Devices and Failure Mechanisms: Background

2.1. DC–AC Converters (or) Reduced Switch Multilevel Inverters (RSC-MLIs)

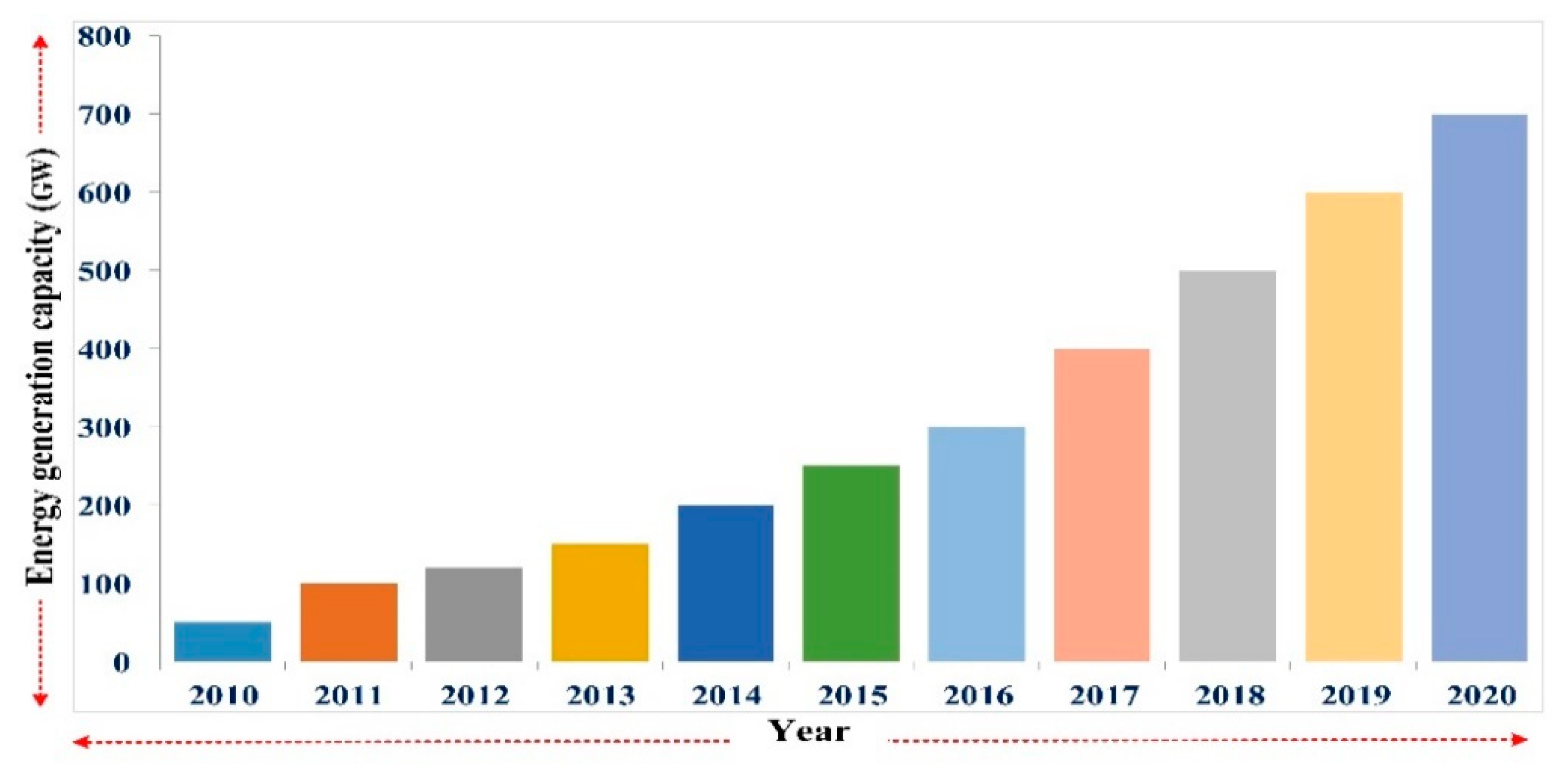

2.1.1. Motivational Factors

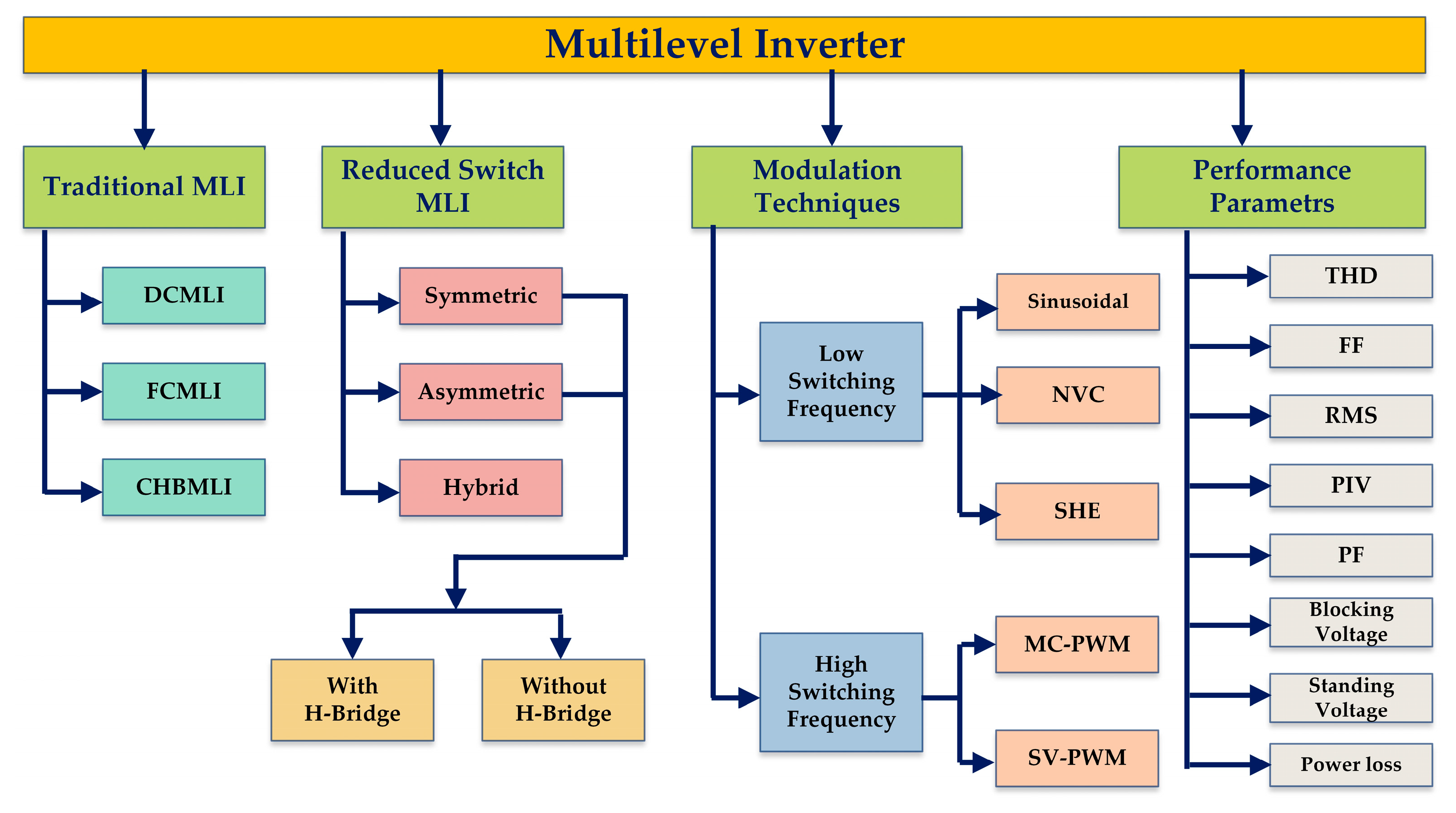

2.1.2. Classification

2.1.3. Assessment Parameters for MLI

2.1.4. Modulation Techniques

- Sine Property: This is a contemporary technique for determining the firing angle to be supplied to the switching devices. By using this approach, calculating the firing angle is simple. To do simulations with ease, the firing angle is often calculated in degrees with the option of converting to any other unit of time, such as “seconds”.

- Space Vector/Nearest Vector Control (SVC/NVC): This operates at a low switching frequency and is an SHE alternative. It does not generate the average load voltage for every switching time such as SHE. SVC selects a vector closest to the reference vector to minimize the distance or space error. The NVC approach is straightforward and appropriate for greater output voltage levels, since the increasing density of vectors generates only modest mistakes concerning the reference vector.

- Selective Harmonic Elimination (SHE): In 1973, researchers proposed SHE, a voltage control and harmonic elimination theory. This method eliminates the most dominating chosen lower-order harmonics. SHE can reduce output filter size and THD. As the switching angles are pre-determined as offline, it is presumed to be open-loop modulation. The firing angle for switching is calculated using multiple Fourier equations, according to the authors. By choosing the firing angle for the Fourier series equation correctly, odd harmonics may be restricted for any MLI level. These firing angles are sent to switches via a microcontroller. Hence, it may be implemented without a closed-loop controller.

- Multi-Carrier Pulse Width Modulation (MC-PWM) technique: This method uses numerous triangular carriers to generate a single modulating sinusoidal signal. The number of carriers is usually (n−1), where n is the inverter level. Carrier disposition PWM and phase-shifted PWM are two forms of MC-PWM.

- Space Vector Pulse Width Modulation (SV-PWM) technique: The reference waveform is modulated by numerous vector states in the SV-PWM approach. This approach generates PWM voltages under a known voltage using digital modulation. This system fails with several levels because sector identification and switching sequence selection are critical. An “n”-level inverter needs “(n − 1)2” vector combinations per sector, six sectors, and “n3” switching sequences. This approach achieves a better fundamental voltage ratio and better harmonic removal than sinusoidal PWM. SV-PWM also has a 15% higher maximum peak output voltage than triangle carrier-based modulation.

2.2. Applications of Multilevel Inverters in Renewable Energy Systems

2.2.1. Solar Photovoltaic (PV) Systems

2.2.2. Wind Energy Conversion Systems (WECS)

2.2.3. Fuel Cells (FC)

2.3. Failure Mechanisms of Modern Power Electronic Devices

2.3.1. Chip-Related Failure Mechanisms

- Dielectric Breakdown: The Failure Mechanisms of Contemporary Power Electronic Devices are listed in Figure 14. A time-dependent dielectric breakdown (TDDB) occurs when gate oxide degrades owing to accumulating faults [25,30]. Impact ionization, anode hole injection, and trap production are described in [31]. Catastrophic/acute dielectric breakdown happens when the device undergoes extreme electrical or thermal stress, such as overvoltage and electrostatic discharge [25,32].

- Latch-Up: IGBTs and MOSFETs can latch up if the parasitic thyristor or bipolar junction transistor structure is activated, causing a loss of gate control. Any excessive current will kill the device if the latch-up is not eliminated [30,33]. High dv/dt causes MOSFET and IGBT latch-up. In [34], heating the IGBT caused a latch-up.

2.3.2. Package-Related Failure Mechanisms

- Bond Wire Failure: Bond wire failures are of two types: (1) Lift-off and (2) heel-cracking bond wire. Mismatching Si and Al CTEs causes bond wire lift-off. During thermal cycling (TC), a fracture forms at the wire-to-device contact, leading to bond wire lift-off. Bond wire heel cracking is caused by fracture fatigue. Thermal cycling alters a bond wire loop’s bending angle by shifting its top. Advanced IGBT modules seldom fatigue [26].

- Solder Fatigue: A typical power module has two solder layers: one between the Si device and DBC and another between the substrate and baseplate in Figure 13. A higher substrate-to-baseplate CTE mismatch causes solder fatigue. Thermal and power cycling cause voids and fractures in solder-attached layers [35]. Void increases thermal resistance, raising die temperature and accelerating void propagation. Die temperatures and void growth generate a positive feedback loop. Heat might harm the gadget. Overheating can induce latch-up and failure to ON [36]. Package issues might cause chip issues.

- Aluminum Reconstruction: Aluminum reconstruction is the aging of silicon chip metallization [37]. Aluminum can undergo reconstruction if compressive and tensile stresses exceed the elastic limit, brought about by the dissimilar CTEs of aluminum and silicon. This mode of failure is prevented by passivation layers [26]. A correlative table may be produced based on IGBT module failure modes and mechanisms to highlight likely failure sites, causes, and impacted parameters [38]. Table 2 summarizes, as follows.

3. Fundamentals of Reliability and Lifespan Evaluation

3.1. Reliability

- The burn-in or early failure period, during which the hazard function tends to diminish with time.

- There is a constant danger function during the random failure.

- The deterioration period, where the threat function rises.

3.2. Failure

3.3. Failure Rate

3.4. “Mean Time to Failure” (MTTF)

3.5. “Mean Time to Repair” (MTTR)

3.6. “Mean Time between Failures” (MTBF)

3.7. “Availability” and “Average Availability”

3.8. Methodology for Lifespan Evaluation

3.8.1. Approximate Technique

3.8.2. Exact Technique

3.9. Results and Discussion

- Diodes

- DC-link capacitors

- IGBT switches

Series Redundancy

4. The Effects of PV Array Size on the Durability and Reliability of PV Inverters

4.1. Mission-Profile-Based Lifetime Estimation

4.2. Monte Carlo Simulation-Based Lifetime Estimation

4.2.1. Mission Profile Translation to Thermal Loading

4.2.2. Thermal Cycle Counting

4.2.3. Estimation of the Lifetime Consumption

5. Challenges and Future Work

- Challenges:

- Accelerated aging usually targets one failure mode such as gate oxide deterioration, latch-up, short circuit, bond wire fatigue, etc. In reality, numerous stresses cause device or module breakdowns. Certain mission-profile-based tests cannot replicate operating situations.

- In many practical applications, all failure prediction factors may not be measurable, limiting aging information.

- Due to accessibility and environmental considerations, live condition monitoring may not be possible in some applications.

- Several electrical characteristics, such as RDSON, Vth, etc., differ amongst devices of the same batch due to differences in manufacturing procedures. To create future condition monitoring for each device/module, a baseline must be established before installation.

- The equipment in real-life operation receives changing loads and different stresses; however, accelerated testing is often done for a constant loading situation.

- None of the lifespan prediction models are scalable, meaning that simulating the aging of a lower-rated device would not shed light on the aging of a similar, higher-rated device. In particular, for broad bandgap devices, the magnitude of the parasitic parameters does not rise linearly with the higher rating of the device, and it varies considerably, even among the same rated devices.

- To fulfill the high grid code requirements and handle the power quality concerns cost-effectively, researchers have, lately, started to design hybrid topologies. It is necessary to explore the performance of these innovative topologies in grid-integrated applications, since most of them have not been assessed in grid-connected RESs.

- For the grid-connected RES applications, further research is required into the performance analysis of contemporary MLIs. Smart grid solutions need to take MLIs into account as well.

- Opportunities:

- Now, there is a window of opportunity to investigate the reliability concerns of emerging technologies that make use of wide bandgap semiconductors.

- We will be able to access the modules in any practical application if we develop a universal strategy, such as integrating a reflectometry method at the gate drives and gathering all required data.

- The rating of the prognostic hardware will be greatly reduced by moving to the gate terminal in addition to providing access to every power electronic device at the lower potential terminals.

- To prevent measuring any electrical parameters and ensure there is no human mistake, Spread-spectrum time-domain reflectometry (SSTDR)-based live condition monitoring might be recommended.

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

Abbreviations

| MLIs | Multilevel Inverters |

| CHB-MLI | Cascaded H-Bridge Multilevel Inverter |

| TSV | Total Standing Voltage |

| PV | Photovoltaic |

| MPPT | Maximum Power Point Tracking |

| THD | Total Harmonic Distortion |

| EMI | Electro-Magnetic Interference |

| MMC | Modular Multilevel Converter |

| FC-MLI | Flying Capacitor Multilevel Inverter |

| SOC | State of Charge |

| NPC | Neutral Point Clamped |

| BESS | Battery Energy Storage System |

| PWM | Pulse Width Modulation |

| FR | Failure rate |

| MTTF | Mean time to failure |

| MTTR | Mean time to repair |

| MTBF | Mean time between failures |

| PI | Proportional plus Integral controller |

| SHE | Selective harmonic elimination |

| NVC | Nearest vector control |

| PWM | Pulse width modulation |

| SVPWM | Space vector pulse width modulation |

| RSC-MLI | Reduced switch count multilevel inverter |

| TDDB | Time-dependent dielectric breakdown |

| MOSFET | Metal–oxide–semiconductor field-effect transistor |

| IGBT | Insulated Gate Bipolar Transistor |

Nomenclature

| λp | Expected failure rate |

| λO | Failure rate due to operational stresses |

| λe | Failure rate due to environmental stresses |

| λC | Failure rate due to temperature cycling stresses |

| λSj | Failure rate due to solder joints |

| λi | Failure rate due to induced stresses |

| A | Scaling factor for the rate of failure |

| T | Temperature, |

| ΔT | Change in temperatures |

| S | Stress ratio |

| λb | Switch and diode base failure rates |

| THS | Inductor’s hot spot (heat sink) temperature |

| TA | Ambient temperature |

| πT | Temperature factor of switch and diode |

| TC | Heat sink temperature |

| θjc | Thermal resistance of the diode or switch |

| Ploss | Power loss of the diode or switch: |

| VS | Ratio of operating voltage to rated voltage. |

| πCV | Failure rate of capacitors |

| πQ | Quality factor |

| πE | Environmental factor |

| πA | Application factor |

| πC | Contact construction factor |

References

- Hasan, K.; Yousuf, S.B.; Tushar, M.S.H.K.; Das, B.K.; Das, P.; Islam, S. Effects of different environmental and operational factors on the PV performance: A comprehensive review. Energy Sci. Eng. 2021, 10, 656–675. [Google Scholar] [CrossRef]

- Alavi, O.; Viki, A.H.; Shamlou, S. A Comparative Reliability Study of Three Fundamental Multilevel Inverters Using Two Different Approaches. Electronics 2016, 5, 18. [Google Scholar] [CrossRef]

- Dhanamjayulu, C.; Prasad, D.; Padmanaban, S.; Maroti, P.K.; Holm-Nielsen, J.B.; Blaabjerg, F. Design and Implementation of Seventeen Level Inverter With Reduced Components. IEEE Access 2021, 9, 16746–16760. [Google Scholar] [CrossRef]

- Dhanamjayulu, C.; Padmanaban, S.; Holm-Nielsen, J.B.; Blaabjerg, F. Design and Implementation of a Single-Phase 15-Level Inverter With Reduced Components for Solar PV Applications. IEEE Access 2020, 9, 581–594. [Google Scholar] [CrossRef]

- Khasim, S.R.; Dhanamjayulu, C.; Padmanaban, S.; Holm-Nielsen, J.B.; Mitolo, M. A Novel Asymmetrical 21-Level Inverter for Solar PV Energy System With Reduced Switch Count. IEEE Access 2021, 9, 11761–11775. [Google Scholar] [CrossRef]

- Dhanamjayulu, C.; Rudravaram, V.; Sanjeevikumar, P. Design and implementation of a novel 35-level inverter topology with reduced switch count. Electr. Power Syst. Res. 2022, 212, 108641. [Google Scholar] [CrossRef]

- Khasim, S.R.; Dhanamjayulu, C. Design and Implementation of Asymmetrical Multilevel Inverter With Reduced Components and Low Voltage Stress. IEEE Access 2022, 10, 3495–3511. [Google Scholar] [CrossRef]

- Rodriguez, J.; Lai, J.-S.; Peng, F.Z. Multilevel inverters: A survey of topologies, controls, and applications. IEEE Trans. Ind. Electron. 2002, 49, 724–738. [Google Scholar] [CrossRef]

- Dhanamjayulu, C.; Padmanaban, S. A Novel Neutral Point Clamped Symmetrical Boost Inverters with Reduced Components. In Proceedings of the 2021 IEEE 12th Energy Conversion Congress & Exposition-Asia (ECCE-Asia), Singapore, 24–27 May 2021; pp. 1431–1436. [Google Scholar] [CrossRef]

- Prasad, D.; Dhanamjayulu, C.; Padmanaban, S.; Holm-Nielsen, J.B.; Blaabjerg, F.; Khasim, S.R. Design and Implementation of 31-Level Asymmetrical Inverter with Reduced Components. IEEE Access 2021, 9, 22788–22803. [Google Scholar] [CrossRef]

- Rodriguez, J.; Bernet, S.; Wu, B.; Pontt, J.O.; Kouro, S. Multilevel Voltage-Source-Converter Topologies for Industrial Medium-Voltage Drives. IEEE Trans. Ind. Electron. 2007, 54, 2930–2945. [Google Scholar] [CrossRef]

- Rodriguez, J.; Bernet, S.; Steimer, P.K.; Lizama, I.E. A Survey on Neutral-Point-Clamped Inverters. IEEE Trans. Ind. Electron. 2010, 57, 2219–2230. [Google Scholar] [CrossRef]

- Kouro, S.; Leon, J.I.; Vinnikov, D.; Franquelo, L.G. Grid-Connected Photovoltaic Systems: An Overview of Recent Research and Emerging PV Converter Technology. IEEE Ind. Electron. Mag. 2015, 9, 47–61. [Google Scholar] [CrossRef]

- Hassaine, L.; Olias, E.; Quintero, J.; Salas, V. Overview of power inverter topologies and control structures for grid connected photovoltaic systems. Renew. Sustain. Energy Rev. 2014, 30, 796–807. [Google Scholar] [CrossRef]

- Daher, S.; Schmid, J.; Antunes, F.L.M. Multilevel Inverter Topologies for Stand-Alone PV Systems. IEEE Trans. Ind. Electron. 2008, 55, 2703–2712. [Google Scholar] [CrossRef]

- Murugesan, M.; Pari, R.; Sivakumar, R.; Sivaranjani, S. Different types of multilevel inverter topologies—A technical Review. Int. J. Adv. Engg. Tech. 2016, 7, 155. [Google Scholar]

- Hasan, N.S.; Rosmin, N.; Osman, D.A.A.; Musta’amal@Jamal, A.H. Reviews on multilevel converter and modulation techniques. Renew. Sustain. Energy Rev. 2017, 80, 163–174. [Google Scholar] [CrossRef]

- Kala, P.; Arora, S. A comprehensive study of classical and hybrid multilevel inverter topologies for renewable energy applications. Renew. Sustain. Energy Rev. 2017, 76, 905–931. [Google Scholar] [CrossRef]

- Shehu, G.S.; Kunya, A.B.; Shanono, I.H.; Yalcinoz, T. A Review of Multilevel Inverter Topology and Control Techniques. J. Autom. Control. Eng. 2016, 4, 233–241. [Google Scholar] [CrossRef]

- Nyamathulla, S.; Dhanamjayulu, C. Design of 17-Level Inverter with Reduced Switch Count. In Proceedings of the 2021 Innovations in Power and Advanced Computing Technologies (i-PACT), Kuala Lumpur, Malaysia, 27–29 November 2021; pp. 1–8. [Google Scholar]

- Chattopadhyay, S.K.; Chakraborty, C. Three-Phase Hybrid Cascaded Multilevel Inverter Using Topological Modules With 1:7 Ratio of Asymmetry. IEEE J. Emerg. Sel. Top. Power Electron. 2018, 6, 2302–2314. [Google Scholar] [CrossRef]

- Callegari, J.; Silva, M.; de Barros, R.; Brito, E.; Cupertino, A.; Pereira, H. Lifetime evaluation of three-phase multifunctional PV inverters with reactive power compensation. Electr. Power Syst. Res. 2019, 175, 105873. [Google Scholar] [CrossRef]

- Hanif, A.; Yu, Y.; DeVoto, D.; Khan, F.H. A Comprehensive Review Toward the State-of-the-Art in Failure and Lifetime Predictions of Power Electronic Devices. IEEE Trans. Power Electron. 2018, 34, 4729–4746. [Google Scholar] [CrossRef]

- Yang, S.; Xiang, D.; Bryant, A.; Mawby, P.; Ran, L.; Tavner, P. Condition Monitoring for Device Reliability in Power Electronic Converters: A Review. IEEE Trans. Power Electron. 2010, 25, 2734–2752. [Google Scholar] [CrossRef]

- Wang, C.; Ji, B.; Song, X.; Pickert, V.; Cao, W. IGBT condition monitoring with system identification methods. In Proceedings of the 2014 IEEE Conference and Expo Transportation Electrification Asia-Pacific (ITEC Asia-Pacific), Beijing, China, 31 August–3 September 2014. [Google Scholar] [CrossRef]

- Physical Characterization Group. Selected failure mechanisms of modern power modules. Microelectron. Reliab. 2002, 42, 653–667. [Google Scholar] [CrossRef]

- Krebs, T.; Duch, S.; Schmitt, W.; Kotter, S.; Prenosil, P.; Thomas, S. A breakthrough in power electronics reliability New die attach and wire bonding materials. In Proceedings of the 2013 IEEE 63rd Electronic Components and Technology Conference, Las Vegas, NV, USA, 28–31 May 2013; pp. 1746–1752. [Google Scholar] [CrossRef]

- Hinata, Y.; Horio, M.; Ikeda, Y.; Yamada, R.; Takahashi, Y. Full SiC power module with advanced structure and its solar inverter application. In Proceedings of the 2013 Twenty-Eighth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 17–21 March 2013; pp. 604–607. [Google Scholar] [CrossRef]

- Nguyen, T.-T.; Ahmed, A.; Thang, T.V.; Park, J.-H. Gate Oxide Reliability Issues of SiC MOSFETs Under Short-Circuit Operation. IEEE Trans. Power Electron. 2014, 30, 2445–2455. [Google Scholar] [CrossRef]

- Vaalasranta, I.; Pippola, J.; Frisk, L. Power MOSFET failure and degradation mechanisms in fly back topology under high temperature and high humidity conditions. In Proceedings of the 9th 2013 9th IEEE International Symposium on Diagnostics for Electric Machines, Power Electronics and Drives (SDEMPED), Valencia, Spain, 27–30 August 2013; pp. 16–22. [Google Scholar]

- Lombardo, S.; Stathis, J.H.; Linder, B.P.; Pey, K.L.; Palumbo, F.; Tung, C.H. Dielectric breakdown mechanisms in gate oxides. J. Appl. Phys. 2005, 98, 121301. [Google Scholar] [CrossRef]

- Sonnenfeld, G.; Goebel, K.; Celaya, J.R. An agile accelerated aging, characterization and scenario simulation system for gate controlled power transistors. In Proceedings of the 2008 IEEE AUTOTESTCON, Salt Lake City, UT, USA, 8–11 September 2008; pp. 208–215. [Google Scholar] [CrossRef]

- Benbahouche, L.; Merabet, A.; Zegadi, A. A comprehensive analysis of failure mechanisms: Latch up and second breakdown in IGBT(IXYS) and improvement. In Proceedings of the 2012 19th International Conference on Microwaves, Radar & Wireless Communications, Warsaw, Poland, 21–23 May 2012; Volume 1, pp. 190–192. [Google Scholar] [CrossRef]

- Patil, N.; Celaya, J.; Das, D.; Goebel, K.; Pecht, M. Precursor Parameter Identification for Insulated Gate Bipolar Transistor (IGBT) Prognostics. IEEE Trans. Reliab. 2009, 58, 271–276. [Google Scholar] [CrossRef]

- Bouarroudj, M.; Khatir, Z.; Ousten, J.-P.; Lefebvre, S. Temperature-Level Effect on Solder Lifetime During Thermal Cycling of Power Modules. IEEE Trans. Device Mater. Reliab. 2008, 8, 471–477. [Google Scholar] [CrossRef]

- Patil, N.; Das, D.; Pecht, M. A prognostic approach for non-punch through and field stop IGBTs. Microelectron. Reliab. 2011, 52, 482–488. [Google Scholar] [CrossRef]

- Pietranico, S.; Lefebvre, S.; Pommier, S.; Bouaroudj, M.B.; Bontemps, S. A study of the effect of degradation of the aluminum metallization layer in the case of power semiconductor devices. Microelectron. Reliab. 2011, 51, 1824–1829. [Google Scholar] [CrossRef]

- Valentine, N.; Das, D.; Pecht, M. Failure mechanisms of insulated gate bipolar transistors (IGBTs). In Proceedings of the NREL Photovoltaic Reliability Workshop 2015, Golden, CO, USA, 24–27 February 2015; pp. 6–10. [Google Scholar]

- Lee, Y.; Hwang, D. A study on the techniques of estimating the probability of failure. J. Chungcheong Math. Soc. 2008, 21, 573–583. [Google Scholar]

- Song, Y.; Wang, B. Survey on Reliability of Power Electronic Systems. IEEE Trans. Power Electron. 2012, 28, 591–604. [Google Scholar] [CrossRef]

- Wang, H.; Ma, K.; Blaabjerg, F. Design for reliability of power electronic systems. In Proceedings of the 38th Annual Conference on IEEE Industrial Electronics Society, Montreal, QC, Canada, 25–28 October 2012; pp. 33–44. [Google Scholar]

- Dhanamjayulu, C.; Sanjeevikumar, P.; Muyeen, S.M. A structural overview on transformer and transformer-less multilevel inverters for renewable energy applications. Energy Rep. 2022, 8, 10299–10333. [Google Scholar]

- Klutke, G.; Kiessler, P.; Wortman, M. A critical look at the bathtub curve. IEEE Trans. Reliab. 2003, 52, 125–129. [Google Scholar] [CrossRef]

- Birolini, A. Reliability Engineering, 5th ed.; Springer: Berlin/Heidelberg, Germany, 2007. [Google Scholar]

- Lyu, M.R. Handbook of Software Reliability Engineering; IEEE Computer Society Press & McGraw-Hill: Hightstown, NJ, USA, 1996. [Google Scholar]

- Stapelberg, R.F. Handbook of Reliability, Availability, Maintainability and Safety in Engineering Design; Springer Science & Business Media: Berlin/Heidelberg, Germany, 2009. [Google Scholar]

- Rausand, M.; Hoyland, A. System Reliability Theory: Models, Statistical Methods, and Applications; John Wiley & Sons: Hoboken, NJ, USA, 2004. [Google Scholar]

- Yang, N.; Dhillon, B. Availability analysis of a repairable standby human-machine system. Microelectron. Reliab. 1995, 35, 1401–1413. [Google Scholar] [CrossRef]

- Goel, A. A New Approach to Electronic Systems Reliability Assessment. Ph.D. Thesis, Rensselaer Polytechnic Institute, Troy, NY, USA, 2007. [Google Scholar]

- Abdi, B.; Ranjbar, A.H.; Gharehpetian, G.B.; Milimonfared, J. Reliability Considerations for Parallel Performance of Semiconductor Switches in High-Power Switching Power Supplies. IEEE Trans. Ind. Electron. 2009, 56, 2133–2139. [Google Scholar] [CrossRef]

- Ranjbar, A.H.; Abdi, B.; Gharehpetian, G.B.; Fahimi, B. Reliability assessment of single-stage/two-stage PFC converters. In Proceedings of the 2009 Compatibility and Power Electronics, Badajoz, Spain, 20–22 May 2009; pp. 253–257. [Google Scholar] [CrossRef]

- SAE G-11 Committee. Aerospace Information Report on Reliability Prediction Methodologies for Electronic Equipment AIR5286; Draft Report; SAE: Warrendale, PA, USA, 1998. [Google Scholar]

- Siemens, A.G. Siemens Company Standard SN29500 (Version 6.0). Failure Rates of Electronic Components. Siemens Technical Liaison and Standardization; Siemens AG: Munich, Germany, 1999. [Google Scholar]

- Union Technique de L’Electricité. RDF 2000: Reliability Data Handbook; Union Technique de L’Electricité: Nanterre, France, 2000. [Google Scholar]

- Kiran, S.R.; Basha, C.H.H.; Singh, V.P.; Dhanamjayulu, C.; Prusty, B.R.; Khan, B. Reduced Simulative Performance Analysis of Variable Step Size ANN Based MPPT Techniques for Partially Shaded Solar PV Systems. IEEE Access 2022, 10, 48875–48889. [Google Scholar] [CrossRef]

- Telcordia Technologies. Special Report SR-332: Reliability Prediction Procedure for Electronic Equipment (Issue 1); Telcordia Customer Service; Telcordia Technologies AG: Piscataway, NJ, USA, 2001. [Google Scholar]

- British Telecom. Handbook of Reliability Data for Components Used in Telecommunication Systems; British Telecom: Birmingham, UK, 1987. [Google Scholar]

- Pecht, M.; Nash, F. Predicting the reliability of electronic equipment. Proc. IEEE 1994, 82, 992–1004. [Google Scholar] [CrossRef]

- Empowering the Reliability Professional. Available online: http://www.reliasoft.com/ (accessed on 18 December 2011).

- Jones, A.; Hayes, J. A comparison of electronic reliability prediction methodologies. IEEE Trans. Reliab. 1999, 48, 127–134. [Google Scholar] [CrossRef]

- EATON White Paper TD02000001E. The Reliability of Neutral Point Clamped vs. Cascaded H-Bridge Inverters. October 2009. Available online: http://www.eaton.com (accessed on 15 April 2016).

- Krug, D.; Bernet, S.; Fazel, S.S.; Jalili, K.; Malinowski, M. Comparison of 2.3-kV Medium-Voltage Multilevel Converters for Industrial Medium-Voltage Drives. IEEE Trans. Ind. Electron. 2007, 54, 2979–2992. [Google Scholar] [CrossRef]

- Anderson, R.T. Reliability Design Handbook; ITT Research Institute: Chicago, IL, USA, 1976. [Google Scholar]

- Dylis, D.D.; Priore, M.G. A comprehensive reliability assessment tool for electronic systems. In Proceedings of the IEEE Annual Reliability and Maintainability Symposium, Philadelphia, PA, USA, 22–25 January 2001; pp. 308–313. [Google Scholar]

- Lu, H.; Bailey, C.; Yin, C. Design for reliability of power electronics modules. Microelectron. Reliab. 2009, 49, 1250–1255. [Google Scholar] [CrossRef]

- Khosroshahi, A.; Abapour, M.; Sabahi, M. Reliability Evaluation of Conventional and Interleaved DC–DC Boost Converters. IEEE Trans. Power Electron. 2014, 30, 5821–5828. [Google Scholar] [CrossRef]

- Richardeau, F.; Pham, T.T.L. Reliability Calculation of Multilevel Converters: Theory and Applications. IEEE Trans. Ind. Electron. 2012, 60, 4225–4233. [Google Scholar] [CrossRef]

- US Department of Defense. MIL-HDBK-217F (NOTICE 2), Military Handbook Reliability Prediction of Electronic Equipment; Defense Technical Information Center: Alexandria, VA, USA, 1995.

- Graovac, D.; Pürschel, M. IGBT Power Losses Calculation Using the Data-Sheet Parameters; Infineon Application Note; Infineon Technologies AG: Neubiberg, Germany, 2009; pp. 1–17. [Google Scholar]

- Chiodo, E.; Lauria, D. Some Basic Properties of the Failure Rate of Redundant Reliability Systems in Industrial Electronics Applications. IEEE Trans. Ind. Electron. 2015, 62, 5055–5062. [Google Scholar] [CrossRef]

- Li, S.; Xu, L. Strategies of fault tolerant operation for three-level PWM inverters. IEEE Trans. Power Electron. 2006, 21, 933–940. [Google Scholar] [CrossRef]

- Ceballos, S.; Pou, J.; Zaragoza, J.; Martin, J.L.; Robles, E.; Gabiola, I.; Ibanez, P. Efficient Modulation Technique for a Four-Leg Fault-Tolerant Neutral-Point-Clamped Inverter. IEEE Trans. Ind. Electron. 2008, 55, 1067–1074. [Google Scholar] [CrossRef]

- Nguyen-Duy, K.; Liu, T.-H.; Chen, D.-F.; Hung, J.Y. Improvement of Matrix Converter Drive Reliability by Online Fault Detection and a Fault-Tolerant Switching Strategy. IEEE Trans. Ind. Electron. 2011, 59, 244–256. [Google Scholar] [CrossRef]

- Barriuso, P.; Dixon, J.; Flores, P.; Moran, L. Fault-Tolerant Reconfiguration System for Asymmetric Multilevel Converters Using Bidirectional Power Switches. IEEE Trans. Ind. Electron. 2008, 56, 1300–1306. [Google Scholar] [CrossRef]

- Ambusaidi, K.; Pickert, V.; Zahawi, B. New Circuit Topology for Fault Tolerant H-Bridge DC–DC Converter. IEEE Trans. Power Electron. 2009, 25, 1509–1516. [Google Scholar] [CrossRef]

- Pham, T.T.L.; Richardeau, F.; Gateau, G. Diagnosis strategies and reconfiguration of a 5-level double-boost PFC with fault-tolerant capability. In Proceedings of the 2011 IEEE International Symposium on Industrial Electronics, Gdansk, Poland, 27–30 June 2011; pp. 1857–1862. [Google Scholar] [CrossRef]

- Sangwongwanich, A.; Yang, Y.; Sera, D.; Blaabjerg, F. Impacts of PV array sizing on PV inverter lifetime and reliability. In Proceedings of the 2017 IEEE Energy Conversion Congress and Exposition (ECCE), Cincinnati, OH, USA, 1–5 October 2017; pp. 3830–3837. [Google Scholar] [CrossRef]

- Fiorelli, J.; Zuercher-Martinson, M. How oversizing your array to-inverter ratio can improve solar-power system performance. Solar Power World 2013, 7, 42–48. [Google Scholar]

- Khatib, T.; Mohamed, A.; Sopian, K. A review of photovoltaic systems size optimization techniques. Renew. Sustain. Energy Rev. 2013, 22, 454–465. [Google Scholar] [CrossRef]

- Prasad, D.; Dhanamjayulu, C. Reduced Voltage Stress Asymmetrical Multilevel Inverter With Optimal Components. IEEE Access 2022, 10, 53546–53559. [Google Scholar] [CrossRef]

- SMA. 7 Reasons Why You Should Oversize Your PV Array. December 2015. Available online: https://www.sma-sunny.com/en/7-reasons-why-you-should-oversize-your-pv-array-2/ (accessed on 1 January 2022).

- Global Sustainable Energy Solutions (GSES) India. Oversizing PV Arrays; Technical Report; 2014; Available online: https://gses.in/old-gses-in/publications/resources-and-information/oversizing-pv-arrays (accessed on 1 January 2022).

- Solar Edge. Oversizing of Solar Edge Inverters, Technical Note; Technical Report; July 2016; Available online: https://knowledge-center.solaredge.com/sites/kc/files/inverter_dc_oversizing_guide.pdf (accessed on 1 January 2022).

- Prasad, D.; Dhanamjayulu, C. Solar PV-Fed Multilevel Inverter with Series Compensator for Power Quality Improvement in Grid-Connected Systems. IEEE Access 2022, 10, 81203–81219. [Google Scholar] [CrossRef]

- Good, J.; Johnson, J. Impact of inverter loading ratio on solar photovoltaic system performance. Appl. Energy 2016, 177, 475–486. [Google Scholar] [CrossRef]

- Moore, L.M.; Post, H.N. Five years of operating experience at a large, utility-scale photovoltaic generating plant. Prog. Photovolt. Res. Appl. 2008, 16, 249–259. [Google Scholar] [CrossRef]

- Baumgartner, F.; Maier, O.; Schär, D.; Sanchez, D.; Toggweiler, P. Survey of Operation and Maintenance Costs of PV Plants in Switzerland. In Proceedings of the 31st European Photovoltaic Solar. Energy Conference and Exhibition (EU PVSEC 2015), Hamburg, Germany, 14–18 September 2015; pp. 1583–1586. [Google Scholar] [CrossRef]

- Musallam, M.; Yin, C.; Bailey, C.; Johnson, M. Mission Profile-Based Reliability Design and Real-Time Life Consumption Estimation in Power Electronics. IEEE Trans. Power Electron. 2014, 30, 2601–2613. [Google Scholar] [CrossRef]

- Kjaer, S.; Pedersen, J.; Blaabjerg, F. A Review of Single-Phase Grid-Connected Inverters for Photovoltaic Modules. IEEE Trans. Ind. Appl. 2005, 41, 1292–1306. [Google Scholar] [CrossRef]

- Yang, Y.; Blaabjerg, F. Overview of single-phase grid-connected photovoltaic systems. Electr. Power Compon. Syst. 2015, 43, 1352–1363. [Google Scholar] [CrossRef]

- Blaabjerg, F.; Teodorescu, R.; Liserre, M.; Timbus, A.V. Overview of Control and Grid Synchronization for Distributed Power Generation Systems. IEEE Trans. Ind. Electron. 2006, 53, 1398–1409. [Google Scholar] [CrossRef]

- Mondol, J.D.; Yohanis, Y.G.; Norton, B. Optimal sizing of array and inverter for grid-connected photovoltaic systems. Sol. Energy 2006, 80, 1517–1539. [Google Scholar] [CrossRef]

- Chen, S.; Li, P.; Brady, D.; Lehman, B. Determining the optimum grid-connected photovoltaic inverter size. Sol. Energy 2012, 87, 96–116. [Google Scholar] [CrossRef]

- Mounetou, R.; Alcantara, I.B.; Incalza, A.; Justiniano, J.; Loiseau, P.; Piguet, G.; Sabene, A. Oversizing array-to-inverter (dc-ac) ratio: What are the criteria and how to define the optimum? In Proceedings of the 29th European Photovoltaic Solar Energy Conference and Exhibition, Amsterdam, The Netherlands, 22–26 September 2014; pp. 2813–2821. [Google Scholar]

- Faranda, R.S.; Hafezi, H.; Leva, S.; Mussetta, M.; Ogliari, E. The Optimum PV Plant for a Given Solar DC/AC Converter. Energies 2015, 8, 4853–4870. [Google Scholar] [CrossRef]

- Felgemacher, C.; Araujo, S.; Noeding, C.; Zacharias, P.; Ehrlich, A.; Schidleja, M. Evaluation of cycling stress imposed on IGBT modules in PV central inverters in sunbelt regions. In Proceedings of the CIPS, Nuremberg, Germany, 8–10 March 2016; pp. 1–6. [Google Scholar]

- Wang, H.; Liserre, M.; Blaabjerg, F. Toward reliable power electronics: Challenges, design tools, and opportunities. IEEE Ind. Electron. Mag. 2013, 7, 17–26. [Google Scholar] [CrossRef]

- Yang, Y.; Sangwongwanich, A.; Blaabjerg, F. Design for Reliability of Power Electronics for Grid-Connected Photovoltaic Systems. CPSS Trans. Power Electron. Appl. 2016, 1, 92–103. [Google Scholar] [CrossRef]

- Sangwongwanich, A.; Blaabjerg, F. Monte Carlo Simulation with Incremental Damage for Reliability Assessment of Power Electronics. IEEE Trans. Power Electron. 2020, 36, 7366–7371. [Google Scholar] [CrossRef]

- Novak, M.; Sangwongwanich, A.; Blaabjerg, F. Monte Carlo Based Reliability Estimation Methods in Power Electronics. In Proceedings of the 2020 IEEE 21st Workshop on Control and Modeling for Power Electronics (COMPEL), Aalborg, Denmark, 9–12 November 2020; pp. 1–7. [Google Scholar]

- Reigosa, P.D.; Wang, H.; Yang, Y.; Blaabjerg, F. Prediction of bond wire fatigue of IGBTs in a PV inverter under a long-term operation. IEEE Trans. Power Electron. 2016, 31, 7171–7182. [Google Scholar]

- Ma, K.; Wang, H.; Blaabjerg, F. New Approaches to Reliability Assessment: Using physics-of-failure for prediction and design in power electronics systems. IEEE Power Electron. Mag. 2016, 3, 28–41. [Google Scholar] [CrossRef]

- Sangwongwanich, A.; Yang, Y.; Sera, D.; Blaabjerg, F. Lifetime Evaluation of Grid-Connected PV Inverters Considering Panel Degradation Rates and Installation Sites. IEEE Trans. Power Electron. 2017, 33, 1225–1236. [Google Scholar] [CrossRef]

- Chung, H.S.-H.; Wang, H.; Blaabjerg, F.; Pecht, M. Reliability of Power Electronic Converter Systems; IET: Stevenage, UK, 2015. [Google Scholar]

| Properties | Two-Level Inverter | Multilevel Inverter |

|---|---|---|

| Structure | Complicated | Modular |

| Electromagnetic interference (EMI) | High | Low |

| Input current distortions | High | Low |

| Voltage Applications | Low | High |

| Stress on power electronic switches | More | Less |

| Rate of change in voltage | High | Low |

| Production of common-mode voltage | Higher | Lower |

| Power quality performance | Low | High |

| Fault-tolerant operation | Impossible | Possible |

| Harmonic content | Low | High |

| Switching losses | High | Low |

| Production of multiple voltage level | Not possible | Possible |

| The ability of transformer-less operation | No | Yes |

| Efficiency | Low | High |

| Ability to operate at low/high/ fundamental frequency | More | Less |

| Operation at the fundamental frequency | Fails | Can operate |

| Operation at high voltage and current | Can operate (for parallelized structures) | Can operate |

| Failure Mechanism | Location | Causes | Modes | Parameter Affected |

|---|---|---|---|---|

| Hot electrons | Oxide/substrate interface | 1. Overvoltage 2. High current density | High leakage currents | Vth |

| Delamination of die attach | Die attach | 1. High temperature 2. High current density | Open circuit | Vc |

| Time-dependent dielectric breakdown (TDDB) | Oxide layer | 1. High temperature 2. High electric field 3. Overvoltage | 1. Short circuit 2.Increased leakage current 3. Loss of gate control | Vth |

| Bond wire/solder fatigue | Bond wire/solder | 1. High temperature 2. High current density | Open circuit | Vc |

| Latch-up | Silicon Die | 1. Irradiation 2. High electric field 3. Overvoltage | 1. Device burnout 2. Loss of gate control | Vc |

| Application (Pr Rated Output Power) | πA |

|---|---|

| Linear Amplification (Pr < 2 W) Small signal switching | 1.5 0.7 |

| Non-Linear, (Pr ≥ 2 W) 2 ≤ Pr < 5 W 2 ≤ Pr < 5 W 50 ≤ Pr < 250 W Pr ≥ 250 W | 2.0 4.0 8.0 10 |

| Contact Construction | πc |

|---|---|

| Metallurgically Bonded | 1.0 |

| Non-Metallurgically Bonded and Spring-Loaded contacts | 2.0 |

| Name of the Components/Inverter Type | NPC | FC | CHB |

|---|---|---|---|

| IGBTs | 4800 for (12) | 4800 for (12) | 1200 for (12) |

| Capacitors | 600 for (2) | 1500 for (5) | 1200 for (3) |

| Diodes | 1800 for (18) | 1200 for (12) | 1200 for (12) |

| Total FITs | 7200 | 7500 | 3600 |

| Failure Rate (failure/106 h) | 7.2 | 7.5 | 3.6 |

| MTTF (hours) | 138,888 | 133,333 | 277,777 |

| Type | Ploss | Tc | Tj | πT | πA | πE | πQ | |

|---|---|---|---|---|---|---|---|---|

| NPC | 95.27 W | 45 | 68.817 | 2.288 | 10 | 1 | 5.5 | 1.511 |

| FC | 130.5 W | 45 | 77.625 | 2.636 | 10 | 1 | 5.5 | 1.740 |

| CHB | 18.46 W | 45 | 49.615 | 1.637 | 10 | 1 | 5.5 | 1.080 |

| Type | Ploss | Tc | Tj | πT | πC | πS | πE | πQ | |

|---|---|---|---|---|---|---|---|---|---|

| NPC | 11.144 W | 35 | 52.830 | 1.938 | 1 | 1.938 | 1 | 5.5 | 0.0353 |

| FC | 0.088 W | 35 | 35.140 | 1.381 | 1 | 1.381 | 1 | 5.5 | 0.0007 |

| CHB | 1.118 | 35 | 36.789 | 1.427 | 1 | 1.427 | 1 | 5.5 | 0.0064 |

| Type | Capacitor | TA | πcv | πE | πQ | ||

|---|---|---|---|---|---|---|---|

| NPC | 220 mF | 22.7 | 0.045 | 1.471 | 1 | 10 | 0.6619 |

| FC | 2200 µF | 22.7 | 0.065 | 0.856 | 1 | 10 | 0.5565 |

| CHB | 660 µF | 22.7 | 0.102 | 0.733 | 1 | 10 | 0.7472 |

| Parameter | NPC | FC | CHB |

|---|---|---|---|

| Failure Rate (Failure/106 h) | 19.9853 | 23.6709 | 15.2784 |

| MTTF (hours) | 50,036 | 42,245 | 65,451 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Nyamathulla, S.; Chittathuru, D.; Muyeen, S.M. An Overview of Multilevel Inverters Lifetime Assessment for Grid-Connected Solar Photovoltaic Applications. Electronics 2023, 12, 1944. https://doi.org/10.3390/electronics12081944

Nyamathulla S, Chittathuru D, Muyeen SM. An Overview of Multilevel Inverters Lifetime Assessment for Grid-Connected Solar Photovoltaic Applications. Electronics. 2023; 12(8):1944. https://doi.org/10.3390/electronics12081944

Chicago/Turabian StyleNyamathulla, Shaik, Dhanamjayulu Chittathuru, and S. M. Muyeen. 2023. "An Overview of Multilevel Inverters Lifetime Assessment for Grid-Connected Solar Photovoltaic Applications" Electronics 12, no. 8: 1944. https://doi.org/10.3390/electronics12081944

APA StyleNyamathulla, S., Chittathuru, D., & Muyeen, S. M. (2023). An Overview of Multilevel Inverters Lifetime Assessment for Grid-Connected Solar Photovoltaic Applications. Electronics, 12(8), 1944. https://doi.org/10.3390/electronics12081944