A New Symmetrical Source-Based DC/AC Converter with Experimental Verification

Abstract

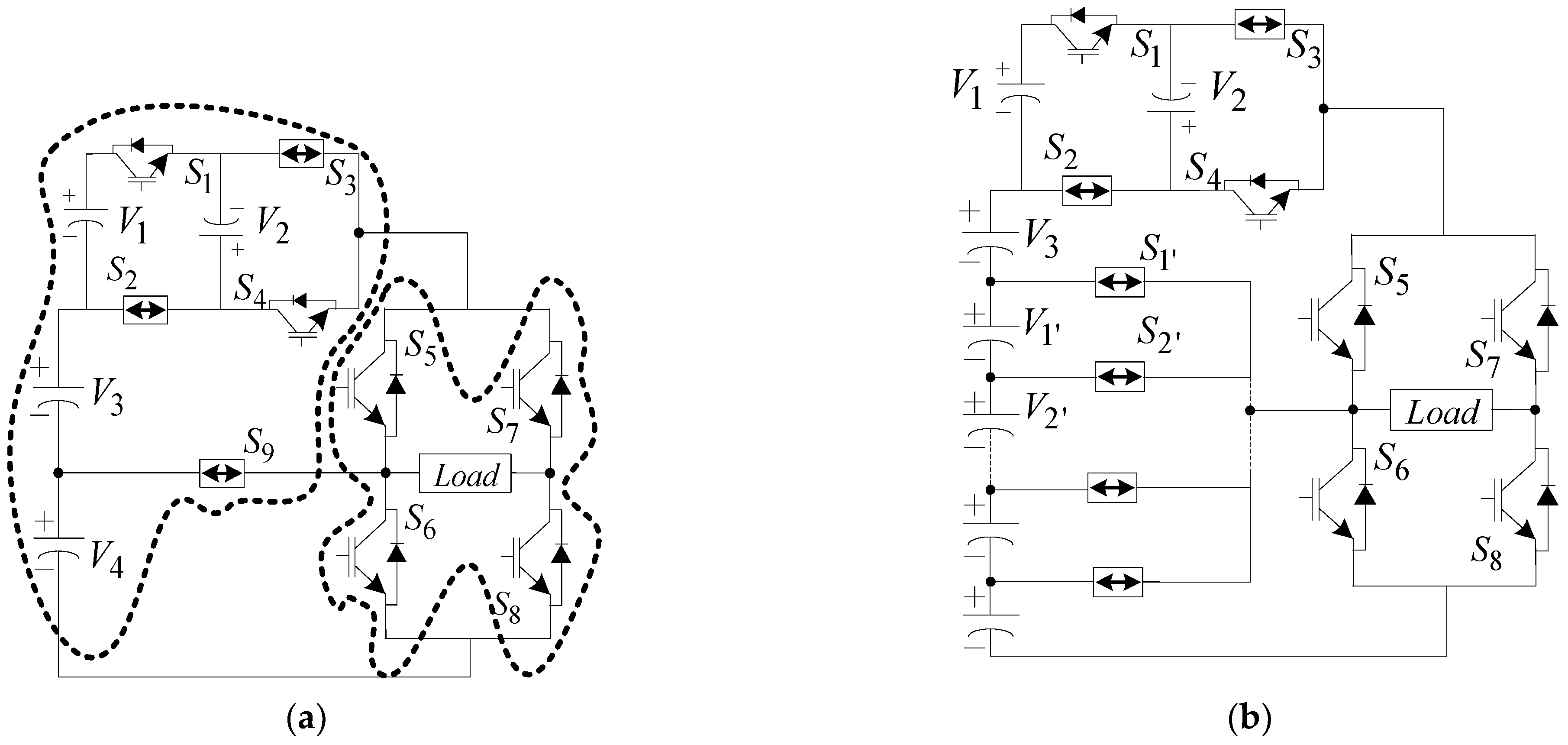

1. Introduction

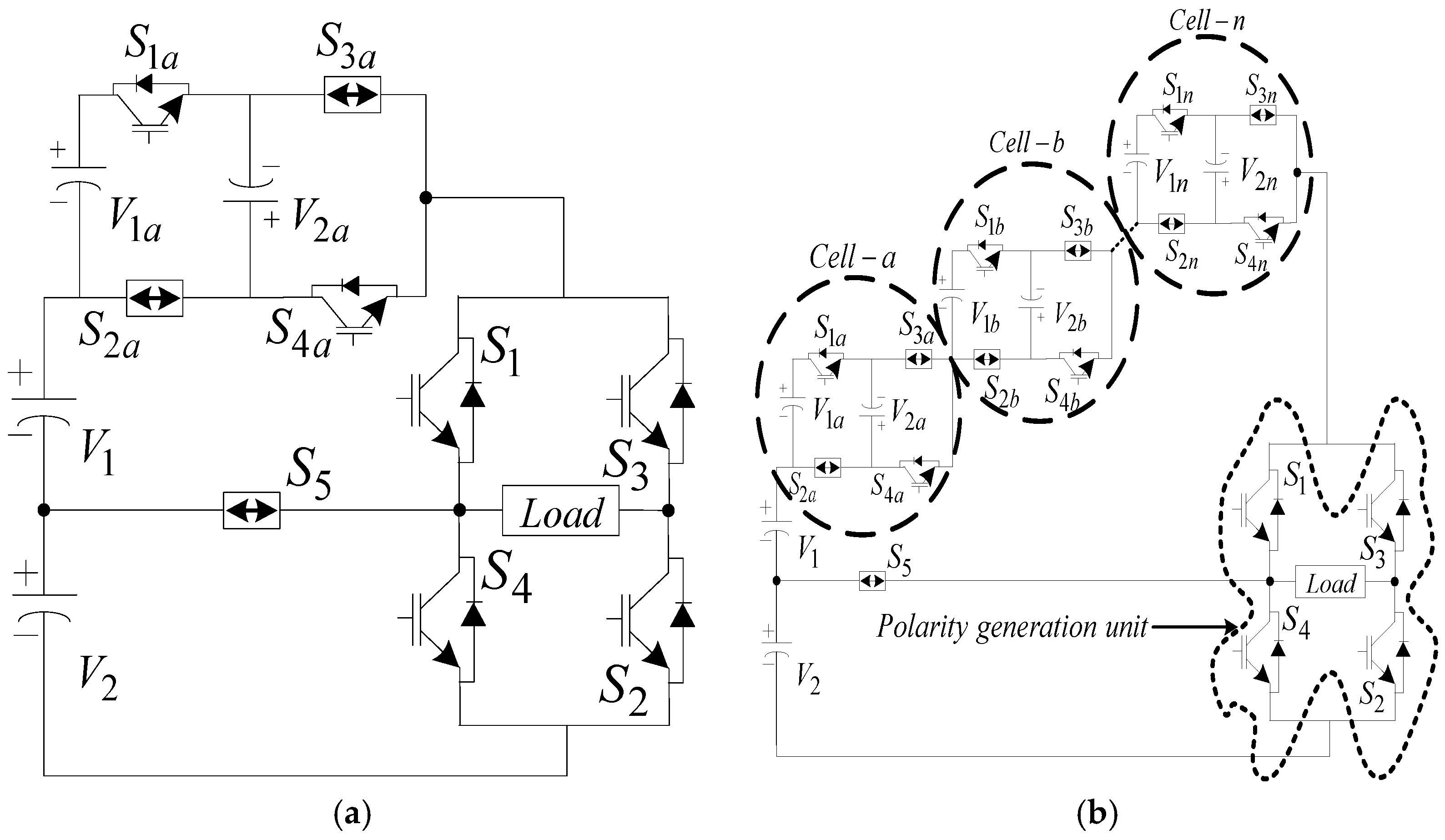

2. Proposed Reduced-Switch Topology

2.1. Circuit Operation of the Proposed Circuit−I

2.2. Circuit Operation of the Proposed Circuit-II

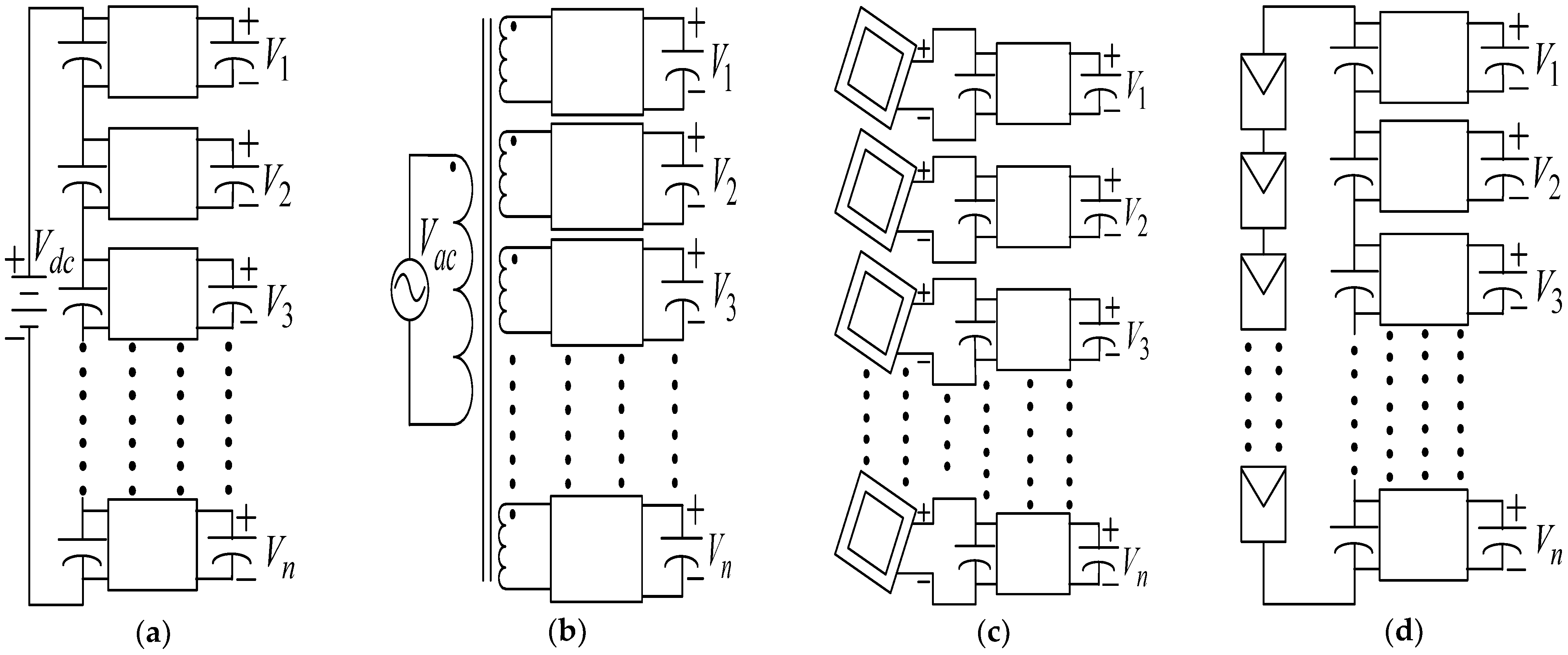

- One DC supply with DC/DC converters is employed for the required capacitors.

- One AC supply is fed to the transformer primary side, with isolated multi-windings on the secondary side, then connected to a bridge rectifier, and fed to the required capacitors.

- Every photovoltaic module is connected with DC/DC converters for the required capacitors.

- Photovoltaic modules connected in series with DC/DC converters are employed for the required capacitors.

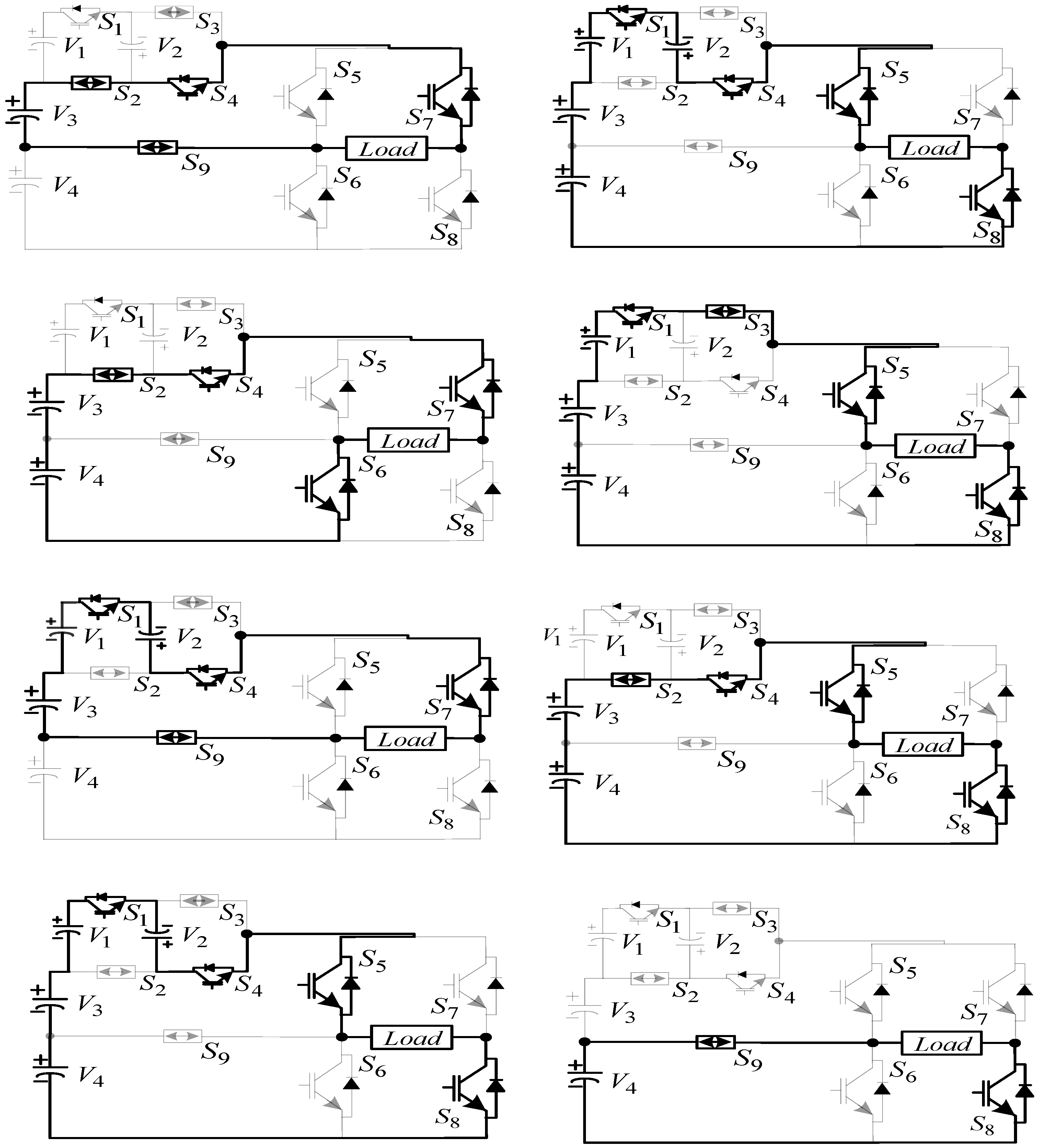

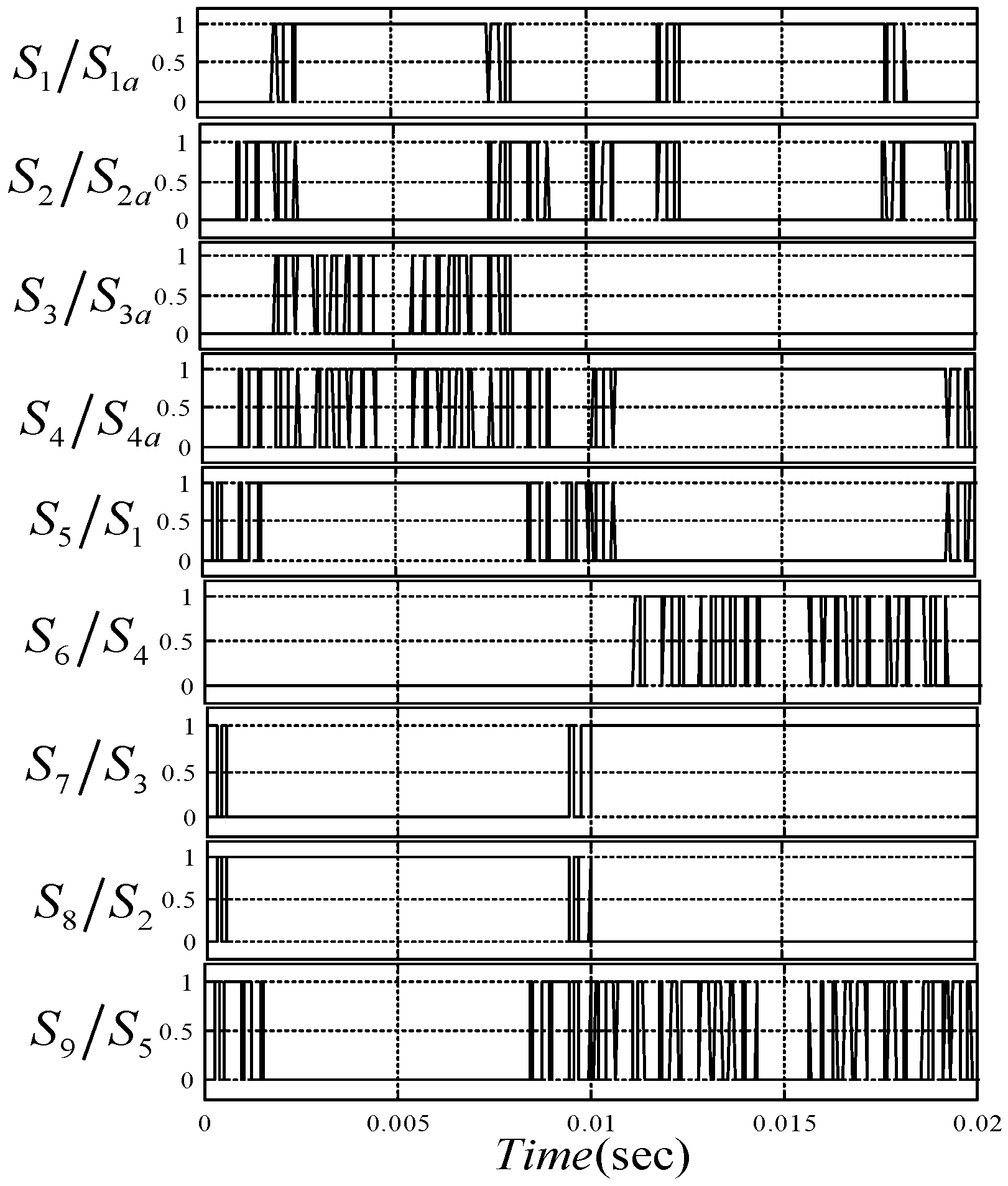

3. Modes of Operation

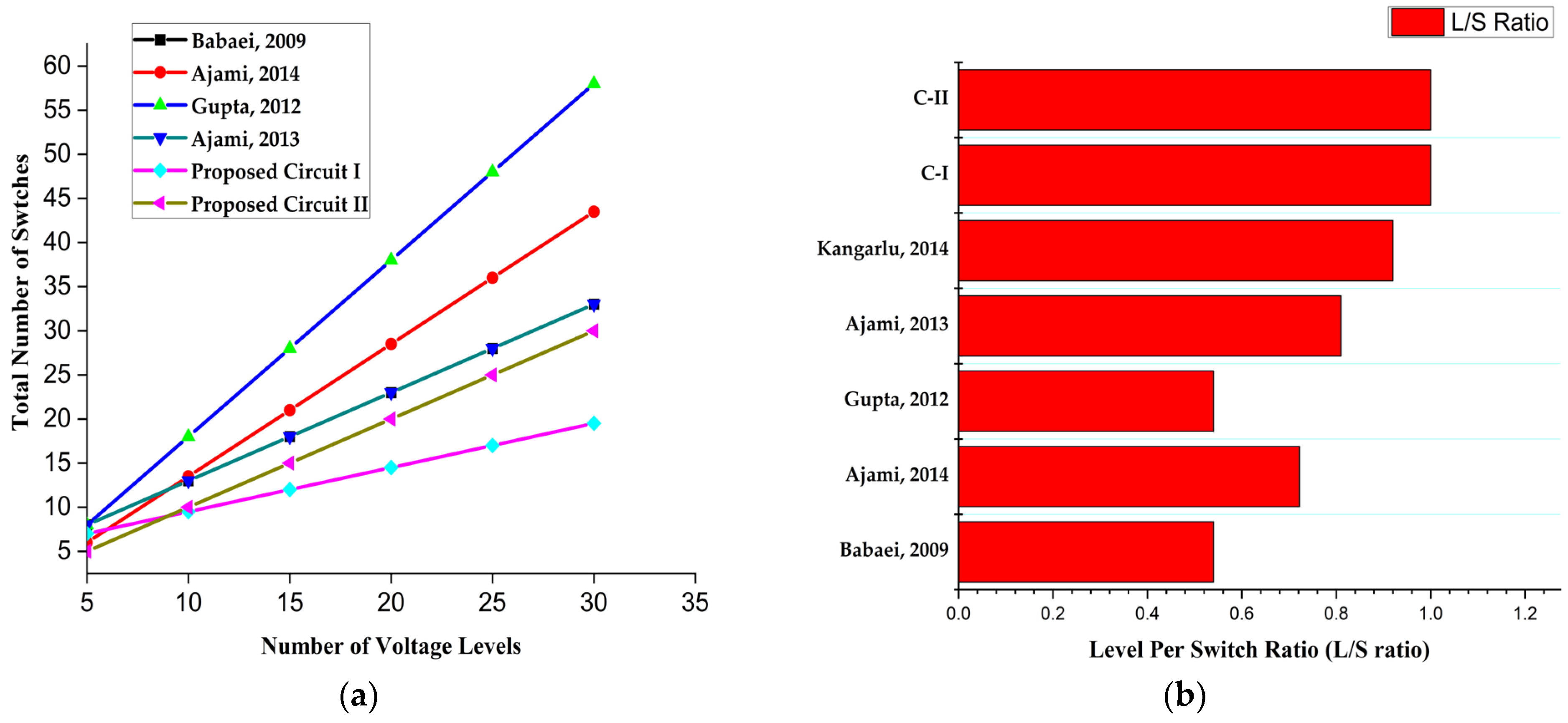

4. Comparison with other MLI Topologies

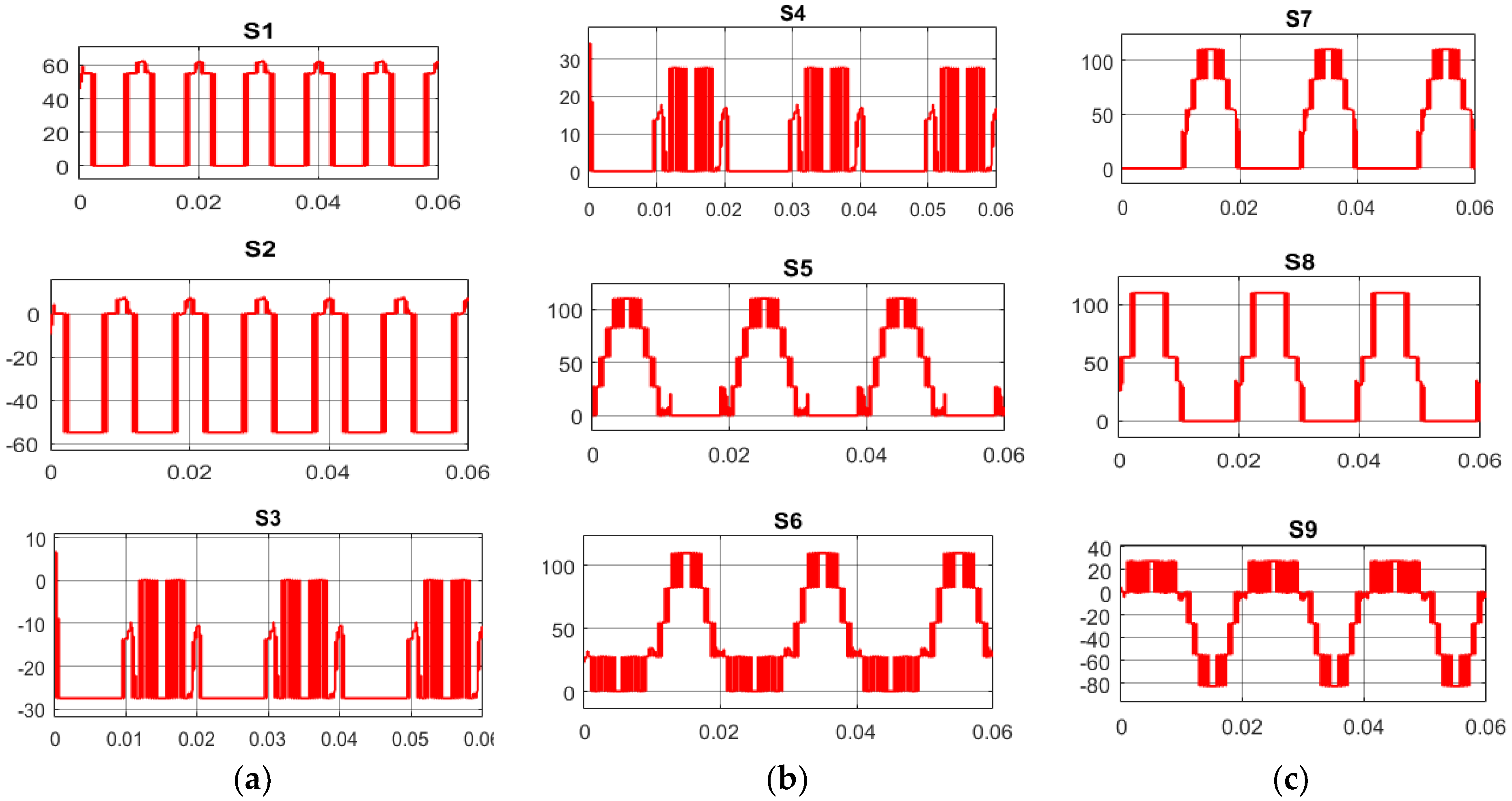

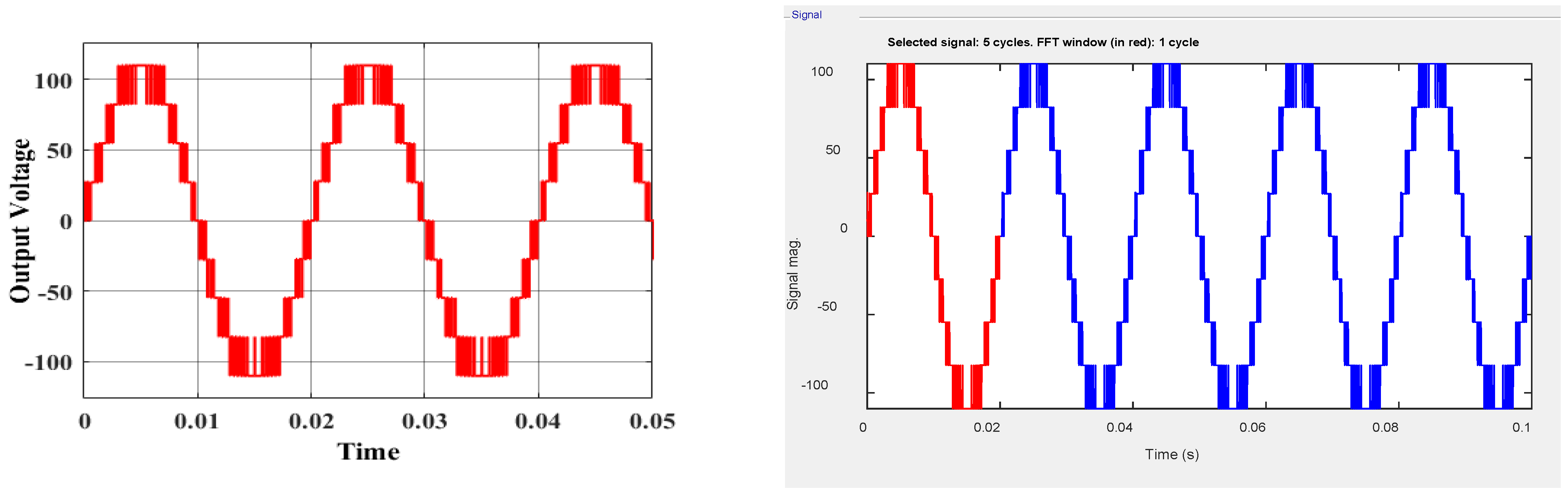

5. Simulation and Experimental Verification

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Correction Statement

References

- Jha, K.K.; Mahato, B.; Prakash, P.; Jana, K.C. Hardware Implementation of Single Phase Power Factor Correction System using Micro-controller. Int. J. Power Electron. Drive Syst. 2016, 7, 787–790. [Google Scholar]

- Rodriguez, J.; Franquelo, L.G.; Kouro, S.; Leon, J.I.; Portillo, R.C.; Prats, M.A.M.; Perez, M.A. Multilevel converters: An enabling technology for high-power applications. Proc. IEEE 2009, 97, 1786–1817. [Google Scholar] [CrossRef]

- Veenstra, M.; Rufer, A. Control of a hybrid asymmetric multilevel inverter for competitive medium-voltage industrial drives. IEEE Trans. Ind. Appl. 2005, 41, 655–664. [Google Scholar] [CrossRef]

- Franquelo, L.G.; Rodriguez, J.; Leon, J.I.; Kouro, S.; Portillo, R.; Prats, M.A. The age of multilevel converters arrives. IEEE Ind. Electron. Mag. 2008, 2, 28–39. [Google Scholar] [CrossRef]

- Mahato, B.; Mittal, S.; Nayak, P.K. Novel Topology of Multi-level Inverter for higher Voltage Steps. In Proceedings of the 2018 International Conference on Recent Trends in Electrical, Control and Communication (RTECC), Malaysia, 20–22 March 2018; pp. 158–163. [Google Scholar]

- Rodriguez, J.; Lai, J.S.; Peng, F.Z. Multilevel Inverters: A survey of topologies, controls, and applications. IEEE Trans. Ind. Electron. 2002, 49, 724–738. [Google Scholar] [CrossRef]

- Mahato, B.; Raushan, R.; Jana, K.C. Modulation and control of multilevel inverter for an open-end winding induction motor with constant voltage levels and harmonics. IET Power Electron. 2017, 10, 71–79. [Google Scholar] [CrossRef]

- Kouro, S.; Malinowski, M.; Gopakumar, K.; Pou, J.; Franquelo, L.G.; Wu, B.; Rodriguez, J.; Pérez, M.A.; Leon, J.I. Recent advances and industrial applications of multilevel converters. IEEE Trans. Ind. Electron. 2010, 57, 2553–2580. [Google Scholar] [CrossRef]

- Jana, K.C.; Jana, K.C.; Majumdar, S.; Pal, P.K.; Mahato, B. Performance Analysis of a Multimodule Staircase (MM-STC)-Type Multilevel Inverter with Reduced Component Count and Improved Efficiency. IEEE J. Emerg. Sel. Top. Power Electron. 2021, 10, 6619–6633. [Google Scholar]

- Lewicki, A.; Krzeminski, Z.; Abu-Rub, H. Space-vector pulsewidth modulation for three-level NPC converter with the neutral point voltage control. IEEE Trans. Ind. Electron. 2011, 58, 5076–5086. [Google Scholar] [CrossRef]

- Abu-Rub, H.; Malinowski, M.; Al-Haddad, K. Power Electronics for Renewable Energy Systems, Transportation and Industrial Applications; John Wiley & Sons: Hoboken, NJ, USA, 2014. [Google Scholar]

- Escalante, M.F.; Vannier, J.C.; Arzandé, A. Flying capacitor multilevel inverters and DTC motor drive applications. IEEE Trans. Ind. Electron. 2002, 49, 809–815. [Google Scholar] [CrossRef]

- Mahto, K.K.; Pal, P.K.; Das, P.; Mittal, S.; Mahato, B. A New Design of Multilevel Inverter Based on T-type Symmetrical and Asymmetrical DC Sources. Iran. J. Sci. Technol. Trans. Electr. Eng. 2022, 47, 639–657. [Google Scholar] [CrossRef]

- Nami, A.; Zare, F.; Ghosh, A.; Blaabjerg, F. A hybrid cascade converter topology with series-connected symmetrical and asymmetrical diode-clamped H-bridge cells. IEEE Trans. Power Electron. 2011, 26, 51–65. [Google Scholar] [CrossRef]

- Gupta, K.K.; Ranjan, A.; Bhatnagar, P.; Sahu, L.K.; Jain, S. Multilevel inverter topologies with reduced device count: A review. IEEE Trans. Power Electron. 2016, 31, 135–151. [Google Scholar] [CrossRef]

- Lezana, P.; Rodríguez, J.; Oyarzún, D.A. Cascaded multilevel inverter with regeneration capability and reduced number of switches. IEEE Trans. Ind. Electron. 2008, 55, 1059–1066. [Google Scholar] [CrossRef]

- Mahato, B.; Ranjan, M.; Pal, P.K.; Gupta, S.K.; Mahto, K.K. Design, development and verification of a new multilevel inverter for reduced power switches. Arch. Electr. Eng. 2022, 71, 1051–1063. [Google Scholar]

- Babaei, E.; Laali, S.; Bayat, Z. A single-phase cascaded multilevel inverter based on a new basic unit with reduced number of power switches. IEEE Trans. Ind. Electron. 2015, 62, 922–929. [Google Scholar] [CrossRef]

- Kangarlu, M.F.; Babaei, E. A generalized cascaded multilevel inverter using series connection of submultilevel inverters. IEEE Trans. Power Electron. 2013, 28, 625–636. [Google Scholar] [CrossRef]

- Dahidah, M.S.; Konstantinou, G.; Agelidis, V.G. A review of multilevel selective harmonic elimination PWM: Formulations, solving algorithms, implementation and applications. IEEE Trans. Power Electron. 2015, 30, 4091–4106. [Google Scholar] [CrossRef]

- Mahato, B.; Majumdar, S.; Jana, K.C. A new and generalized MLI with overall lesser power electronic devices. J. Circ. Syst. Comput. 2020, 29, 2050058. [Google Scholar] [CrossRef]

- Jana, K.C.; Biswas, S.K. Generalised switching scheme for a space vector pulse-width modulation-based N-level inverter with reduced switching frequency and harmonics. IET Power Electron. 2015, 8, 2377–2385. [Google Scholar]

- McGrath, B.P.; Holmes, D.G. Multicarrier PWM strategies for multilevel inverters. IEEE Trans. Ind. Electron. 2002, 49, 858–867. [Google Scholar] [CrossRef]

- Babaei, E.; Hosseini, S.H. New cascaded multilevel inverter topology with minimum number of switches. Energy Convers. Manag. 2009, 50, 2761–2767. [Google Scholar] [CrossRef]

- Ajami, A.; Oskuee, M.R.; Khosroshahi, M.T.; Mokhberdoran, A. Cascade-multi-cell multilevel converter with reduced number of switches. IET Power Electron. 2014, 7, 2914–2924. [Google Scholar] [CrossRef]

- Gupta, K.K.; Jain, S. Topology for multilevel inverters to attain maximum number of levels from given DC sources. IET Power Electron. 2012, 5, 435–446. [Google Scholar] [CrossRef]

- Ajami, A.; Oskuee, M.R.J.; Mokhberdoran, A.; Van den Bossche, A. Developed cascaded multilevel inverter topology to minimise the number of circuit devices and voltage stresses of switches. IET Power Electron. 2013, 7, 459–466. [Google Scholar] [CrossRef]

- Gautam, S.P.; Kumar, L.; Gupta, S. Hybrid topology of symmetrical multilevel inverter using less number of devices. IET Power Electron. 2015, 8, 2125–2135. [Google Scholar] [CrossRef]

- Kangarlu, M.F.; Babaei, E. Cross-switched multilevel inverter: An innovative topology. IET Power Electron. 2014, 6, 642–651. [Google Scholar] [CrossRef]

- Alishah, R.S.; Nazarpour, D.; Hosseini, S.H.; Sabahi, M. Reduction of Power Electronic Elements in Multilevel Converters Using a New Cascade Structure. IEEE Trans. Ind. Electron. 2014, 62, 256–269. [Google Scholar] [CrossRef]

| Modes | Switching States 1 = ON; 0 = OFF | Circuit−I Voltages | Circuit−II Voltages | Stepped Output Voltage Generation | ||||||||

| Circuit−I | ||||||||||||

| Circuit−II | ||||||||||||

| Mode-1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | |||

| Mode-2 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | |||

| Mode-3 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | |||

| Mode-4 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | |||

| Mode-5 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | --- | --- | |

| 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | --- | --- | ||

| Mode-6 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 1 | |||

| Mode-7 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | |||

| Mode-8 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 1 | |||

| Mode-9 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | |||

| MLI Compared with the Proposed Topology | Total Switches (M) | Gate Driver Circuit (N) | Capacitors/Isolated DC Sources (O) | Main Diodes (P) | Switches | |

|---|---|---|---|---|---|---|

| Unidirectional Switches (Q) | Bi-Directional Switches (R) | |||||

| [24] | --- | |||||

| [25] | --- | |||||

| [26] | --- | |||||

| [27] | --- | |||||

| [28] | ||||||

| [29] | --- | |||||

| [30] | 4 | 4 | ||||

| Proposed Circuit−I Topology | 6 | |||||

| Proposed Circuit−II Topology | ||||||

| Cited Papers | Voltage Levels | Total Switches (M) | Capacitors/Isolated DC Sources (O) | PIV (Peak Inverse Voltage) | TSV (Total Standing Voltage) |

|---|---|---|---|---|---|

| [24] | 9 | 16 | 4 | 4 Vdc | 24 Vdc |

| [25] | 9 | 12 | 4 | Vdc | 12 Vdc |

| [26] | 9 | 16 | 4 | 3 Vdc | 24 Vdc |

| [27] | 9 | 12 | 4 | Vdc | 12 Vdc |

| [28] | 9 | 7 | 4 | 2 Vdc | 13 Vdc |

| [29] | 9 | 10 | 4 | 4 Vdc | 16 Vdc |

| [30] | 9 | 7 | 4 | 3 Vdc | 20 Vdc |

| Circuit−I and Circuit−II Topology | 9 | 9 | 4 | 4 Vdc | 24 Vdc |

| Parameters | Name and Value or Type | |

|---|---|---|

| Switching parameters IGBT | CT-60AM-18F: 900 V, 60 A Von, IGBT = 1.3 V, Von, Dio = 1.5 V, RDio = 0.01Ω, RIGBT = 0.11Ω, β = 3 | |

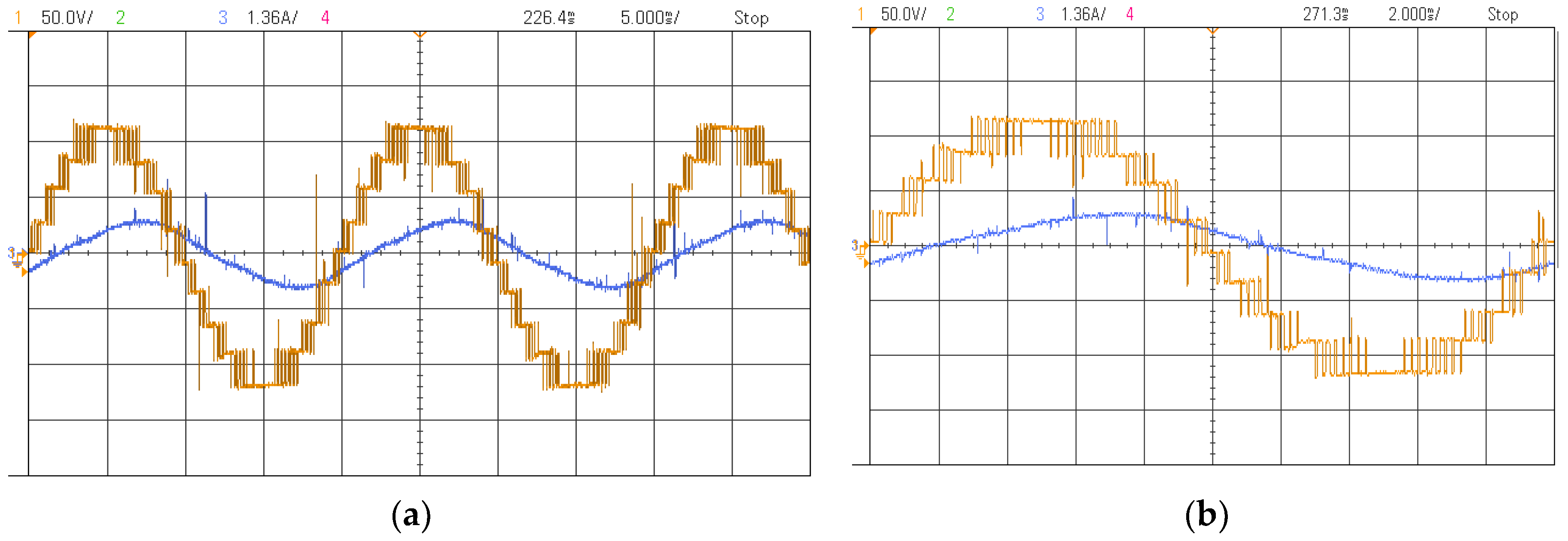

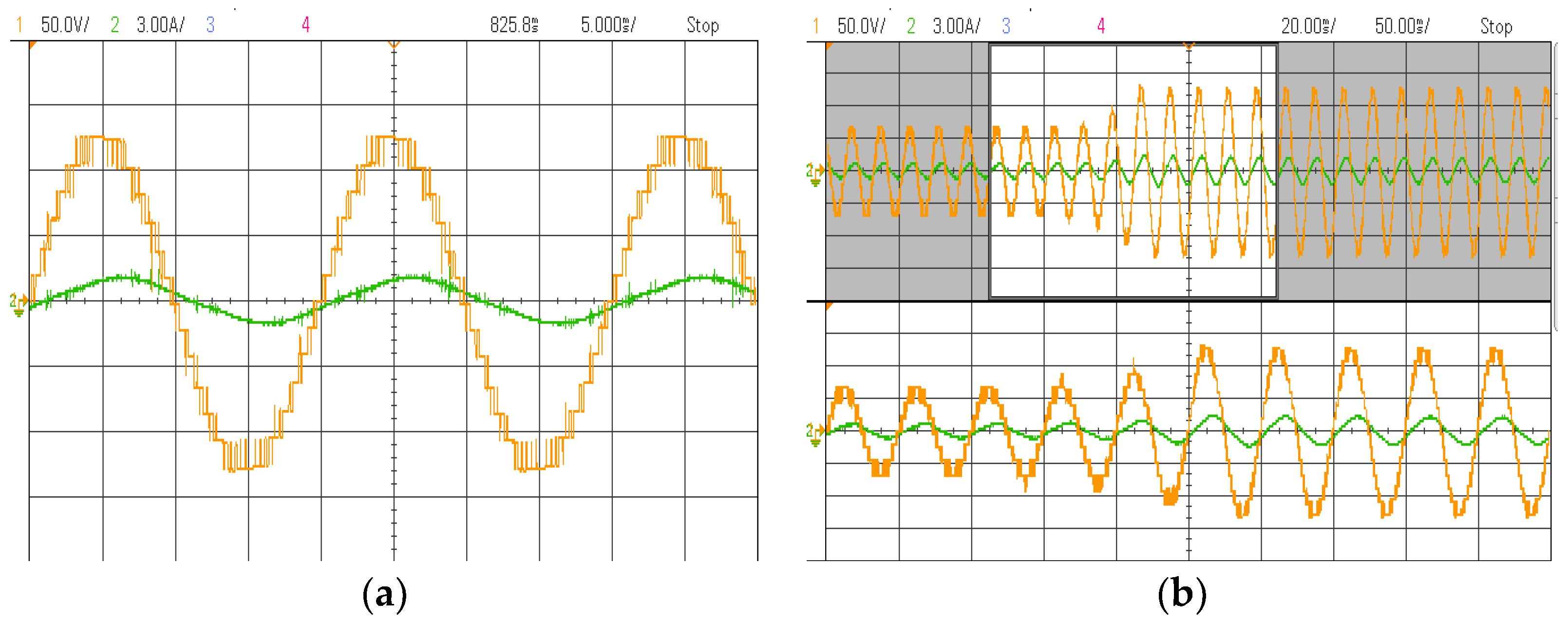

| Types of switching devices and their controlling elements | Diode driver Controller, switching frequency | MUR1560G: 600 V, 15 A TLP250: 10–35, ±1.5 A DS1103, 6 kHz |

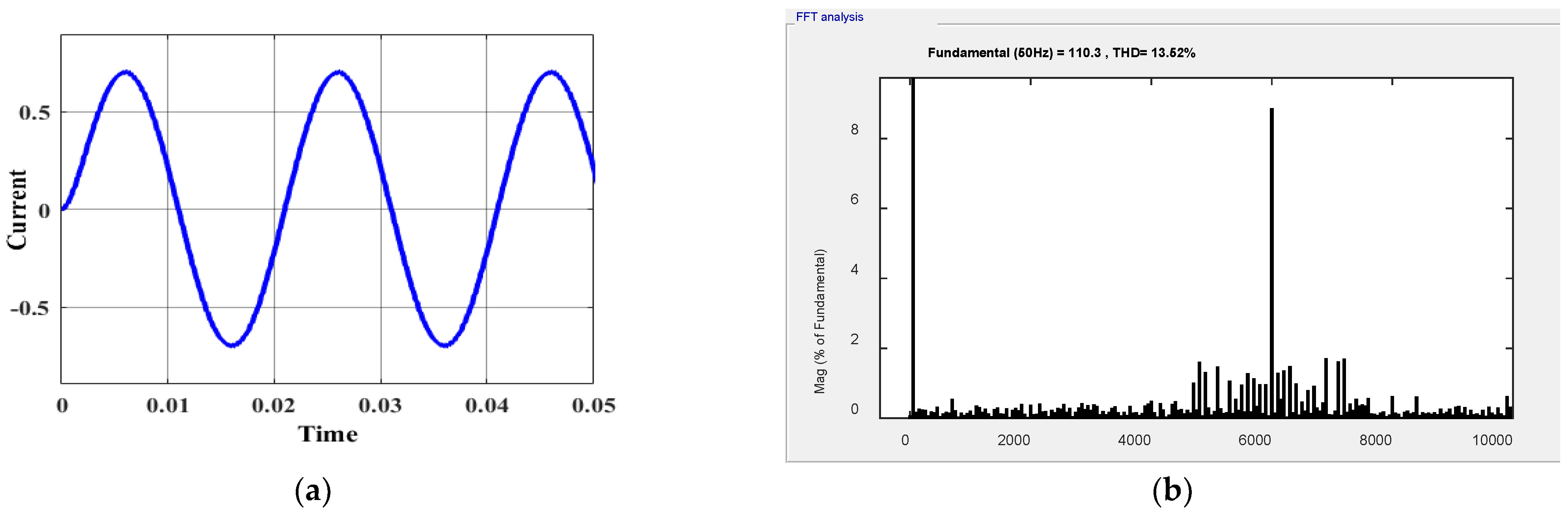

| Common parameters of simulation and experimental tests | 9-level inverter (same for circuit−I topology and circuit−II topologies) (V1 = V2 = V3 = V4 = Vdc = 27.5 V) R = 200 Ω, L = 150 mH, Vpk = 110.3 V, Ipk = 0.71 A. | |

| 11-level inverter, (Circuit−I Topology) (V1 = V2 = V3 = V4 = V5 = Vdc = 30 V) R = 200 Ω, L = 100 mH, Vpk = 145 V, Ipk = 1.2 A. | ||

| 13-level inverter, (circuit−II topology) (V1 = V2 = V3 = V4 = V5 = V6 = Vdc = 21 V) R = 200 Ω, L = 100 mH, Vpk = 125.7 V, Ipk = 1.2 A. | ||

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Mahto, K.K.; Mahato, B.; Chandan, B.; Das, D.; Das, P.; Fotis, G.; Vita, V.; Mann, M. A New Symmetrical Source-Based DC/AC Converter with Experimental Verification. Electronics 2024, 13, 1975. https://doi.org/10.3390/electronics13101975

Mahto KK, Mahato B, Chandan B, Das D, Das P, Fotis G, Vita V, Mann M. A New Symmetrical Source-Based DC/AC Converter with Experimental Verification. Electronics. 2024; 13(10):1975. https://doi.org/10.3390/electronics13101975

Chicago/Turabian StyleMahto, Kailash Kumar, Bidyut Mahato, Bikramaditya Chandan, Durbanjali Das, Priyanath Das, Georgios Fotis, Vasiliki Vita, and Michael Mann. 2024. "A New Symmetrical Source-Based DC/AC Converter with Experimental Verification" Electronics 13, no. 10: 1975. https://doi.org/10.3390/electronics13101975

APA StyleMahto, K. K., Mahato, B., Chandan, B., Das, D., Das, P., Fotis, G., Vita, V., & Mann, M. (2024). A New Symmetrical Source-Based DC/AC Converter with Experimental Verification. Electronics, 13(10), 1975. https://doi.org/10.3390/electronics13101975