High-Performance Wave Union Time-to-Digital Converter Implementation Based on Routing Path Delays of FPGA

Abstract

:1. Introduction

2. Methodology

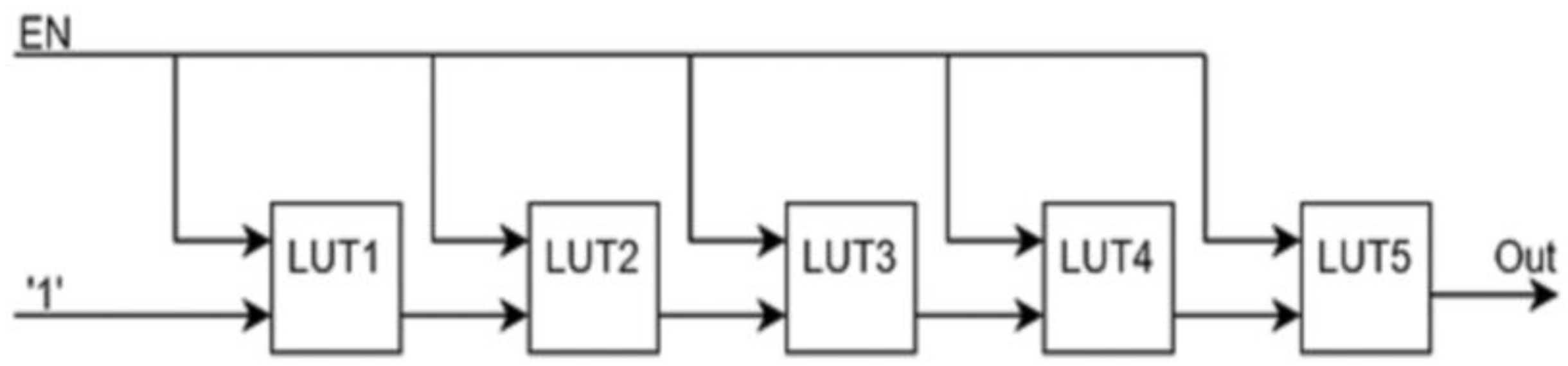

2.1. Architecture of Wave Union A TDCs

2.2. Architecture of Wave Union B TDC

3. Results and Discussion

3.1. Stastical Results of WU-A TDC

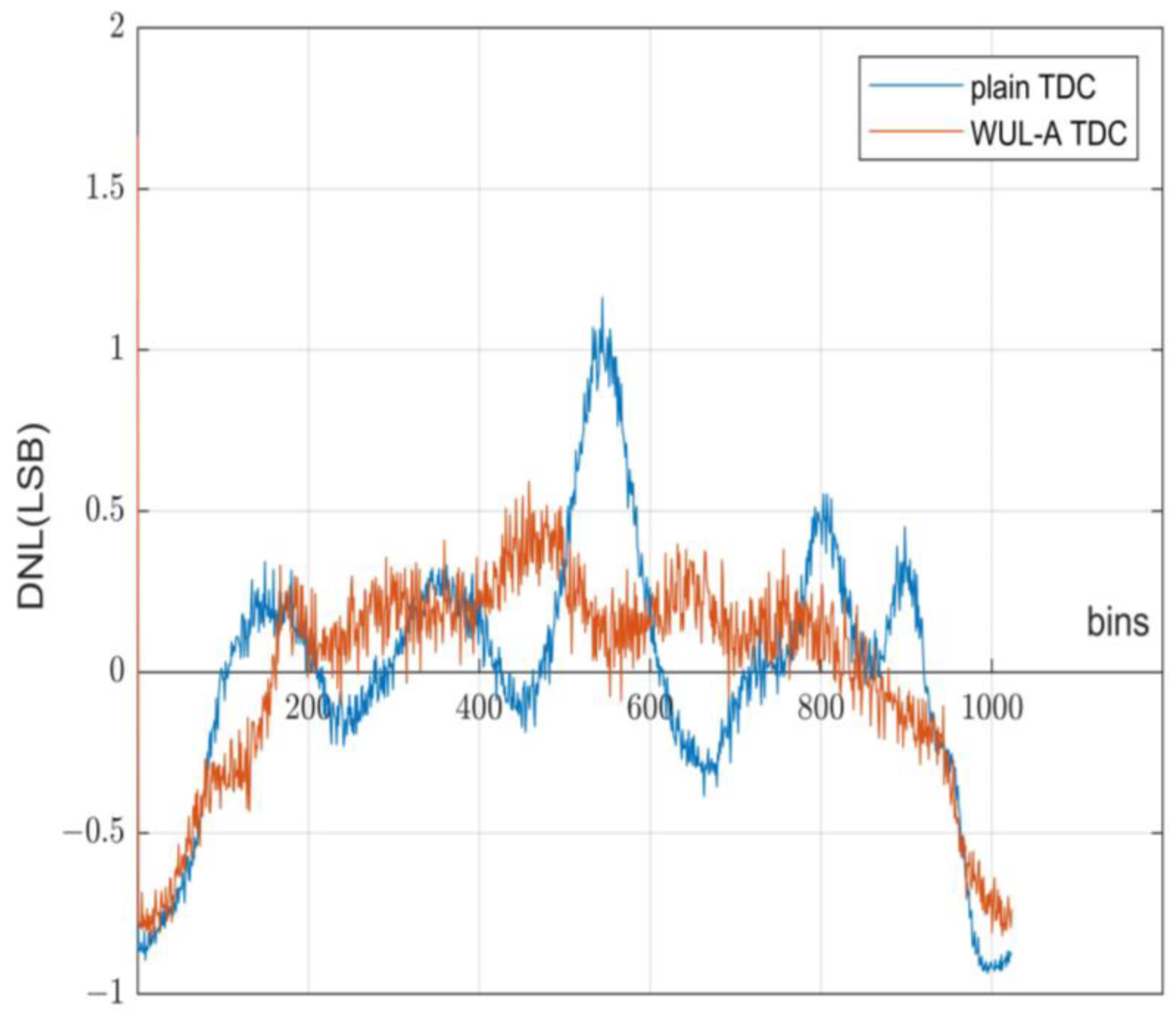

3.2. Differential and Integral Non-Linearity of WU-A TDC

3.3. Statistical Results of WU-B TDC

3.4. Differential and Integral Non-Linearity of WU-B TDC

3.5. Comparison with Prior Works

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Korkan, A.O.; Yuksel, H. A Novel Time-to-Amplitude Converter and a Low-Cost Wide Dynamic Range FPGA TDC for LiDAR Application. IEEE Trans. Instrum. Meas. 2022, 71, 2005015. [Google Scholar] [CrossRef]

- Xie, W.; Chen, H.; Zang, Z.; Li, D.D.U. Multi-channel high-linearity time-to-digital converters in 20 nm and 28 nm FPGAs for LiDAR applications. In Proceedings of the 2020 6th International Conference on Event-Based Control, Communication, and Signal Processing (EBCCSP), Krakow, Poland, 23–25 September 2020; pp. 4–7. [Google Scholar] [CrossRef]

- Jee, D.W.; Seo, Y.H.; Park, H.J.; Sim, J.Y. A 2 GHz fractional-N digital PLL with 1b noise shaping ΔΣ TDC. IEEE J. Solid-State Circuits 2012, 47, 875–883. [Google Scholar] [CrossRef]

- Gao, W.; Gao, D.; Guo, C.H.; Hu, Y. Time-to-Digital Converters (TDCs) for PET Imaging. In Biomedical Engineering, Trends in Electronics, Communications and Software; Laskovski, A.N., Ed.; IntechOpen: London, UK, 2009. [Google Scholar]

- Lecoq, P. Pushing the Limits in Time-of-Flight PET Imaging. IEEE Trans. Radiat. Plasma Med. Sci. 2017, 1, 473–485. [Google Scholar] [CrossRef]

- Wang, Y.; Xie, W.; Chen, H.; Day-Uei Li, D. High-resolution time-to-digital converters (TDCs) with a bidirectional encoder. Meas. J. Int. Meas. Confed. 2023, 206, 112258. [Google Scholar] [CrossRef]

- Dikopoulos, E.; Birbas, M.; Birbas, A. An Adaptive Downsampling FPGA-Based TDC Implementation for Time Measurement Improvement. Chips 2022, 1, 175–190. [Google Scholar] [CrossRef]

- Tontini, A.; Gasparini, L.; Pancheri, L.; Passerone, R. Design and Characterization of a Low-Cost FPGA-Based TDC. IEEE Trans. Nucl. Sci. 2018, 65, 680–690. [Google Scholar] [CrossRef]

- Fishburn, M.W.; Menninga, L.H.; Favi, C.; Charbon, E. A 19.6 ps, FPGA-based TDC with multiple channels for open source applications. IEEE Trans. Nucl. Sci. 2013, 60, 2203–2208. [Google Scholar] [CrossRef]

- Lai, J.; Luo, Y.; Shao, Q.; Bao, L.; Liu, X. A high-resolution TDC implemented in a 90nm process FPGA. In Proceedings of the International Conference on ASIC, Shenzhen, China, 28–31 October 2013; pp. 2–4. [Google Scholar] [CrossRef]

- Kwiatkowski, P. Employing FPGA DSP blocks for time-to-digital conversion. Metrol. Meas. Syst. 2019, 26, 631–643. [Google Scholar] [CrossRef]

- Wang, H.; Zhang, M.; Yao, Q. A new realization of time-to-digital converters based on FPGA internal routing resources. IEEE Trans. Ultrason. Ferroelectr. Freq. Control 2013, 60, 1787–1795. [Google Scholar] [CrossRef]

- Zhang, M.; Wang, H.; Liu, Y. A 7.4 ps FPGA-based TDC with a 1024-unit measurement matrix. Sensors 2017, 17, 865. [Google Scholar] [CrossRef]

- Siecha, R.T.; Alemu, G.; Prinzie, J.; Leroux, P. 5.7 ps Resolution Time-to-Digital Converter Implementation Using Routing Path Delays. Electronics 2023, 12, 3478. [Google Scholar] [CrossRef]

- Dudek, P.; Szczepański, S.; Hatfield, J.V. A high-resolution CMOS time-to-digital converter utilizing a Vernier delay line. IEEE J. Solid-State Circuits 2000, 35, 240–247. [Google Scholar] [CrossRef]

- Cui, K.; Li, X. A high-linearity vernier time-to-digital converter on FPGAs with improved resolution using bidirectional-operating vernier delay lines. IEEE Trans. Instrum. Meas. 2020, 69, 5941–5949. [Google Scholar] [CrossRef]

- Cui, K.; Li, X.; Liu, Z.; Zhu, R. Toward Implementing Multichannels, Ring-Oscillator-Based, Vernier Time-to-Digital Converter in FPGAs: Key Design Points and Construction Method. IEEE Trans. Radiat. Plasma Med. Sci. 2017, 1, 391–399. [Google Scholar] [CrossRef]

- Shen, Q.; Liu, S.; Qi, B.; An, Q.; Liao, S.; Shang, P.; Peng, C.; Liu, W. A 1.7 ps equivalent bin size and 4.2 ps RMS FPGA TDC based on multichain measurements averaging method. IEEE Trans. Nucl. Sci. 2015, 62, 947–954. [Google Scholar] [CrossRef]

- Liu, C.; Wang, Y. A 128-channel, 710 M samples/second, and less than 10 ps RMS resolution time-to-digital converter implemented in a kintex-7 FPGA. IEEE Trans. Nucl. Sci. 2015, 62, 773–783. [Google Scholar] [CrossRef]

- Wu, J.; Shi, Z. The 10-ps wave union TDC: Improving FPGA TDC resolution beyond its cell delay. IEEE Nucl. Sci. Symp. Conf. Rec. 2008, 1, 3440–3446. [Google Scholar] [CrossRef]

- Wang, J.; Liu, S.; Zhao, L.; Hu, X.; An, Q. The 10-ps multitime measurements averaging TDC implemented in an FPGA. IEEE Trans. Nucl. Sci. 2011, 58, 2011–2018. [Google Scholar] [CrossRef]

- Bayer, E.; Zipf, P.; Traxler, M. A multichannel high-resolution (<5 ps RMS between two channels) time-to-digital converter (TDC) implemented in a field programmable gate array (FPGA). In Proceedings of the IEEE Nuclear Science Symposium Conference Record, Valencia, Spain, 23–29 October 2011; pp. 876–879. [Google Scholar] [CrossRef]

- Kwiatkowski, P.; Szplet, R. Efficient Implementation of Multiple Time Coding Lines-Based TDC in an FPGA Device. IEEE Trans. Instrum. Meas. 2020, 69, 7353–7364. [Google Scholar] [CrossRef]

- Kwiatkowski, P.; Sondej, D.; Szplet, R. A brief review of wave union TDCs. In Proceedings of the EBCCSP 2021—7th International Conference on Event-Based Control, Communication, and Signal Processing, Krakow, Poland, 22–25 June 2021; pp. 1–6. [Google Scholar] [CrossRef]

- Avnet Electronics Marketing. ZedBoard ZynqTM Evaluation and Development Hardware User’s Guide. 2012. Available online: https://digilent.com/reference/_media/zedboard:zedboard_ug.pdf (accessed on 12 April 2024).

- Travaglini, R.; Antone, I.D.; Meneghini, S.; Rignanese, L.; Zu, M. Design and implementation of projects with Xilinx Zynq FPGA: A practical case. Mem. Della Soc. Astron. Ital. 2017, 88, 186–194. [Google Scholar]

- Wang, Y.; Liu, C. A 3.9 ps Time-Interval RMS Precision Time-to-Digital Converter Using a Dual-Sampling Method in an UltraScale FPGA. IEEE Trans. Nucl. Sci. 2016, 63, 2617–2621. [Google Scholar] [CrossRef]

- Wang, Y.; Zhou, X.; Song, Z.; Kuang, J.; Cao, Q. A 3.0-ps rms Precision 277-MSamples/s Throughput Time-to-Digital Converter Using Multi-Edge Encoding Scheme in a Kintex-7 FPGA. IEEE Trans. Nucl. Sci. 2019, 66, 2275–2281. [Google Scholar] [CrossRef]

- Alshahry, S.M.; Alshehry, A.H.; Alhazmi, A.K.; Chodavarapu, V.P. A Size, Weight, Power, and Cost-Efficient 32-Channel Time to Digital Converter Using a Novel Wave Union Method. Sensors 2023, 23, 6621. [Google Scholar] [CrossRef] [PubMed]

- Szplet, R.; Sondej, D.; Grzȩda, G. High-Precision Time Digitizer Based on Multiedge Coding in Independent Coding Lines. IEEE Trans. Instrum. Meas. 2016, 65, 1884–1894. [Google Scholar] [CrossRef]

- Lusardi, N.; Garzetti, F.; Geraci, A. Digital instrument with configurable hardware and firmware for multi-channel time measures. Rev. Sci. Instrum. 2019, 90, 055113. [Google Scholar] [CrossRef] [PubMed]

- Xilinx Inc. Zynq-7000 SoC Data Sheet: Overview. Xilinx 2018, DS190, 1–21. [Google Scholar]

- Lusardi, N.; Garzetti, F.; Corna, N.; De Marco, R.; Geraci, A. Very High-Performance 24-Channels Time-to-Digital Converter in Xilinx 20-nm Kintex UltraScale FPGA. In Proceedings of the 2019 IEEE Nuclear Science Symposium and Medical Imaging Conference (NSS/MIC), Manchester, UK, 26 October–2 November 2019; pp. 5–8. [Google Scholar] [CrossRef]

- Xie, W.; Chen, H.; Li, D.D.U. Efficient Time-to-Digital Converters in 20 nm FPGAs with Wave Union Methods. IEEE Trans. Ind. Electron. 2022, 69, 1021–1031. [Google Scholar] [CrossRef]

- Kwiatkowski, P.; Sondej, D.; Szplet, R. Bubble-proof algorithm for wave union tdcs. Electronics 2022, 11, 30. [Google Scholar] [CrossRef]

| WU-A (1024 Counter Matrix) | WU-B (1024 Counter Matrix) | ||||

|---|---|---|---|---|---|

| Available | Used | Utilization (%) | Used | Utilization (%) | |

| Slice Registers | 106,400 | 51,214 | 48.13 | 51,193 | 48.11 |

| Slice LUTs | 53,200 | 30,359 | 57.07 | 30,392 | 57.13 |

| LUTs as logic | 53,200 | 19,059 | 35.83 | 19,092 | 35.89 |

| LUTs as memory | 17,400 | 11,300 | 64.94 | 11,300 | 64.94 |

| Slices | 13,300 | 12,682 | 95.35 | 12,603 | 94.76 |

| Block RAM | 140 | 64.5 | 46.07 | 64.5 | 46.07 |

| BUFGCTRL | 32 | 7 | 21.88 | 7 | 21.88 |

| MMCME2-ADV | 4 | 3 | 75 | 3 | 75 |

| Work | Method | Technology | Bins | LSB (ps) | DNL (LSB) | INL (LSB) |

|---|---|---|---|---|---|---|

| [20] (2008) | WU-A WU-B | 90 nm | 64 | 30 - | - - | - - |

| [21] (2011) | WU-B | 90 nm | 830 | 12 | 1.1 | 8 |

| [22] (2011) | WU-A | 90 nm | 256 | 3.6 | - | - |

| [30] (2016) | Super WU-A | 45 nm | 2176 | 0.9 | - | −26.2 |

| [33] (2019) | Super WU-A | 20 nm | 8192 | 1.17 | - | - |

| [28] (2019) | WU-A | 28 nm | 1018 | 1.77 | 4.5 | −37.7 |

| [23] (2020) | Multi-sampling WU-A | 28 nm | 1500 | 1.11 | 4 | 50 |

| [34] (2022) | WU-A | 20 nm | 790 | 1.23–2.53 | 1.75 | 5.97 |

| [35] (2021) | Multi-sampling WU-A and WU-B | 28 nm | 200 | 0.39 | - | - |

| This work | WU-A | 28 nm | 1024 | 5.7 | 0.33 (RMS) | 1.12 (RMS) |

| WU-B | 16,384 | 0.356 | 0.60 (RMS) | 1.04 (RMS) |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Siecha, R.T.; Alemu, G.; Prinzie, J.; Leroux, P. High-Performance Wave Union Time-to-Digital Converter Implementation Based on Routing Path Delays of FPGA. Electronics 2024, 13, 2359. https://doi.org/10.3390/electronics13122359

Siecha RT, Alemu G, Prinzie J, Leroux P. High-Performance Wave Union Time-to-Digital Converter Implementation Based on Routing Path Delays of FPGA. Electronics. 2024; 13(12):2359. https://doi.org/10.3390/electronics13122359

Chicago/Turabian StyleSiecha, Roza Teklehaimanot, Getachew Alemu, Jeffrey Prinzie, and Paul Leroux. 2024. "High-Performance Wave Union Time-to-Digital Converter Implementation Based on Routing Path Delays of FPGA" Electronics 13, no. 12: 2359. https://doi.org/10.3390/electronics13122359