Operational Amplifiers Defect Detection and Localization Using Digital Injectors and Observer Circuits

Abstract

1. Introduction

- This manuscript provides a more extensive explanation of Intentional Offset Injection (IOI) op amp defect detection and shows, by way of analytical formulas, how to realize robust testing circuitry.

- We demonstrate how to apply intentional offset injections to all possible offset injection sites for a given op amp architecture and validate with simulation results.

- In this manuscript, we discuss a novel defect localization technique for op amps using a binary sequence obtained from the state of the digital injectors and detectors employed in our method after testing.

2. Literature Review

2.1. Defect Terminology Review

- A fault is an unexpected change in a specified performance of a primitive circuit or circuit module that is not within the circuit’s specification limits [21].

- A defect is an unintended physical change in the manufactured circuit that causes a difference between the fabricated circuit and its layout. Defects are of two types: hard and soft defects.

- A soft defect, also called a parametric defect, does not affect the circuit topology but translates to variations in the component parameters that affect its output. They result from imperfections in IC fabrication, causing variations in oxide thickness, substrate doping, threshold voltage, mobility, and transistor width [14].

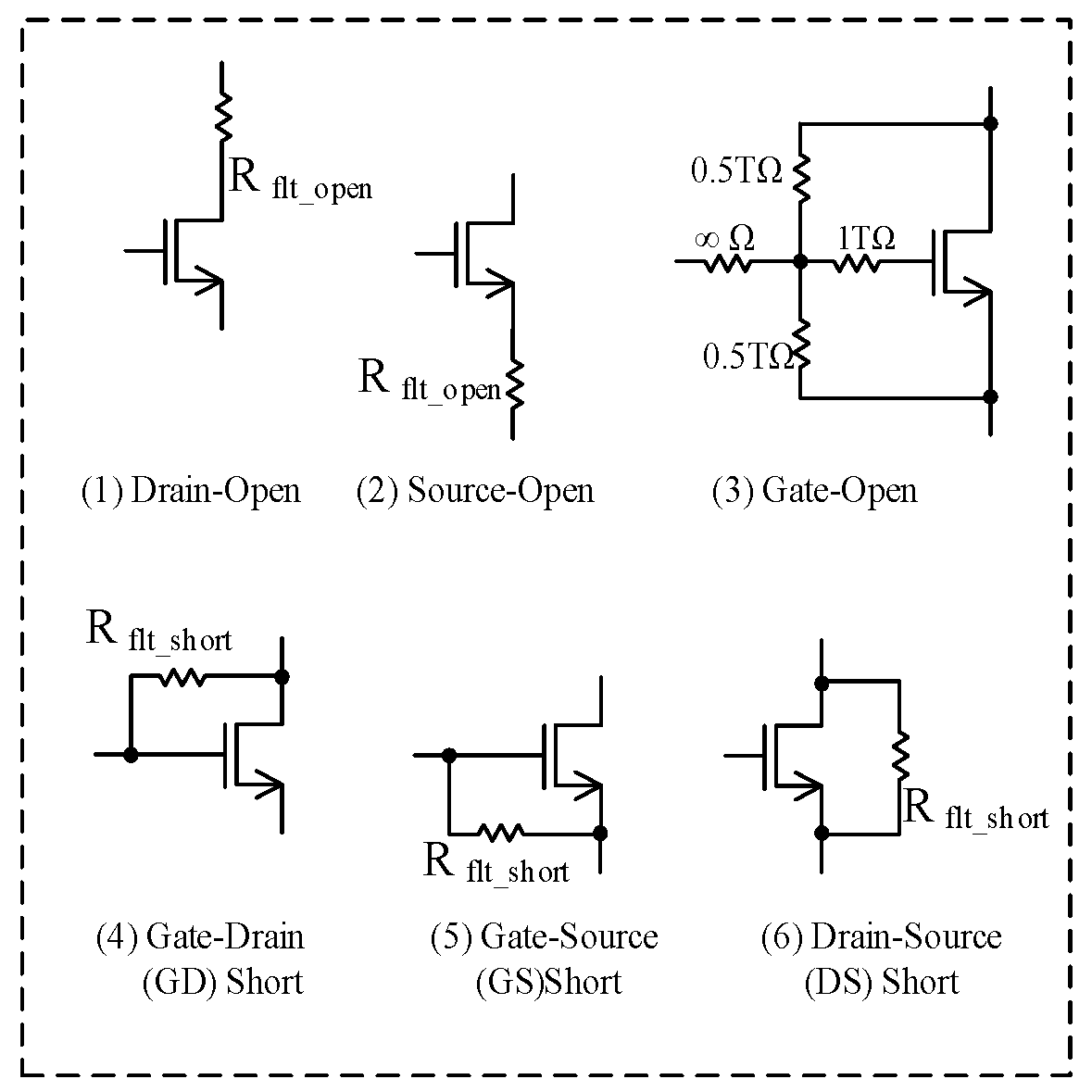

- Hard (catastrophic) defects, on the other hand, are those that change circuit topology. They are generally introduced by local defect mechanisms such as impure particles on the wafer surface, defects in oxide, dust particle interaction during masking, which blocks the exposure, etc. Hard defects usually result from short and open defects in circuit components. The defect detection techniques presented in this work primarily focus on catastrophic defects, as they make up about 80% of observed analog faults [20].

- The defect universe refers to all reasonably likely defects that can be algorithmically defined, excluding those in unused circuitry.

- The defect model is an equivalent circuit for a defect in the context of a circuit simulator. In this work, the defect models for testing defects are in line with P2427 standards [21].

- The defect coverage is the weighted percentage of defects detected by tests applied to the circuit’s ports as a fraction of all defects in the circuit’s defect universe. Although it is not the only metric, a high defect coverage is one of the hallmarks of a good defect detection and diagnosis strategy.

- Defect localization is the mapping out of the physical region of the circuit where the defect occurred.

- Defect collapsing comprises grouping defects that have the same effect. Defect collapsing serves as a good basis to reduce the amount of defect testing simulation by simulating a few samples in each cluster.

2.2. Defect Model

2.3. Op Amp Defect Testing Methods in Literature

2.3.1. Oscillation Test Methodology (OTM)

2.3.2. IDDQ and IDDT Testing

3. Proposed Testing and Localization Technique

3.1. Intentional Offset Injection (IOI)

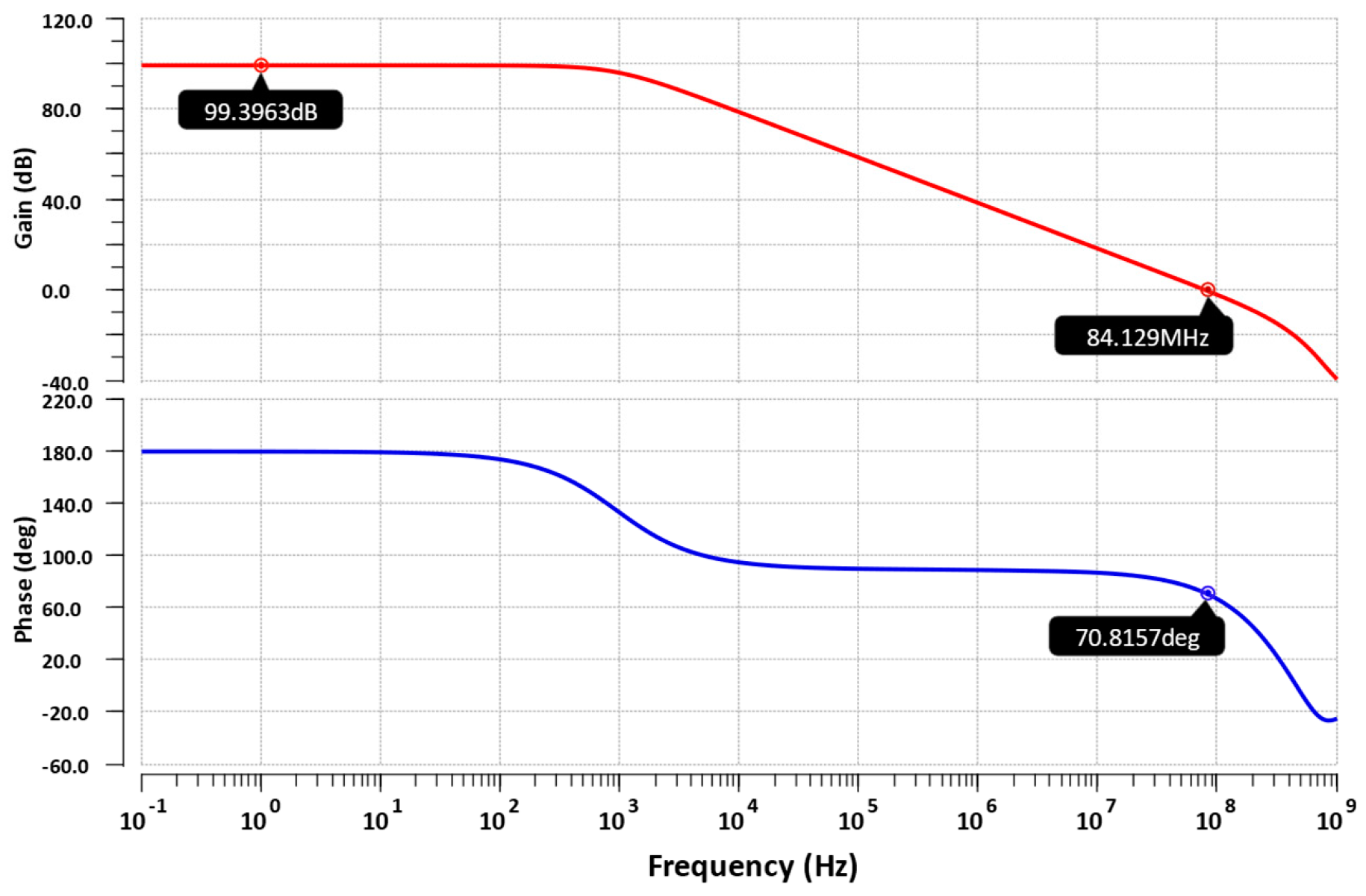

3.2. Compensation Network

3.3. Widlar Mismatch Injection

3.4. Detectors

3.5. Proposed Defect Localization Method

3.5.1. Localization Approach for Short Defects

3.5.2. Localization for Open Defect

| Algorithm 1: open defect clustering and localization |

| Open defect list: Control injector states: Branches to monitor: for each defect in defect list: Carry out defect simulation and obtain branch current for all 4 states. for each element : for all 4 states: generate 4- bit binary. If node current, is within limit and then; Bit = 1 Else: Bit = 0 Compute Decimal equivalence of 4k-bit binary streams due to defect for all do If they have the same, then; place in one group. |

4. Defect Simulation Results

4.1. Simulation Results for Telescopic Op Amp

4.1.1. Defect Detection in Telescopic Op Amp (Main Structure)

4.1.2. Defect Detection in Compensation Network

4.1.3. Defect Detection in Widlar Reference and Current Bias Circuit

4.1.4. Defect Localization and Clustering in Telescopic Op Amp

4.2. Defect Coverage and Localization Simulation Results for Folded Cascode Op Amp

4.2.1. Defect Detection in FCA

4.2.2. Defect Localization in FCA

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Ince, M.; Ozev, S. Digital Defect Based Built-in Self-Test for Low Dropout Voltage Regulators. In Proceedings of the 2020 IEEE European Test Symposium (ETS), Tallinn, Estonia, 25–29 May 2020; pp. 1–2. [Google Scholar] [CrossRef]

- ISO26262; ISO 26262: Road vehicles—Functional Safety Organization for Standardization. ISO: Geneva, Switzerland, 2011.

- Saikiran, M.; Ganji, M.; Chen, D. Robust DfT Techniques for Built-in Fault Detection in Operational Amplifiers with High Coverage. In Proceedings of the 2020 IEEE International Test Conference (ITC), Washington, DC, USA, 1–6 November 2020; pp. 1–10. [Google Scholar] [CrossRef]

- Dobbelaere, W.; Colle, F.; Coyette, A.; Vanhooren, R.; Xama, N.; Gomez, J.; Gielen, G. Applying Vstress and defect activation coverage to produce zero-defect mixed-signal automotive ICs. In Proceedings of the 2019 IEEE International Test Conference (ITC), Washington, DC, USA, 9–15 November 2019; pp. 1–4. [Google Scholar] [CrossRef]

- Binu, D.; Kariyappa, B.S. A survey on fault diagnosis of analog circuits: Taxonomy and state of the art. AEU Int. J. Electron. Commun. 2017, 73, 68–83. [Google Scholar] [CrossRef]

- Nardi, A.; Armato, A. Functional safety methodologies for automotive applications. In Proceedings of the 2017 IEEE/ACM International Conference on Computer-Aided Design (ICCAD), Irvine, CA, USA, 13–16 November 2017; pp. 970–975. [Google Scholar] [CrossRef]

- Sekyere, M.; Saikiran, M.; Chen, D. All Digital Low-Cost Built-in Defect Testing Strategy for Operational Amplifiers with High Coverage. In Proceedings of the 2022 IEEE 28th International Symposium on On-Line Testing and Robust System Design (IOLTS), Torino, Italy, 12–14 September 2022; pp. 1–5. [Google Scholar] [CrossRef]

- Liu, Z.; Chaganti, S.K.; Chen, D. Improving Time-Efficiency of Fault-Coverage Simulation for MOS Analog Circuit. IEEE Trans. Circuits Syst. I 2018, 65, 1664–1674. [Google Scholar] [CrossRef]

- Saikiran, M.; Sekyere, M.; Ganji, M.; Yang, R.; Chen, D. Low-cost defect simulation framework for analog and mixed signal (AMS) circuits with enhanced time-efficiency. Analog. Integr. Circ. Signal Process. 2023, 117, 73–94. [Google Scholar] [CrossRef]

- Karaca, O.; Kirscher, J.; Laroche, A.; Tributsch, A.; Maurer, L.; Pelz, G. Fault grouping for fault injection based simulation of AMS circuits in the context of functional safety. In Proceedings of the 2016 13th International Conference on Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design (SMACD), Lisbon, Portugal, 27–30 June 2016; pp. 1–4. [Google Scholar] [CrossRef]

- Sanyal, S.; Garapati, S.P.P.K.; Patra, A.; Dasgupta, P.; Bhattacharya, M. Fault Classification and Coverage of Analog Circuits using DC Operating Point and Frequency Response Analysis. In Proceedings of the 2019 on Great Lakes Symposium on VLSI, Tysons Corner, VA, USA, 9–11 May 2019; ACM: New York, NY, USA, 2019; pp. 123–128. [Google Scholar] [CrossRef]

- Shintani, M.; Mian, R.-U.-H.; Inoue, M.; Nakamura, T.; Kajiyama, M.; Eiki, M. Wafer-level Variation Modeling for Multi-site RF IC Testing via Hierarchical Gaussian Process. In Proceedings of the 2021 IEEE International Test Conference (ITC), Anaheim, CA, USA, 10–15 October 2021; pp. 103–112. [Google Scholar] [CrossRef]

- Kim, S.; Jin, J.; Kim, J. A Cost-Effective and Compact All-Digital Dual-Loop Jitter Attenuator for Built-Off-Test Applications. Electronics 2022, 11, 3630. [Google Scholar] [CrossRef]

- Arabi, K.; Kaminska, B. Oscillation-test strategy for analog and mixed-signal integrated circuits. In Proceedings of the 14th VLSI Test Symposium, Princeton, NJ, USA, 28 April–1 May 1996; IEEE Computer Society Press: Washington, DC, USA, 1996; pp. 476–482. [Google Scholar] [CrossRef]

- Arabi, K.; Kaminska, B. Testing analog and mixed-signal integrated circuits using oscillation-test method. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 1997, 16, 745–753. [Google Scholar] [CrossRef]

- Kaur, M.; Kaur, J. Testing of low voltage two stage operational amplifier using oscillation test methodology. In Proceedings of the 2015 International Conference on Signal Processing and Communication (ICSC), Noida, India, 16–18 March 2015; pp. 401–405. [Google Scholar] [CrossRef]

- Guibane, B.; Hamdi, B.; Mtibaa, A. Investigation on the Effectiveness of Current Supply Testing Methods in CMOS Operational Amplifiers. In Proceedings of the 2018 15th International Multi-Conference on Systems, Signals & Devices (SSD), Yasmine Hammamet, Tunisia, 19–22 March 2018; pp. 1041–1044. [Google Scholar] [CrossRef]

- Kilic, Y.; Zwolinski, M. Testing analog circuits by supply voltage variation and supply current monitoring. In Proceedings of the IEEE 1999 Custom Integrated Circuits Conference (Cat. No.99CH36327), San Diego, CA, USA, 19 May 1999; pp. 155–158. [Google Scholar] [CrossRef]

- Yellampalli, S.; Srivastava, A.; Pulendra, V.K. A combined oscillation, power supply current and I/sub DDQ/testing methodology for fault detection in floating gate input CMOS operational amplifier. In Proceedings of the 48th Midwest Symposium on Circuits and Systems, Covington, KY, USA, 7–10 August 2005; Volume 1, pp. 503–506. [Google Scholar] [CrossRef]

- Madian, A.H.; Amer, H.H.; Eldesouky, A.O. Catastrophic short and open fault detection in MOS current mode circuits: A case study. In Proceedings of the 2010 12th Biennial Baltic Electronics Conference, Tallinn, Estonia, 4–6 October 2010; pp. 145–148. [Google Scholar] [CrossRef]

- P2427/D0.35; IEEE Draft Standard for Analog Defect Modeling and Coverage. IEEE: Piscataway, NJ, USA, 2022.

- A’ain, A.K.B.; Bratt, A.H.; Dorey, A.P. Testing analogue circuits by AC power supply voltage. In Proceedings of the 9th International Conference on VLSI Design, Bangalore, India, 3–6 January 1995; IEEE Computer Society Press: Washington, DC, USA, 1996; pp. 238–241. [Google Scholar] [CrossRef]

- Witte, J.F.; Makinwa, K.A.A.; Huijsing, J.H. Dynamic Offset Compensated CMOS Amplifiers; Springer: Dordrecht, The Netherlands, 2009. [Google Scholar] [CrossRef]

- Pelgrom, M.J.M.; Duinmaijer, A.C.J.; Welbers, A.P.G. Matching properties of MOS transistors. IEEE J. Solid-State Circuits 1989, 24, 1433–1439. [Google Scholar] [CrossRef]

- Wannaboon, C.; Jiteurtragool, N.; San-Um, W.; Tachibana, M. Phase difference analysis technique for parametric faults BIST in CMOS analog circuits. IEICE Electron. Express 2018, 15, 20180175. [Google Scholar] [CrossRef]

| 0 | |||

| Injection Site | Coverage | Undetected | Detected with Comparator |

|---|---|---|---|

| Defect-Free | Open Defect in Compensation Network | |||||

|---|---|---|---|---|---|---|

| State | Time | expected | ||||

| Case 1 | Case 2 | |||||

| Intrinsic Offset | Bit0 | 0 | 0 | X | L | H |

| Positive Offset | Bit1 | 0 | 1 | H | H | H |

| Intrinsic Offset | Bit2 | 0 | 0 | H | L | H |

| Negative Offset | Bit3 | 1 | 0 | L | L | L |

| Intrinsic Offset | Bit4 | 1 | 1 | L | L | H |

| Detector | Positive IOI | Negative IOI | Mismatch + Positive IOI | Mismatch + Negative IOI |

|---|---|---|---|---|

| 1 | 1 | 1 | 1 | |

| 1 | 1 | 0 | 0 | |

| 0 | 0 | 1 | 1 | |

| 1 | 0 | 1 | 0 |

| Cluster | Defects in Cluster | Cluster | Defects in Cluster |

|---|---|---|---|

| 1 | 10 | ||

| 2 | 11 | ||

| 3 | 12 | ||

| 4 | 13 | ||

| 5 | 14 | ||

| 6 | 15 | ||

| 7 | 16 | ||

| 8 | 17 | ||

| 9 | 18 |

| Cluster | Defects in Cluster | Cluster | Defects in Cluster |

|---|---|---|---|

| 1 | 7 | ||

| 2 | 8 | ||

| 3 | 9 | ||

| 4 | 10 | ||

| 5 | 11 | ||

| 6 | 12 |

| Injection Site | Coverage | Undetected | Detected with Comparator |

|---|---|---|---|

| Cluster | Defects in Cluster | Cluster | Defects in Cluster |

|---|---|---|---|

| 1 | 11 | ||

| 2 | 12 | ||

| 3 | 13 | ||

| 4 | 14 | ||

| 5 | 15 | ||

| 6 | 16 | ||

| 7 | 17 | ||

| 8 | 18 | ||

| 9 | 19 | ||

| 10 | 20 | ||

| Undetected |

| Cluster | Defects in Cluster | Cluster | Defects in Cluster |

|---|---|---|---|

| 1 | 9 | ||

| 2 | 10 | ||

| 3 | 11 | ||

| 4 | 12 | ||

| 5 | 13 | ||

| 6 | 14 | ||

| 7 | 15 | ||

| 8 | 16 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Sekyere, M.; Saikiran, M.; Chen, D. Operational Amplifiers Defect Detection and Localization Using Digital Injectors and Observer Circuits. Electronics 2024, 13, 2871. https://doi.org/10.3390/electronics13142871

Sekyere M, Saikiran M, Chen D. Operational Amplifiers Defect Detection and Localization Using Digital Injectors and Observer Circuits. Electronics. 2024; 13(14):2871. https://doi.org/10.3390/electronics13142871

Chicago/Turabian StyleSekyere, Michael, Marampally Saikiran, and Degang Chen. 2024. "Operational Amplifiers Defect Detection and Localization Using Digital Injectors and Observer Circuits" Electronics 13, no. 14: 2871. https://doi.org/10.3390/electronics13142871

APA StyleSekyere, M., Saikiran, M., & Chen, D. (2024). Operational Amplifiers Defect Detection and Localization Using Digital Injectors and Observer Circuits. Electronics, 13(14), 2871. https://doi.org/10.3390/electronics13142871