State Space Average Modeling, Small Signal Analysis, and Control Implementation of an Efficient Single-Switch High-Gain Multicell Boost DC-DC Converter with Low Voltage Stress

Abstract

1. Introduction

- Low voltage stress on the main switch and diodes.

- Simplicity of control due to single-switch topology.

- The structure of the converter can be extended to n cells for high voltage gain.

- Compact size and minimum number of components guarantee a cost-effective converter.

- Good robustness of the closed-loop control under different working conditions.

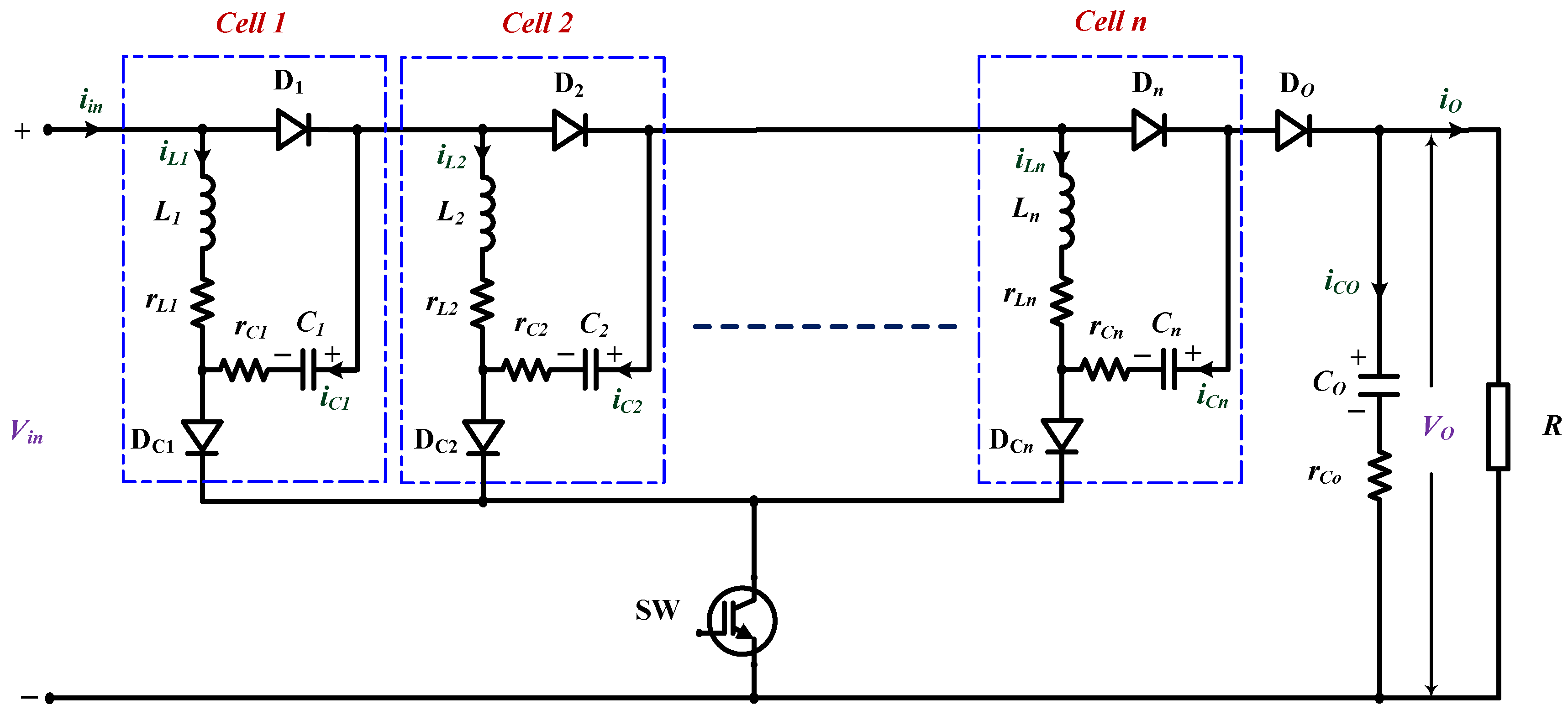

2. Proposed Converter Topology

3. State Space Average Modeling

- The semiconductor switch is on (i.e., closed) for a time dTs and is off (i.e., open) for a time (1 − d)Ts during a switching period time Ts.

- The duty ratio (d) is expressed as the ratio of the time the switch is on (on time) over the switching period time Ts. The switching frequency (Fs) is given as Fs = 1/Ts.

- The converter works in the CCM, considering the design considerations of inductors and capacitors as follows:where Ln is the inductance of cell n, Cn is the capacitance of cell n, Co is the output capacitance, R is the load resistance, ∆i is the allowable percentage of the inductor current ripple, and ∆v is the allowable percentage of the capacitor voltage ripple.

- The semiconductor switch and all diodes are modeled as ideal semiconductor devices.

- The parasitic series resistances of the passive elements (i.e., inductors and capacitors) are taken into consideration.

3.1. On State (0 < t < dTs)

3.2. Off State (dTs < t < Ts)

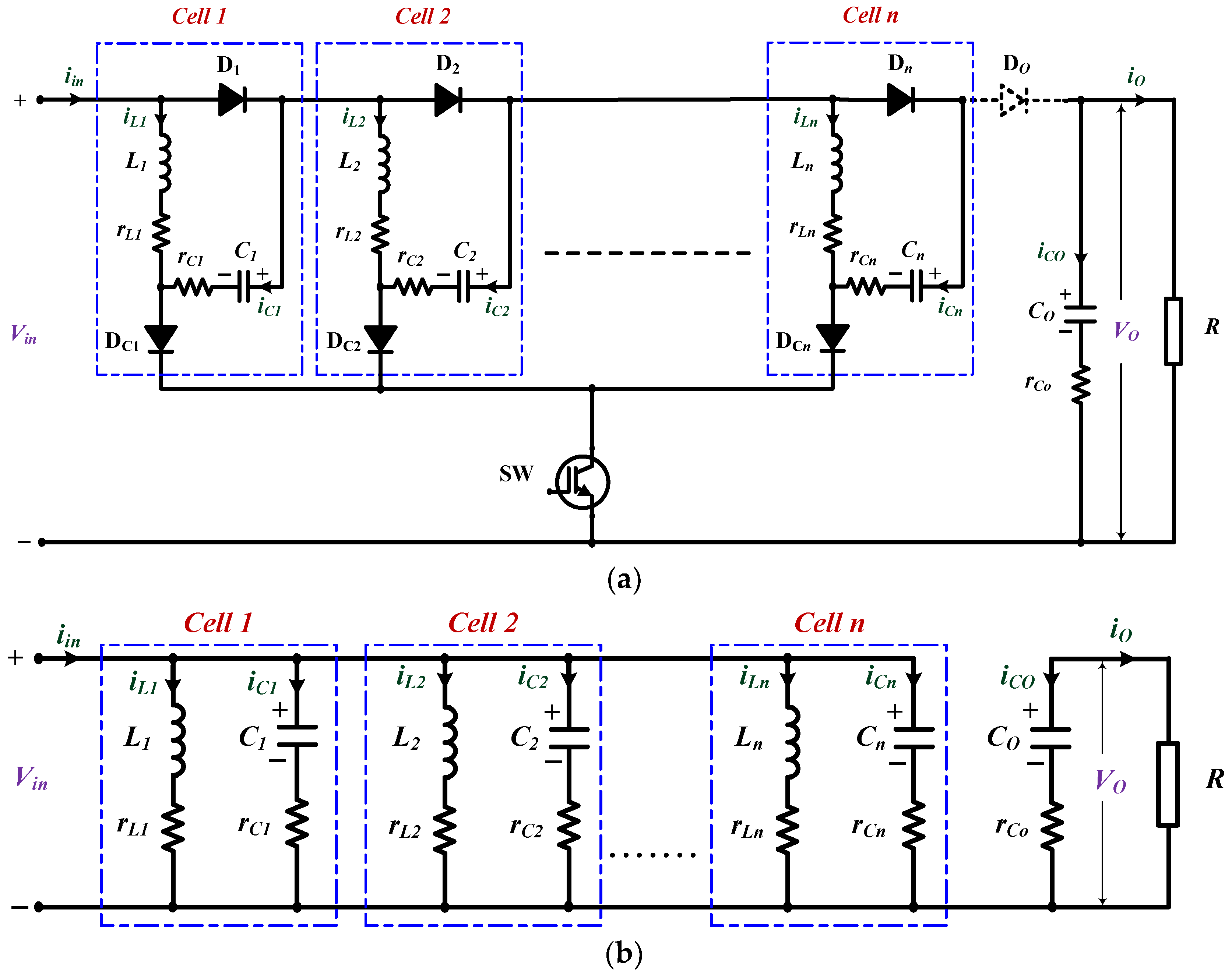

3.3. Average Model

4. Small Signal Analysis

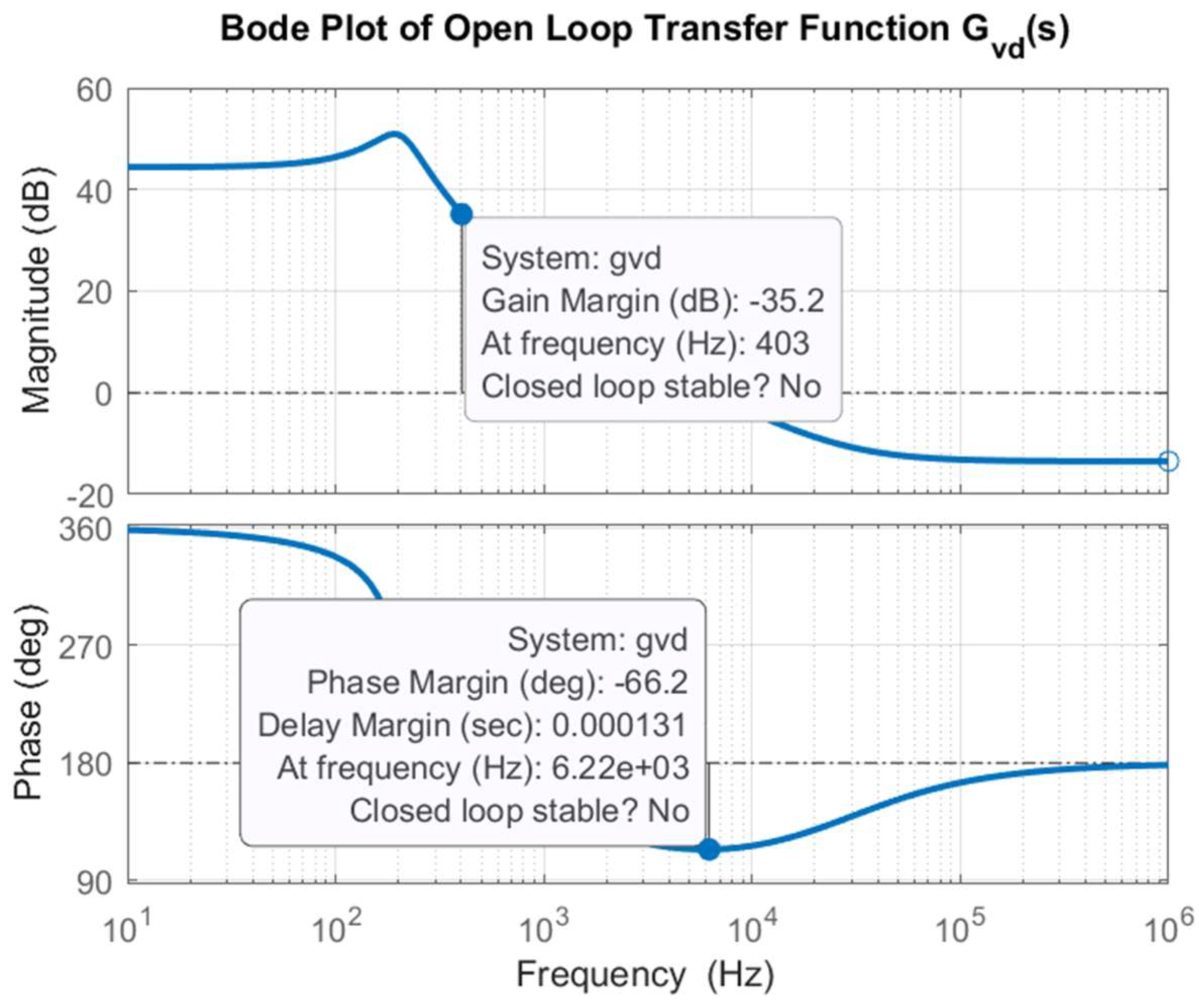

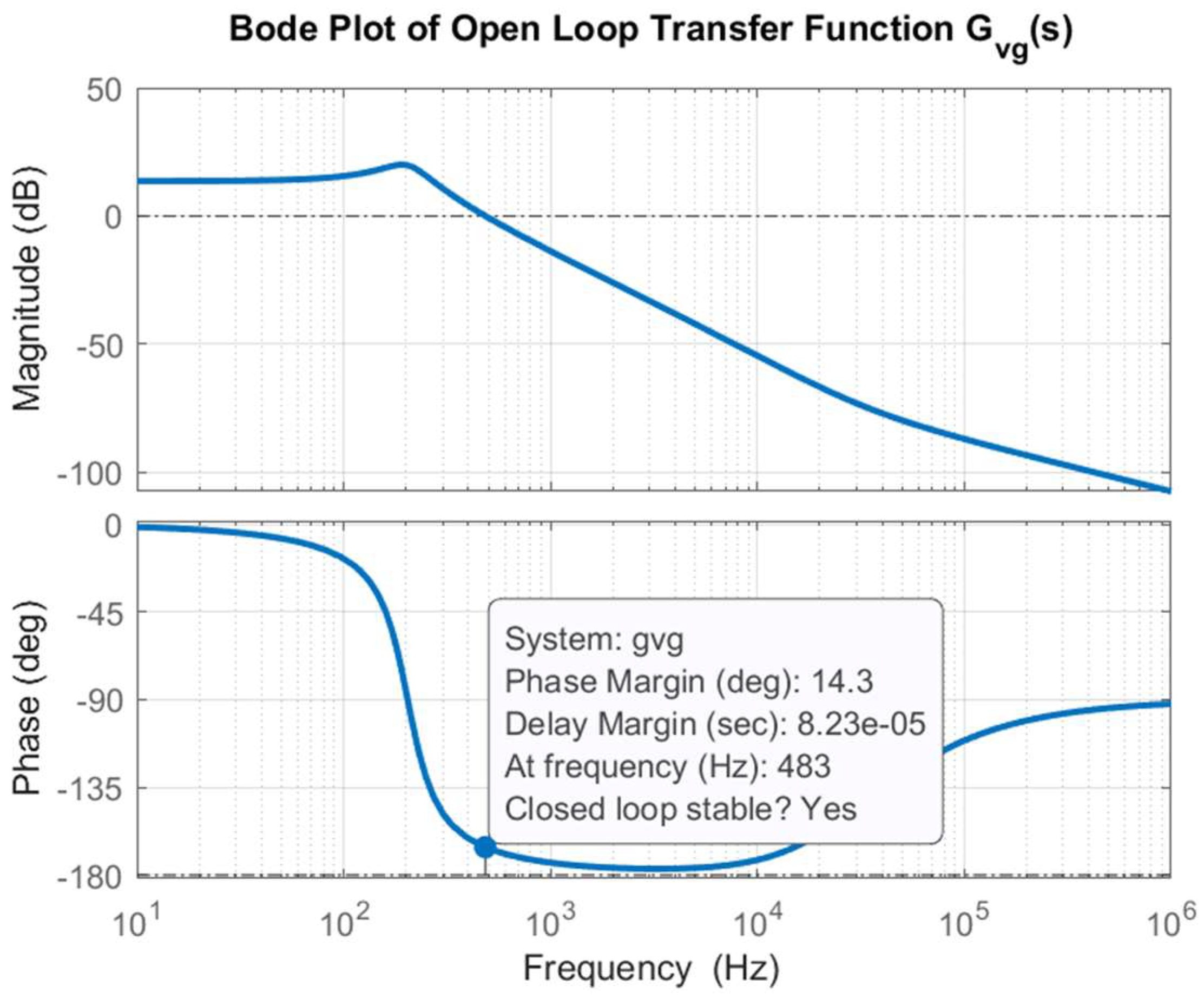

5. Stability Analysis

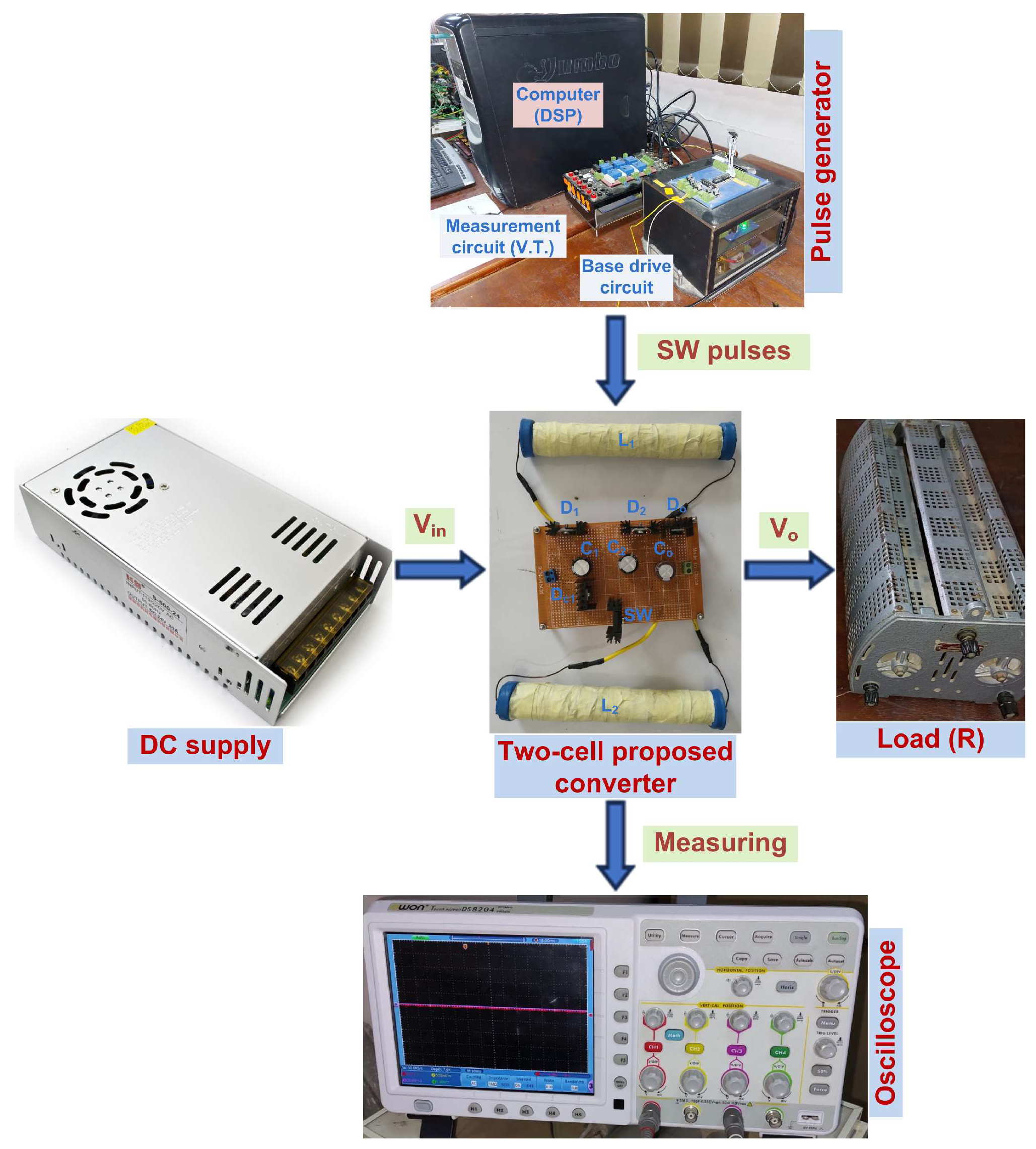

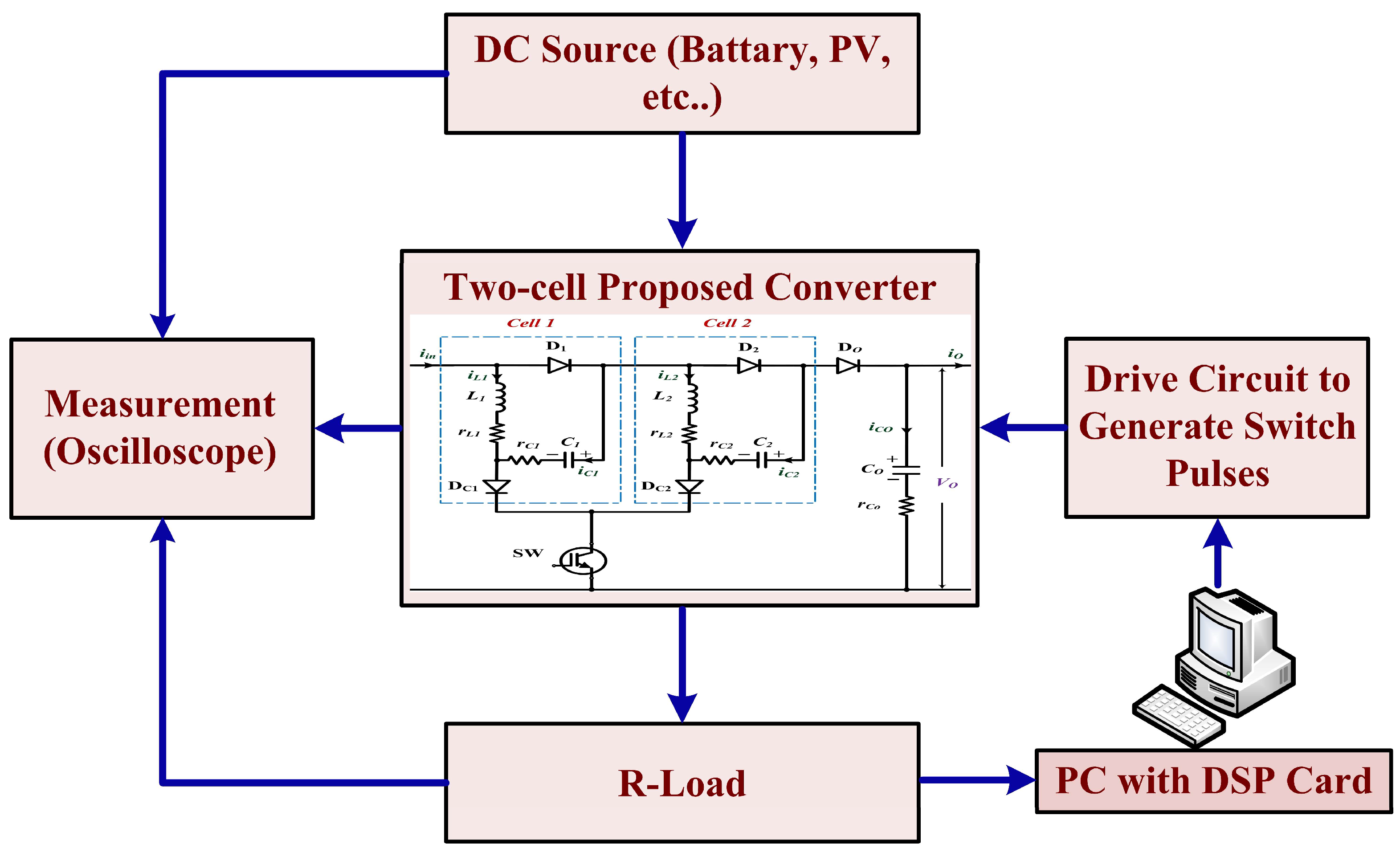

6. Experimental System Setup

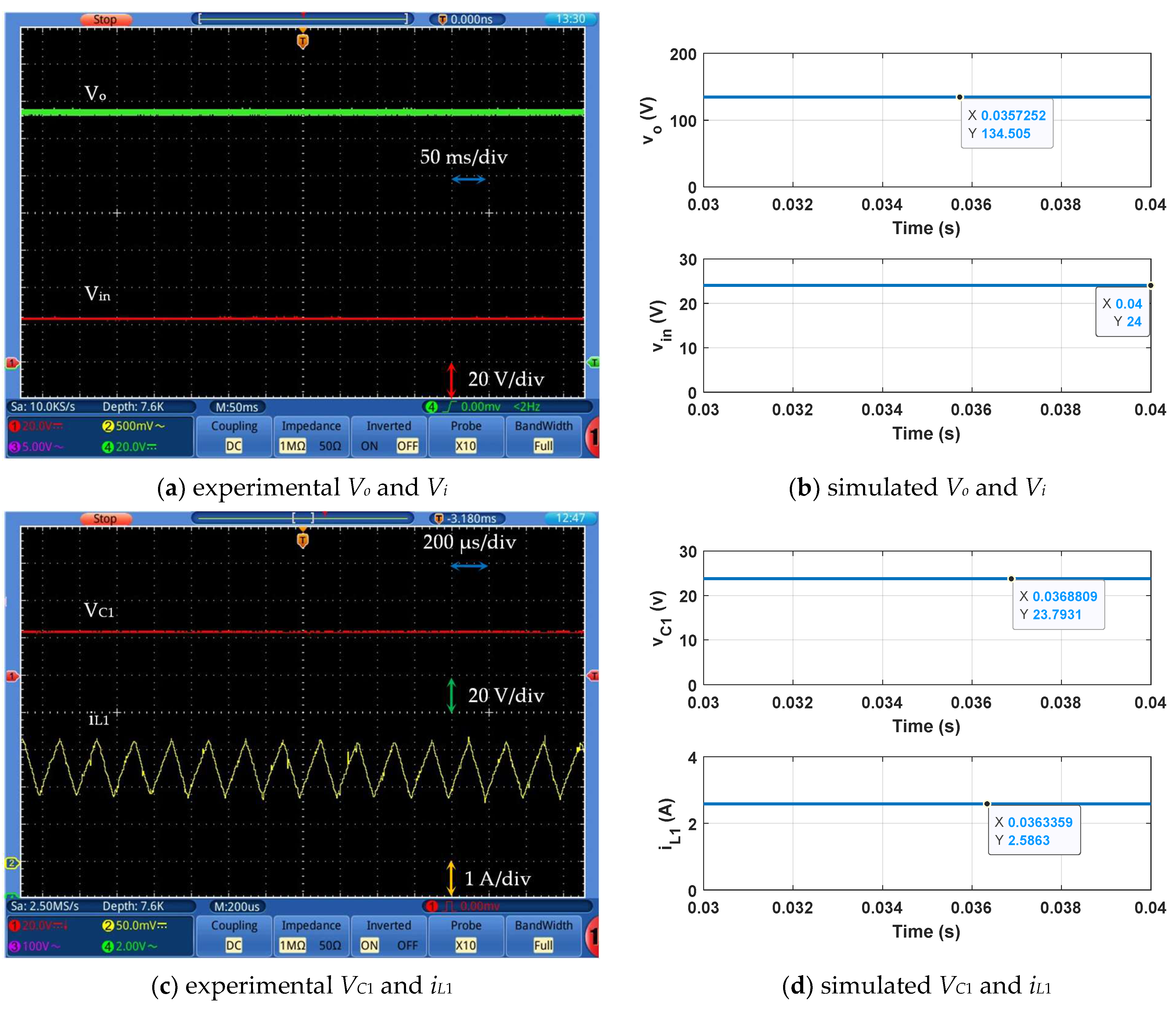

7. Open-Loop Performance

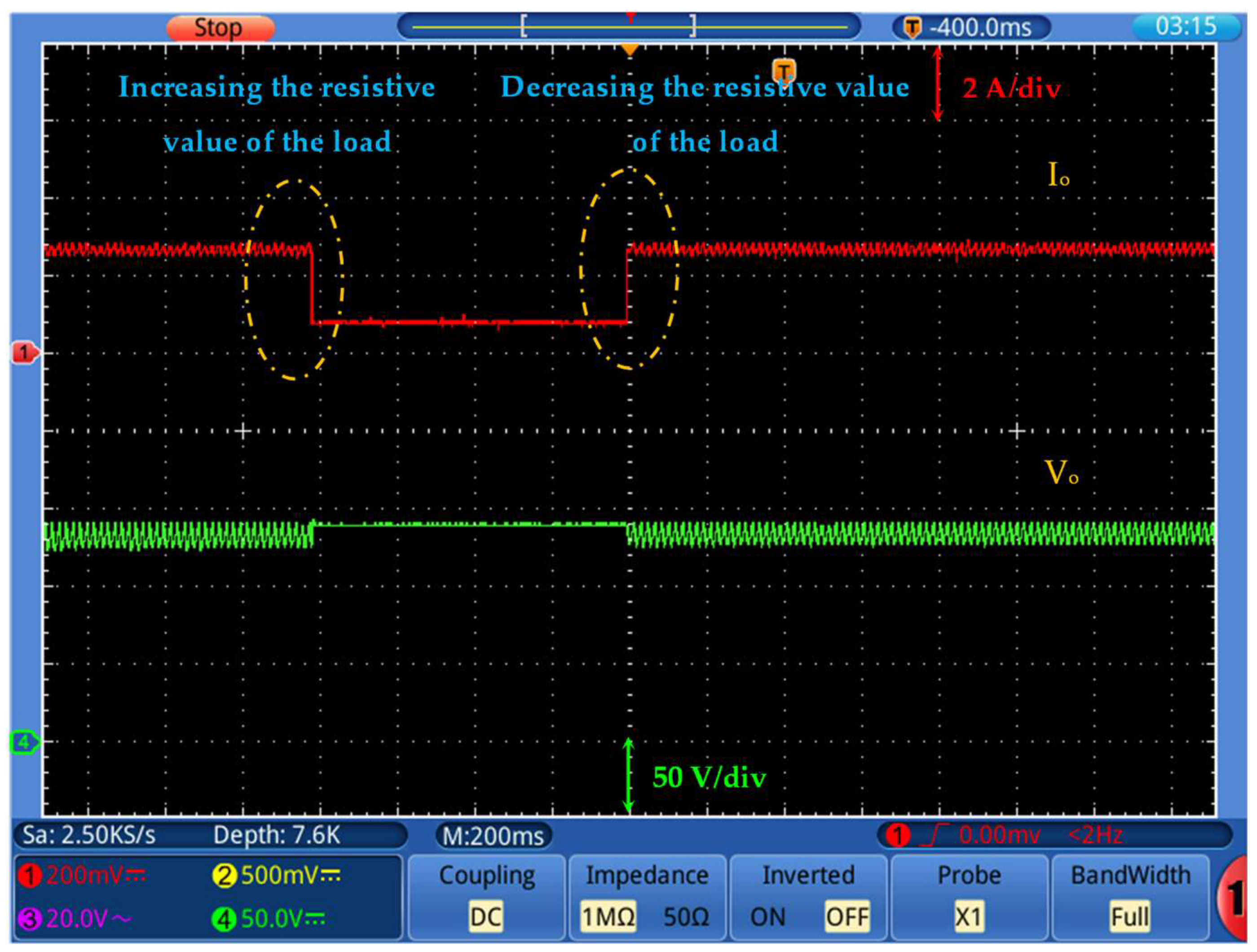

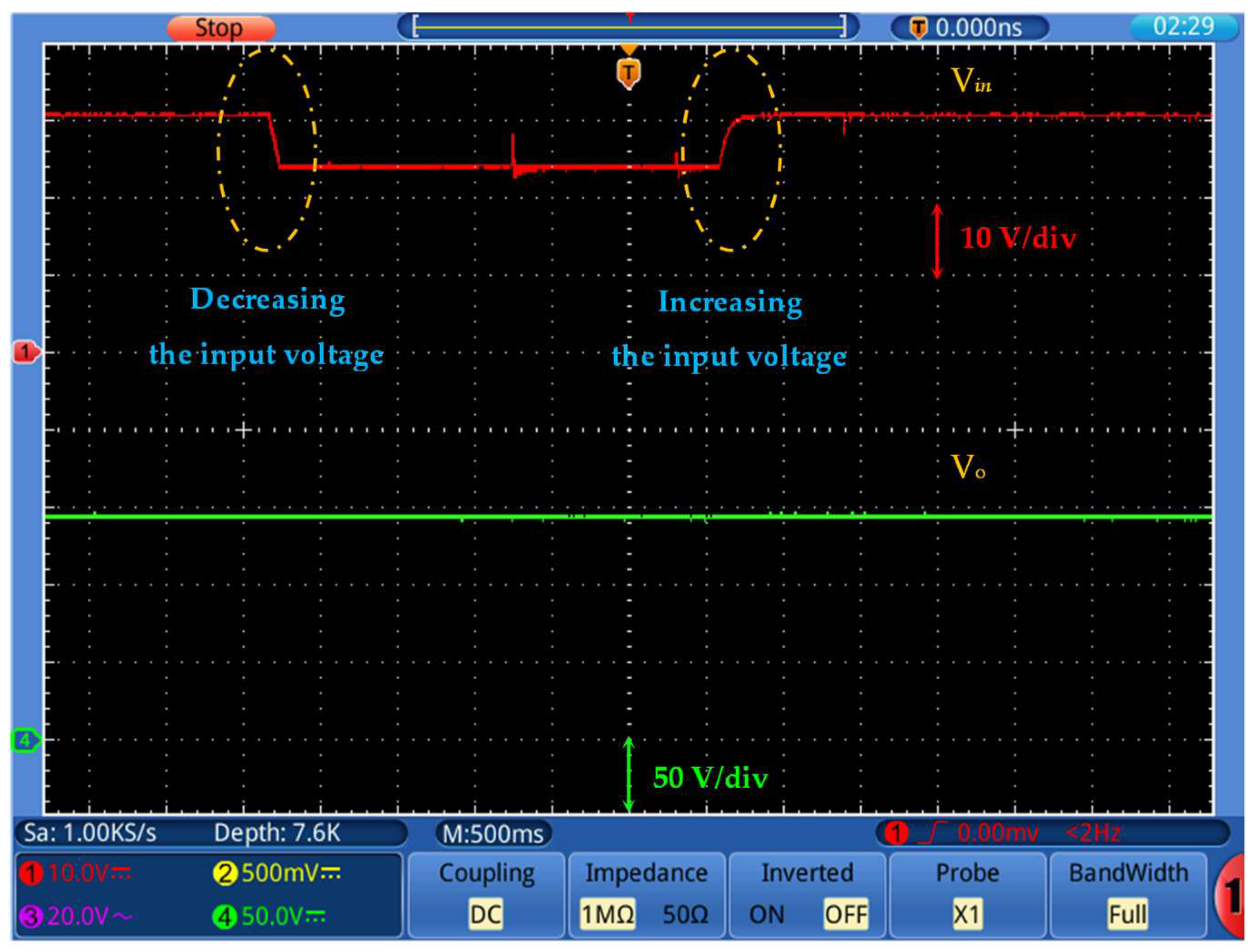

8. Closed-Loop Performance

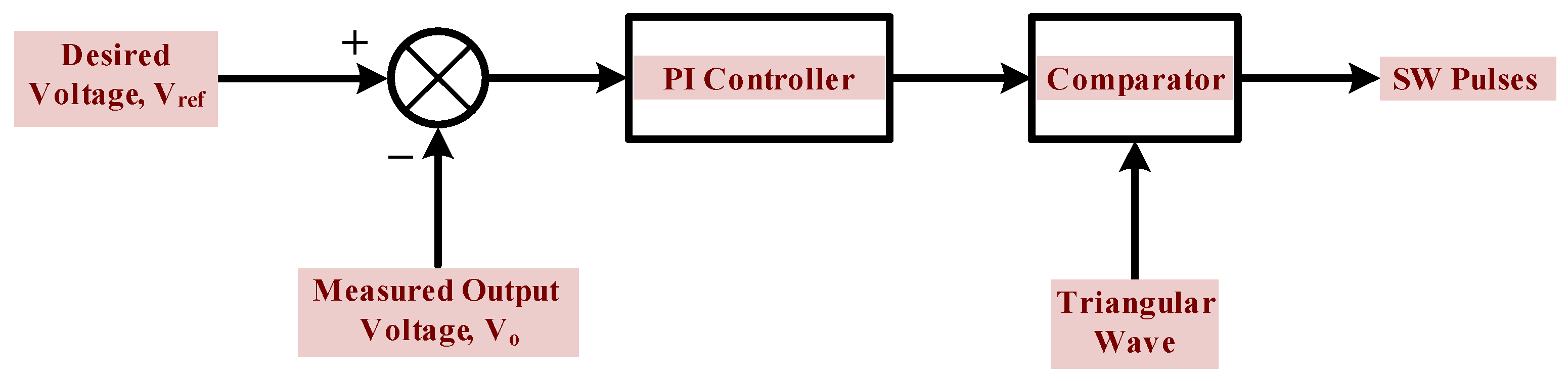

8.1. PI Controller

8.2. Closed-Loop Results

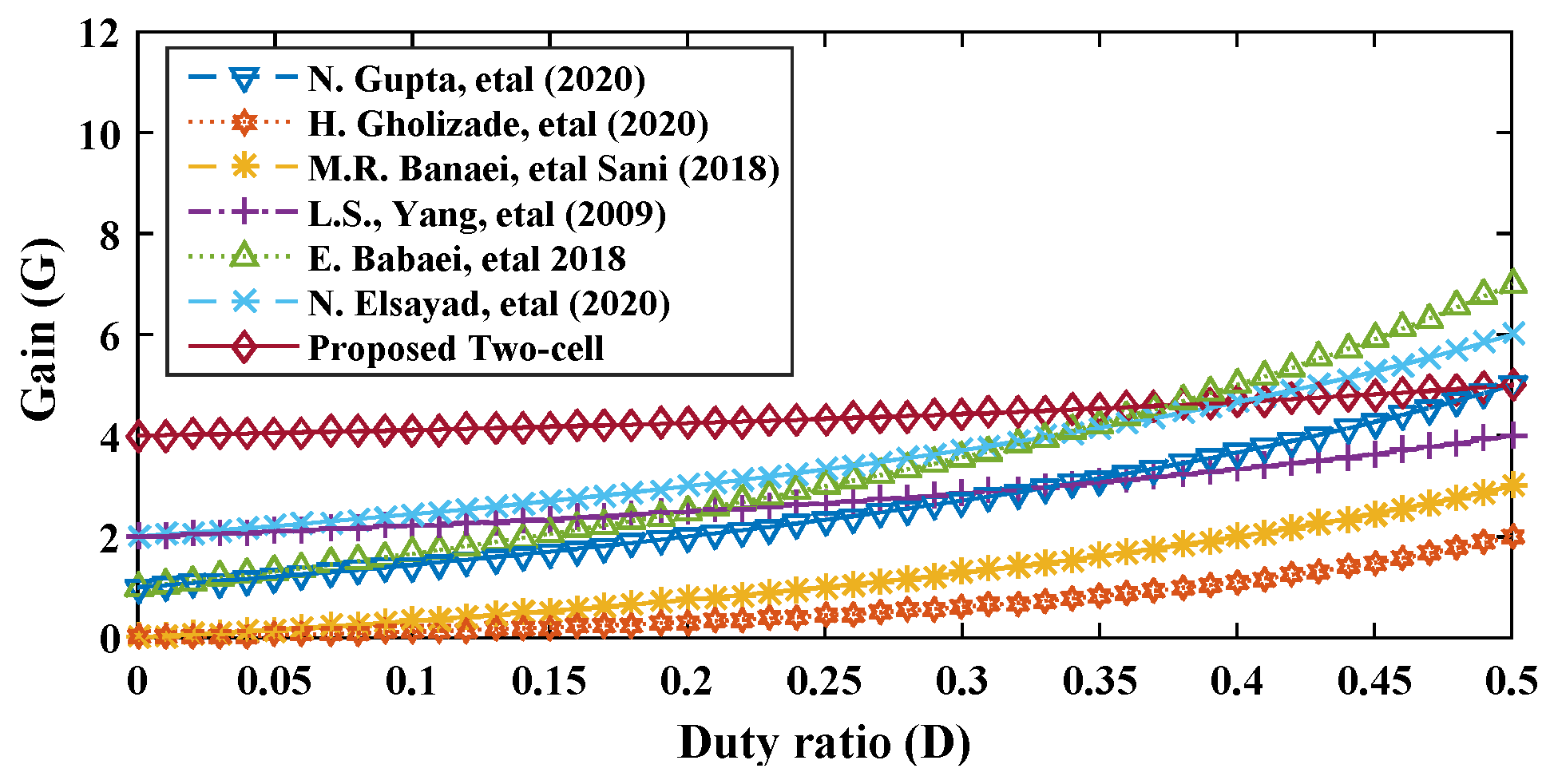

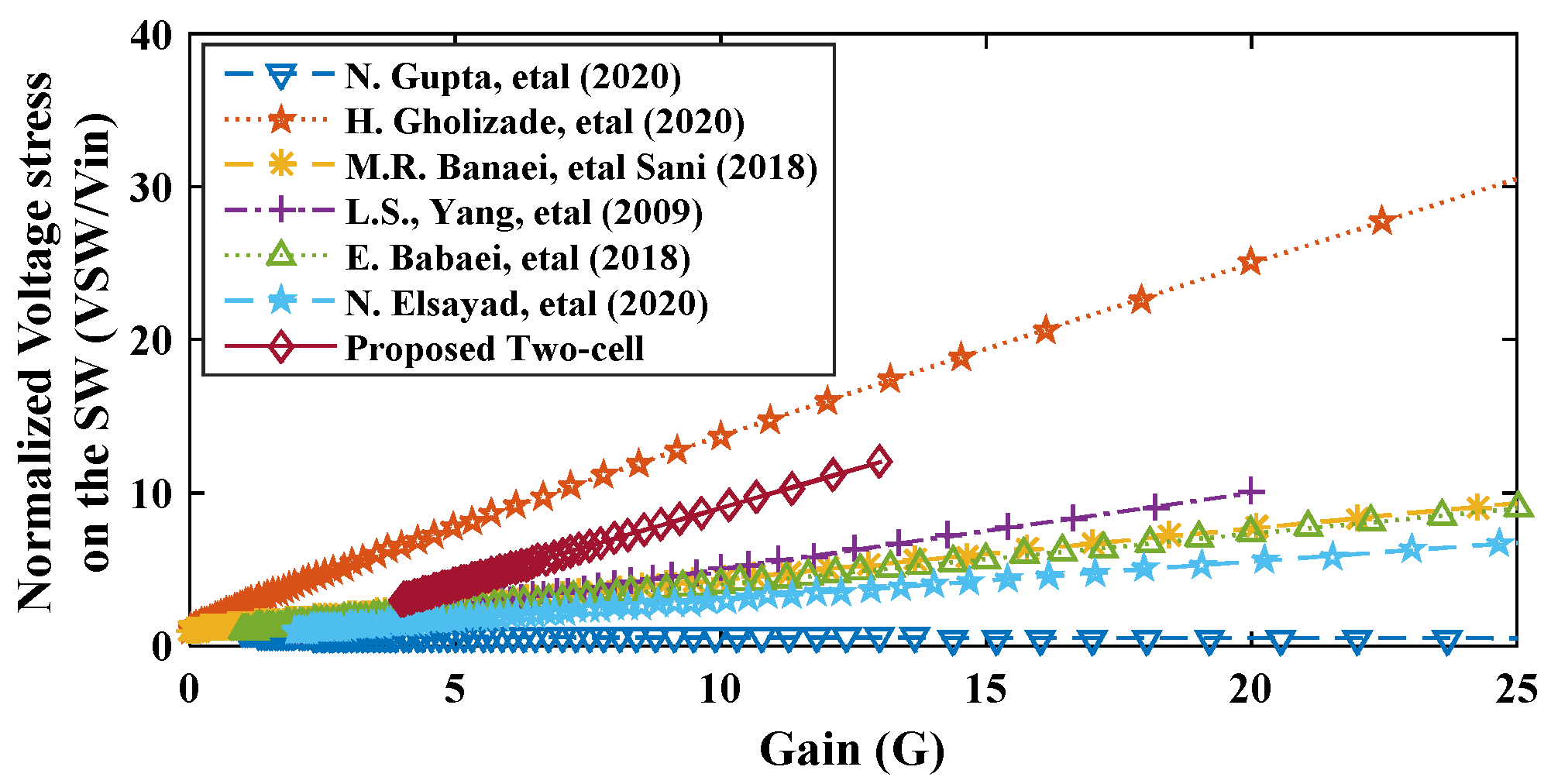

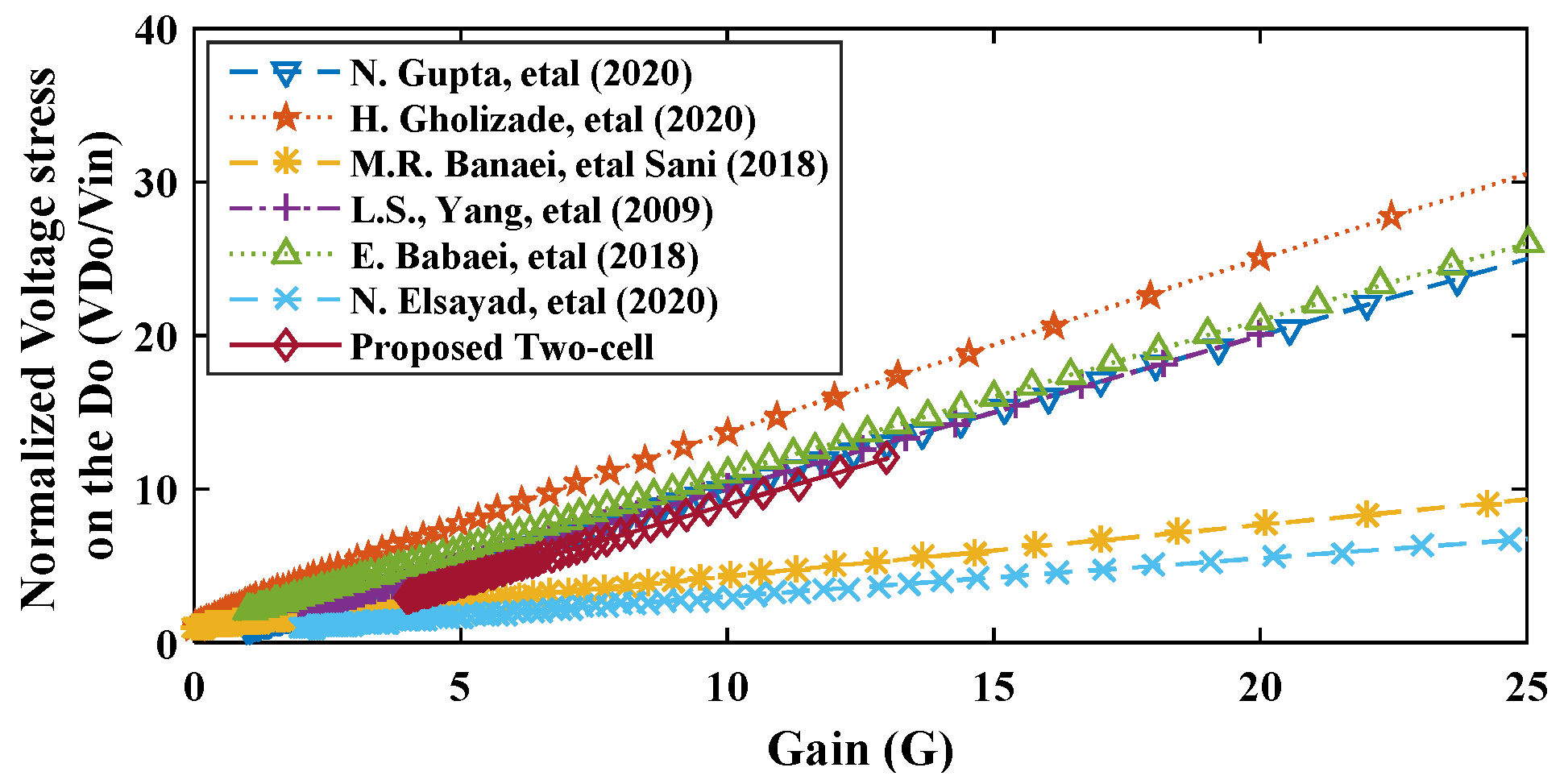

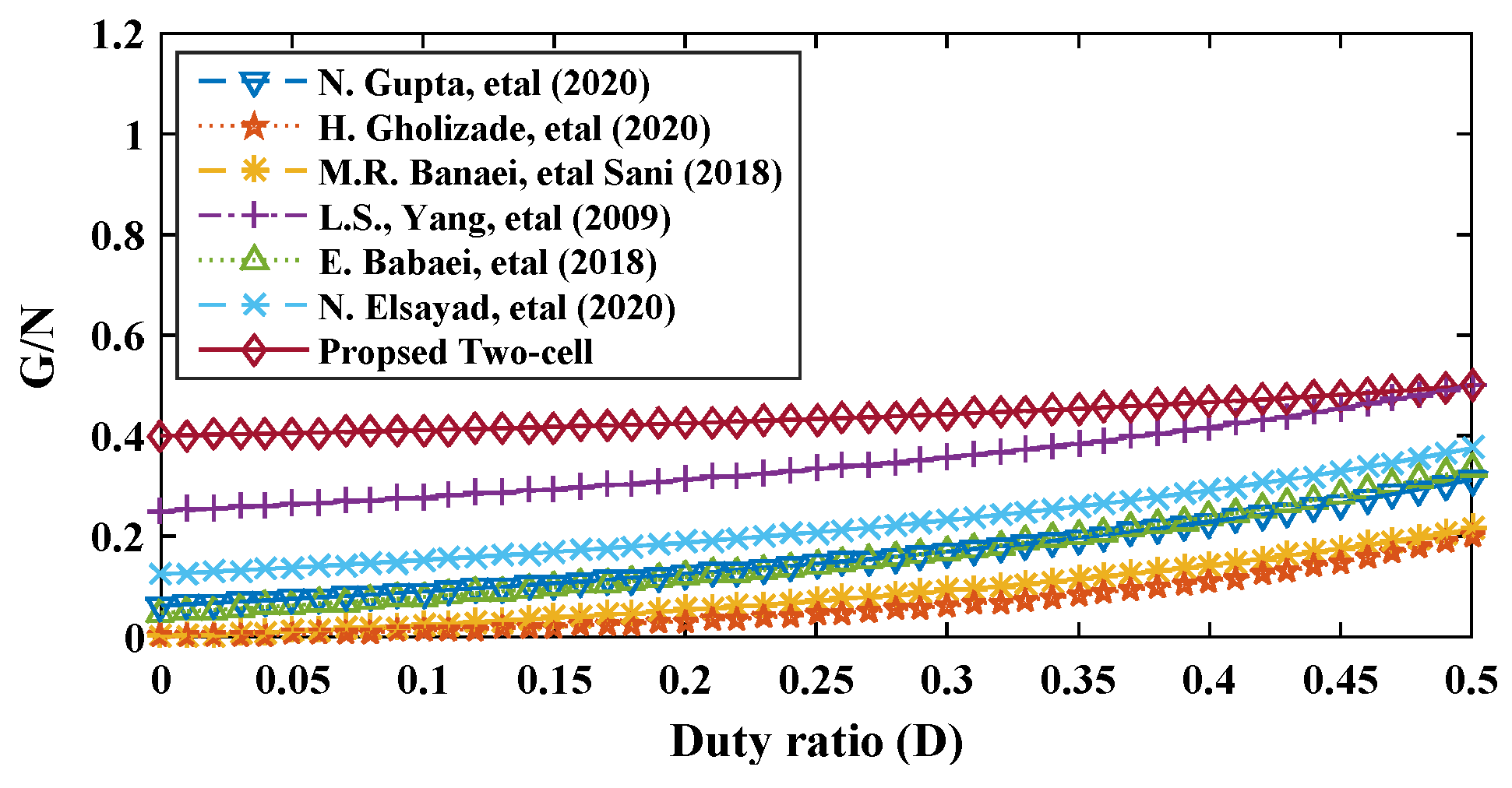

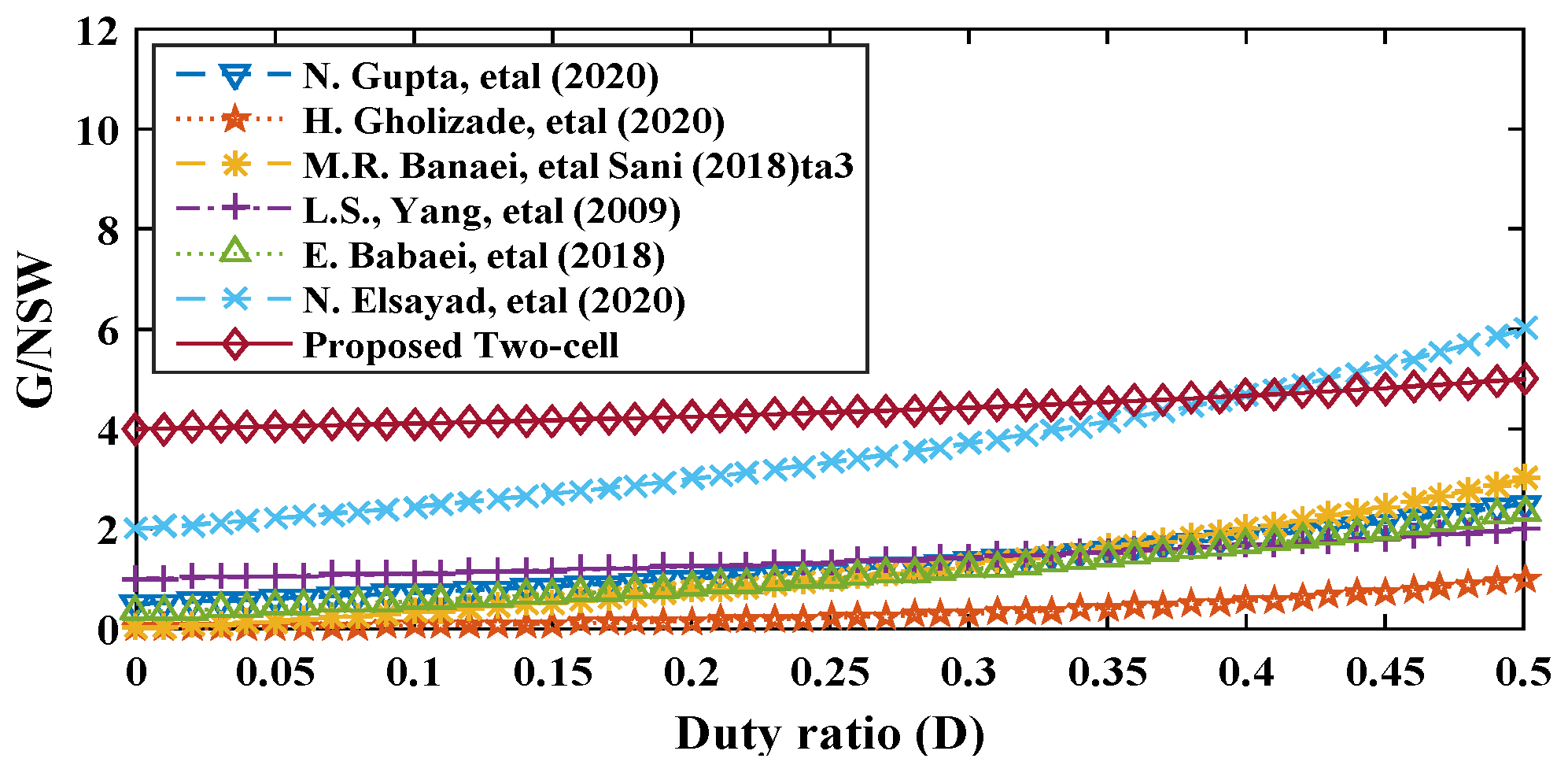

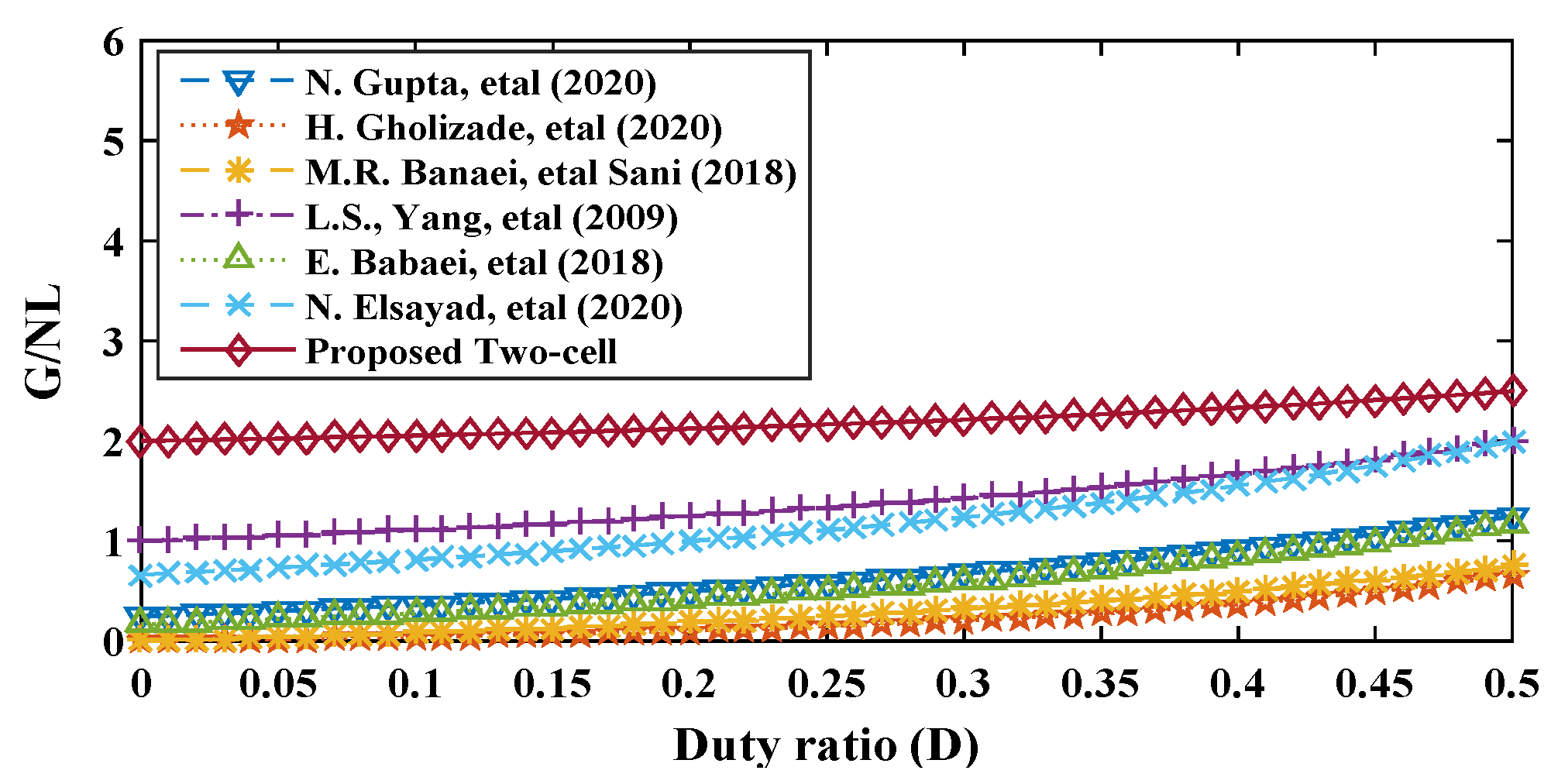

9. Comparison with Recent Converters

10. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Alkhaldi, A.; Elkhateb, A.; Laverty, D. Voltage Lifting Techniques for Non-Isolated DC/DC Converters. Electronics 2023, 12, 718. [Google Scholar] [CrossRef]

- Zhang, C.; Xu, B.; Jasni, J.; Radzi, M.A.M.; Azis, N.; Zhang, Q. Model Control and Digital Implementation of the Three Phase Interleaved Parallel Bidirectional Buck–Boost Converter for New Energy Electric Vehicles. Energies 2022, 15, 7178. [Google Scholar] [CrossRef]

- Chen, J.; Hu, H.; Wang, M.; Ge, Y.; Wang, K.; Huang, Y.; Yang, K.; He, Z.; Xu, Z.; Li, Y.R. Power Flow Control-Based Regenerative Braking Energy Utilization in AC Electrified Railways: Review and Future Trends. IEEE Trans. Intell. Transp. Syst. 2024, 25, 6345–6365. [Google Scholar] [CrossRef]

- Elbarbary, Z.M.S.; Cheema, K.M.; Al-Gahtani, S.F.; El-Sehiemy, R.A. High gain chopper supplied from PV system to fed synchronous reluctance motor drive for pumping water application. Sci. Rep. 2022, 12, 15519. [Google Scholar] [CrossRef]

- Tahami, H.; Akbari, E.; Mohammed, A.H.; Faraji, R.; Channumsin, S. A Transformerless Enhanced-Boost Quasi-Z-Source Inverter with Low Input Current Ripple for Stand-Alone RES-Based Systems. Energies 2023, 16, 2611. [Google Scholar] [CrossRef]

- Mumtaz, F.; Yahaya, N.Z.; Meraj, S.T.; Singh, N.S.S.; Abro, G.E.M. A Novel Non-Isolated High-Gain Non-Inverting Interleaved DC–DC Converter. Micromachines 2023, 14, 585. [Google Scholar] [CrossRef] [PubMed]

- Li, S.; Haskew, T.A.; Li, D.; Hu, F. Integrating photovoltaic and power converter characteristics for energy extraction study of solar PV systems,” Renewable Energy. Renew. Energy 2011, 36, 3238–3245. [Google Scholar] [CrossRef]

- Gules, R.; Pfitscher, L.L.; Franco, L.C. An Interleaved Boost DC-DC Converter with Large Conversion Ratio. In Proceedings of the IEEE International Symposium on Industrial Electronics, Rio de Janeiro, Brazil, 9–11 June 2003; Volume 1, pp. 411–416. [Google Scholar] [CrossRef]

- Yao, G.; Chen, A.; He, X. Soft Switching Circuit for Interleaved Boost Converters. IEEE Trans. Power Electron. 2007, 22, 80–86. [Google Scholar] [CrossRef]

- Ismail, E.H.; Al-Saffar, M.A.; Sabzali, A.J.; Fardoun, A.A. A Family of Single-Switch PWM Converters with High Step-Up Conversion Ratio. IEEE Trans. Circuits Syst.—I Regul. Pap. 2008, 55, 1159–1171. [Google Scholar] [CrossRef]

- Axelrod, B.; Berkovich, Y.; Ioinovici, A. Switched-Capacitor/Switched-Inductor Structures for Getting Transformerless Hybrid DC–DC PWM Converters. IEEE Trans. Circuits Syst.—I Regul. Pap. 2008, 55, 687–696. [Google Scholar] [CrossRef]

- Yang, P.; Xu, J.; Zhou, G.; Zhang, S. A New Quadratic Boost Converter with High Voltage Step-up Ratio and Reduced Voltage Stress. In Proceedings of the IEEE 7th International Power Electronics and Motion Control Conference—ECCE Asia, Harbin, China, 2–5 June 2012; pp. 1–6. [Google Scholar] [CrossRef]

- Algamluoli, A.F.; Wu, X. A New Single-Cell Hybrid Inductor-Capacitor DC-DC Converter for Ultra-High Voltage Gain in Renewable Energy Applications. Electronics 2023, 12, 3101. [Google Scholar] [CrossRef]

- Alilou, S.M.; Maalandish, M.; Samadian, A.; Abolhassani, P.; Hosseini, S.H.; Khooban, M.-H. A new high step-up DC-DC converter using voltage lift techniques suitable for renewable applications. CSEE J. Power Energy Syst. 2023, 1–10, (early access). [Google Scholar]

- Mansour, A.S.; Sarhan, E.M.; El-Sabbe, A.E.; Osheba, D.S.M. A Single-switch Non-isolated High Gain DC/DC Converter for PV Applications. Eng. Res. J. 2022, 45, 261–271. [Google Scholar] [CrossRef]

- Mansour, A.S.; Amer, A.H.; El-Kholy, E.E.; Zaky, M.S. High gain DC/DC converter with continuous input current for renewable energy applications. Sci. Rep. 2022, 12, 12138. [Google Scholar] [CrossRef]

- Zaid, M.; Malick, I.H.; Ashraf, I.; Tariq, M.; Alamri, B.; Rodrigues, E.M.G. A Nonisolated Transformerless High-Gain DC–DC Converter for Renewable Energy Applications. Electronics 2022, 11, 2014. [Google Scholar] [CrossRef]

- Gholizadeh, H.; Ben-Brahim, L. A New Non-Isolated High-Gain Single-Switch DC–DC Converter Topology with a Continuous Input Current. Electronics 2022, 11, 2900. [Google Scholar] [CrossRef]

- Mirzaei, A.; Rezvanyvardom, M.; Najafi, E. A fully soft switched high step-up SEPIC-boost DC-DC converter with one auxiliary switch. Int. J. Circuit Theory Appl. 2019, 47, 427–444. [Google Scholar] [CrossRef]

- Patidar, K.; Umarikar, A.C. High step-up pulse-width modulation DC–DC converter based on quasi-Z-source topology. IET Power Electron. 2015, 8, 477–488. [Google Scholar] [CrossRef]

- Siwakoti, Y.P.; Blaabjerg, F.; Loh, P.C. Quasi Y-Source Boost DC-DC Converter. IEEE Trans. Power Electron. 2015, 30, 6514–6519. [Google Scholar] [CrossRef]

- Zhao, J.; Chen, D.; Jiang, J. Transformerless High Step-Up DC-DC Converter with Low Voltage Stress for Fuel Cells. IEEE Access 2021, 9, 10228–10238. [Google Scholar] [CrossRef]

- Salehi, N.; Martínez-García, H.; Velasco-Quesada, G. Modified Cascaded Z-Source High Step-Up Boost Converter. Electronics 2020, 9, 1932. [Google Scholar] [CrossRef]

- Nouri, T.; Hosseini, S.H.; Babaei, E. Analysis of voltage and current stresses of a generalised step-up DC–DC converter. IET Power Electron. 2014, 7, 1347–1361. [Google Scholar] [CrossRef]

- Gupta, N.; Bhaskar, M.S.; Almakhles, D.; Sanjeevikumar, P.; Subramaniam, U.; Leonowicz, Z.; Mitolo, M. Novel non-isolated quad-switched inductor double-switch converter for DC microgrid application. In Proceedings of the IEEE International Conference on Environment and Electrical Engineering and IEEE Industrial and Commercial Power Systems Europe (EEEIC/I&CPS Europe), Madrid, Spain, 9–12 June 2020; pp. 1–6. [Google Scholar] [CrossRef]

- Gholizade, H.; Aboufazeli, S.; Rafiee, Z.; Afjei, E.; Hamzeh, M. A non-isolated high gain DC–DC converters with positive output voltage and reduced current stresses. In Proceedings of the IEEE 11th Power Electronics, Drive Systems, and Technologies Conference, Tehran, Iran, 4–6 February 2020; pp. 1–6. [Google Scholar] [CrossRef]

- Banaei, M.R.; Sani, S.G. Analysis and implementation of a new SEPIC based single switch buck-boost DC–DC converter with continuous input current. IEEE Trans. Power Electron. 2018, 33, 10317–10325. [Google Scholar] [CrossRef]

- Yang, L.S.; Liang, T.J.; Chen, J.F. Transformerless DC–DC converters with high step-up voltage gain. IEEE Trans. Industr. Electron. 2009, 56, 3144–3152. [Google Scholar] [CrossRef]

- Babaei, E.; Maheri, H.M.; Sabahi, M.; Hosseini, S.H. Extendable nonisolated high gain DC–DC converter based on active–passive inductor cells. IEEE Trans. Ind. Electron. 2018, 65, 9478–9487. [Google Scholar] [CrossRef]

- Elsayad, N.; Moradisizkoohi, H.; Mohammed, O. A new SEPIC-based step-up DC-DC converter with wide conversion ratio for fuel cell vehicles: Analysis and design. IEEE Trans. Ind. Electron. 2020, 68, 6390–6400. [Google Scholar] [CrossRef]

- Mansour, A.S.; Zaky, M.S. A new extended single-switch high gain DC–DC boost converter for renewable energy applications. Sci. Rep. 2023, 13, 264. [Google Scholar] [CrossRef] [PubMed]

- Das, H.S.; Li, Z.; Li, S.; Dong, W. Small Signal Modeling, Control and Experimentation of Boost Converter Including Parasitic Elements. J. Control Autom. Electr. Syst. 2021, 32, 956–967. [Google Scholar] [CrossRef]

- Deraz, S.A.; Azazi, H.Z.; Zaky, M.S.; Metwaly, M.K.; Dessouki, M.E. Performance Investigation of Three-Phase Three-Switch Direct PWM AC/AC Voltage Converters. IEEE Access 2019, 7, 11485–11501. [Google Scholar] [CrossRef]

- Alajmi, B.N.; Ahmed, N.A.; Al-Othman, A.K. Small-signal analysis and control implementation of boost converter fed PMDC motor for electric vehicle applications. J. Eng. Res. 2021, 9, 189–208. [Google Scholar] [CrossRef]

- Abdel-Gawad, H.; Sood, V.K. Small-Signal Analysis of Boost Converter, including Parasitics, operating in CCM. In Proceedings of the 6th IEEE Power India International Conference (PIICON), Delhi, India, 5–7 December 2014; pp. 1–5. [Google Scholar] [CrossRef]

- Khatun, K.; Ratnam, V.V.; Rathore, A.K.; Narasimharaju, B.L. Small-Signal Analysis and Control of Soft-Switching Naturally Clamped Snubberless Current-Fed Half-Bridge DC/DC Converter. Appl. Sci. 2020, 10, 6130. [Google Scholar] [CrossRef]

- Górecki, P. Electrothermal Averaged Model of a Diode–IGBT Switch for a Fast Analysis of DC–DC Converters. IEEE Trans-Actions Power Electron. 2022, 37, 13003–13013. [Google Scholar] [CrossRef]

- Górecki, P.; d’Alessandro, V. A Datasheet-Driven Electrothermal Averaged Model of a Diode–MOSFET Switch for Fast Sim-ulations of DC–DC Converters. Electronics 2024, 13, 154. [Google Scholar] [CrossRef]

- Ayachit, A.; Kazimierczuk, M.K. Averaged Small-Signal Model of PWM DC-DC Converters in CCM Including Switching Power Loss. IEEE Trans. Circuits Syst. II Express Briefs 2019, 66, 262–266. [Google Scholar] [CrossRef]

- Zhang, Y.; Dong, Z.; Liu, J.; Ma, X.; Li, X.; Han, J. Modeling and controller design of high voltage gain DC-DC converter with multi-cell diode-capacitor network. In Proceedings of the IEEE 8th International Power Electronics and Motion Control Conference (IPEMC-ECCE Asia), Hefei, China, 22–26 May 2016; pp. 3066–3072. [Google Scholar] [CrossRef]

- Garg, M.M.; Hote, Y.V.; Pathak, M.K. Design and Performance Analysis of a PWM dc–dc Buck Converter Using PI–Lead Compensator. Arab. J. Sci. Eng. 2015, 40, 3607–3626. [Google Scholar] [CrossRef]

| Parameter | Value |

|---|---|

| Vin | 24 V |

| Vo | 132 V |

| rLi | 0.64 Ω |

| Li | 1.7 mH |

| rCi | 0.12 Ω |

| Ci | 47 µF |

| rCo | 0.12 Ω |

| Co | 47 µF |

| Fs | 5 kHz |

| R | 130 Ω |

| Diodes | MUR1560 |

| Main switch (SW) | FGH40N60UFD |

| Item | Ref. [25] | Ref. [26] | Ref. [27] | Ref. [28] | Ref. [29] | Ref. [30] | The Proposed n = 2 |

|---|---|---|---|---|---|---|---|

| Switch, SW | 2 | 2 | 1 | 2 | 3 | 1 | 1 |

| Inductor, L | 4 | 3 | 4 | 2 | 6 | 3 | 2 |

| Capacitor, C | 1 | 3 | 6 | 2 | 1 | 7 | 3 |

| Diode, D | 9 | 2 | 3 | 2 | 11 | 5 | 4 |

| Total Component Count | 16 | 10 | 14 | 8 | 21 | 16 | 10 |

| Gain, G | |||||||

| ) | |||||||

| ) | |||||||

| Fs (KHz) | 50 | 60 | 33 | 100 | 20 | 100 | 5 |

| Open/Closed Loop | Open-loop | Open-loop | Open-loop | Open-loop | Open/Closed-loop | Open/Closed-loop | Open/Closed-loop |

| Control Method | n/a | n/a | n/a | n/a | PI Controller | Type III voltage controller | PI Controller |

| Exp. Efficiency (%) Pout = 100 W | n/a | n/a | 93 | 92 | 95.6 | 92.1 | 96 |

| Type of Load | Grounded | Grounded | Grounded | Grounded | Floating | Floating | Grounded |

| G at D = 0.4 | 3.67 | 1.11 | 2 | 3.33 | 5 | 4.67 | 4.67 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Deraz, S.A.; Zaky, M.S.; Tawfiq, K.B.; Mansour, A.S. State Space Average Modeling, Small Signal Analysis, and Control Implementation of an Efficient Single-Switch High-Gain Multicell Boost DC-DC Converter with Low Voltage Stress. Electronics 2024, 13, 3264. https://doi.org/10.3390/electronics13163264

Deraz SA, Zaky MS, Tawfiq KB, Mansour AS. State Space Average Modeling, Small Signal Analysis, and Control Implementation of an Efficient Single-Switch High-Gain Multicell Boost DC-DC Converter with Low Voltage Stress. Electronics. 2024; 13(16):3264. https://doi.org/10.3390/electronics13163264

Chicago/Turabian StyleDeraz, Said A., Mohamed S. Zaky, Kotb B. Tawfiq, and Arafa S. Mansour. 2024. "State Space Average Modeling, Small Signal Analysis, and Control Implementation of an Efficient Single-Switch High-Gain Multicell Boost DC-DC Converter with Low Voltage Stress" Electronics 13, no. 16: 3264. https://doi.org/10.3390/electronics13163264

APA StyleDeraz, S. A., Zaky, M. S., Tawfiq, K. B., & Mansour, A. S. (2024). State Space Average Modeling, Small Signal Analysis, and Control Implementation of an Efficient Single-Switch High-Gain Multicell Boost DC-DC Converter with Low Voltage Stress. Electronics, 13(16), 3264. https://doi.org/10.3390/electronics13163264