A High-Quality and Space-Efficient Design for Memristor Emulation

Abstract

:1. Introduction

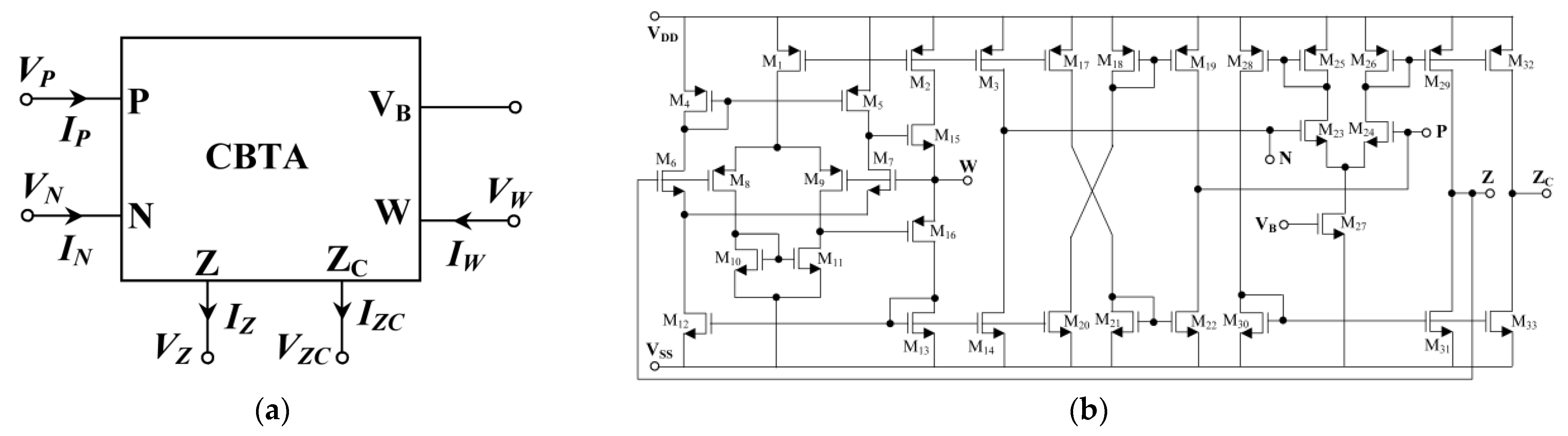

2. CBTA Symbol and CMOS Realization

3. Proposed Memristor Emulator Using CBTA

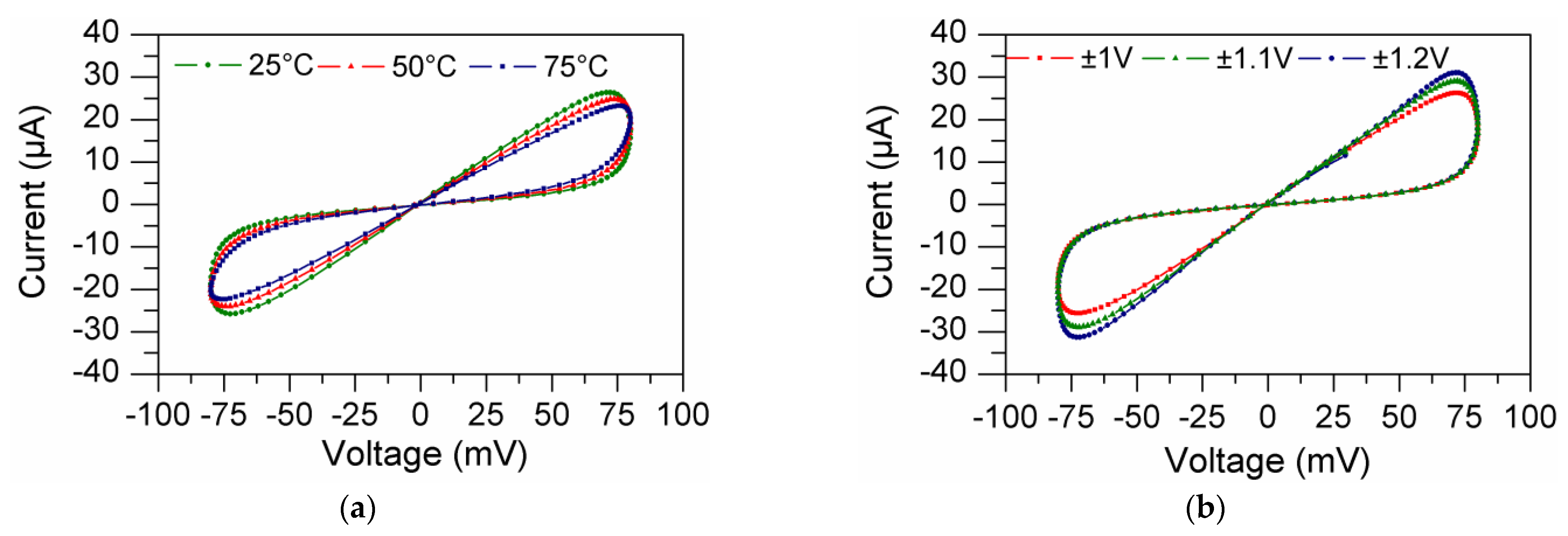

4. Non-Ideal Study of Memristor Emulator

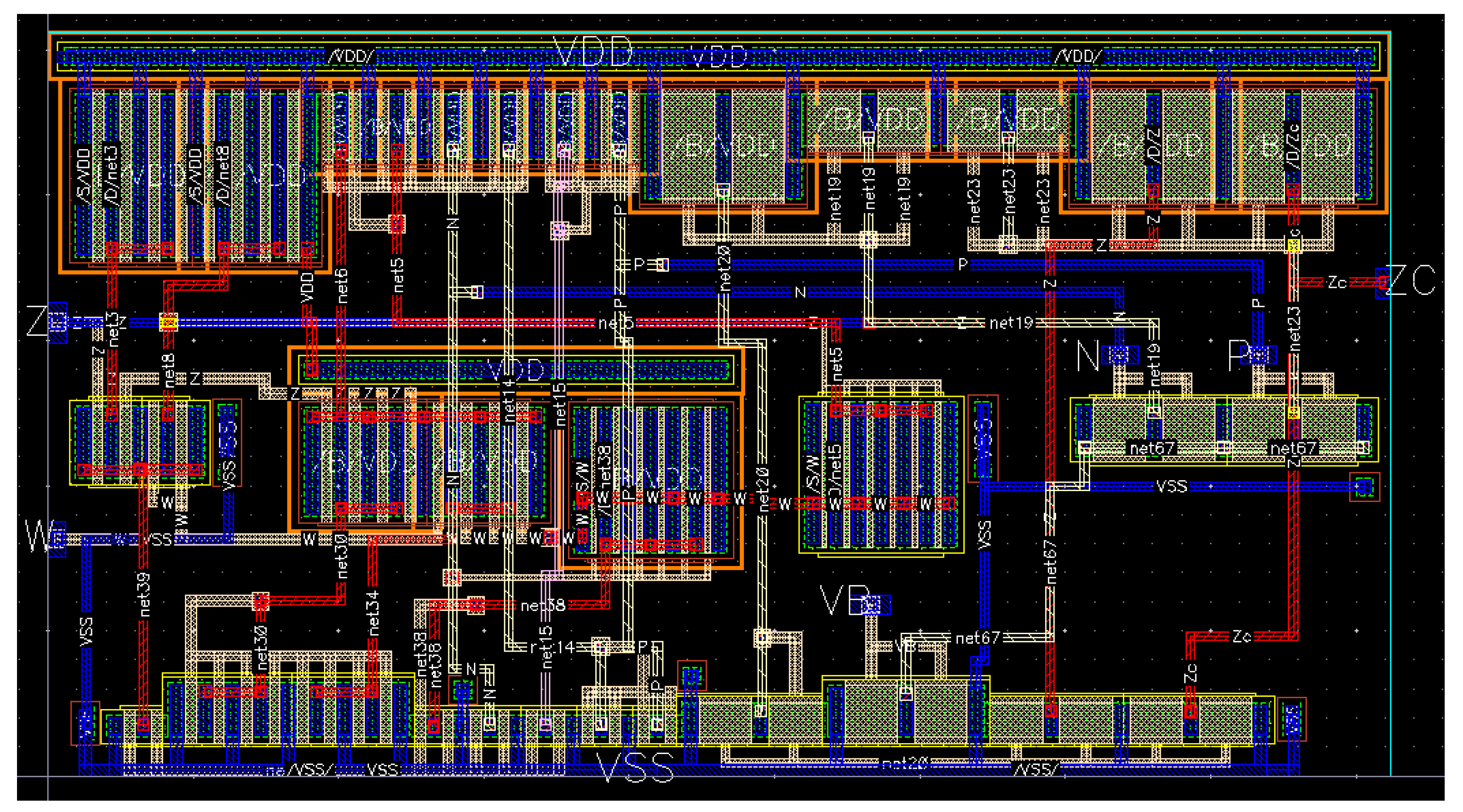

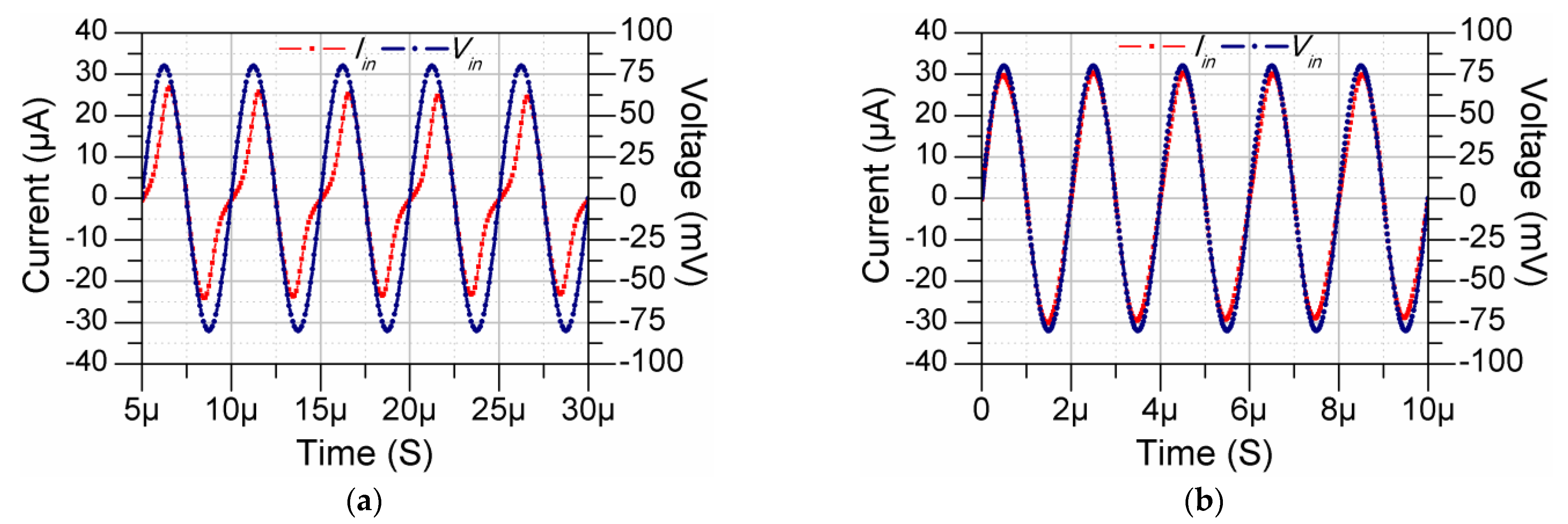

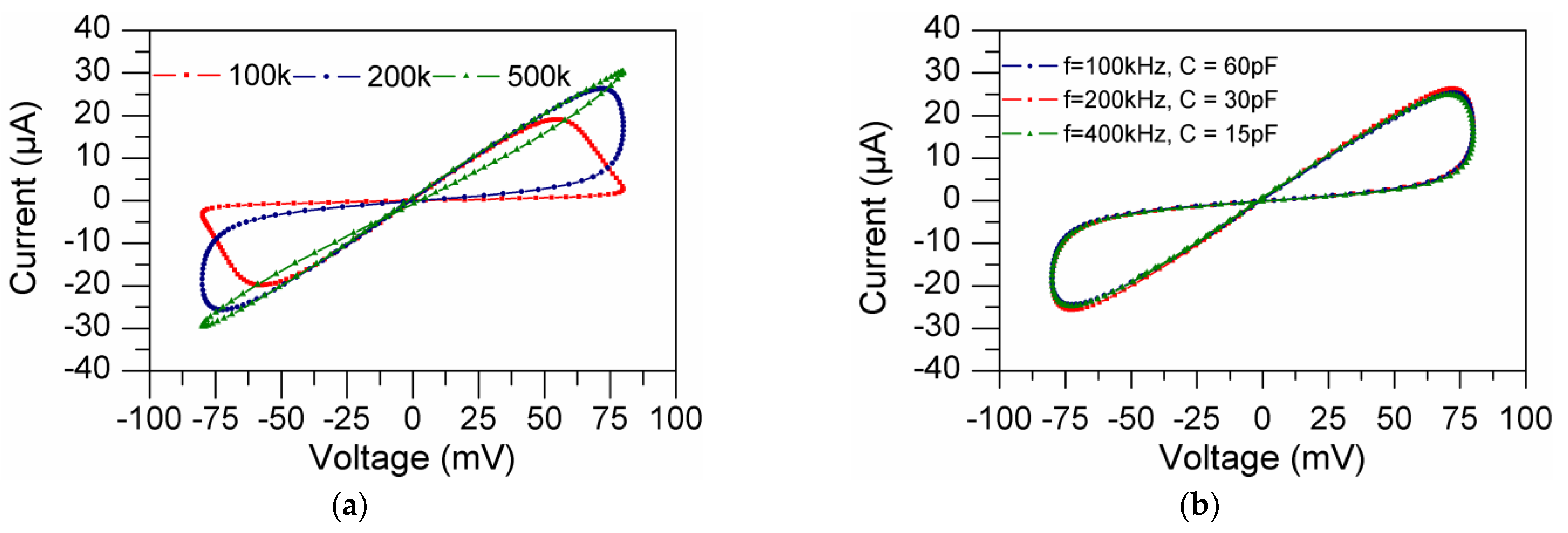

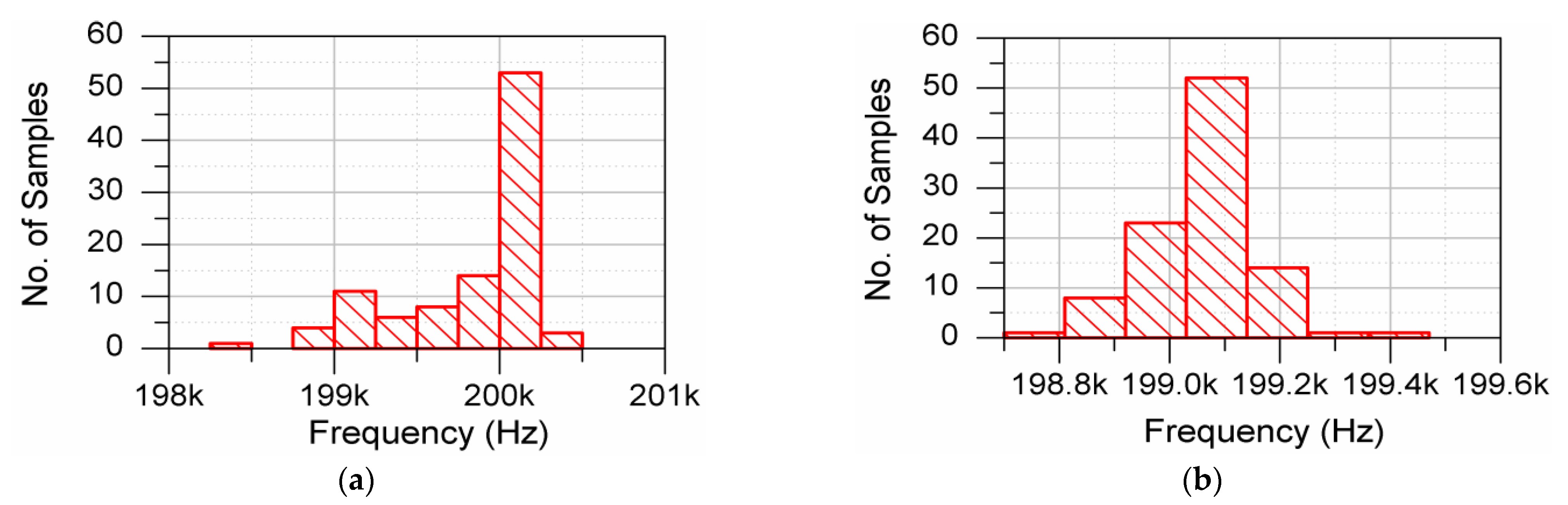

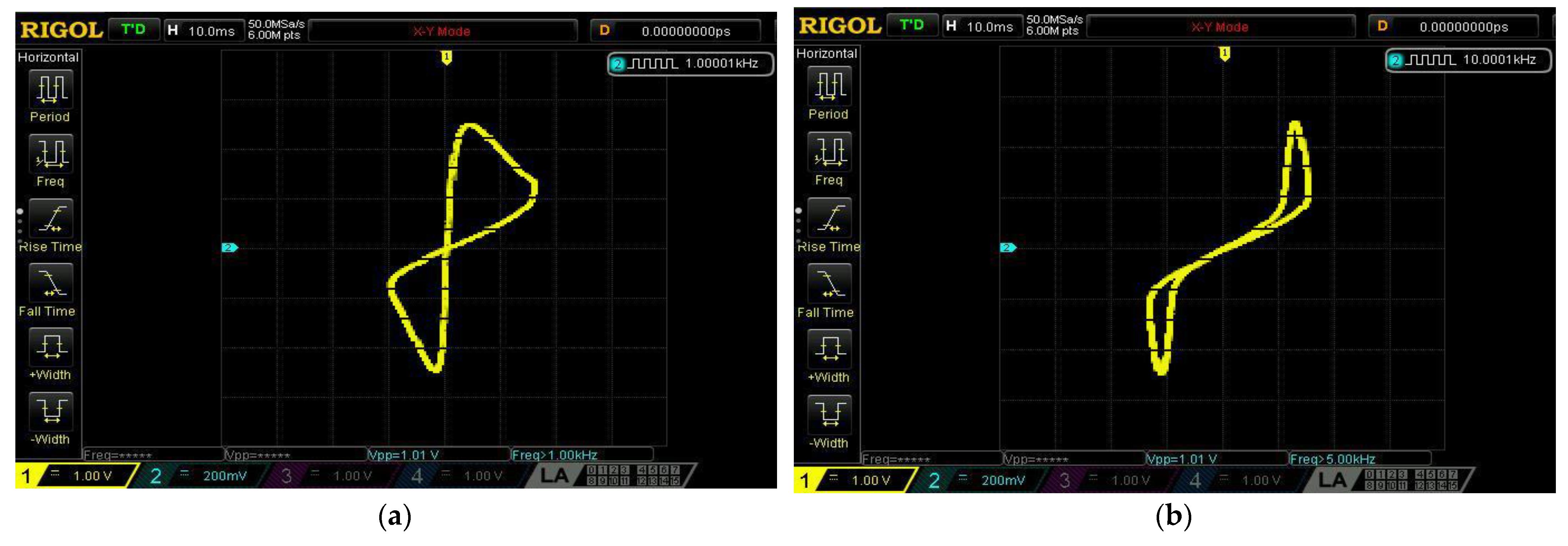

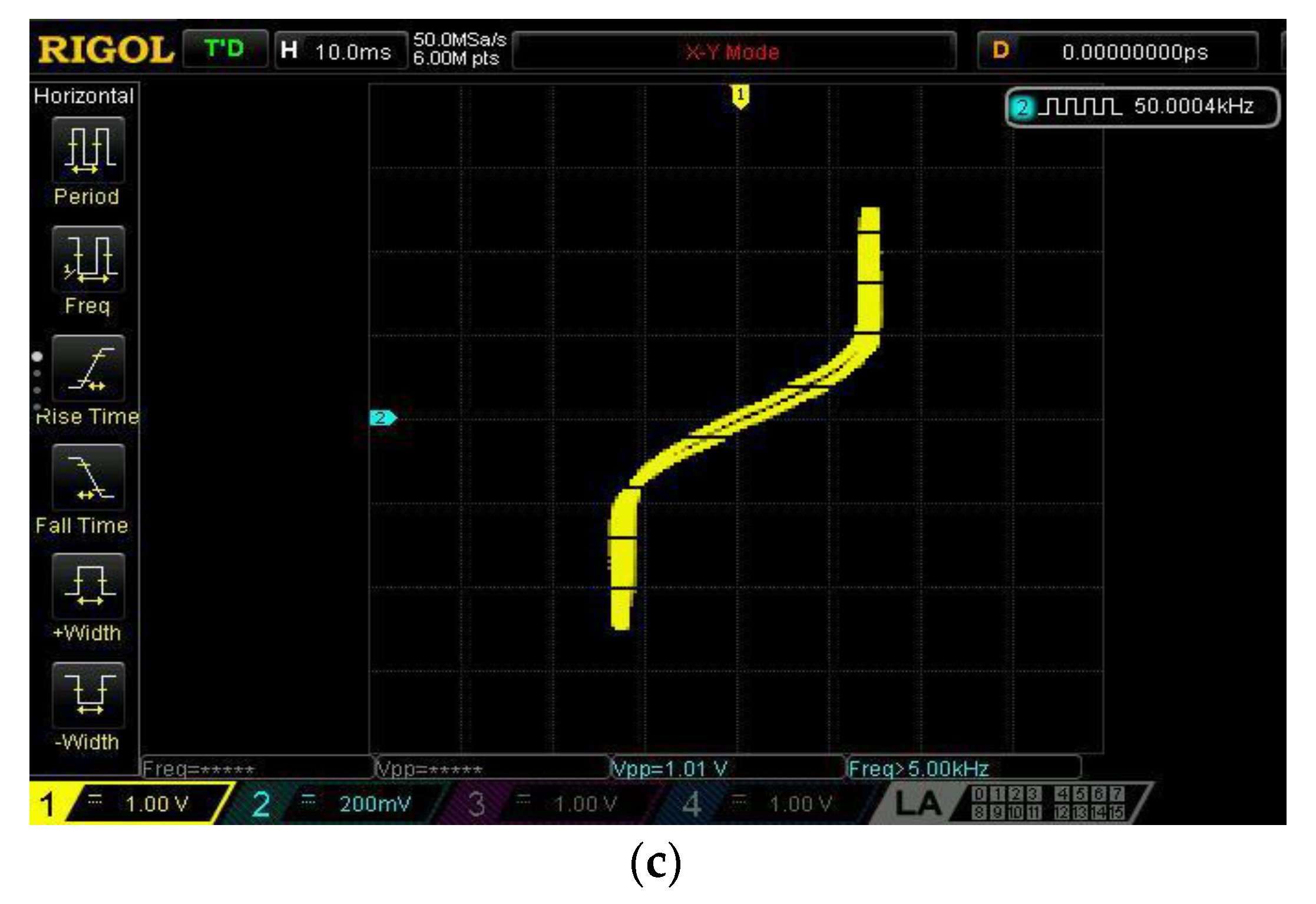

5. Simulation Results

6. Experimental Verification and Comparison

7. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Chua, L.O. Memristor-the missing circuit element. IEEE Trans. Circuit Theory 1971, 18, 507–519. [Google Scholar] [CrossRef]

- Strukov, D.B.; Snider, G.S.; Stewart, D.R.; Williams, R.S. The missing memristor found. Nat. Publ. Group 2008, 453, 80–83. [Google Scholar] [CrossRef]

- Bao, B.; Yu, J.; Hu, F.; Liu, Z. Generalized memristor consisting of diode bridge with first order parallel RC filter. Int. J. Bifurc. Chaos 2014, 24, 1450143. [Google Scholar] [CrossRef]

- Corinto, F.; Ascoli, A. Memristive diode bridge with LCR filter. Electron. Lett. 2012, 48, 824–825. [Google Scholar] [CrossRef]

- Barboni, L. A novel passive circuit emulator for a current-controlled memristor. Act. Passiv. Electron. Compon. 2021, 2021, 5582774. [Google Scholar] [CrossRef]

- Yeşil, A.; Babacan, Y.; Kaçar, F. A new DDCC based memristor emulator circuit and its applications. Microelectron. J. 2014, 45, 282–287. [Google Scholar] [CrossRef]

- Kim, H.; Sah, M.P.; Yang, C.; Cho, S.; Chua, L.O. Memristor emulator for memristor circuit applications. IEEE Trans. Circuits Syst. I Regul. Pap. 2012, 59, 2422–2431. [Google Scholar]

- Yu, D.; Iu, H.H.C.; Fitch, A.L.; Liang, Y. A floating memristor emulator based relaxation oscillator. IEEE Trans. Circuits Syst. I Regul. Pap. 2014, 61, 2888–2896. [Google Scholar] [CrossRef]

- Sánchez-López, C.; Mendoza-Lopez, J.; Carrasco-Aguilar, M.A.; Muñiz-Montero, C. A floating analog memristor emulator circuit. IEEE Trans. Circuits Syst. II Express Briefs 2014, 61, 309–313. [Google Scholar]

- Abuelma’atti, M.T.; Khalifa, Z.J. A new floating memristor emulator and its application in frequency-to-voltage conversion. Analog Integr. Circuits Signal Process. 2016, 86, 141–147. [Google Scholar] [CrossRef]

- Raj, N.; Ranjan, R.K.; Khateb, F. Flux-controlled memristor emulator and its experimental results. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2020, 28, 1050–1061. [Google Scholar] [CrossRef]

- Petrovic, P.B. Floating incremental/decremental flux-controlled memristor emulator circuit based on single VDTA. Analog Integr. Circuits Signal Process. 2018, 96, 417–433. [Google Scholar] [CrossRef]

- Cam, Z.G.; Sedef, H. A new floating memristance simulator circuit based on second generation current conveyor. J. Circuits Syst. Comput. 2017, 26, 1750029. [Google Scholar] [CrossRef]

- Yesil, A.; Babacan, Y.; Kacar, F. Electronically tunable memristor based on VDCC. AEU-Int. J. Electron. Commun. 2019, 107, 282–290. [Google Scholar] [CrossRef]

- Abuelma’atti, M.T.; Khalifa, Z.J. A new memristor emulator and its application in digital modulation. Analog Integr. Circuits Signal Process. 2014, 80, 577–584. [Google Scholar] [CrossRef]

- Sánchez-López, C.; Aguila-Cuapio, L.E. A 860 kHz grounded memristor emulator circuit. AEU-Int. J. Electron. Commun. 2017, 73, 23–33. [Google Scholar] [CrossRef]

- Babacan, Y.; Yesil, A.; Kacar, F. Memristor emulator with tunable characteristic and its experimental results. AEU-Int. J. Electron. Commun. 2017, 81, 99–104. [Google Scholar] [CrossRef]

- Umut, E.A.; Shahram, M.; Mehmet, S. Memristor emulator circuits using single CBTA. AEU-Int. J. Electron. Commun. 2017, 82, 109–118. [Google Scholar]

- Abuelma’atti, M.T.; Khalifa, Z.J. A continuous-level memristor emulator and its application in a multivibrator circuit. AEU-Int. J. Electron. Commun. 2015, 69, 771–775. [Google Scholar] [CrossRef]

- Yeşil, A.; Babacan, Y.; Kaçar, F. Design and experimental evolution of memristor with only one VDTA and one capacitor. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2018, 38, 1123–1132. [Google Scholar] [CrossRef]

- Ranjan, R.K.; Raj, N.; Bhuwal, N.; Khateb, F. Single DVCCTA based high frequency incremental/decremental memristor emulator and its application. AEU-Int. J. Electron. Commun. 2017, 82, 177–190. [Google Scholar] [CrossRef]

- Yadav, N.; Rai, S.K.; Pandey, R. New grounded and floating memristor emulators using OTA and CDBA. Int. J. Circuit Theory Appl. 2020, 48, 1154–1179. [Google Scholar] [CrossRef]

- Cam Taskiran, Z.G.; Ayten, U.E.; Sedef, H. Dual-output operational transconductance amplifier-based electronically controllable memristance simulator circuit. Circuits Syst. Signal Process. 2019, 38, 26–40. [Google Scholar] [CrossRef]

- Elwakil, A.S.; Fouda, M.E.; Radwan, A.G. A simple model of double-loop hysteresis behavior in memristive elements. IEEE Trans. Circuits Syst. II Express Briefs 2013, 60, 487–491. [Google Scholar] [CrossRef]

- Gupta, S.; Rai, S.K. New grounded and floating decremental/incremental memristor emulator circuits based on CDTA and its application. Wirel. Pers. Commun. 2020, 113, 773–798. [Google Scholar] [CrossRef]

- Bhardwaj, K.; Srivastava, M. New electronically adjustable memelement emulator for realizing the behaviour of fully-floating meminductor and memristor. Microelectron. J. 2021, 114, 105126. [Google Scholar] [CrossRef]

- Raj, A.; Singh, S.; Kumar, P. Dual mode, high frequency and power efficient grounded memristor based on OTA and DVCC. Analog Integr. Circuits Signal Process. 2022, 110, 81–89. [Google Scholar] [CrossRef]

- Yadav, N.; Rai, S.K.; Pandey, R. Novel memristor emulators using fully balanced VDBA and grounded capacitor. Iran. J. Sci. Technol. Trans. Electr. Eng. 2021, 45, 229–245. [Google Scholar] [CrossRef]

- Sharma, P.K.; Prasad, S.S.; Tasneem, S.; Priyadarshini, B.; Ranjan, R.K. Resistive tunable memristor emulator model and its application. AEU-Int. J. Electron. Commun. 2023, 160, 154500. [Google Scholar] [CrossRef]

- Bhardwaj, K.; Srivastava, M. Compact floating dual memelement emulator employing VDIBA and OTA: A novel realization. Circuits Syst. Signal Process. 2022, 41, 5933–5967. [Google Scholar] [CrossRef]

- Suresha, B.; Shankar, C.; Rudraswamy, S.B. A floating memristor emulator for analog and digital applications with experimental results. Analog Integr. Circuits Signal Process. 2024, 118, 77–90. [Google Scholar] [CrossRef]

- Bhardwaj, K.; Srivastava, M. New multiplier-less compact tunable charge-controlled memelement emulator using grounded passive elements. Circuits Syst. Signal Process. 2022, 41, 2429–2465. [Google Scholar] [CrossRef]

- Romero, F.J.; Ohata, A.; Toral-Lopez, A.; Godoy, A.; Morales, D.P.; Rodriguez, N. Memcapacitor and meminductor circuit emulators: A review. Electronics 2021, 10, 1225. [Google Scholar] [CrossRef]

- Petrović, P.B. Electronically adjustable grounded memcapacitor emulator based on single active component with variable switching mechanism. Electronics 2022, 11, 161. [Google Scholar] [CrossRef]

- Romero, F.J.; Escudero, M.; Medina-Garcia, A.; Morales, D.P.; Rodriguez, N. Meminductor emulator based on a modified Antoniou’s gyrator circuit. Electronics 2020, 9, 1407. [Google Scholar] [CrossRef]

- Yesil, A.; Babacan, Y.; Kacar, F. A new floating memristor based on CBTA with grounded capacitors. J. Circuits Syst. Comput. 2019, 28, 1950217. [Google Scholar] [CrossRef]

- Kumar, A.; Chaturvedi, B.; Jagga, S. New CMOS compatible realizations of grounded/floating L, C multiplier and FDNC simulators. Circuits Syst. Signal Process. 2023, 42, 1911–1939. [Google Scholar] [CrossRef]

- Chaturvedi, B.; Kumar, A. A novel electronically controlled Schmitt trigger with clockwise and anticlockwise hystereses. AEU-Int. J. Electron. Commun. 2018, 89, 136–145. [Google Scholar] [CrossRef]

- Chaturvedi, B.; Kumar, A. High CMRR current-mode instrumentation amplifier for low voltage and low power applications. AEU-Int. J. Electron. Commun. 2019, 104, 147–154. [Google Scholar] [CrossRef]

- Kumar, A.; Chaturvedi, B.; Mohan, J. Minimal realizations of integrable memristor emulators. J. Comput. Electron. 2023, 22, 504–518. [Google Scholar] [CrossRef]

| MOSFET | W/L |

|---|---|

| M1–M3, M17–M19 | 4.5 µm/0.36 µm |

| M4, M5 | 22.5 µm/0.36 µm |

| M6, M7 | 5 µm/0.36 µm |

| M8, M9 | 15 µm/0.36 µm |

| M10, M11 | 7.5 µm/0.36 µm |

| M12–M14, M20–M22 | 1.5 µm/0.36 µm |

| M15, M16 | 30 µm/0.18 µm |

| M23–M27 | 3.6 µm/1.8 µm |

| M28, M29, M32 | 7.2 µm/1.8 µm |

| M30, M31,M33 | 2.4 µm/1.8 µm |

| Ref. | Count of Active Components | Passive Components/Count | All Grounded Passive Components | Incremental/Decremental | Floating (F)/Grounded (G) Structure | Supply Voltages (V) | Operational Frequency | Sim/Exp Results |

|---|---|---|---|---|---|---|---|---|

| 6 | 1 DDCC, 1 Multiplier | R/2, C/1 | No | Both | F | ±1.5 | 1 MHz | Sim |

| 7 | 5 OPAMP, 1 Multiplier, 10 MOSFET | R/8, C/1 | No | Both | F | ±5 | 800 Hz | Both |

| 8 | 4 AD844, 1 AD633, 1 OPAMP | R/8, C/1 | No | Decremental | F | ±15 | 120 Hz | Exp |

| 9 | 4 AD844, 1 AD633 | R/5, C/1 | No | Both | F | ±10 | 20.2 kHz | Both |

| 10 | 4 CFOA, 2 D | R/4, C/4 | No | Incremental | F | NA | 6 kHz | Exp |

| 11 | 1 CCII, 1 OTA | R/1, C/1 | Yes | Both | G | ±1.2 | 26.3 MHz | Both |

| 12 | 1 VDTA, 1 Multiplier | R/2, C/1 | Yes | Both | F | ±0.9 | 2 MHz | Both |

| 13 | 4 CCII, 1 Multiplier | R/3, C/1 | No | Both | F | ±10 | 40 kHz | Both |

| 14 | 1 VDCC, 2 MOSFET | C/1 | Yes | Both | G | ±0.9 | 2 MHz | Both |

| 15 | 3 CFOA (AD844), 1 D | R/4, C/2 | No | Both | G | NA | 700 Hz | Exp |

| 16 | 1 AD844, 1 Multiplier (AD633) | R/1, C/1 | No | Both | G | ±10 | 860 kHz | Both |

| 17 | 1 MO-OTA, 1 Multiplier | R/1, C/1 | Yes | Both | G | ±1.25 | 5 kHz | Both |

| 18 | 1 CBTA,1 Multiplier | R/2, C/1 | No | Both | G | ±0.9 | 460 kHz | Sim |

| 19 | 2 CFOA, 1 OTA | R/3, C/2 | Yes | Decremental | G | ±12 | 600 Hz | Exp |

| 20 | 1 VDTA | MOS-C/1 | Yes | Both | G | ±0.9 | 50 MHz | Both |

| 21 | 1 DVCCTA | R/3, C/1 | No | Both | G | ±1.25 | 1 MHz | Sim |

| 22 | 1 CDBA, 1 OTA | C/1 | Yes | Both | Both | ±0.9 | 1 MHz | Sim |

| 23 | 2 OTA, 1 Multiplier | R/1, C/1 | Yes | Both | F | ±1.5 | 180 kHz | Both |

| 24 | 2 CCII, 1 Multiplier, 1 Buffer | R/3, C/1 | No | Both | G | ±10 | 100 kHz | Both |

| 25 | 1 CDTA, 1 OTA | C/1 | Yes | Both | Both | ±0.9 | 2 MHz | Sim |

| 26 | 2 VDTA | R/1, C/1 | Yes | Both | F | ±0.9 | 1.5 MHz | Sim |

| 27 | 1 OTA, 1 DVCC | R/1, C/1 | Yes | Both | G | ±1.2 | 1 MHz | Sim |

| 28 | 1 FB-VDBA | C/1 | Yes | Both | Both | ±0.9 | 1 MHz | Sim |

| 29 | 1 DVCC, 1 OTA | R/1, C/1 | Yes | Both | G | ±0.9 | 30 MHz | Both |

| 30 | 1 VDIBA, 1 OTA, 2 MOS | R/1, C/1 | Yes | Both | F | ±1 | 8 MHz | Both |

| 31 | 1 OPAMP, 1 MOSFET | R/5, C/1 | No | Both | Both | ±1.5 | 20 kHz | Both |

| 32 | 1 VDCC, 1 OTA | R/2, C/1 | Yes | Incremental | G | --- | 1 MHz | Both |

| This work | 1 CBTA | C/1 | Yes | Both | Both | ±1 | 2 MHz | Both |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kumar, A.; Chaturvedi, B. A High-Quality and Space-Efficient Design for Memristor Emulation. Electronics 2024, 13, 3331. https://doi.org/10.3390/electronics13163331

Kumar A, Chaturvedi B. A High-Quality and Space-Efficient Design for Memristor Emulation. Electronics. 2024; 13(16):3331. https://doi.org/10.3390/electronics13163331

Chicago/Turabian StyleKumar, Atul, and Bhartendu Chaturvedi. 2024. "A High-Quality and Space-Efficient Design for Memristor Emulation" Electronics 13, no. 16: 3331. https://doi.org/10.3390/electronics13163331