Estimation of Void Area and Position in Solder Layer of Power Semiconductor Devices Based on Temperature Distribution Characteristics

Abstract

:1. Introduction

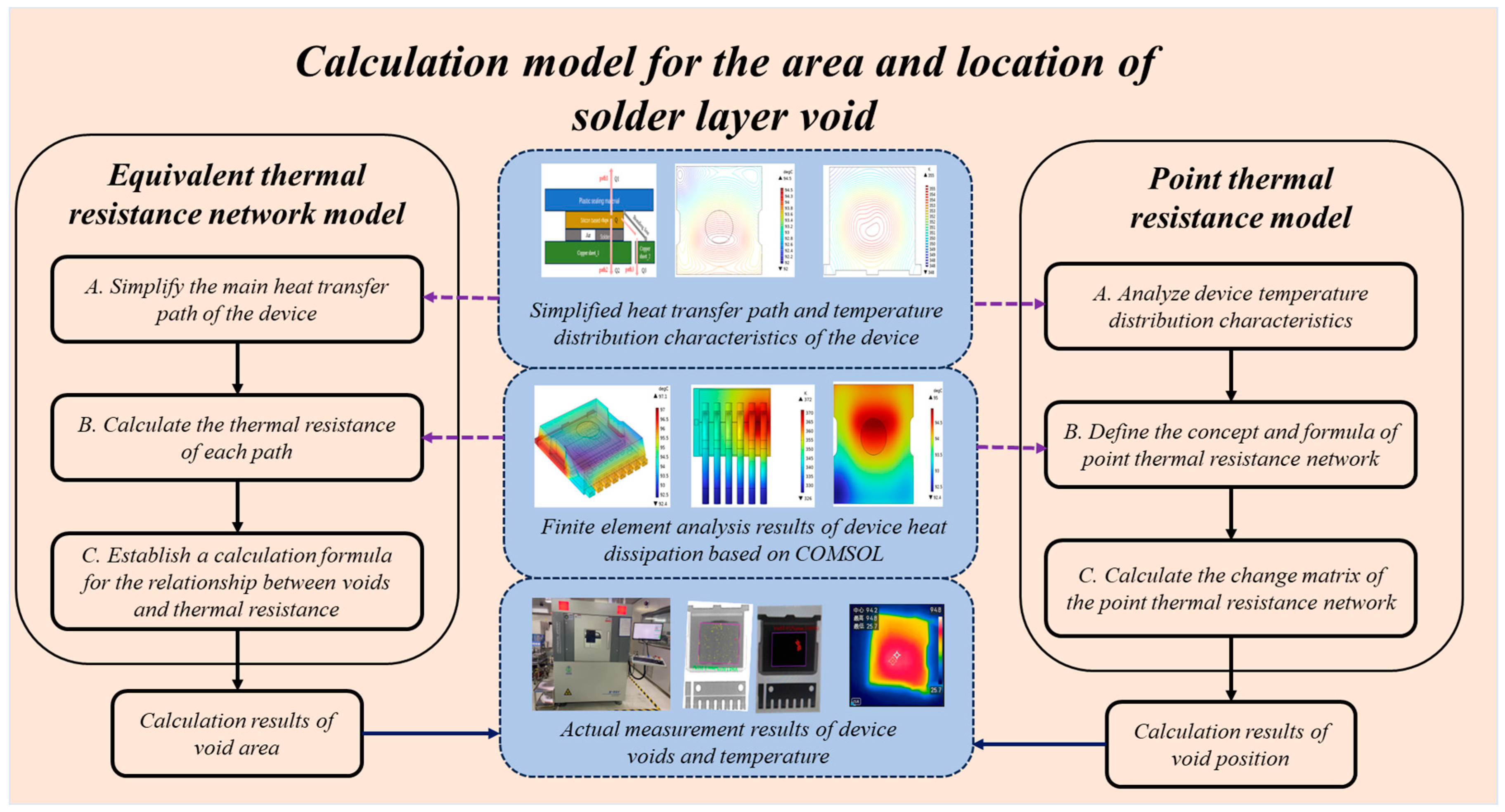

2. Void Area Calculation Model and Localization Model

2.1. Modeling Process

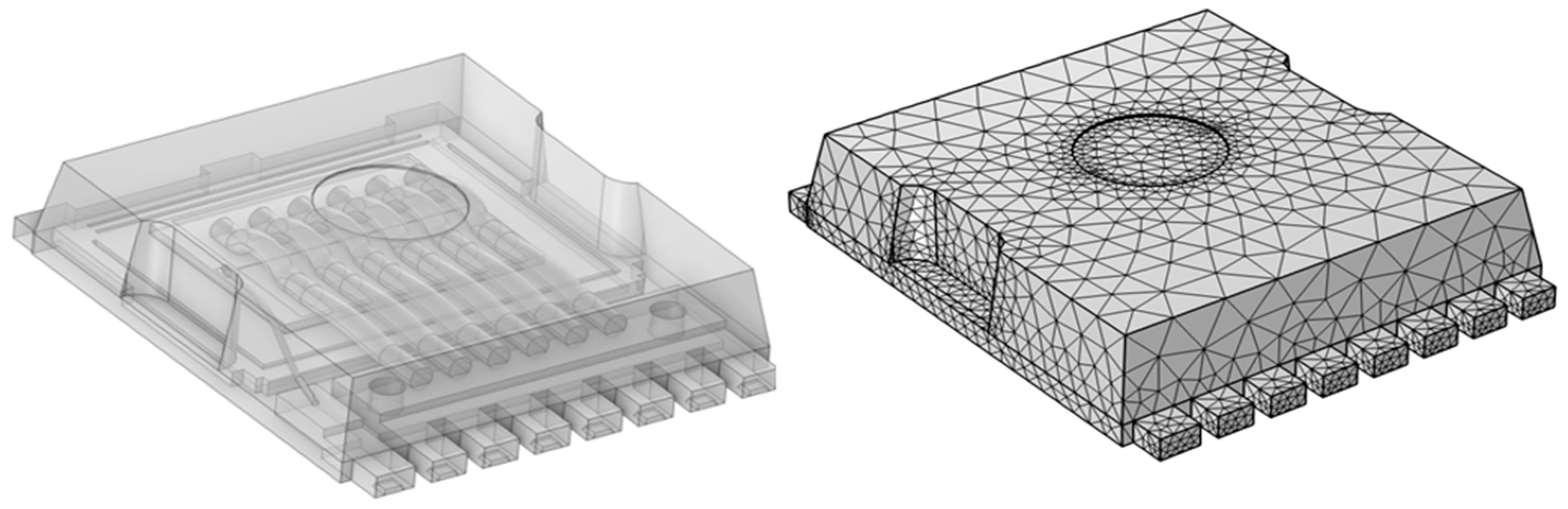

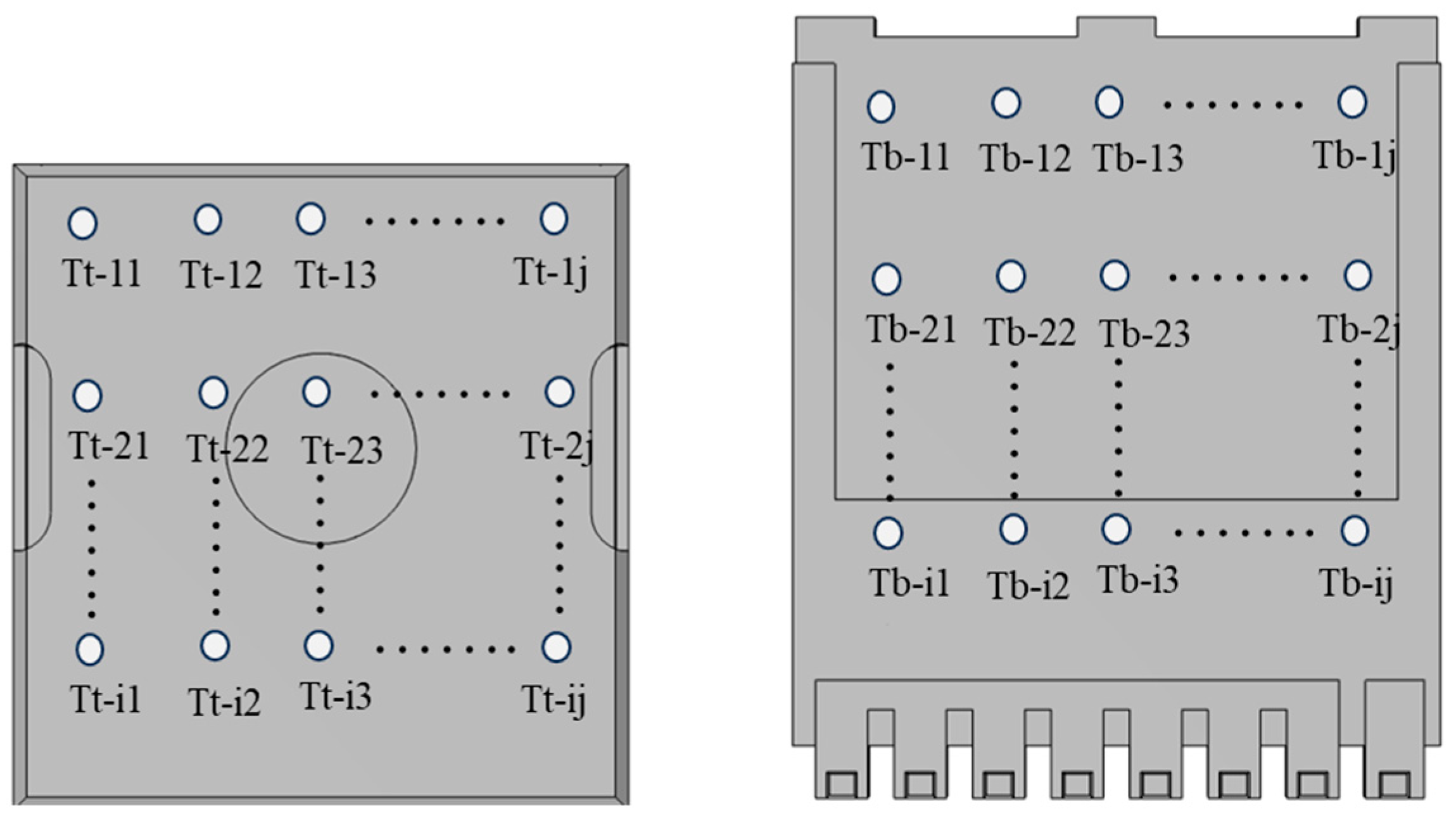

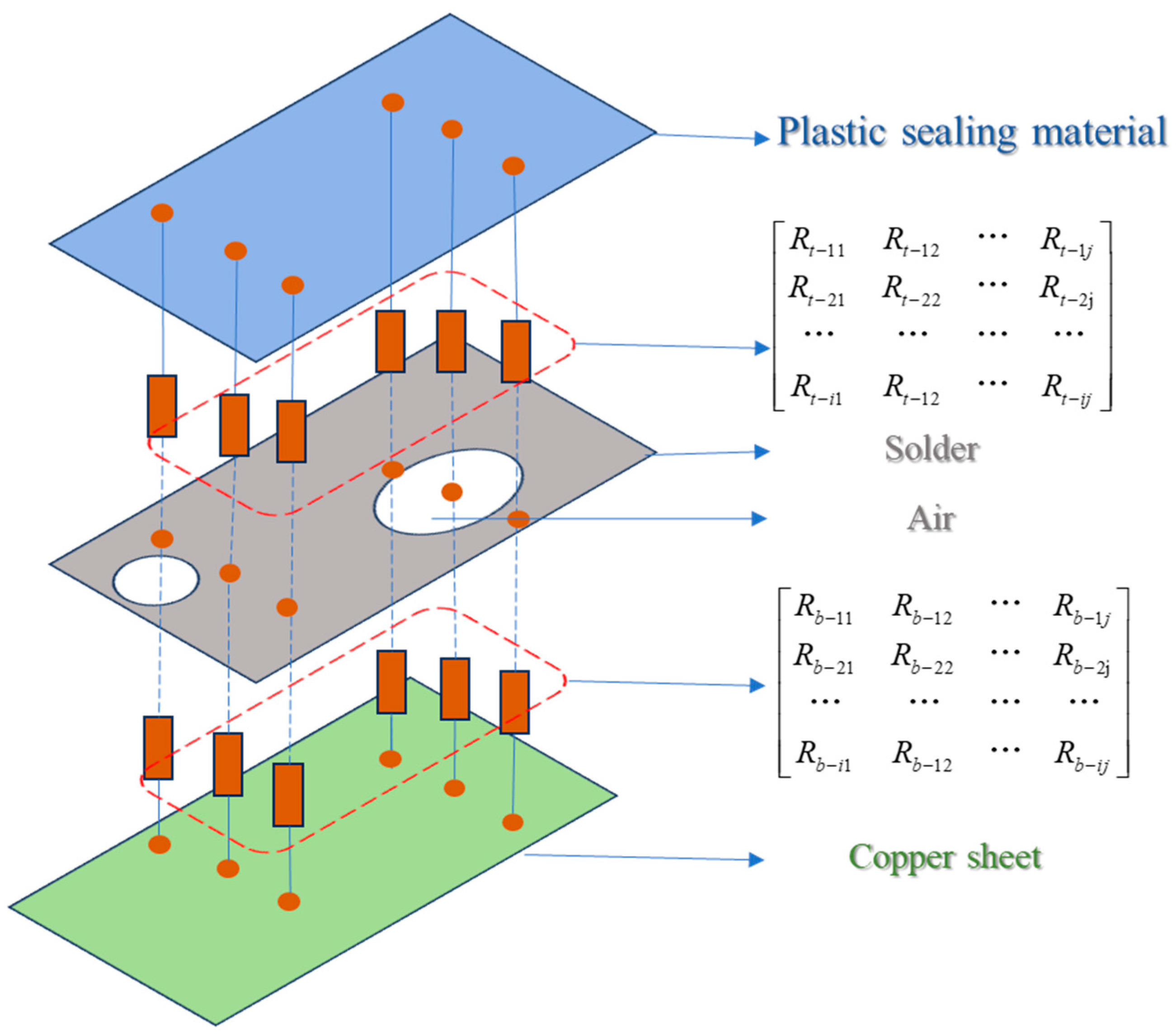

2.1.1. Finite Element Heat Transfer Thermal Calculation Model

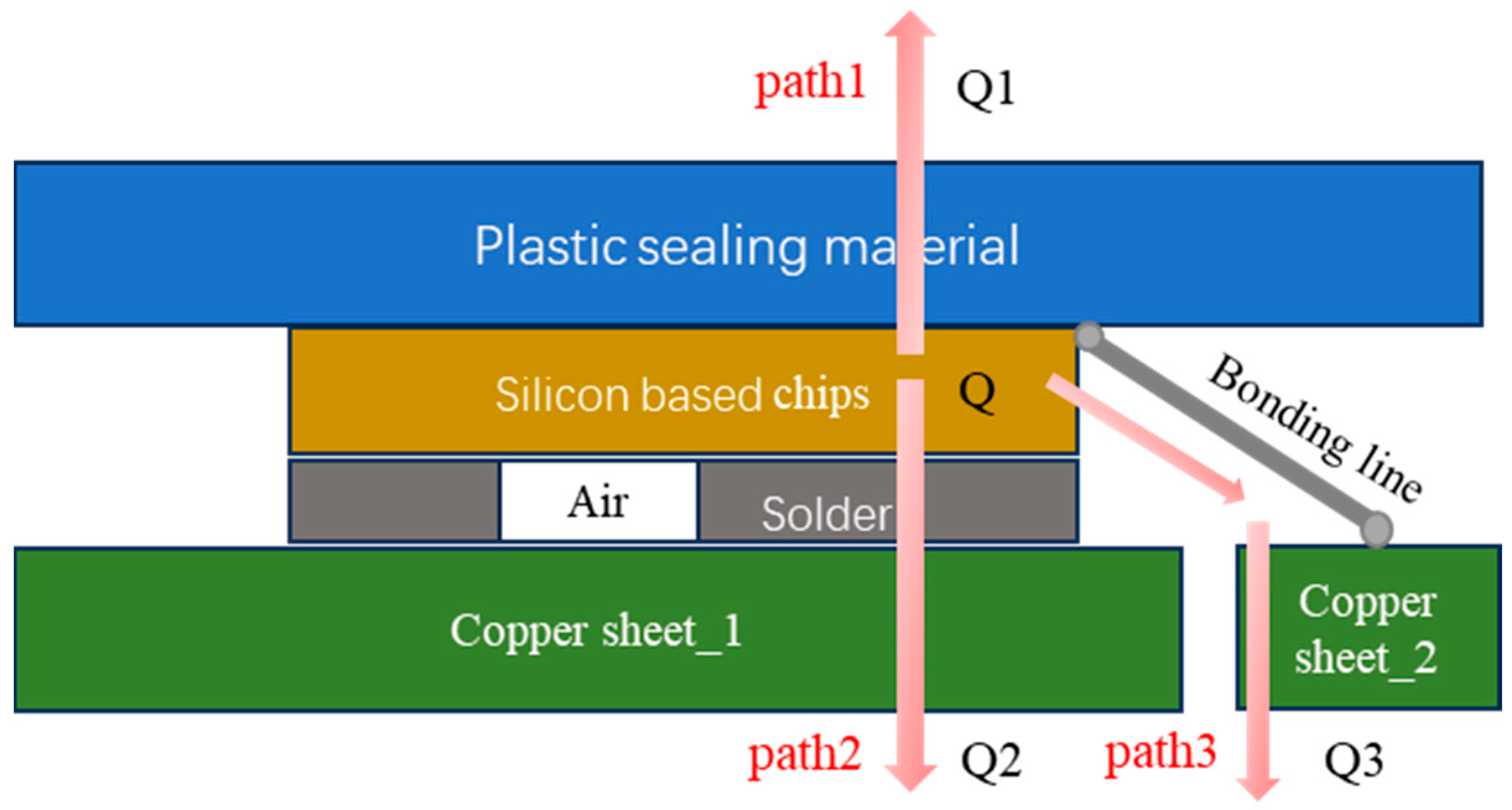

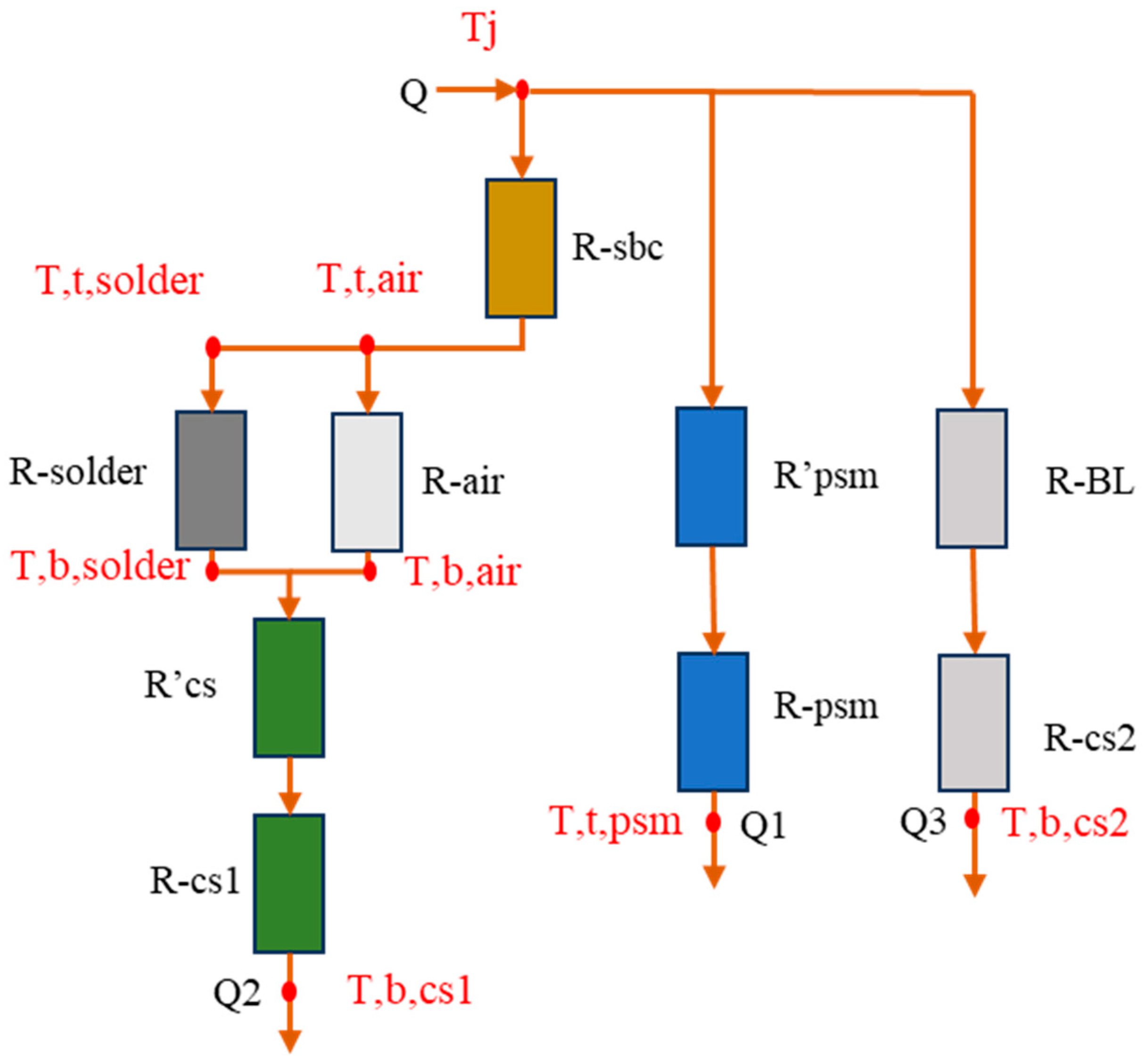

2.1.2. Equivalent Thermal Resistance Model Based on Major Heat Flow Paths

2.1.3. Calculation Model of Void Location Based on Point Thermal Resistance Network

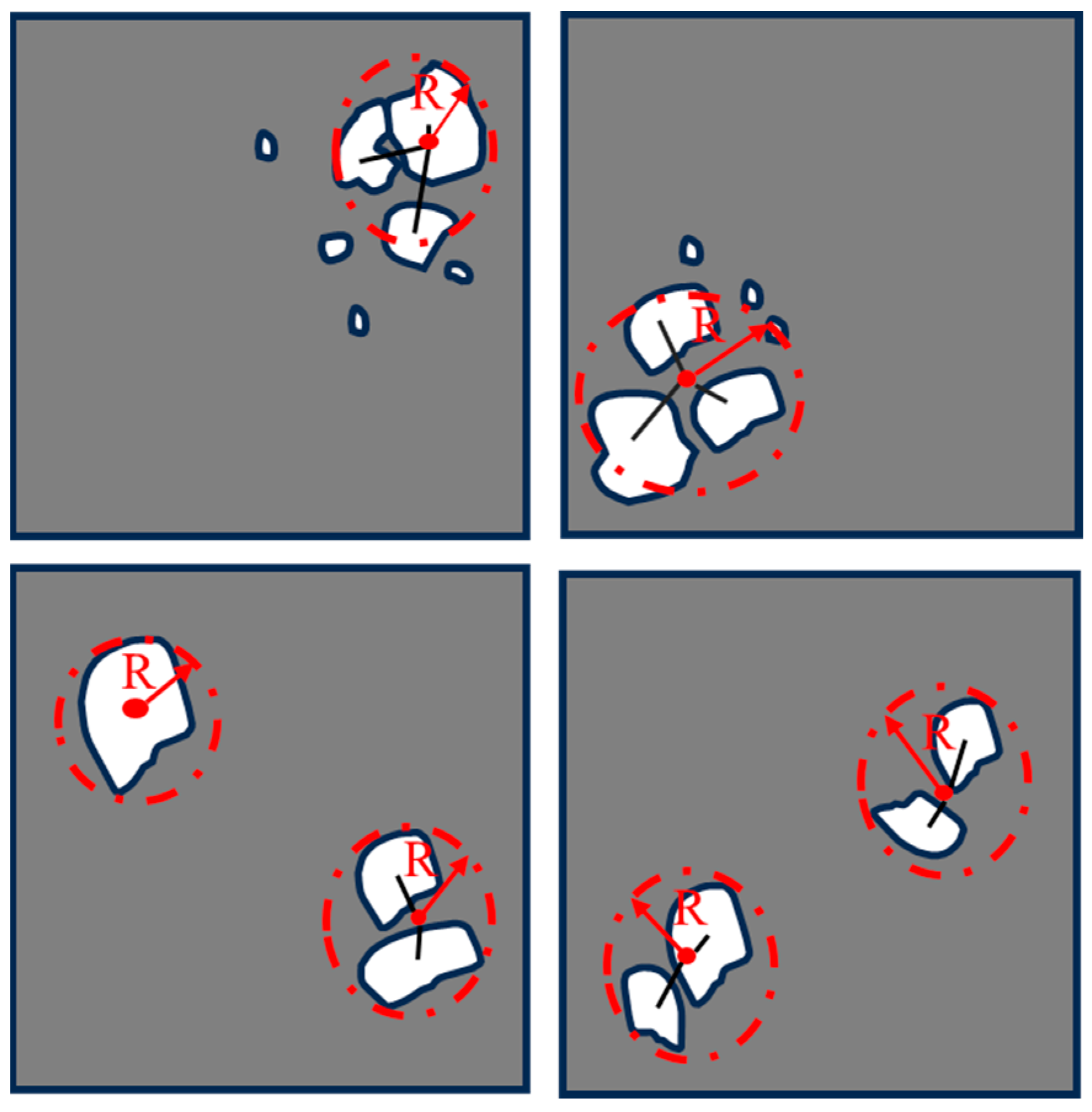

2.1.4. Equivalent Calculation of Area and Location of Solder Layer Voids

2.2. Simulation Results and Discussion

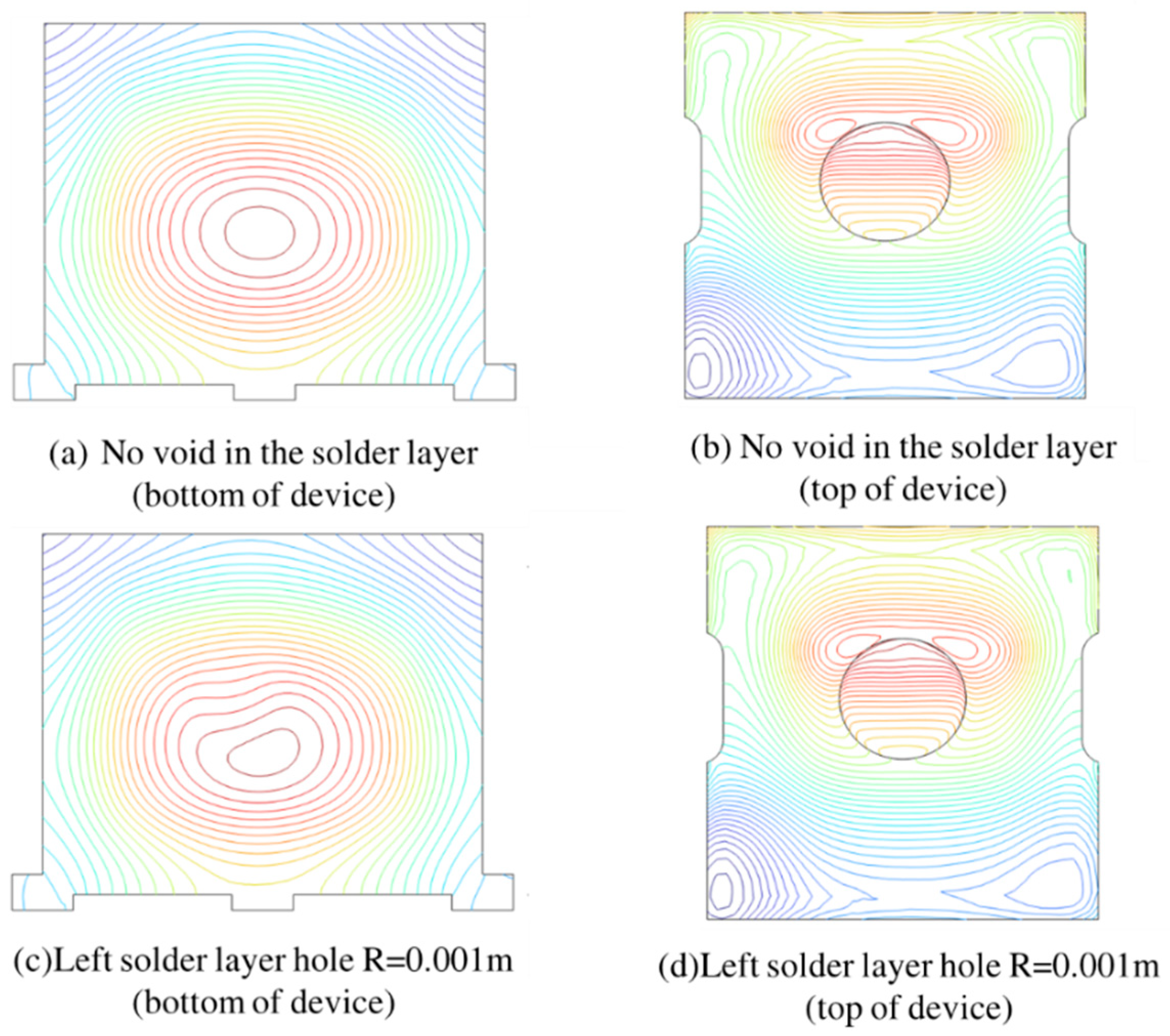

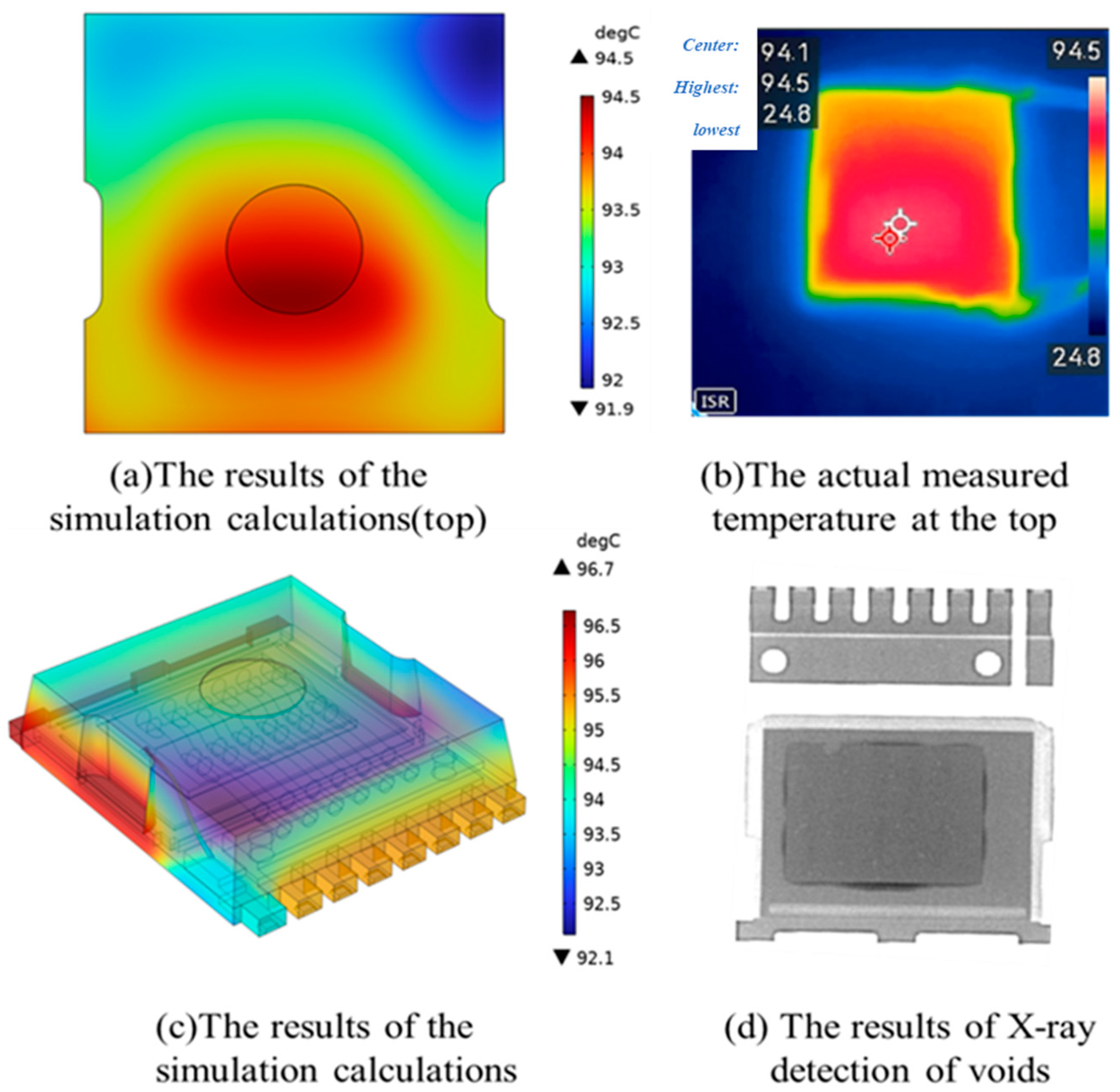

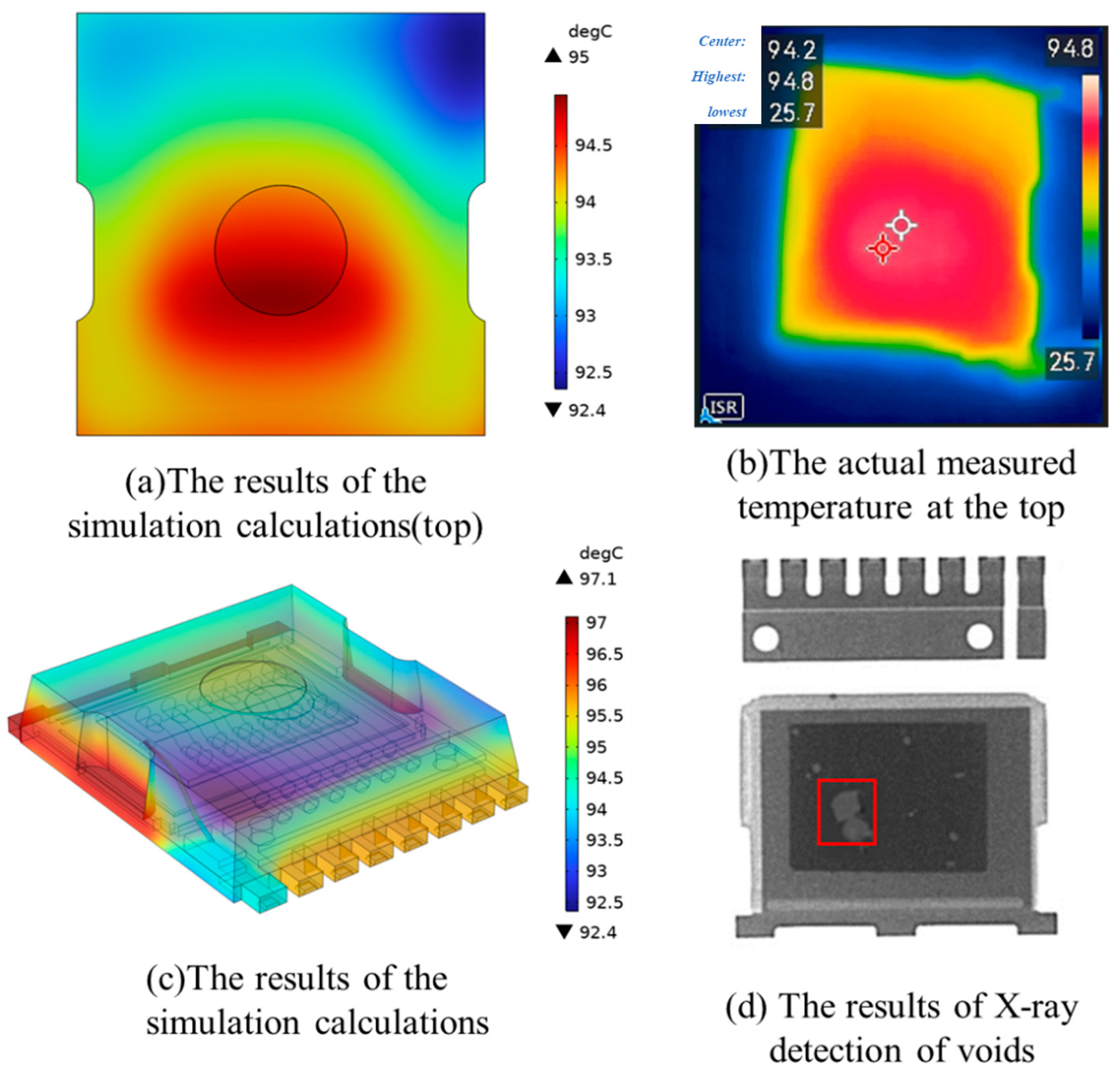

Effect of Voids on Device Temperature Distribution

2.3. Effect of Voids on Thermal Resistance of Heat Transfer Paths

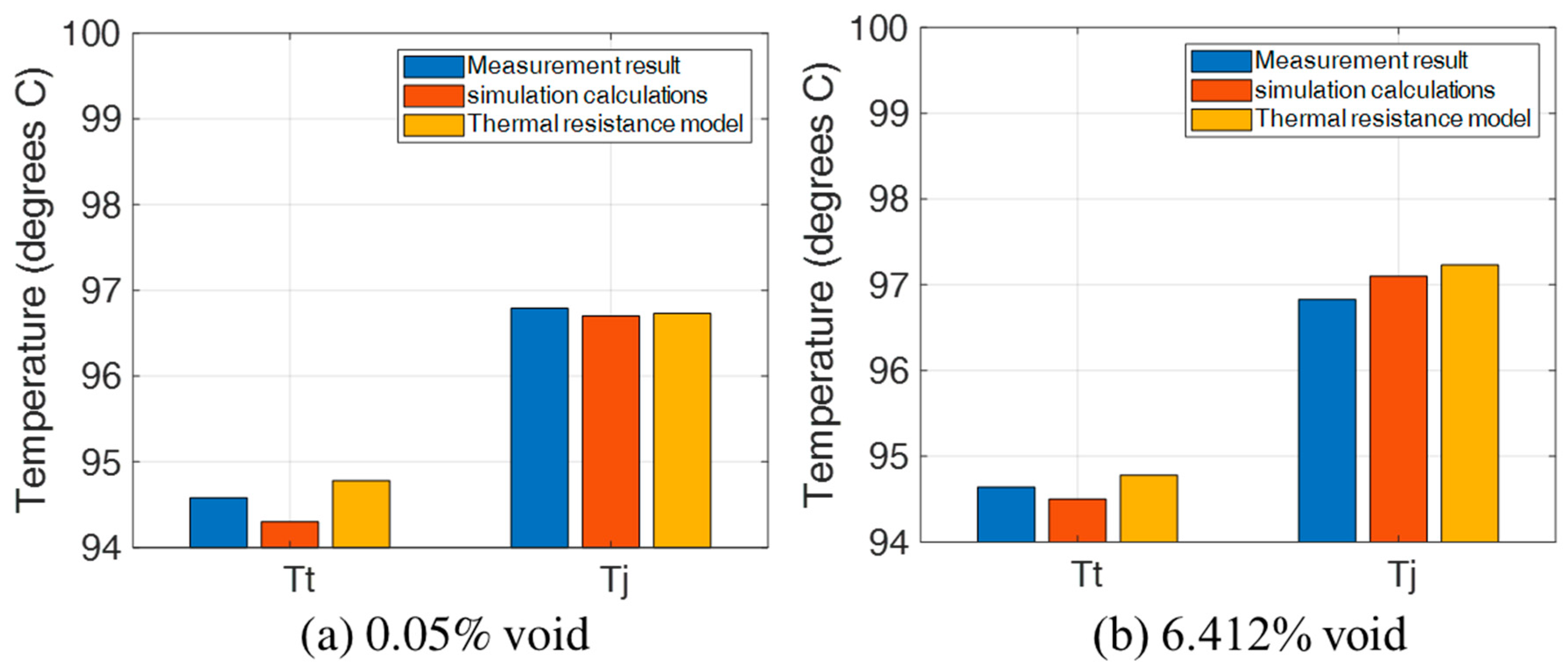

3. Comparison between Measurement Results and Calculation Results

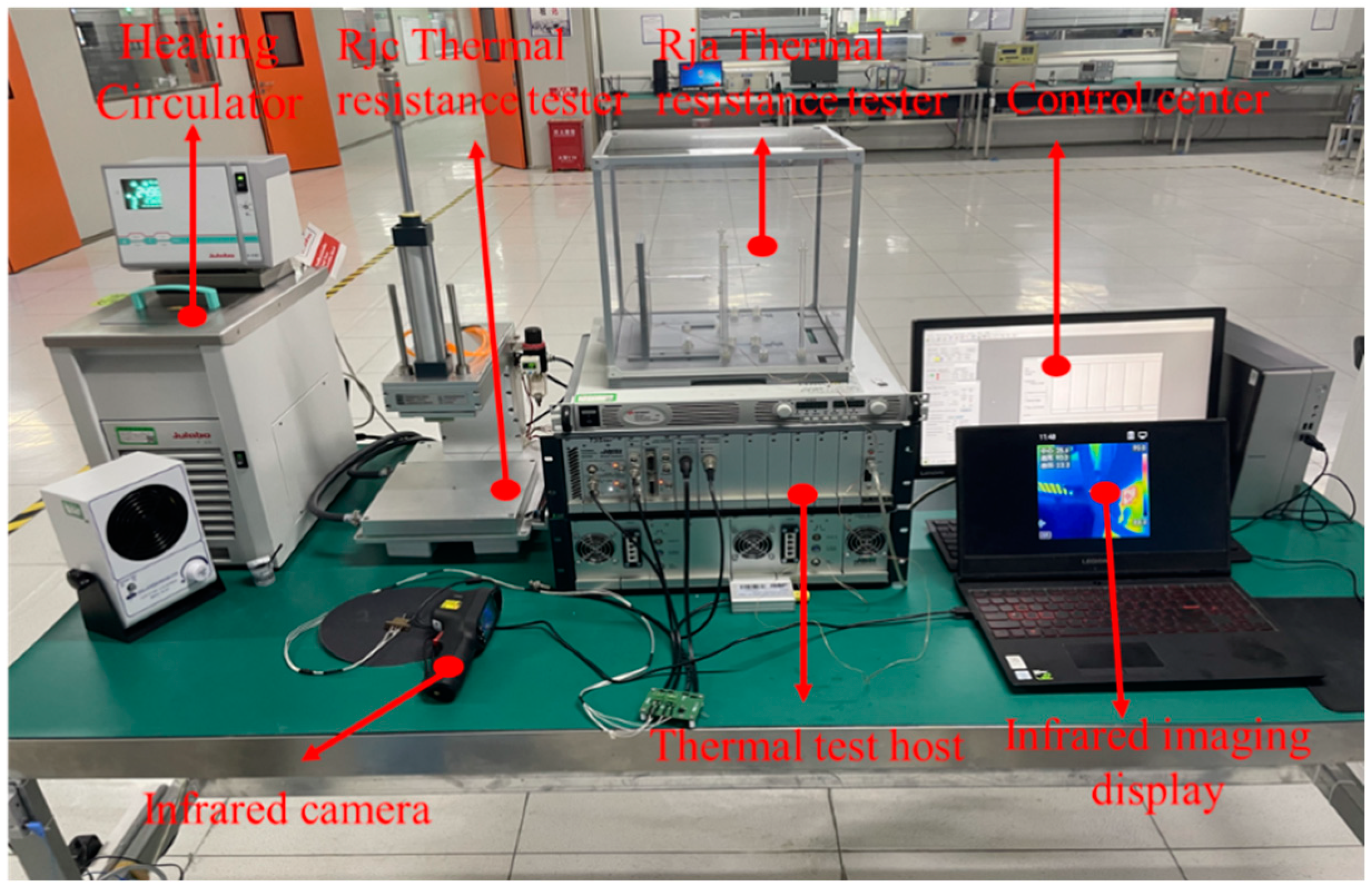

Experimental Platform for X-ray Void Rate Detection

4. Results and Discussion

- The thermal resistance of the device is basically unaffected by the location of the solder layer voids, while the area of the solder layer voids has a greater impact on the thermal resistance; the voids are in the range of 5–25%, and the area of the voids is positively and linearly correlated with the thermal resistance of the heat dissipation paths.

- The voids in the solder layer lead to an increase in the thermal resistance of the main heat dissipation paths inside the device and to the accumulation of heat at the location of the voids.

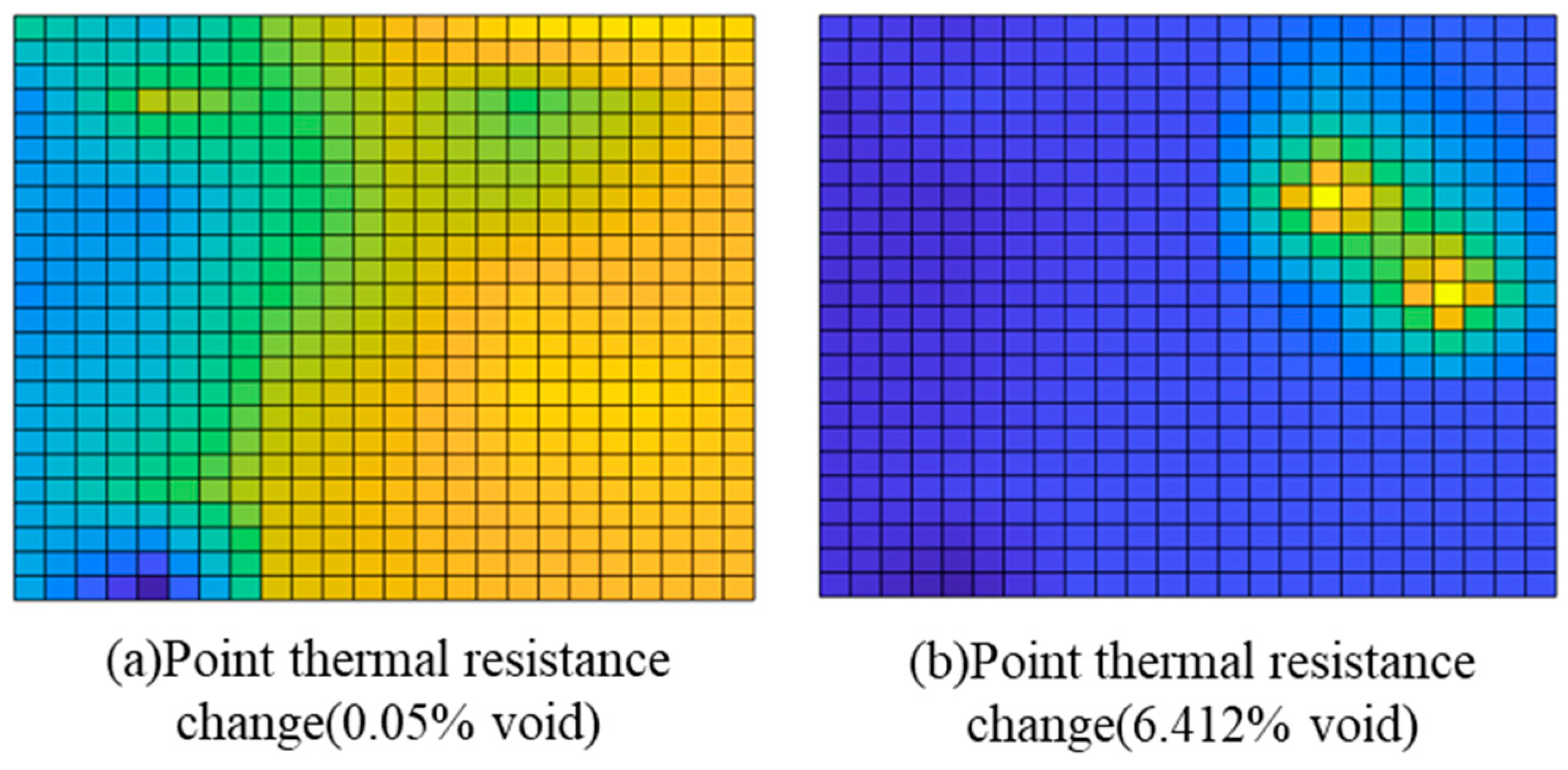

- The maximum value of the point thermal resistance change matrix is the center of the void, and the approximate extent of the void can be determined by the range in which the matrix change occurs.

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Alatise, O.; Deb, A.; Bashar, E.; Ortiz Gonzalez, J.; Jahdi, S.; Issa, W. A Review of Power Electronic Devices for Heavy Goods Vehicles Electrification: Performance and Reliability. Energies 2023, 16, 4380. [Google Scholar] [CrossRef]

- Aharon, I.; Kuperman, A. Topological overview of powertrains for battery-powered vehicles with range extenders. IEEE Trans. Power Electron. 2011, 3, 868–876. [Google Scholar] [CrossRef]

- Scheuermann, U. Reliability challenges of automotive power electronics. Microelectron. Reliab. 2009, 49, 1319–1325. [Google Scholar] [CrossRef]

- Quintero, P.O.; McCluskey, F.P. Temperature cycling reliability of high-temperature lead-free die-attach technologies. IEEE Trans. Device Mater. Reliab. 2011, 11, 531–539. [Google Scholar] [CrossRef]

- Li, Y.; Fu, G.; Wan, B.; Wu, Z.; Yan, X.; Zhang, W. A study on the effects of electrical and thermal stresses on void formation and migration lifetime of Sn3.0Ag0.5Cu solder joints. Solder. Surf. Mt. Technol. 2022, 3, 162–173. [Google Scholar] [CrossRef]

- Lu, Y.; Christou, A. Lifetime estimation of insulated gate bipolar transistor modules using two-step bayesian estimation. IEEE Trans. Device Mater. Reliab. 2017, 17, 414–421. [Google Scholar] [CrossRef]

- Cui, H.; Zhou, M.; Yang, C.; Li, J.; Wang, C. Influence mechanism of solder aging and thermal network model optimization of multi-chip IGBT modules. Microelectron. Reliab. 2022, 139, 114827. [Google Scholar] [CrossRef]

- Huang, Y.; Luo, Y.; Xiao, F.; Liu, B.; Tang, X. Temporal and spatial differences in thermal transfer behavior of IGBTs caused by the baseplate and die-attach solder cracking. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 10, 7177–7187. [Google Scholar] [CrossRef]

- Jia, Y.; Huang, Y.; Xiao, F.; Deng, H.; Duan, Y.; Iannuzzo, F. Impact of solder degradation on Vce of IGBT module: Experiments and modeling. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 10, 4536–4545. [Google Scholar] [CrossRef]

- Frede, B.; Marco, L.; Ma, K. Power electronics converters forwind turbine systems. IEEE Trans. Ind. Appl. 2012, 48, 708–719. [Google Scholar]

- Otiaba, K.C.; Bhatti, R.S.; Ekere, N.N.; Mallik, S.; Alam, M.O.; Amalu, E.H.; Ekpu, M. Numerical study on thermal impacts of different void patterns on performance of chip-scale packaged power device. Microelectron. Reliab. 2012, 12, 1409–1419. [Google Scholar] [CrossRef]

- Du, M.; Guo, Q.; Wang, H.; Ouyang, Z.; Wei, K. An improved cauer model of IGBT module: Inclusive void fraction in solder layer. IEEE Trans. Compon. Packag. Manuf. Technol. 2020, 10, 1401–1410. [Google Scholar] [CrossRef]

- Okereke, M.I.; Ling, Y. A computational investigation of the effect of three-dimensional void morphology on the thermal resistance of solder thermal interface materials. Appl. Therm. Eng. 2018, 142, 346–360. [Google Scholar] [CrossRef]

- Kenny, C.; Okereke, M.I.; Bhatti, R.S. Numerical assessment of the effect of void morphology on thermo-mechanical performance of solder thermal interface material. Appl. Therm. Eng. 2014, 64, 51–63. [Google Scholar]

- Li, Q.; Zhang, F.; Chen, Y.; Fu, T.; Zheng, Z. A junction temperature model based on heat flow distribution in an IGBT module with solder layer voids. Heliyon 2024, 10, 25–33. [Google Scholar] [CrossRef] [PubMed]

- Li, H.; Hu, Y.; Liu, S.; Li, Y.; Liao, X.; Liu, Z. An improved thermal network model of the IGBT module for wind power converters considering the effects of base-plate solder fatigue. IEEE Trans. Device Mater. Reliab. 2016, 16, 570–575. [Google Scholar] [CrossRef]

- Fan, Y.; Cui, H.; Lou, Z.; Teng, J.; Tang, Z.; Peng, J. Base solder voids identification of IGBT modules using case temperature. Microelectron. Reliab. 2020, 115, 113968. [Google Scholar] [CrossRef]

- Kim, K.S.; Huh, S.H.; Suganuma, K. Effects of cooling speed on microstructure and tensile properties of Sn–Ag–Cu alloys. Mater. Sci. Eng. 2002, 333, 106–114. [Google Scholar] [CrossRef]

- Amalu, E.H.; Ekere, N.N. Modelling evaluation of GarofaloArrhenius creep relation for lead-free solder joints in surface mount electronic component assemblies. J. Manuf. Syst 2016, 39, 9–23. [Google Scholar] [CrossRef]

- Wang, C.; He, Y.; Wang, C.; Li, L.; Wu, X. Multi-Chip IGBT Module Failure Monitoring Based on Module Transconductance with Temperature Calibration. Electronics 2020, 9, 1599. [Google Scholar] [CrossRef]

- Samavatian, V.; Iman-Eini, H.; Avenas, Y.; Samavatian, M. Effects of creep failure mechanisms on thermomechanical reliability of solder joints in power semiconductors. IEEE Trans. Power Electron. 2020, 35, 8956–8964. [Google Scholar] [CrossRef]

- Hu, B.; Konaklieva, S.; Kourra, N.; Williams, M.A.; Ran, L.; Lai, W. Long-term reliability evaluation of power modules with low amplitude thermomechanical stresses and initial defects. IEEE J. Emerg. Sel. Top. Power Electron. 2021, 9, 602–615. [Google Scholar] [CrossRef]

- Liu, Y.; Jia, L.; Wang, L.; Wang, J.; Zhang, J.; Zhang, Z. An Accurate and Intelligent Approach to Predicting the Power Device Fatigue Failure Process. IEEE Trans. Power Electron. 2024, 3, 3568–3579. [Google Scholar] [CrossRef]

| Layer | Materials | p (g/cm3) | k W/(m·K) | Cρ (J/Kg·°C) |

|---|---|---|---|---|

| Chip | Si | 2.33 | 148 | 702 |

| Solder | Pb92.5Sn5Ag2.5 | 11.07 | 44 | 143.46 |

| Framework | Al | 2.7 | 211.7 | 880 |

| Bonding wire | KFC | 8.9 | 364 | 390 |

| Plastic compound | 720QE | 1.99 | 0.96 | 800 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Guo, W.; Chen, X.; Tang, Z.; Liu, X.; Ma, Z.; Xu, X.; Xia, D. Estimation of Void Area and Position in Solder Layer of Power Semiconductor Devices Based on Temperature Distribution Characteristics. Electronics 2024, 13, 3544. https://doi.org/10.3390/electronics13173544

Guo W, Chen X, Tang Z, Liu X, Ma Z, Xu X, Xia D. Estimation of Void Area and Position in Solder Layer of Power Semiconductor Devices Based on Temperature Distribution Characteristics. Electronics. 2024; 13(17):3544. https://doi.org/10.3390/electronics13173544

Chicago/Turabian StyleGuo, Wang, Xingang Chen, Zheng Tang, Xingmou Liu, Zhipeng Ma, Xiangtao Xu, and Daquan Xia. 2024. "Estimation of Void Area and Position in Solder Layer of Power Semiconductor Devices Based on Temperature Distribution Characteristics" Electronics 13, no. 17: 3544. https://doi.org/10.3390/electronics13173544