A Novel Modular Multilevel Converter Topology with High- and Low-Frequency Modules and Its Modulation Strategy

Abstract

:1. Introduction

2. Topological Structure of NMMC

3. Hybrid Modulation Strategy of the NMMC

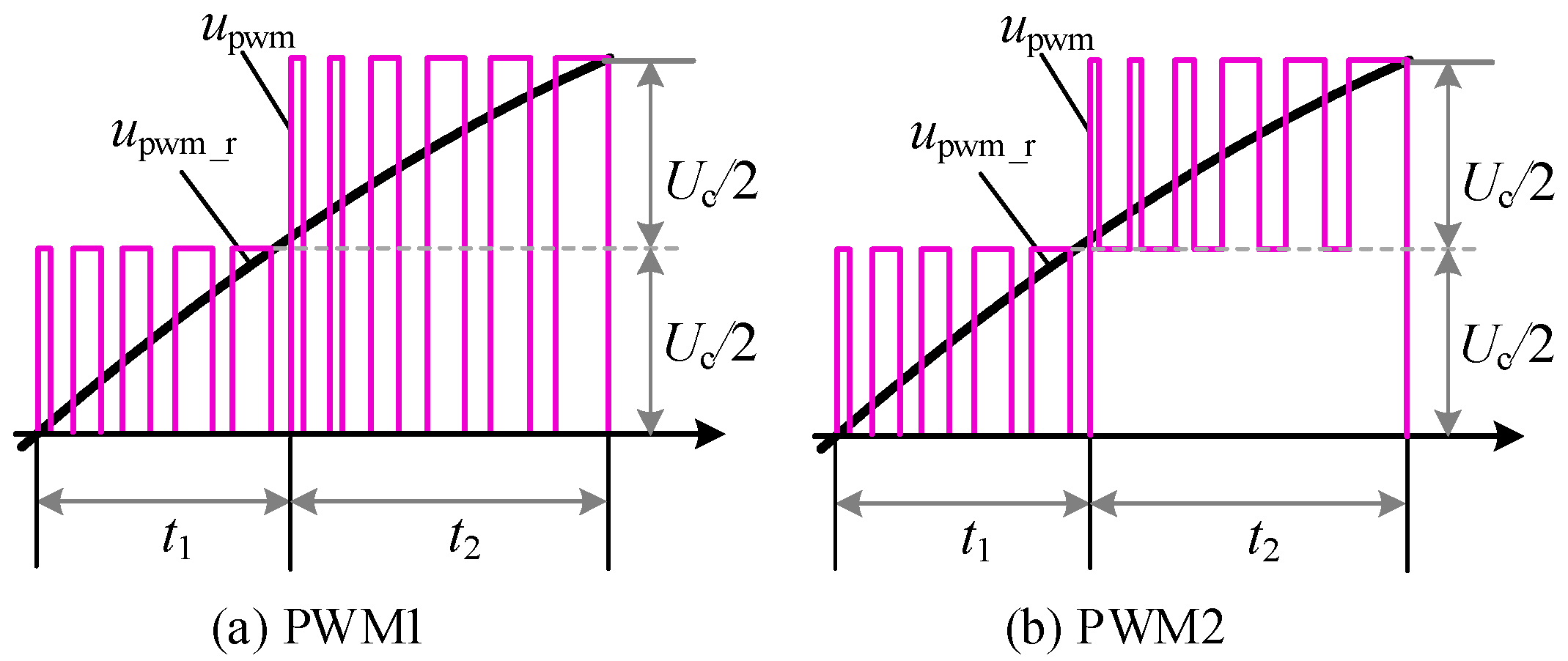

3.1. The Hybrid Modulation Principle of the NMMC

3.2. Modulation Principle of HCCM

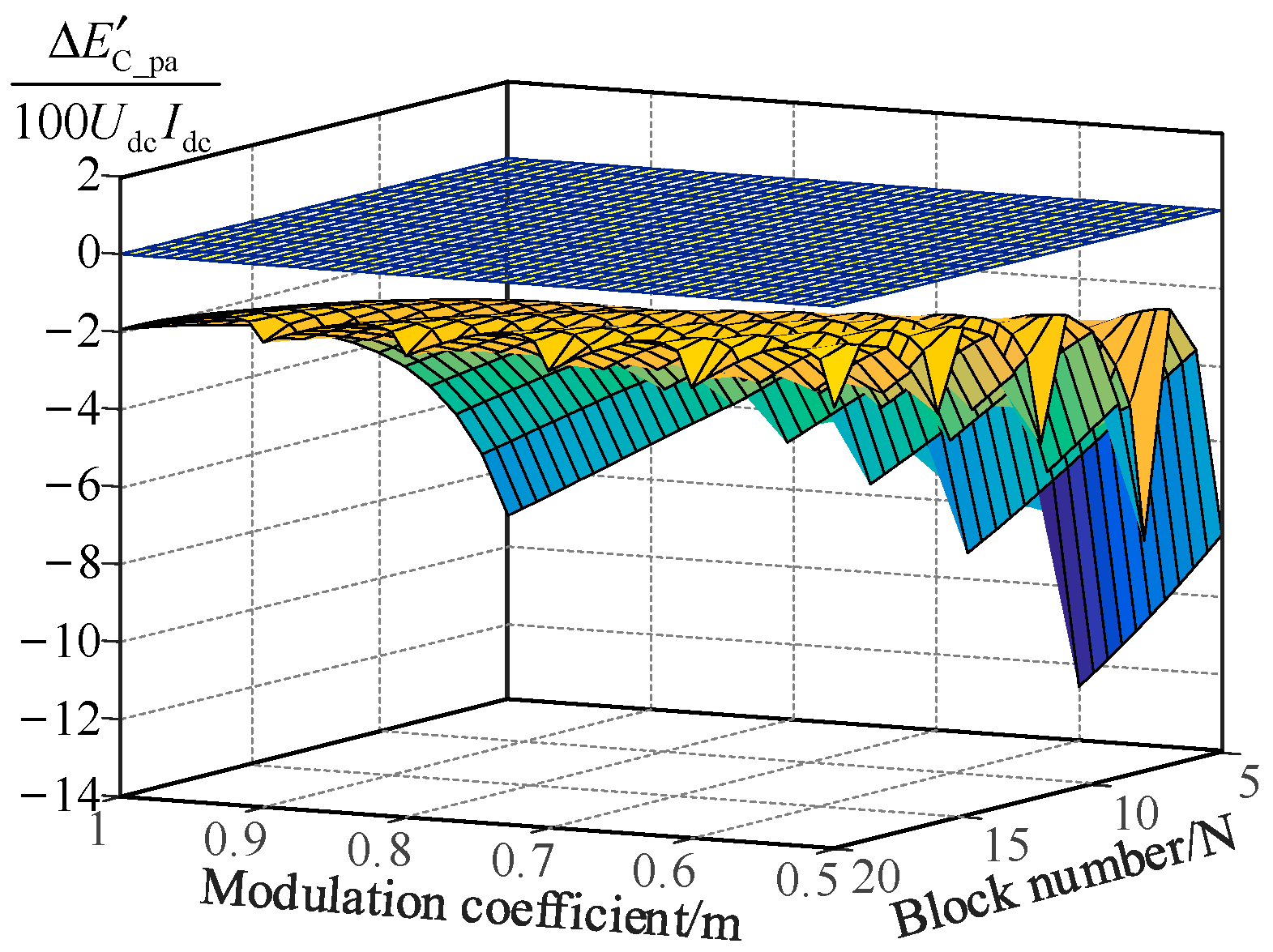

4. Capacitor Energy Analysis of the HCCM

5. The Voltage Balancing Strategy of NMMC

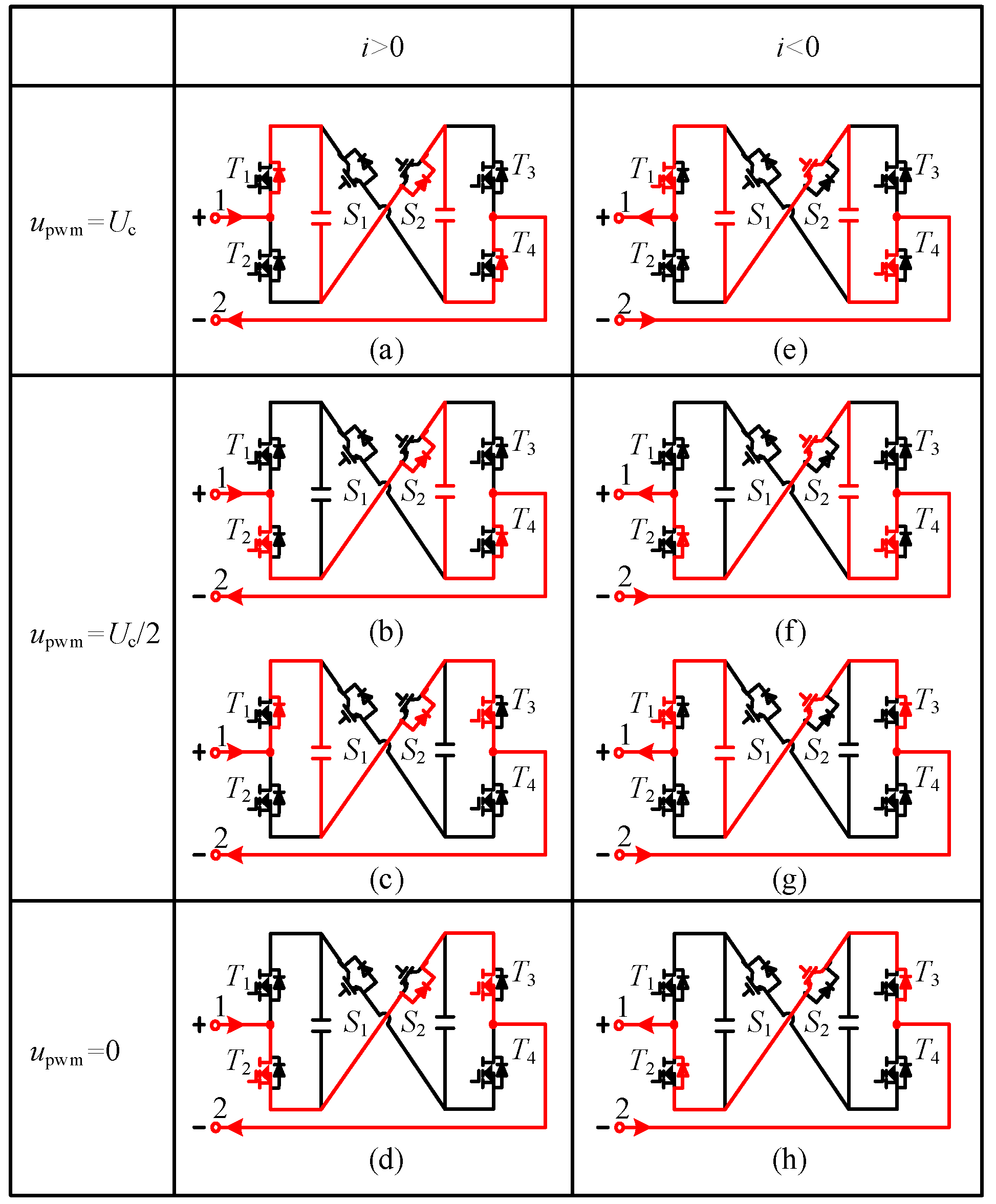

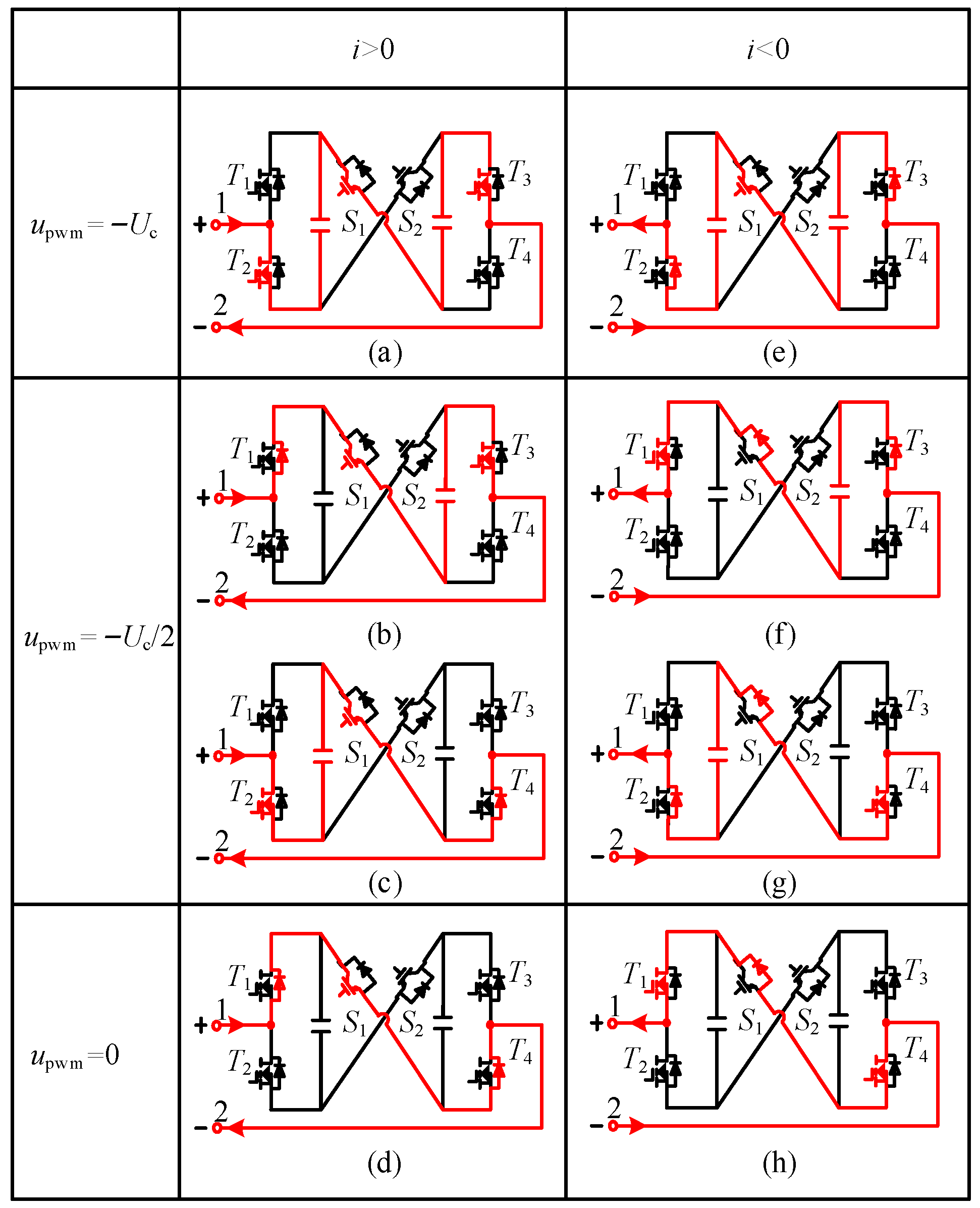

5.1. Internal Balance of Two Capacitor Voltages in HCCM

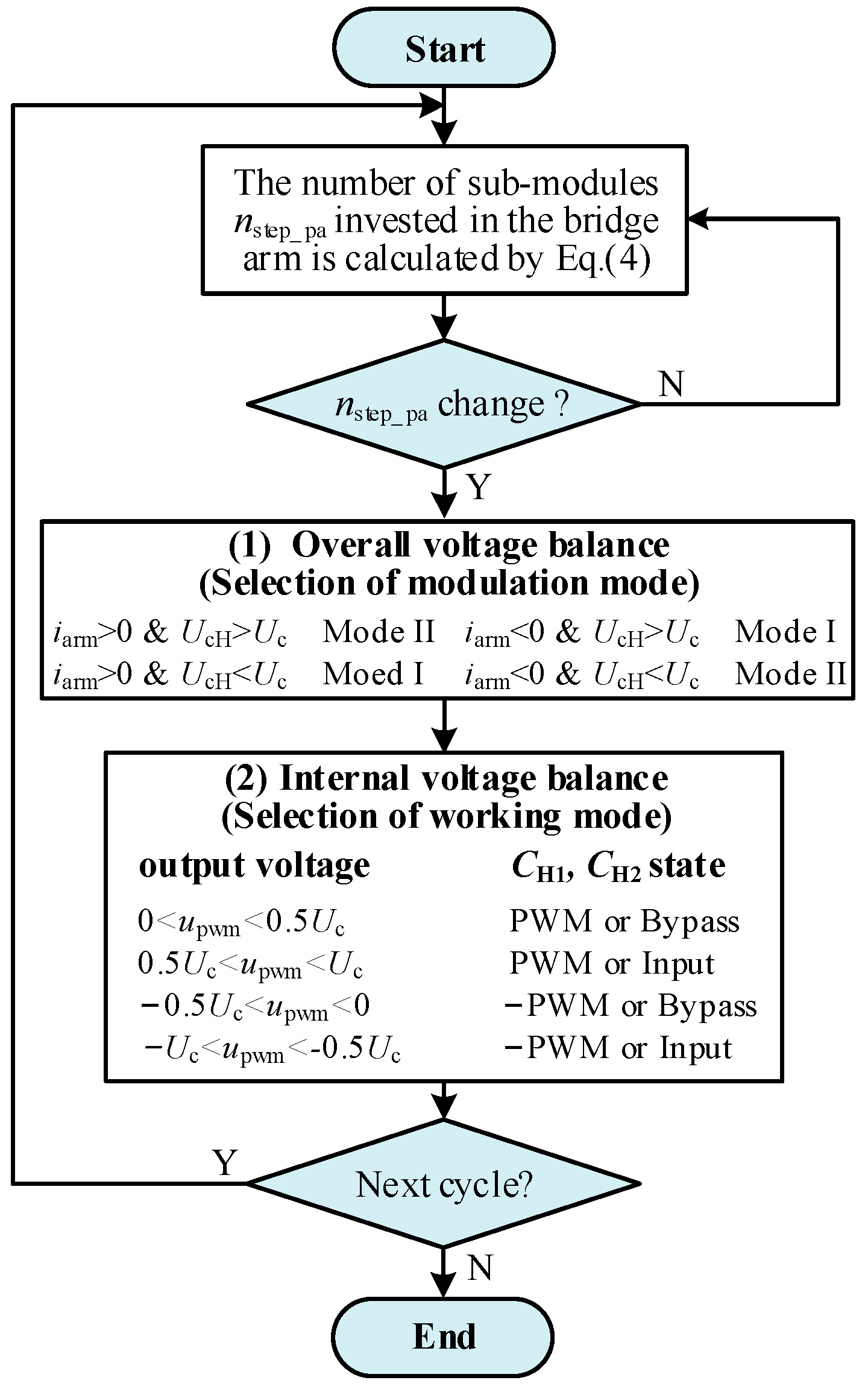

5.2. Voltage Balance Process of the HCCM

- (1)

- The number of nstep_pa needed to be put into the low-frequency sub-module of the upper bridge arm is calculated by (4).

- (2)

- The current time is compared with the nstep_pa calculated at the previous time. If there is no change, it is recalculated. If it changes, it enters the process of voltage balance.

- (3)

- Overall voltage balance. If iarm > 0 and nstep_pa = N − 1, it can only work in mode I. If iarm > 0 and nstep_pa < N − 1, the relationship between the total capacitor voltage UcH of the high-frequency sub-module and the reference capacitor voltage Uc is judged. If UcH < Uc, it works in mode I; if UcH > Uc, it works in mode II. If iarm< 0 and nstep_pa = N − 1, then it can only work in mode I. If iarm < 0 and nstep_pa < N − 1, the relationship between the capacitor voltage of the high-frequency sub-module and the reference capacitor voltage Uc is judged. If UcH < Uc, it works in mode II; if UCH > Uc, it works in mode I.

- (4)

- Internal voltage balance. Taking the output positive voltage of the high-frequency sub-module as an example, upwm = Uc and iarm > 0, the high-frequency sub-module is charged as a whole, and the capacitor CH1 and CH2 with a small voltage are directly input, and the capacitor with a high voltage outputs PWM; upwm = Uc and iarm < 0, the high-frequency sub-module is charged as a whole, and the high-voltage capacitors CH1 and CH2 are bypassed, and the low-voltage capacitors output PWM; when upwm= 0.5Uc and iarm < 0, the high-frequency sub-module is discharged as a whole, then the capacitor CH1 and CH2 with a small voltage are bypassed, and the capacitor with a high voltage outputs PWM.

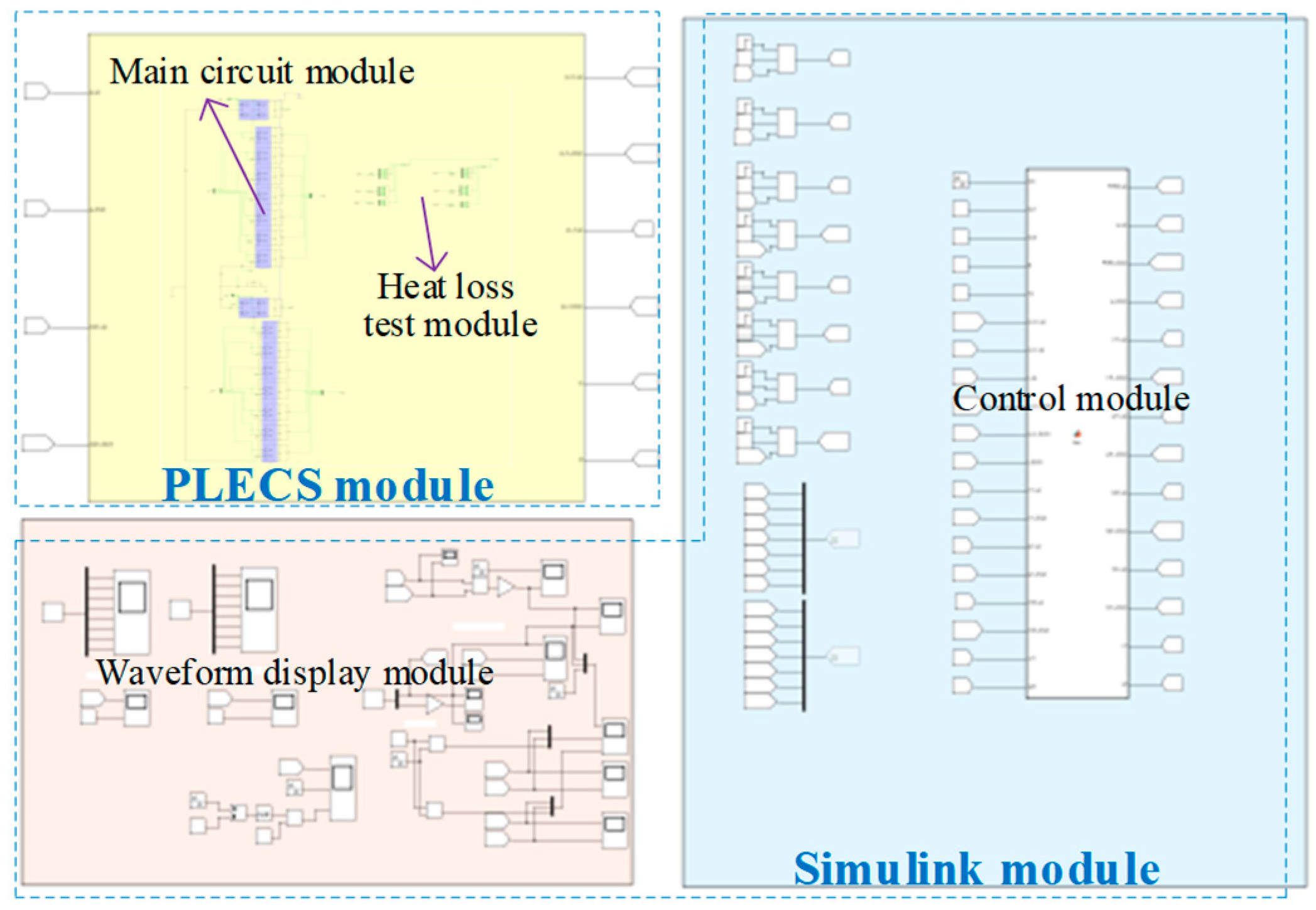

6. Experimental Analysis

7. Comparison of Device Cost and Loss

7.1. Device Cost Comparison

7.2. Loss Comparison

8. Conclusions

- (1)

- The proposed NMMC topology can output 2N + 1 levels with only one high-frequency sub-module for each leg. The number of SiC MOSFET devices is lower, and the total cost of the devices is lower.

- (2)

- Under the premise of ensuring the quality of the output waveform, the hybrid modulation strategy is used to focus the high-frequency action on the SiC MOSFET devices and the low-frequency action on the Si IGBT devices. Under the condition of a high equivalent switching frequency and a high output power, the operation efficiency of the proposed scheme is more obvious than that of the existing scheme.

- (3)

- A thorough examination of the energy fluctuation dynamics within the high-frequency submodule DC capacitor is conducted, leading to the formulation of a tailored voltage balancing strategy. This strategy proficiently ensures the stability of both high- and low-frequency submodule capacitor voltages.

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Abbreviations

| Parameters | Definitions |

| Udc | DC-side voltage of the NMMC |

| Uc | DC-side capacitor voltage of low-frequency submodule |

| U’c | DC-side capacitor voltage of high-frequency submodule |

| Uao | Output voltage of the phase a of the NMMC |

| Um | Output voltage amplitude |

| ω | The angular frequency |

| m | The modulation factor |

| uao_pr | Modulation wave of the upper arm of phase a |

| nstep_pa | The number of sub-modules that need to be put into the low-frequency sub-module of the bridge arm on phase a |

| floor(x) | A down-integer function |

| upwm_par | Reference value of the output voltage of the high-frequency sub-module of the bridge arm on phase a |

| u’step_pa | Step-wave voltage of the low-frequency sub-module in mode II |

| n’step_pa | The number of sub-modules that need to be invested in the low-frequency sub-module of the bridge arm on phase a |

| u’pwm_par | Output voltage reference value of the high-frequency sub-module of the bridge arm on phase a |

| Spa | Average switching function of the high-frequency sub-module of the bridge arm on phase a |

| iarm_pa | The bridge arm current on phase a |

| The total energy fluctuation of the DC-side capacitor of the high-frequency sub-module of the upper arm of a | |

| S’pa | The average switching function of the high-frequency bridge arm of the upper arm of phase a |

| The total energy fluctuation of the DC-side capacitor of the high-frequency sub-module in mode II |

References

- Belhaouane, M.M.; Ayari, M.; Guillaud, X.; Braiek, N.B. Robust Control Design of MMC-HVDC Systems Using Multivariable Optimal Guaranteed Cost Approach. IEEE Trans. Ind. Appl. 2019, 55, 2952–2963. [Google Scholar] [CrossRef]

- Hao, Q.; Li, Z.; Gao, F.; Zhang, J. Reduced-Order Small-Signal Models of Modular Multilevel Converter and MMC-Based HVdc Grid. IEEE Trans. Ind. Electron. 2018, 66, 2257–2268. [Google Scholar] [CrossRef]

- Hou, Y.; Guo, Q.; Ren, P.; Tu, C.; Huang, Z.; Jia, W. A Hybrid Cascaded Multilevel Converter Based on Si and SiC Devices and Its Regulation Optimization Strategy. IEEE Trans. Ind. Appl. 2024, 60, 4001–4011. [Google Scholar] [CrossRef]

- Karwatzki, D.; Mertens, A. Generalized Control Approach for a Class of Modular Multilevel Converter Topologies. IEEE Trans. Power Electron. 2017, 33, 2888–2900. [Google Scholar] [CrossRef]

- Guo, Q.; Hou, Y.; Tu, C.; Zhou, Z.; Zhang, H.; Yu, L.; Wang, L.; Jiang, F.; Wang, X. A Novel Hybrid Modular Multilevel Converter with Three-Phase Coupled High-Frequency Modules for Multi-Index Optimization. IEEE Trans. Transp. Electrif. 2024; early access. [Google Scholar] [CrossRef]

- Zhao, P.; Meng, Y.; Ge, M.; Duan, Z.; Wang, X.; Wang, J. Series-Parallel Multiple Integrated Modular Multilevel DC-DC Converter for All-DC Offshore Wind Power System. IEEE Trans. Power Deliv. 2024, 39, 2482–2494. [Google Scholar] [CrossRef]

- Tang, C.; Thiringer, T. A Model Predictive Control Method with Adaptive Weighting Factors for Enhancing Performance of Modular Multilevel Converters. IEEE J. Emerg. Sel. Top. Power Electron. 2024, 12, 3887–3899. [Google Scholar] [CrossRef]

- Geng, Z.; Yang, Y.; Xiao, Y.; Xie, W. A Submodule Fault-Tolerant Operation Scheme of Modular Multilevel Converters Through Novel Cold and Hot Mixed Topology. IEEE Trans. Power Deliv. 2024, 39, 2470–2481. [Google Scholar] [CrossRef]

- Pratheesh, K.J.; Jagadanand, G.; Ramchand, R. A Generalized-Switch-Matrix-Based Space Vector Modulation Technique Using the Nearest Level Modulation Concept for Neutral-Point-Clamped Multilevel Inverters. IEEE Trans. Ind. Electron. 2018, 65, 4542–4552. [Google Scholar] [CrossRef]

- Miyama, Y.; Ishizuka, M.; Kometani, H.; Akatsu, K. Vibration Reduction by Applying Carrier Phase-Shift PWM on Dual Three-Phase Winding Permanent Magnet Synchronous Motor. IEEE Trans. Ind. Appl. 2018, 54, 5998–6004. [Google Scholar] [CrossRef]

- Ronanki, D.; Williamson, S.S. A Novel 2 N + 1 Carrier-Based Pulse Width Modulation Scheme for Modular Multilevel Converters with Reduced Control Complexity. IEEE Trans. Ind. Appl. 2020, 56, 5593–5602. [Google Scholar] [CrossRef]

- Hu, P.; Jiang, D. A Level-Increased Nearest Level Modulation Method for Modular Multilevel Converters. IEEE Trans. Power Electron. 2014, 30, 1836–1842. [Google Scholar] [CrossRef]

- Wu, D.; Peng, L. Characteristics of nearest level modulation method with circulating current control for modular multilevel converter. IET Power Electron. 2016, 9, 155–164. [Google Scholar] [CrossRef]

- Wang, Y.; Hu, C.; Ding, R.; Xu, L.; Fu, C.; Yang, E. A Nearest Level PWM Method for the MMC in DC Distribution Grids. IEEE Trans. Power Electron. 2018, 33, 9209–9218. [Google Scholar] [CrossRef]

- Wang, Z.; Peng, L.; Zhang, J. Decomposed Nearest Level PWM Method With Reduced Switching Frequency for MMC. IEEE Trans. Power Electron. 2022, 38, 3340–3351. [Google Scholar] [CrossRef]

- Yang, G.; Zhou, S.; Peng, G.; Wu, W.; Xin, Q.; Xu, S. An improved hybrid modulation control strategy for MMC with auxiliary sub-modules. J. Power Supply 2024, 22, 74–82. [Google Scholar]

- Miu, H.; Mei, J.; Zhang, C.; Zheng, J.; Mei, F. A novel topology of n+1 hybrid modular multilevel converter and its control strategy. Electr. Power Autom. Equip. 2018, 38, 88–95. [Google Scholar]

- Shahane, R.; Belkhode, S.; Shukla, A.; Doolla, S. A Highly Efficient Hybrid Devices-based MMC with a Novel Modulation Scheme Using Hardware-in- Loop System. In Proceedings of the 2022 IEEE Applied Power Electronics Conference and Exposition (APEC), Houston, TX, USA, 20–24 March 2022; pp. 675–680. [Google Scholar]

- Li, C.; Lu, R.; Li, C.; Li, W.; Gu, X.; Fang, Y.; Ma, H.; He, X. Space Vector Modulation for SiC and Si Hybrid ANPC Converter in Medium-Voltage High-Speed Drive System. IEEE Trans. Power Electron. 2019, 35, 3390–3401. [Google Scholar] [CrossRef]

- Liu, C.; Zhuang, K.; Pei, Z.; Zhu, D.; Li, X.; Yu, Q.; Xin, H. Hybrid SiC-Si DC–AC Topology: SHEPWM Si-IGBT Master Unit Handling High Power Integrated with Partial-Power SiC-MOSFET Slave Unit Improving Performance. IEEE Trans. Power Electron. 2022, 37, 3085–3098. [Google Scholar] [CrossRef]

- Zhang, C.; Wang, J.; Qu, K.; Hu, B.; Li, Z.; Yin, X.; Shen, Z. WBG and Si Hybrid Half-Bridge Power Processing Toward Optimal Efficiency, Power Quality, and Cost Tradeoff. IEEE Trans. Power Electron. 2022, 37, 6844–6856. [Google Scholar] [CrossRef]

- Yin, T.; Lin, L.; Xu, C.; Zhu, D.; Jing, K. A Hybrid Modular Multilevel Converter Comprising SiC MOSFET and Si IGBT with Its Specialized Modulation and Voltage Balancing Scheme. IEEE Trans. Ind. Electron. 2022, 69, 11272–11282. [Google Scholar] [CrossRef]

- Kiehnle, P.; Himmelmann, P.; Hiller, M. GaN-Based Modular Multilevel Converter for Low-Voltage Grid Enables High Efficiency. In Proceedings of the 2022 24th European Conference on Power Electronics and Applications (EPE’22 ECCE Europe), Hanover, Germany, 5–9 September 2022; pp. 1–7. [Google Scholar]

- Kiehnle, P.; Katzenburg, N.; Stefanski, L.; Hiller, M. Hybrid Implementation of Cascade Control for GaN-Based Modular Multilevel Converter for Low-Voltage Grid. In Proceedings of the 2023 25th European Conference on Power Electronics and Applications (EPE’23 ECCE Europe), Aalborg, Denmark, 4–8 September 2023; pp. 1–10. [Google Scholar]

- Avila, A.; Garcia-Bediaga, A.; Oñederra, O.; Ruias, A.; Rodriguez, A. Comparative analysis of GaN HEMT vs. Si CoolMOS for a high-frequency MMC topology. In Proceedings of the 2017 19th European Conference on Power Electronics and Applications (EPE’17 ECCE Europe), Warsaw, Poland, 11–14 September 2017; pp. 1–9. [Google Scholar]

| S1 | S2 | T1 | T2 | T3 | T4 | Output Voltage |

|---|---|---|---|---|---|---|

| 0 | 1 | 1 | 0 | 0 | 1 | Uc |

| 0 | 1 | 0 | 1 | 0 | 1 | Uc/2 |

| 0 | 1 | 1 | 0 | 1 | 0 | Uc/2 |

| 0 | 1 | 0 | 1 | 1 | 0 | 0 |

| 1 | 0 | 0 | 1 | 1 | 0 | −Uc |

| 1 | 0 | 1 | 0 | 1 | 0 | −Uc/2 |

| 1 | 0 | 0 | 1 | 0 | 1 | −Uc/2 |

| 1 | 0 | 1 | 0 | 0 | 1 | 0 |

| Parameter | Value |

|---|---|

| Number of bridge arm sub-modules N | 8 |

| DC-side voltage Udc of NMMC | 600 V |

| DC-side capacitor voltage Uc of the sub-module | 75 V |

| DC-side capacitance CL of LFSM | 3.8 mF |

| DC-side capacitance CH of the HCCM | 3.8 mF |

| Bridge arm inductance L | 3 mH |

| Carrier frequency fc | 10 kHz |

| Modulation coefficient m | 0.9 |

| Device | Si-MMC | SiC-MMC | Ref. [22] | Proposed NMMC | |

|---|---|---|---|---|---|

| Si IGBT (1700 V/300 A) Model/Price | FF300R17ME4: USD 69.1 | 96 | / | 84 | 96 |

| FF300R17KE3: USD 94.5–121.8 | |||||

| FF300R17ME4_B11: USD 71.43–77.51 | |||||

| FF300R17ME4P_B11: USD 71.2–83.13 | |||||

| FF300R17KE4P: USD 73.15 | |||||

| FF300R17ME7_B11: USD 67.88–77.32 | |||||

| FF300R17KE4: USD 57.9–86 | |||||

| IFF300B17N2E4P_B11: USD 105.6–118.6 | |||||

| FF300R17ME4P: USD 75.2–83.13 | |||||

| SiC MOSFET (1700 V/300 A) Model/Price | CAB320M17XM3: USD 603.9–669.2 | / | 96 | / | / |

| WAS310M17BM3: USD 553.9–611.2 | |||||

| CAS310M17BM3: USD 503.2–555.4 | |||||

| SiC MOSFET (1200 V/300 A) Model/Price | CAS300M12BM2: USD 386.4–430.2 | / | / | 48 | 24 |

| WAB300M12BM3: USD 394.6–436.1 | |||||

| Cost | USD 5558.4–11,692.8 | USD 48307.2–64,243.2 | USD 23,410.8–31,164 | USD 14,832–22,159.2 | |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Huang, Z.; Bai, H.; Xu, M.; Hou, Y.; Yao, R.; Liu, Y.; Guo, Q.; Tu, C. A Novel Modular Multilevel Converter Topology with High- and Low-Frequency Modules and Its Modulation Strategy. Electronics 2024, 13, 3656. https://doi.org/10.3390/electronics13183656

Huang Z, Bai H, Xu M, Hou Y, Yao R, Liu Y, Guo Q, Tu C. A Novel Modular Multilevel Converter Topology with High- and Low-Frequency Modules and Its Modulation Strategy. Electronics. 2024; 13(18):3656. https://doi.org/10.3390/electronics13183656

Chicago/Turabian StyleHuang, Zejun, Hao Bai, Min Xu, Yuchao Hou, Ruotian Yao, Yipeng Liu, Qi Guo, and Chunming Tu. 2024. "A Novel Modular Multilevel Converter Topology with High- and Low-Frequency Modules and Its Modulation Strategy" Electronics 13, no. 18: 3656. https://doi.org/10.3390/electronics13183656