Analysis of Influencing Factors on Multilevel Storage Performance in Phase-Change Random Access Memory

Abstract

1. Introduction

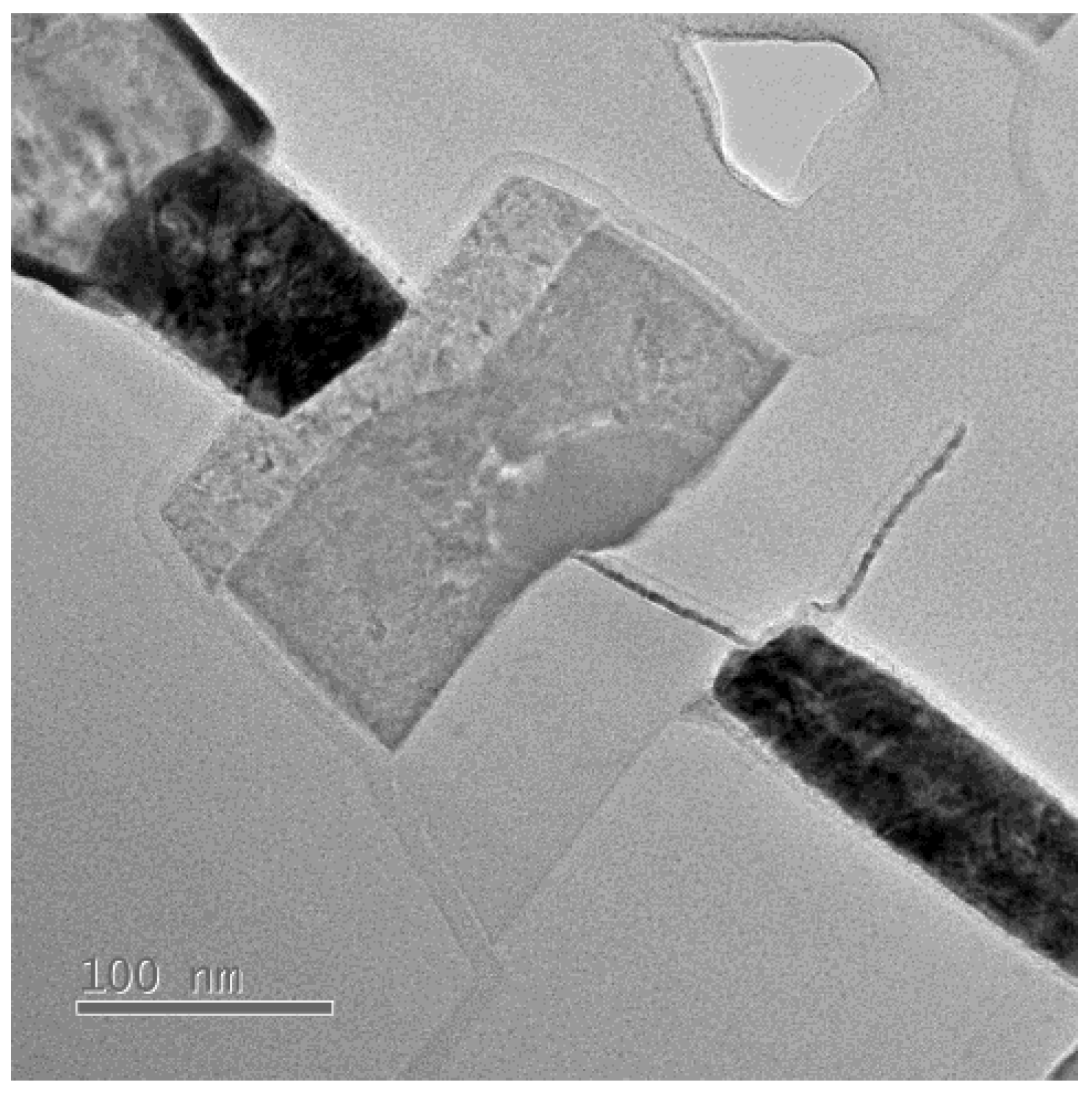

2. Experimental Devices and Experimental Methods

3. Results and Discussion

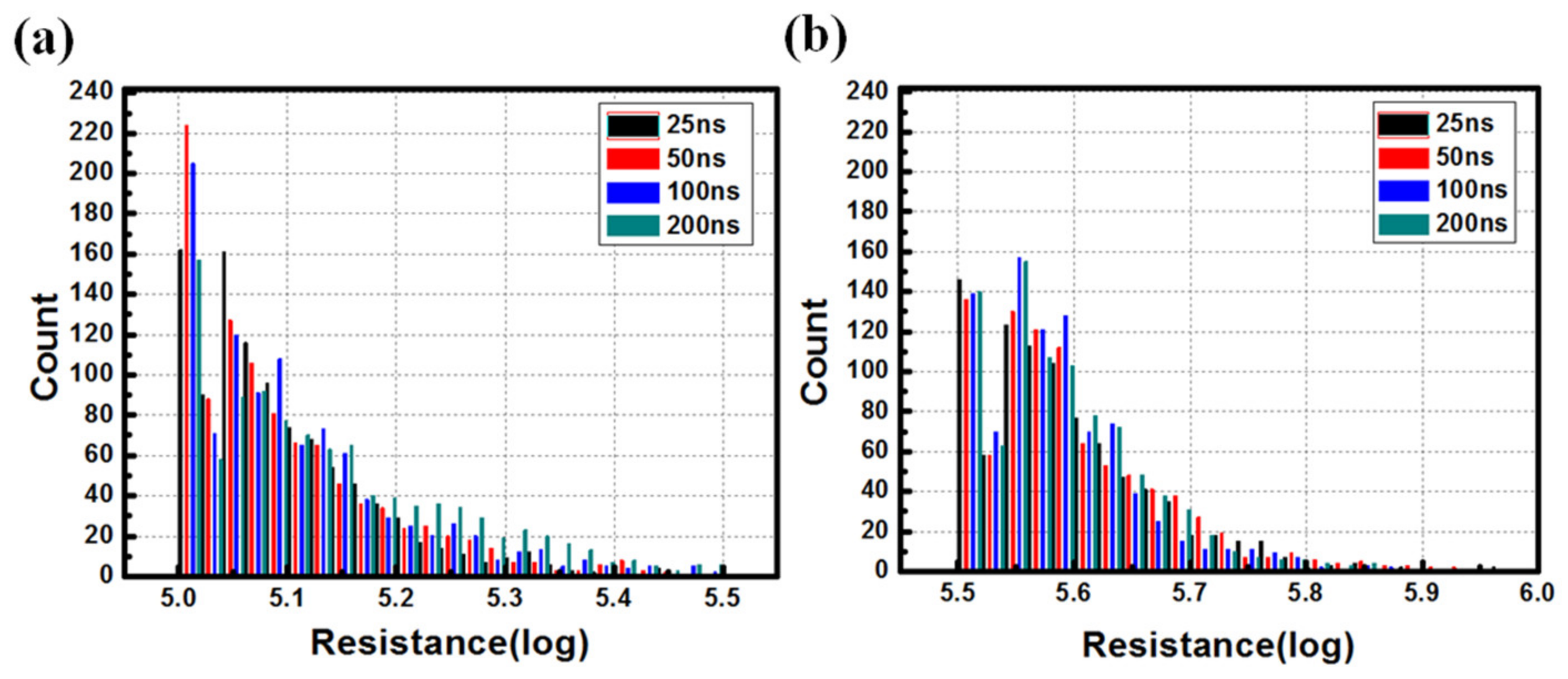

3.1. Effect of TRST on Multilevel Storage

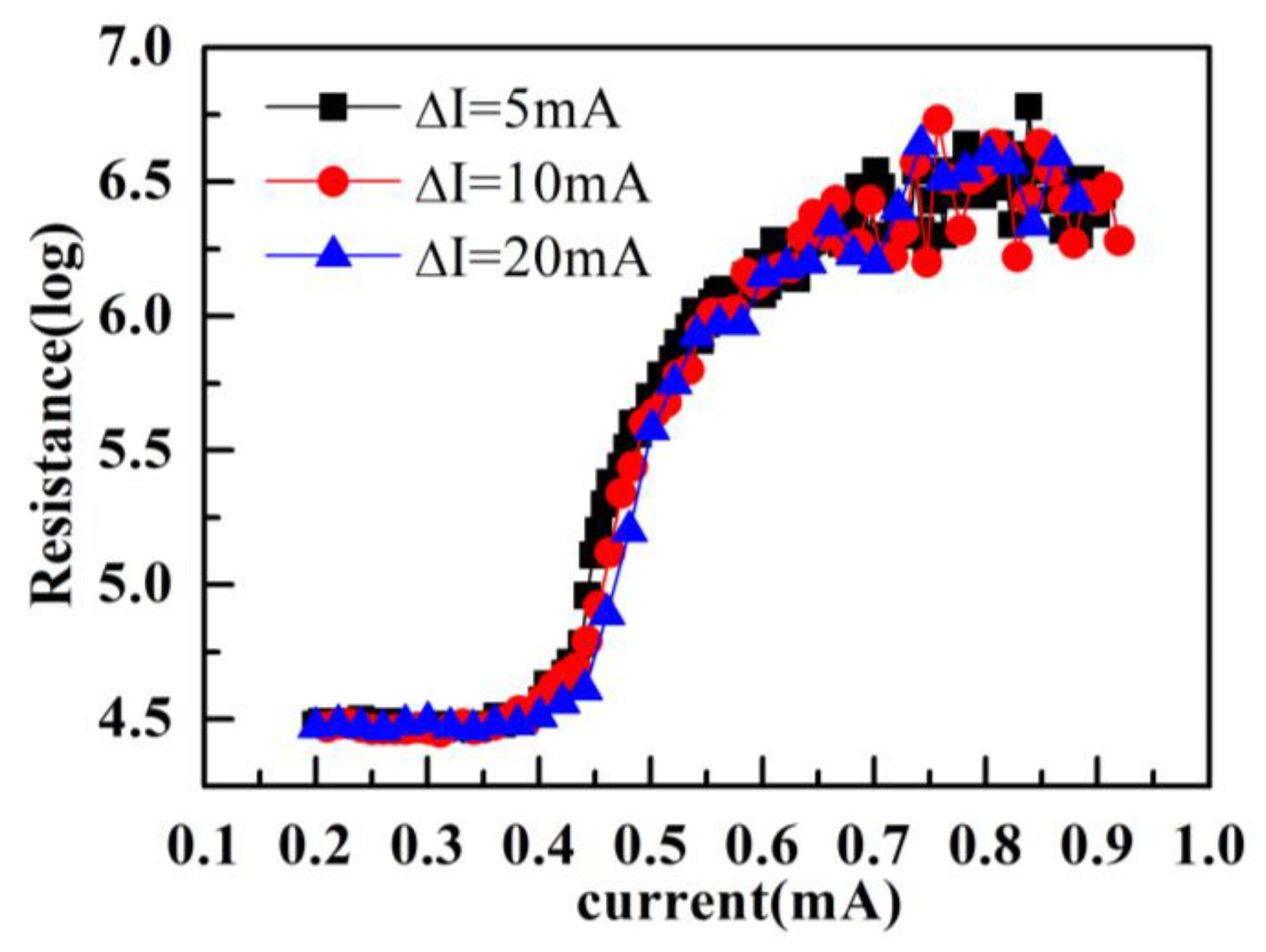

3.2. Effect of Pulse Increase on Multilevel Storage

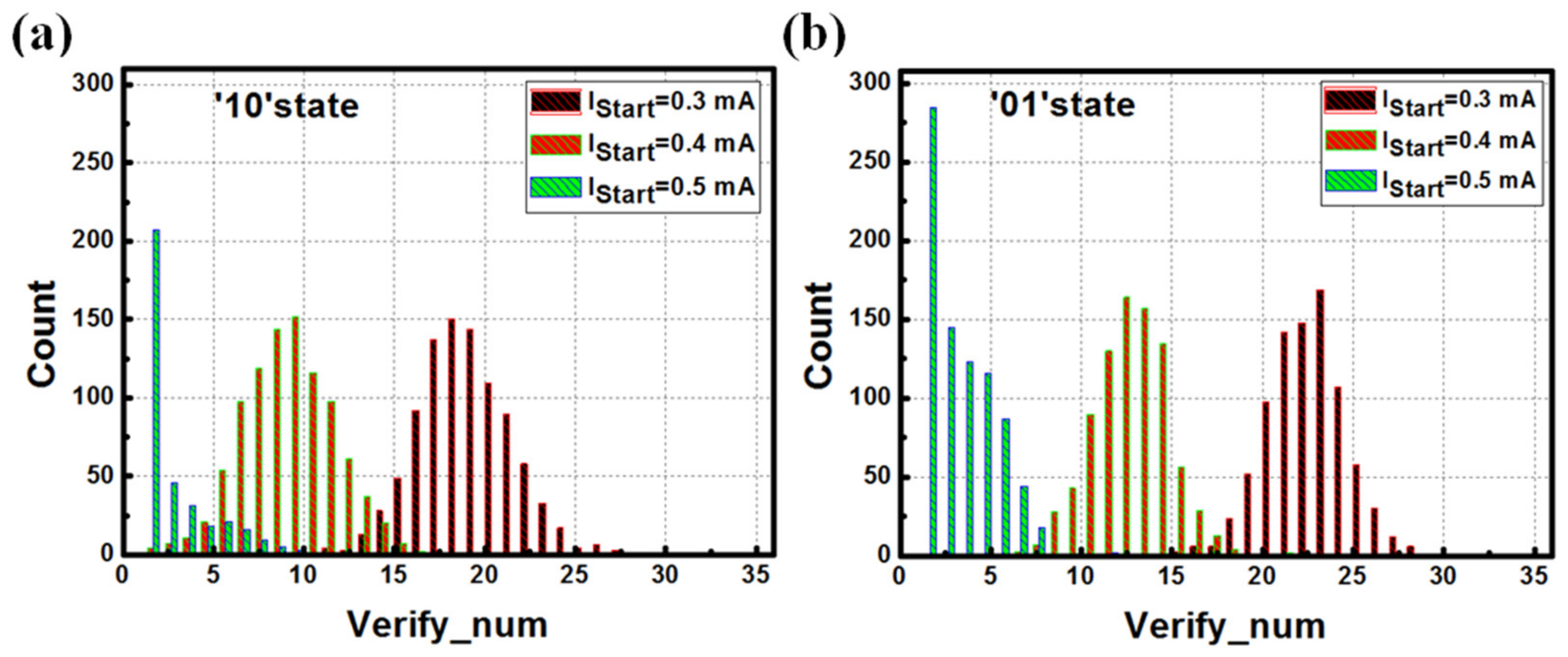

3.3. Effect of IStart on Multilevel Storage

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Oh, J.H.; Park, J.H.; Lim, Y.S.; Lim, H.S.; Oh, Y.T.; Kim, J.S.; Shin, J.M.; Song, Y.J.; Ryoo, K.C.; Lim, D.W.; et al. Full integration of highly manufacturable 512 Mb PRAM based on 90 nm technology. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 11–13 December 2006; pp. 2.6.1–2.6.4. [Google Scholar]

- Rao, F.; Ding, K.Y.; Zhou, Y.X.; Zheng, Y.H.; Xia, M.J.; Lv, S.L.; Song, Z.T.; Feng, S.L.; Ronneberger, I.; Mazzarello, R.; et al. Reducing the stochasticity of crystal nucleation to enable subnanosecond memory writing. Science 2017, 358, 1423–1427. [Google Scholar] [CrossRef] [PubMed]

- Wong, H.S.; Salahuddin, S. Memory leads the way to better computing. Nat. Nanotechnol. 2015, 10, 191–194. [Google Scholar] [CrossRef] [PubMed]

- Chen, Y.C.; Rettner, C.T.; Raoux, S.; Burr, G.W.; Chen, S.H.; Shelby, R.M.; Salinga, M.; Risk, W.P.; Happ, T.D.; McClelland, G.M.; et al. Ultra-thin phase-change bridge memory device using GeSb. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 11–13 December 2006; pp. 30.3.1–30.3.4. [Google Scholar]

- Im, D.H.; Lee, J.I.; Cho, S.L.; An, H.G.; Kim, D.H.; Kim, I.S.; Park, H.; Ahn, D.H.; Horii, H.; Park, S.O.; et al. A Unified 7.5 nm Dash-Type Confined Cell for High Performance PRAM Device. In Proceedings of the IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2008; pp. 1–4. [Google Scholar]

- Raoux, S.; Burr, G.W.; Breitwisch, M.J.; Rettner, C.T.; Chen, Y.C.; Shelby, R.M.; Salinga, M.; Krebs, D.; Chen, S.H.; Lung, H.L.; et al. Phase-change random access memory: A scalable technology. IBM J. Res. Dev. 2008, 52, 465–479. [Google Scholar] [CrossRef]

- Qureshi, M.K.; Srinivasan, V.; Rivers, J.A. Scalable high performance main memory system using phase-change memory technology. ACM Sigarch Comput. Archit. News 2009, 37, 24–33. [Google Scholar] [CrossRef]

- Tuma, T.; Pantazi, A.; Le Gallo, M.; Sebastian, A.; Nanotechnol, E. Stochastic phase-change neurons. Nat. Nanotechnol. 2016, 11, 693–699. [Google Scholar] [CrossRef] [PubMed]

- Xu, K. Silicon electro-optic micro-modulator fabricated in standard CMOS technology as components for all silicon monolithic integrated optoelectronic systems. J. Micromech. Microeng. 2021, 31, 054001. [Google Scholar] [CrossRef]

- Klersy, P.K.; Strand, D.A.; Ovshinsky, S.R. Electrically Erasable, Directly Overwritable, Multibit Single Cell Memory Element and Arrays Fabricated Therefrom. Google Patents. U.S. Patent 5536947A, 16 July 1996. [Google Scholar]

- Ahmad, I.; Imdoukh, M.; Alfailakawi, M.G. Extending multi-level STT-MRAM cell lifetime by minimising two-step and hard state transitions in hot bits. IET Comput. Digit. Tech. 2017, 11, 214–220. [Google Scholar] [CrossRef]

- Burr, G.W.; Brightsky, M.J.; Sebastian, A.; Cheng, H.Y.; Wu, J.Y.; Kim, S.; Sosa, N.E.; Papandreou, N.; Lung, H.L.; Pozidis, H. Recent Progress in Phase-Change Memory Technology. IEEE J. Emerg. Sel. Top. Circuits Syst. 2016, 6, 146–162. [Google Scholar] [CrossRef]

- Liu, L.; Gu, H.; Wu, W.; Wang, Z.; Lai, T. Multi-level phase-change behaviors of Ge2Sb2Te5/Sb7Se3 bilayer films and a design rule of multi-level phase-change films. J. Alloys Compd. 2024, 990, 174424. [Google Scholar] [CrossRef]

- Zhang, M.; Zhang, L.; Jiang, L.; Liu, Z.; Chong, F.T. Balancing Performance and Lifetime of MLC PCM by Using a Region Retention Monitor. In Proceedings of the 2017 IEEE International Symposium on High Performance Computer Architecture (HPCA), Austin, TX, USA, 4–8 February 2017; pp. 385–396. [Google Scholar] [CrossRef]

- Song, Z.; Cai, D.; Cheng, Y.; Wang, L.; Lv, S.; Xin, T.; Feng, G. 12-state multi-level cell storage implemented in a 128 Mb phase change memory chip. Nanoscale 2021, 13, 10455–10461. [Google Scholar] [CrossRef] [PubMed]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, Z.; Cai, D. Analysis of Influencing Factors on Multilevel Storage Performance in Phase-Change Random Access Memory. Electronics 2024, 13, 3802. https://doi.org/10.3390/electronics13193802

Wang Z, Cai D. Analysis of Influencing Factors on Multilevel Storage Performance in Phase-Change Random Access Memory. Electronics. 2024; 13(19):3802. https://doi.org/10.3390/electronics13193802

Chicago/Turabian StyleWang, Zhiyu, and Daolin Cai. 2024. "Analysis of Influencing Factors on Multilevel Storage Performance in Phase-Change Random Access Memory" Electronics 13, no. 19: 3802. https://doi.org/10.3390/electronics13193802

APA StyleWang, Z., & Cai, D. (2024). Analysis of Influencing Factors on Multilevel Storage Performance in Phase-Change Random Access Memory. Electronics, 13(19), 3802. https://doi.org/10.3390/electronics13193802