Predicting Work-in-Process in Semiconductor Packaging Using Neural Networks: Technical Evaluation and Future Applications

Abstract

1. Introduction

2. Related Research

2.1. Reducing Manufacturing Cycle Time

2.2. Reducing Production Variability

2.3. Neural Networks

- Neural Network Applications in Semiconductor Production and Inspection

- Innovative Chip Designs and Simulation Efficiency

- Deep Learning and Bayesian Network Approaches for Defect Detection

- Advanced Neural Network Architectures in Manufacturing

3. Research Methodology

3.1. Problem Statement

3.2. Model Development

- Inclusion of Hidden Layers. This fact enables the network to easily articulate the interactions and influences among input units.

- Use of Smooth and Differentiable Transfer Functions. This unique advantage ensures the network can derive weight adjustment formulas with ease using the steepest descent method.

- High Learning Precision. This strength can enable it to tackle complex sample recognition and highly non-linear function simulation issues.

- Efficient Data Recall Speed

- Wide Application Spectrum.

- Input Layer. For the front end of the network, its primary role is to receive external data and convert these into a format recognizable by the network. The number of processing units it encompasses is not fixed but may be dependent on the nature and complexity of the problem. For instance, in terms of image recognition, the input units might correspond to the pixels of an image, whereas in voice recognition, they might correlate to specific voice features.

- Hidden Layer. Positioned between the input and output layers, this is the network’s core. Its main function is to extract features from the input data and carry out a series of transformations and computations. The number of processing units in this layer is very flexible, and the optimal count is typically determined through multiple experiments and validations. Notably, the hidden layer can be singular or multiple, with its depth and structure often influencing the network’s performance and learning outcomes.

- Output Layer. The final stage of the network, its primary function is to generate the final prediction or classification results based on the computations obtained from the hidden layer. The number of processing units in this layer closely relates to the specific problem’s characteristics. For instance, in terms of the classification tasks, the number of output units might be equal to the number of target categories; whereas in regression tasks, it might be just a single output unit.

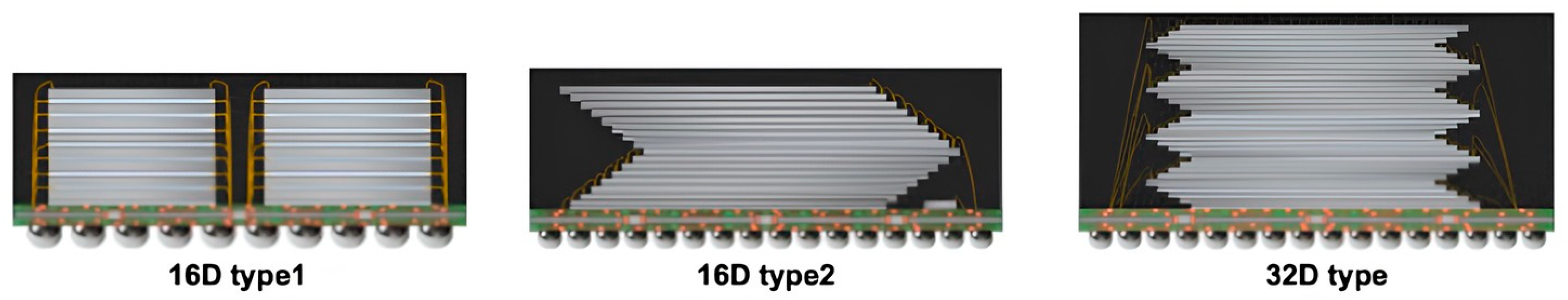

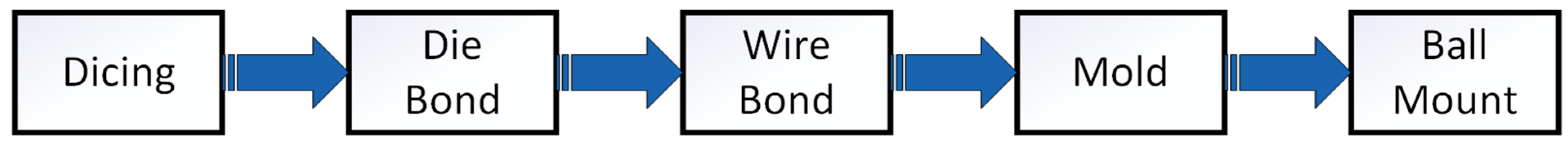

4. Case Study

4.1. Environmental Description

4.2. Model Validation

4.3. Computational Consumption

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Yu, S.; Chen, P.Y. Emerging memory technologies: Recent trends and prospects. IEEE Solid-State Circuits Mag. 2016, 8, 43–56. [Google Scholar] [CrossRef]

- Chien, C.F.; Chen, Y.J.; Hsu, C.Y.; Wang, H.K. Overlay error compensation using advanced process control with dynamically adjusted proportional-integral R2R controller. IEEE Trans. Autom. Sci. Eng. 2013, 11, 473–484. [Google Scholar] [CrossRef]

- Longauer, D.; Vasvári, T.; Hauck, Z. Investigating make-or-buy decisions and the impact of learning-by-doing in the semiconductor industry. Int. J. Prod. Res. 2024, 62, 3835–3852. [Google Scholar] [CrossRef]

- Moore, G. Cramming more components onto integrated circuits. Proc. IEEE 1998, 86, 82–85. [Google Scholar] [CrossRef]

- Schaller, R.R. Moore’s law: Past, present and future. IEEE Spectr. 1997, 34, 52–59. [Google Scholar] [CrossRef]

- Theis, T.N.; Wong, H.S.P. The end of moore’s law: A new beginning for information technology. Comput. Sci. Eng. 2017, 19, 41–50. [Google Scholar] [CrossRef]

- Picard, M.; Mohanty, A.K.; Misra, M. Recent advances in additive manufacturing of engineering thermoplastics: Challenges and opportunities. RSC Adv. 2020, 10, 36058–36089. [Google Scholar] [CrossRef]

- Mobin, S.; Cui, C.; Rao, F. Statistical approach to analyze duty cycle jitter amplification in NAND flash memory system. In Proceedings of the 2018 IEEE 27th Conference on Electrical Performance of Electronic Packaging and Systems (EPEPS), San Jose, CA, USA, 14–17 October 2018; pp. 75–77. [Google Scholar]

- Lee, H.L.; Padmanabhan, V.; Whang, S. The bullwhip effect in supply chains. Sloan Management Review 1997, 38, 93–102. [Google Scholar] [CrossRef]

- Hopp, W.J.; Spearman, M.L.; Chayet, S.; Donohue, K.L.; Gel, E.S. Using an optimized queueing network model to support wafer fab design. IIE Trans. 2002, 34, 119–130. [Google Scholar] [CrossRef]

- Wein, L.M. Scheduling semiconductor wafer fabrication. IEEE Trans. Semicond. Manuf. 1988, 1, 115–130. [Google Scholar] [CrossRef]

- Akcalt, E.; Nemoto, K.; Uzsoy, R. Cycle-time improvements for photolithography process in semiconductor manufacturing. IEEE Trans. Semicond. Manuf. 2001, 14, 48–56. [Google Scholar] [CrossRef]

- Kriett, P.O.; Eirich, S.; Grunow, M. Cycle time-oriented mid-term production planning for semiconductor wafer fabrication. Int. J. Prod. Res. 2017, 55, 4662–4679. [Google Scholar] [CrossRef]

- Tirkel, I. The effectiveness of variability reduction in decreasing wafer fabrication cycle time. In Proceedings of the 2013 Winter Simulations Conference (WSC), Washington, DC, USA, 8–11 December 2013; pp. 3796–3805. [Google Scholar]

- Chien, C.F.; Chen, C.H. A novel timetabling algorithm for a furnace process for semiconductor fabrication with constrained waiting and frequency-based setups. OR Spectr. 2007, 29, 391–419. [Google Scholar] [CrossRef]

- Lv, S.; Kim, H.; Zheng, B.; Jin, H. A review of data mining with big data towards its applications in the electronics industry. Appl. Sci. 2018, 8, 582. [Google Scholar] [CrossRef]

- Huang, C.L. The construction of production performance prediction system for semiconductor manufacturing with artificial neural networks. Int. J. Prod. Res. 1999, 37, 1387–1402. [Google Scholar] [CrossRef]

- Su, C.T.; Yang, T.; Ke, C.M. A neural-network approach for semiconductor wafer post-sawing inspection. IEEE Trans. Semicond. Manuf. 2020, 15, 260–266. [Google Scholar]

- Kim, J.K.; Knag, P.; Chen, T.; Zhang, Z. A 640M pixel/s 3.65 mW sparse event-driven neuromorphic object recognition processor with on-chip learning. In Proceedings of the 2015 Symposium on VLSI Circuits (VLSI Circuits), Kyoto, Japan, 16–19 June 2015; pp. C50–C51. [Google Scholar]

- Han, S.C.; Choi, J.; Hong, S.M. Acceleration of semiconductor device simulation with approximate solutions predicted by trained neural networks. IEEE Trans. Electron Devices 2021, 68, 5483–5489. [Google Scholar] [CrossRef]

- Wang, G.; Hasani, R.M.; Zhu, Y.; Grosu, R. A novel Bayesian network-based fault prognostic method for semiconductor manufacturing process. In Proceedings of the 2017 IEEE International Conference on Industrial Technology (ICIT), Toronto, ON, Canada, 22–25 March 2017; pp. 1450–1454. [Google Scholar]

- Wang, S.; Wang, H.; Yang, F.; Liu, F.; Zeng, L. Attention-based deep learning for chip-surface-defect detection. Int. J. Adv. Manuf. Technol. 2020, 121, 1957–1971. [Google Scholar] [CrossRef]

- Schlosser, T.; Friedrich, M.; Beuth, F.; Kowerko, D. Improving automated visual fault inspection for semiconductor manufacturing using a hybrid multistage system of deep neural networks. J. Intell. Manuf. 2020, 33, 1099–1123. [Google Scholar] [CrossRef]

- Wang, Y.; Sun, W.; Jin, J.; Kong, Z.; Yue, X. MVGCN: Multi-view graph convolutional neural network for surface defect identification using three-dimensional point cloud. J. Manuf. Sci. Eng. 2023, 145, 031004. [Google Scholar] [CrossRef]

- Kusiak, A. Convolutional and generative adversarial neural networks in manufacturing. Int. J. Prod. Res. 2020, 58, 1594–1604. [Google Scholar] [CrossRef]

- Shin, E.; Yoo, C.D. Efficient convolutional neural networks for semiconductor wafer bin map classification. Sensors 2023, 23, 1926. [Google Scholar] [CrossRef]

- Chen, T. A fuzzy back propagation network for output time prediction in a wafer fab. Appl. Soft Comput. 2003, 2, 211–222. [Google Scholar] [CrossRef]

- Chen, T.; Wang, Y.C.; Wu, H.C. A fuzzy-neural approach for remaining cycle time estimation in a semiconductor manufacturing factory—A simulation study. Int. J. Innov. Comput. Inf. Control. 2009, 5, 2125–2139. [Google Scholar]

- Lalis, J.T.; Gerardo, B.D.; Byun, Y. An adaptive stopping criterion for backpropagation learning in feedforward neural network. Int. J. Multimed. Ubiquitous Eng. 2014, 9, 149–156. [Google Scholar] [CrossRef]

- Li, X.J.; Ma, M.; Sun, Y. An adaptive deep learning neural network model to enhance machine-learning-based classifiers for intrusion detection in smart grids. Algorithms 2023, 16, 288. [Google Scholar] [CrossRef]

- Chen, Y.; Ding, S.; Long, J.; Hou, M.; Chen, X.; Gao, J.; He, Y.; Wong, C.P. Rationally designing the trace of wire bonder head for large-span-ratio wire bonding in 3D stacked packaging. IEEE Access 2020, 8, 206571–206580. [Google Scholar] [CrossRef]

| Variables | Data Type | Description |

|---|---|---|

| Customer | Category | Designated customer group. |

| Product Type | Category | Specific type of product. |

| Equipment Type | Category | Equipment model in use. |

| Location | Category | Specific production location or area. |

| Limit Machine Produce | Category | Machines designated for producing a certain product. |

| Remain Process | Numerical | Number of remaining process stations from the current station to completion. |

| Limit Wait Time | Numerical | Maximum waiting time allowed at each station, the unit is minutes. |

| Number of Chips in Package | Numerical | Number of chip layers in each package. |

| Process Total | Numerical | Number of total process stations. |

| Alarm Time | Numerical | Times of equipment alarm past 1 day. |

| Response | Data Type | Description |

| TAT | Numerical | The producing time from start to completion in the station, the unit is hours. |

| Packaging Process | Dicing | Die Bond | Wire Bond | Mold | Ball Mount | Total |

|---|---|---|---|---|---|---|

| Count | 268 | 1730 | 1855 | 545 | 1342 | 5740 |

| Packaging Process | Dicing | Die Bond | Wire Bond | Mold | Ball Mount |

|---|---|---|---|---|---|

| SVM | 0.9080 | 0.3505 | 0.3611 | 0.7631 | 0.6504 |

| BPNN | 0.4285 | 0.1563 | 0.1312 | 0.6139 | 0.1697 |

| Process | Product | N | N + 1 | N + 2 | N + 3 | N + 4 | N + 5 | N + 6 | N + 7 |

|---|---|---|---|---|---|---|---|---|---|

| Die Bond | BGA 16D-1 | 0 | 0 | 4 | 0 | 1 | 3 | 1 | 3 |

| Die Bond | BGA 1D | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| Wire Bond | BGA 16D-3 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| Wire Bond | BGA 2D-1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| Factory | Product | MSE (Before) | MSE (After) | Result |

|---|---|---|---|---|

| A | BGA 3D-9 | 0.31 | 0.04 | Good |

| A | BGA 2D-5 | 0.05 | 0.14 | Fail |

| B | BGA 5D-2 | 0.03 | 0.03 | Draw |

| B | BGA 8D-9 | 0.48 | 0.27 | Good |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wu, C.-T.; Li, S.-H.; Yen, D.C. Predicting Work-in-Process in Semiconductor Packaging Using Neural Networks: Technical Evaluation and Future Applications. Electronics 2024, 13, 4275. https://doi.org/10.3390/electronics13214275

Wu C-T, Li S-H, Yen DC. Predicting Work-in-Process in Semiconductor Packaging Using Neural Networks: Technical Evaluation and Future Applications. Electronics. 2024; 13(21):4275. https://doi.org/10.3390/electronics13214275

Chicago/Turabian StyleWu, Chin-Ta, Shing-Han Li, and David C. Yen. 2024. "Predicting Work-in-Process in Semiconductor Packaging Using Neural Networks: Technical Evaluation and Future Applications" Electronics 13, no. 21: 4275. https://doi.org/10.3390/electronics13214275

APA StyleWu, C.-T., Li, S.-H., & Yen, D. C. (2024). Predicting Work-in-Process in Semiconductor Packaging Using Neural Networks: Technical Evaluation and Future Applications. Electronics, 13(21), 4275. https://doi.org/10.3390/electronics13214275