Optimizing Confined Nitride Trap Layers for Improved Z-Interference in 3D NAND Flash Memory

Abstract

:1. Introduction

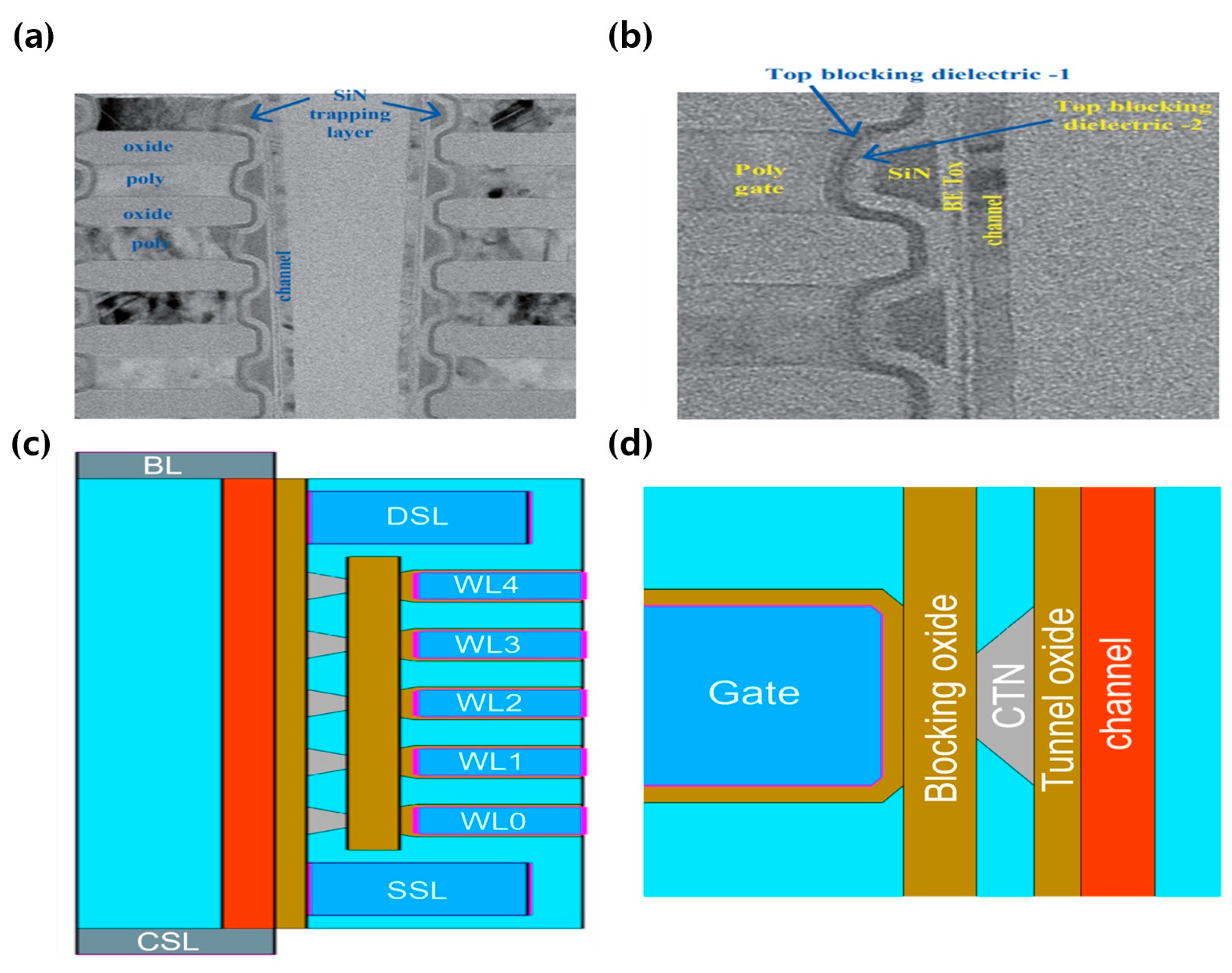

2. Simulation Set Up

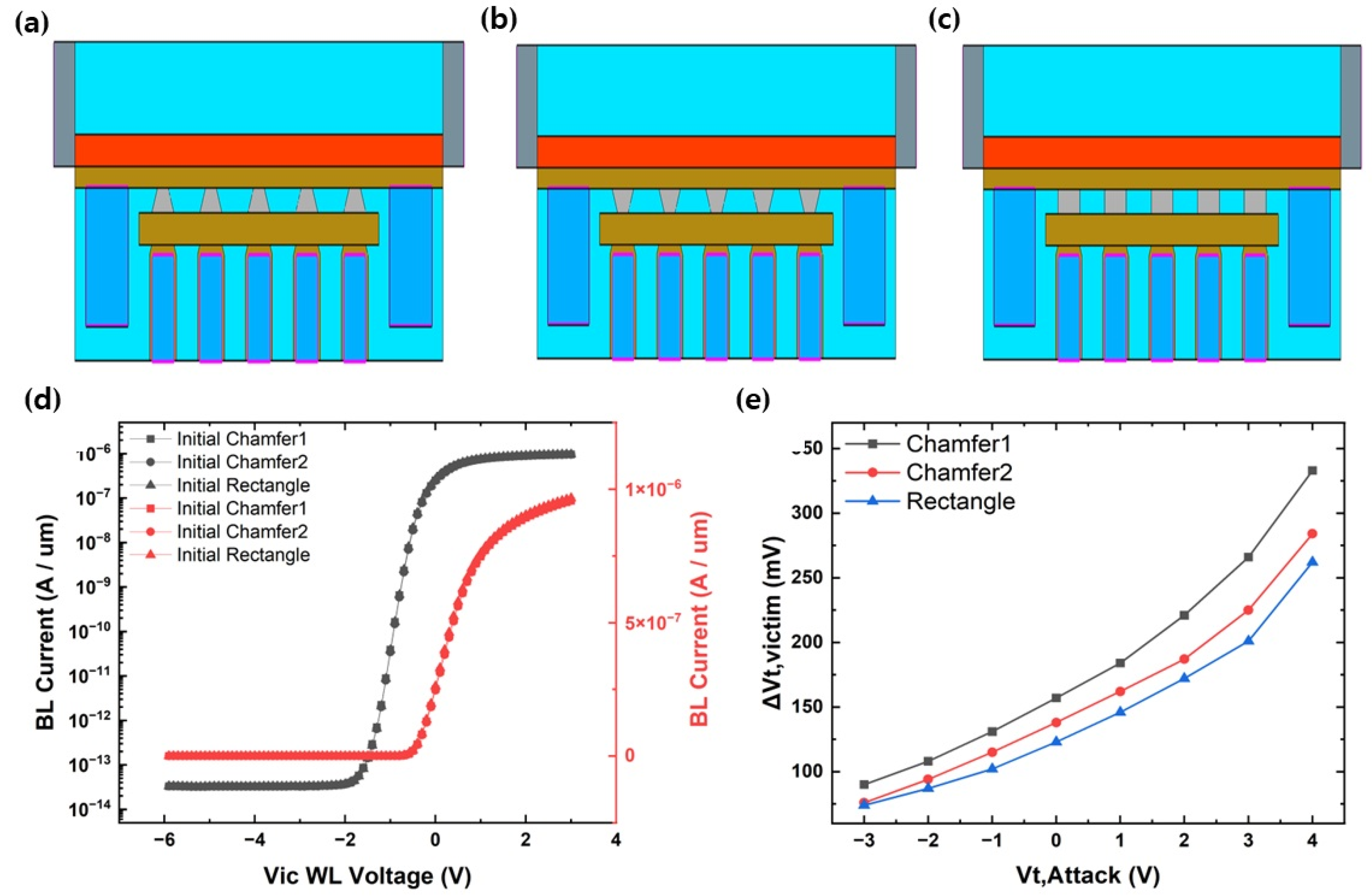

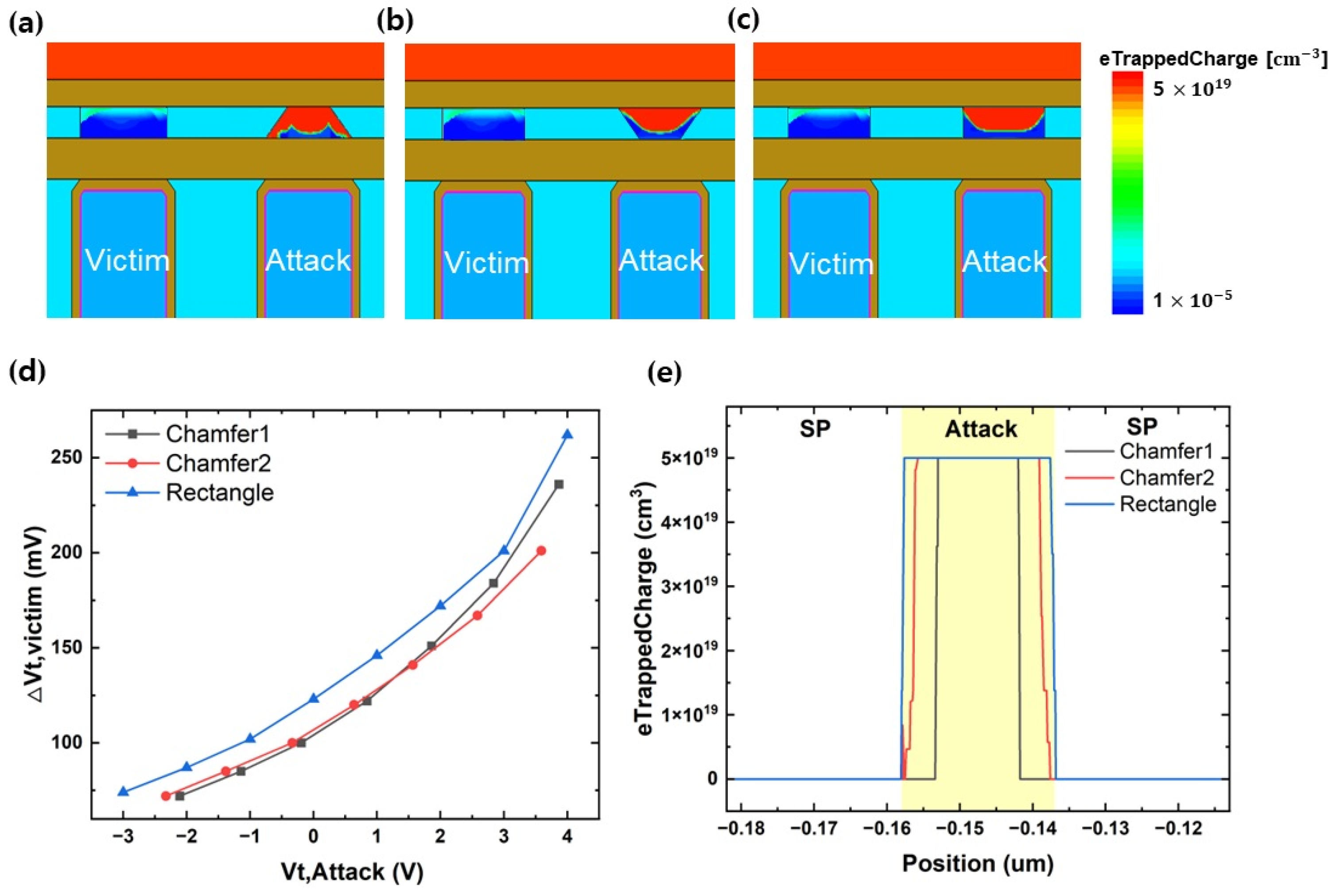

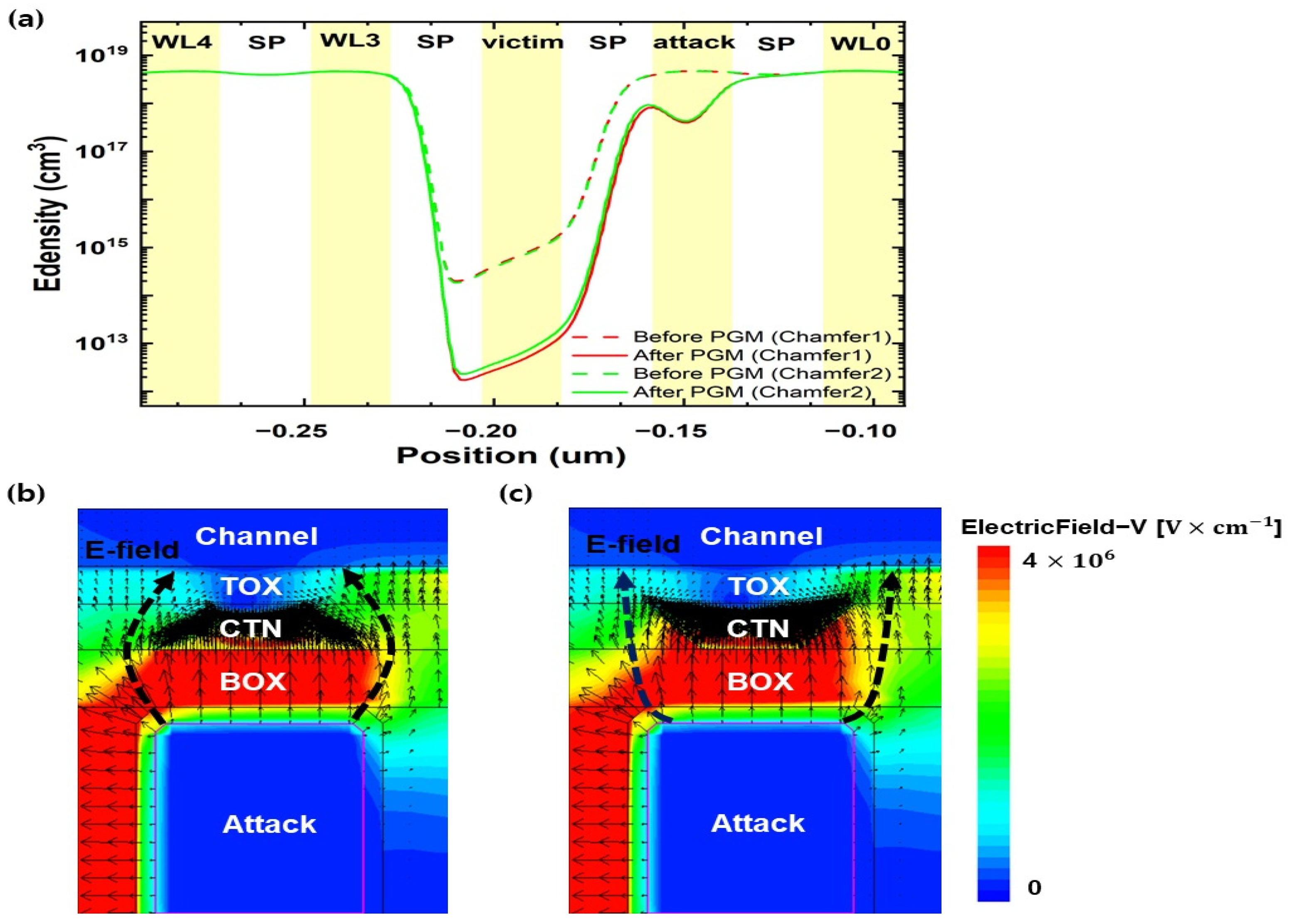

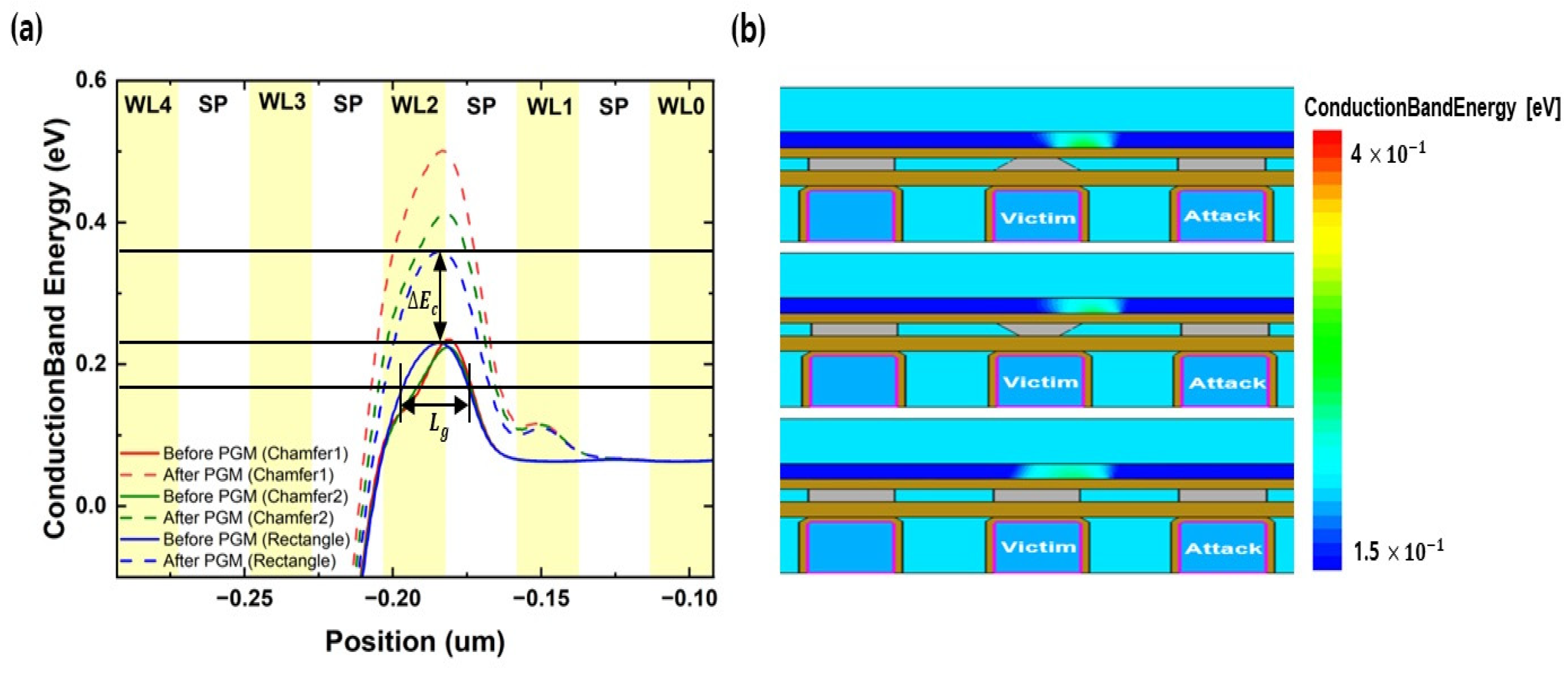

3. Investigation of Z-Interference

4. Process Flow

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Yoon, C.-W. The Fundamentals of NAND Flash Memory: Technology for tomorrow’s fourth industrial revolution. IEEE Solid-State Circuits Mag. 2022, 14, 56–65. [Google Scholar] [CrossRef]

- Aochi, H. BiCS flash as a future 3D non-volatile memory technology for ultra high density storage devices. In Proceedings of the 2009 IEEE International Memory Workshop (IMW), Monterey, CA, USA, 10–14 May 2009; pp. 1–2. [Google Scholar]

- Jang, J.; Kim, H.-S.; Cho, W.; Cho, H.; Kim, J.; Shim, S.I.; Younggoan; Jeong, J.-H.; Son, B.-K.; Kim, D.W.; et al. Vertical cell array using TCAT(terabit cell array transistor) technology for ultra high density NAND flash memory. In Proceedings of the 2019 Symposium on VLSI Technology, Kyoto, Japan, 15–17 June 2009; pp. 192–193. [Google Scholar]

- Goda, A. 3-D NAND Technology Achievements and Future Scaling Perspectives. IEEE Trans. Electron Devices 2020, 67, 1373–1381. [Google Scholar] [CrossRef]

- Kim, Y.; Kang, M.; Park, S.H.; Park, B.-G. Three-Dimensional NAND Flash Memory Based on Single-Crystalline Channel Stacked Array. IEEE Electron Device Lett. 2013, 34, 990–992. [Google Scholar] [CrossRef]

- Du, P.-Y.; Lue, H.-T.; Shih, Y.-H.; Hsieh, K.-Y.; Lu, C.-Y. Overview of 3D NAND Flash and progress of split-page 3D vertical gate (3DVG) NAND architecture. In Proceedings of the 2014 12th IEEE International Conference on Solid-State and Integrated Circuit Technology (ICSICT), Guilin, China, 28–31 October 2014; pp. 1–4. [Google Scholar]

- Kim, B.; Lee, S.; Hah, B.; Park, K.; Park, Y.; Jo, K.; Noh, Y.; Seol, H.; Lee, H.; Shin, J.; et al. 28.2 A High-Performance 1Tb 3b/Cell 3D-NAND Flash with a 194MB/s Write Throughput on over 300 Layers i. In Proceedings of the 2023 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 19–23 February 2023; pp. 27–29. [Google Scholar]

- Kim, M.; Yun, S.W.; Park, J.; Park, H.K.; Lee, J.; Kim, Y.S.; Na, D.; Choi, S.; Song, Y.; Lee, J.; et al. A 1Tb 3b/Cell 8th-Generation 3D-NAND Flash Memory with 164MB/s Write Throughput and a 2.4Gb/s Interface. In Proceedings of the 2022 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 20–26 February 2022; pp. 136–137. [Google Scholar]

- Park, S.; Lee, J.; Jang, J.; Lim, J.K.; Kim, H.; Shim, J.J.; Yu, M.-T.; Kang, J.-K.; Ahn, S.J.; Song, J. Highly-reliable cell characteristics with 128-layer single-stack 3D-NAND flash memory. In Proceedings of the 2021 Symposium on VLSI Technology, Kyoto, Japan, 13–19 June 2021; pp. 1–2. [Google Scholar]

- Jo, H.; Ahn, S.; Shin, H. Investigation and Modeling of Z-Interference in Poly-Si Channel-Based 3-D NAND Flash Memories. IEEE Trans. Electron Devices 2022, 69, 543–548. [Google Scholar] [CrossRef]

- Yi, S.-I.; Kim, J. Novel Program Scheme of Vertical NAND Flash Memory for Reduction of Z-Interference. Micromachines 2021, 12, 584. [Google Scholar] [CrossRef] [PubMed]

- Sim, J.-M.; Song, Y.-H. Asymmetric Read Bias for Alleviating Cell-to-Cell Interference in 3D NAND Flash Memory. In Proceedings of the 2021 IEEE Region 10 Symposium (TENSYMP), Jeju, Republic of Korea, 23–25 August 2021; pp. 1–4. [Google Scholar]

- Sim, J.-M.; Kang, M.; Song, Y.-H. A New Read Scheme for Alleviating Cell-to-Cell Interference in Scaled-Down 3D NAND Flash Memory. Electronics 2020, 9, 1775. [Google Scholar] [CrossRef]

- Jia, J.; Jin, L.; Jia, X.; You, K. A Novel Program Scheme for Z-Interference Improvement in 3D NAND Flash Memory. Micromachines 2023, 14, 896. [Google Scholar] [CrossRef] [PubMed]

- Fu, C.-H.; Lue, H.-T.; Hsu, T.-H.; Chen, W.-C.; Lee, G.-R.; Chiu, C.-J.; Wang, K.-C.; Lu, C.-Y. A Novel Confined Nitride-Trapping Layer Device for 3D NAND Flash with Robust Retention Performances. In Proceedings of the 2019 Symposium on VLSI Technology, Kyoto, Japan, 12 February 2019; pp. T212–T213. [Google Scholar]

- Chang, Y.-W.; Wu, G.-W.; Yang, I.-C.; Huang, Y.-H.; Lee, Y.-J.; Chen, K.-F.; Chen, Y.-J.; Lu, T.-C.; Chen, K.-C.; Lu, C.-Y. Deteriorated Non-Linear Interference in 3D NAND Cell with Word-Line Pitch Scaling Due to the Incapability to Turn on Non-Gate-Controlled Region. IEEE Electron Device Lett. 2023, 44, 1837–1840. [Google Scholar] [CrossRef]

- Park, K.-T.; Sel, J.-S.; Choi, J.; Song, Y.; Kim, C.; Kim, K. A Novel nand Flash Memory with Asymmetric S/D Structure Using Fringe-Field-Induced Inversion Layer. IEEE Trans. Electron Devices 2007, 55, 404–410. [Google Scholar] [CrossRef]

- Fu, C.-H.; Lue, H.-T.; Hsu, T.-H.; Chen, W.-C.; Lee, G.-R.; Chiu, C.-J.; Wang, K.-C.; Lu, C.-Y. A Novel Confined Ni-tride-Trapping Layer Device for 3-D NAND Flash with Robust Retention Performances. IEEE Trans. Electron Devices 2020, 67, 989–994. [Google Scholar] [CrossRef]

- Longjuan, T.; Yinfang, Z.; Jinling, Y.; Yan, L.; Wei, Z.; Jing, X.; Yunfei, L.; Fuhua, Y. Dependence of wet etch rate on deposition, annealing conditions and etchants for PECVD silicon nitride film. J. Semicond. 2009, 30, 155–158. [Google Scholar] [CrossRef]

- Provine, J.; Schindler, P.; Kim, Y.; Walch, S.P.; Kim, H.J.; Kim, K.-H.; Prinz, F.B. Correlation of film density and wet etch rate in hydrofluoric acid of plasma enhanced atomic layer deposited silicon nitride. AIP Adv. 2016, 6, 065012. [Google Scholar] [CrossRef]

| Program | Erase | Read | |

|---|---|---|---|

| Selected cell | 18.5 V~19 V | 0 V | −3 V~5 V |

| Unselected cell | 9 V | 0 V | 5.5 V |

| BL | 0 V | 22 V | 0.5 V |

| DSL | 3.3 V | floating | 3.3 V |

| SSL | 0 V | floating | 3.3 V |

| SL | 2 V | 22 V | 0 V |

| Time | 20 µs | 0.5 ms | - |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kim, Y.; Hong, S.K.; Park, J.K. Optimizing Confined Nitride Trap Layers for Improved Z-Interference in 3D NAND Flash Memory. Electronics 2024, 13, 1020. https://doi.org/10.3390/electronics13061020

Kim Y, Hong SK, Park JK. Optimizing Confined Nitride Trap Layers for Improved Z-Interference in 3D NAND Flash Memory. Electronics. 2024; 13(6):1020. https://doi.org/10.3390/electronics13061020

Chicago/Turabian StyleKim, Yeeun, Seul Ki Hong, and Jong Kyung Park. 2024. "Optimizing Confined Nitride Trap Layers for Improved Z-Interference in 3D NAND Flash Memory" Electronics 13, no. 6: 1020. https://doi.org/10.3390/electronics13061020

APA StyleKim, Y., Hong, S. K., & Park, J. K. (2024). Optimizing Confined Nitride Trap Layers for Improved Z-Interference in 3D NAND Flash Memory. Electronics, 13(6), 1020. https://doi.org/10.3390/electronics13061020